LRC I VRC KODERDEKODER autori Miljan Nikolic 12046

- Slides: 31

LRC I VRC KODER/DEKODER autori: Miljan Nikolic 12046 Milosevic 10278

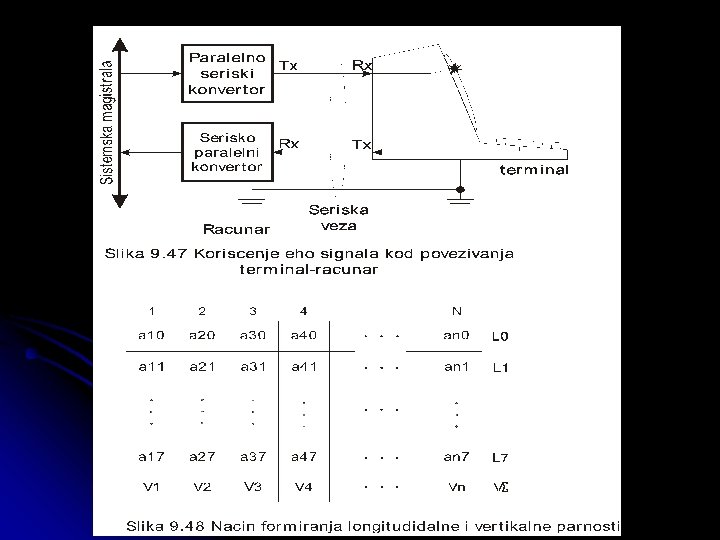

UVOD l l l Pojam prenos podataka, ili komuniciranja podacima odnosi se na prenos informacije sa jednog mesta na drugo u kodiranoj formi pomocu informacionih sistema Prenos se ostvaruje kao serijski ili paralelni Prilikom realizacije komunikacionih sistema uocavaju se pojedini blokovi koji se mogu svrstati u tri razlicite grupe : DTE (Data Terminal Equipment), DCE (Data Comunication Equipment) i kanal

l l l DTE je integrisana celina koju cine tastatura, CRT displej, memorija i upravljacka logika, tj. mikroracunarski sistem. DCE (modulator/demodulator tj. modem) vrsi neophodnu konverziju izmedju DTE-a i kanala. DCE kontrolise vreme trajanja signala, definise propusni opseg predajnog/prijemnog signala, odredjuje nivo snage na predajnoj i prijemnoj strani sa ciljem da prenos bude efikasan i pouzdan Kanal moze da se ostvari kablovskom ili radio vezom.

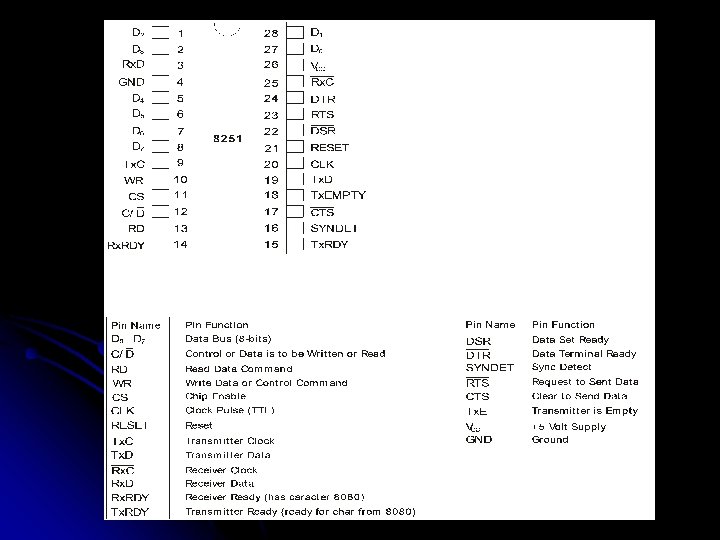

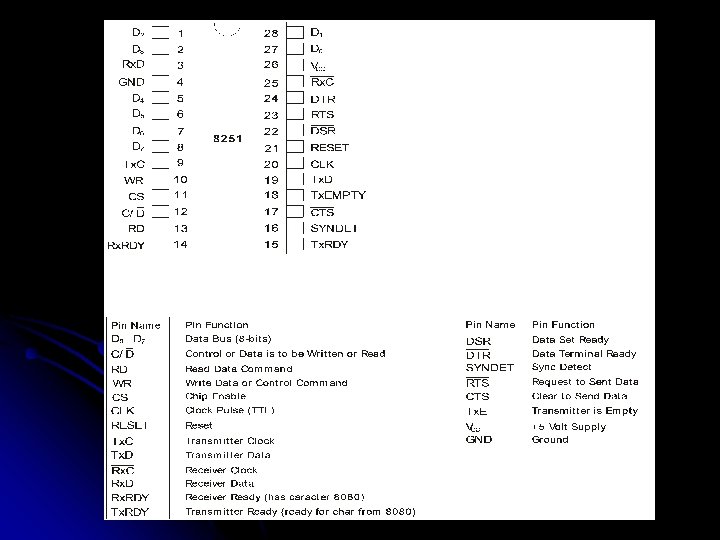

VRC I LRC KODIRANJE l Princip rada USART 8251 l Cip 8251 je univerzalni sinhrono-asinhroni prijemno-predajni cip dizajniran za prenos podataka u mikro kompjuterskim sistemima (USART)

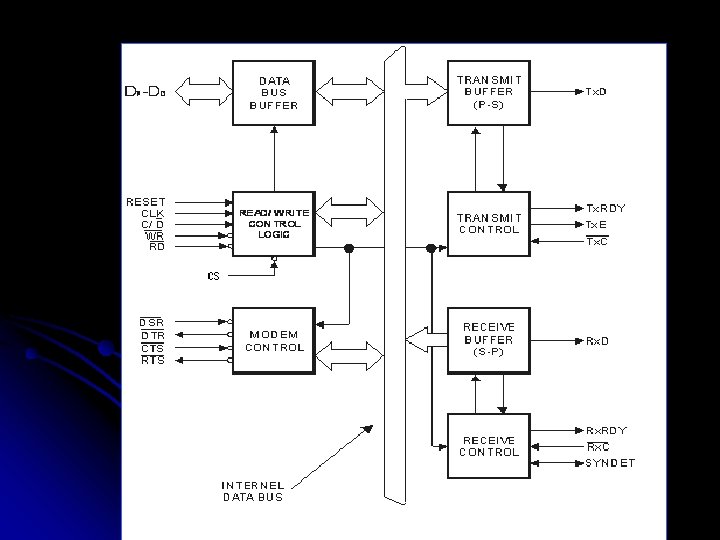

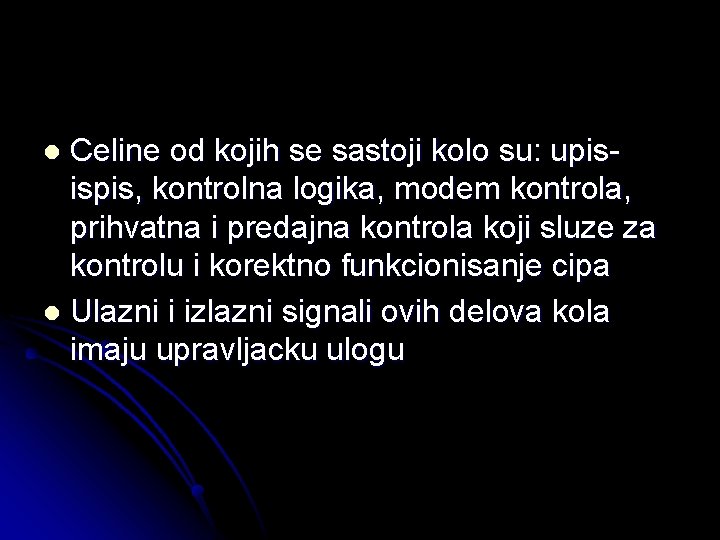

Celine od kojih se sastoji kolo su: upisispis, kontrolna logika, modem kontrola, prihvatna i predajna kontrola koji sluze za kontrolu i korektno funkcionisanje cipa l Ulazni i izlazni signali ovih delova kola imaju upravljacku ulogu l

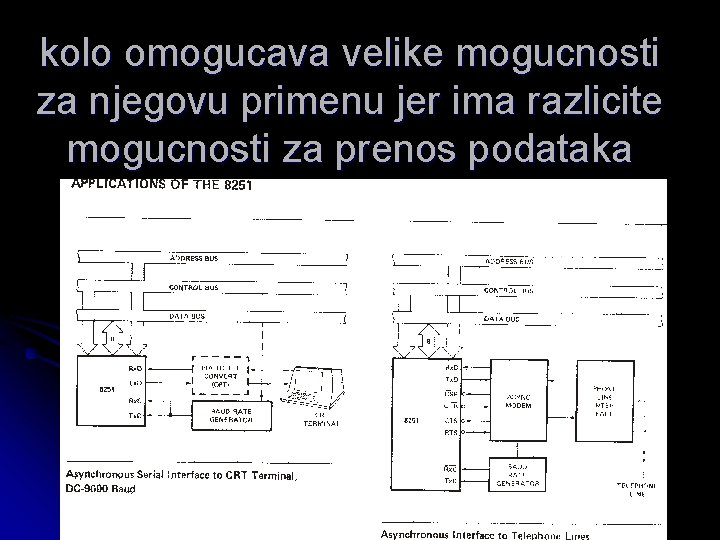

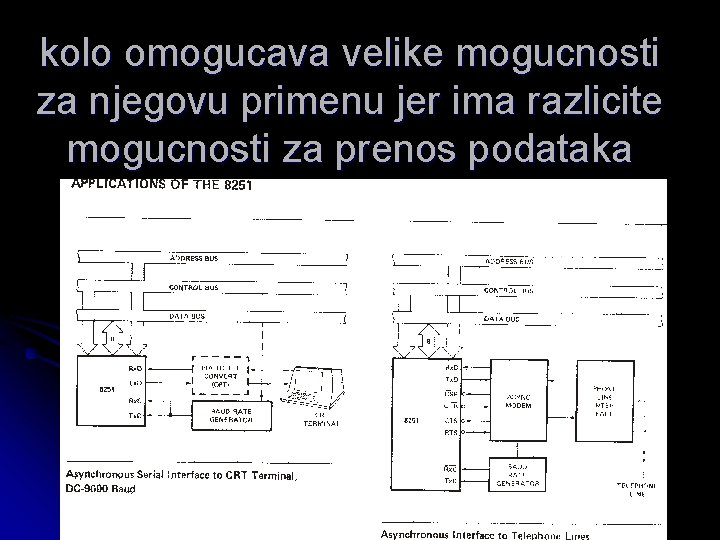

kolo omogucava velike mogucnosti za njegovu primenu jer ima razlicite mogucnosti za prenos podataka

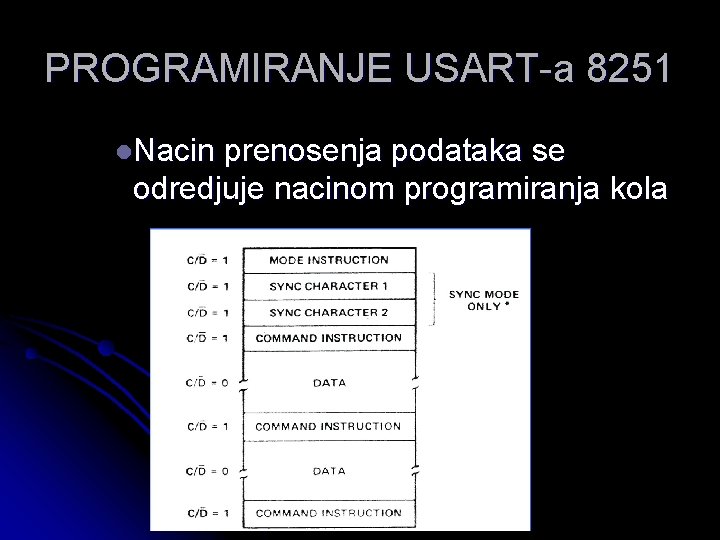

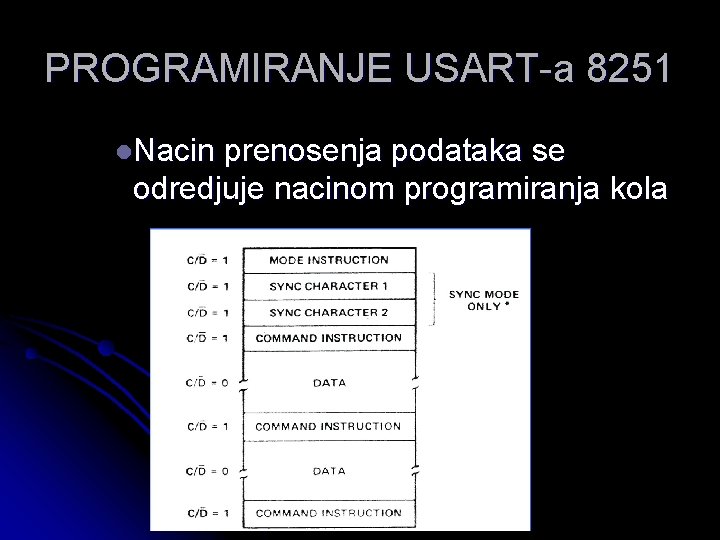

PROGRAMIRANJE USART-a 8251 l. Nacin prenosenja podataka se odredjuje nacinom programiranja kola

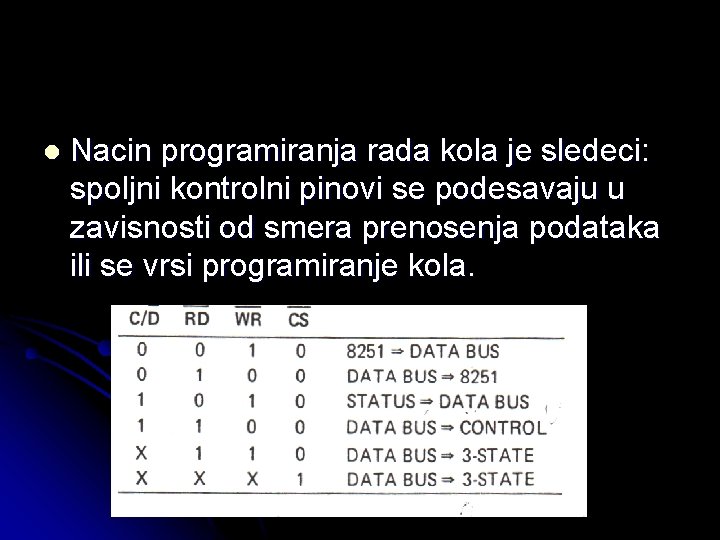

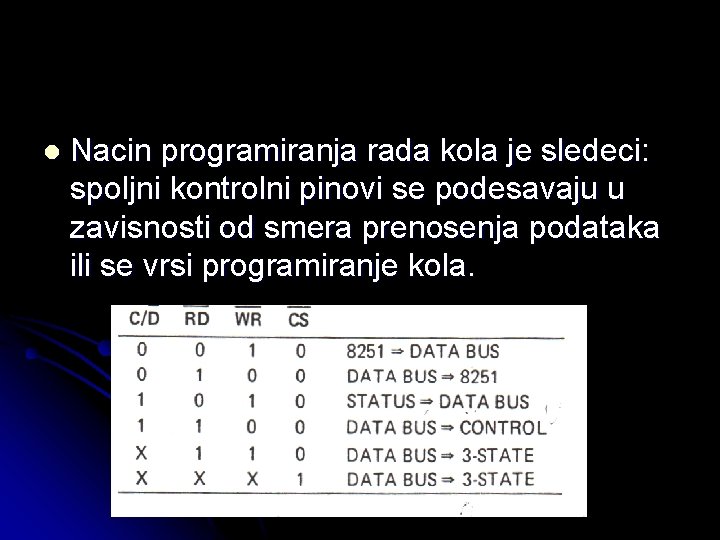

l Nacin programiranja rada kola je sledeci: spoljni kontrolni pinovi se podesavaju u zavisnosti od smera prenosenja podataka ili se vrsi programiranje kola.

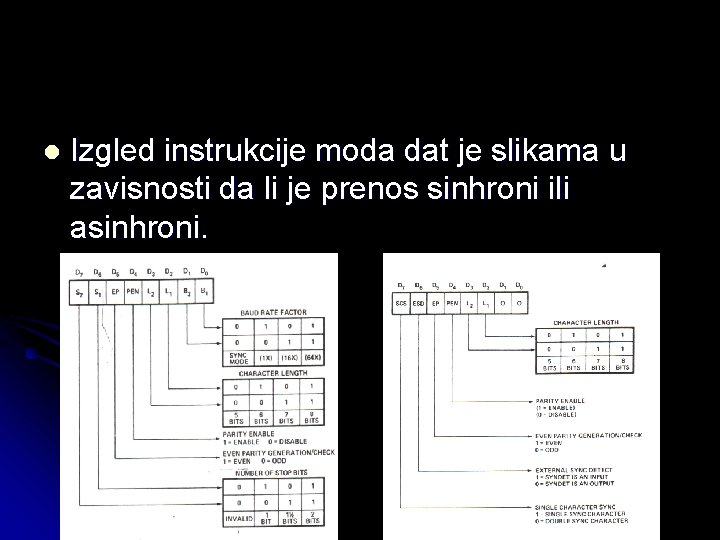

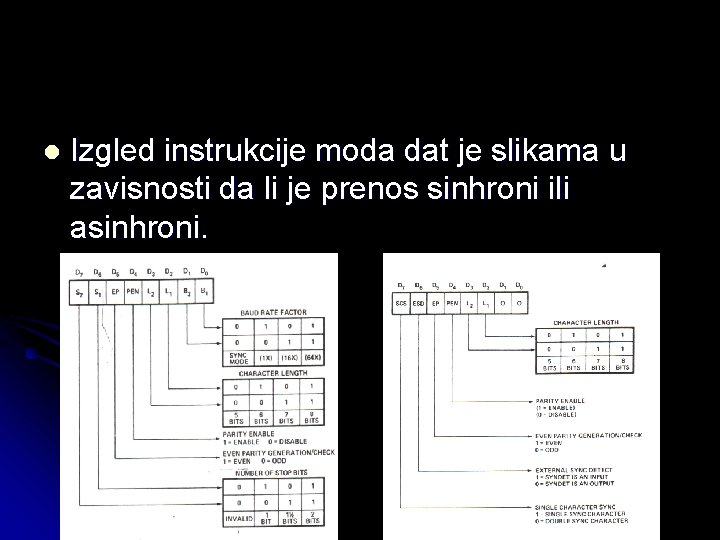

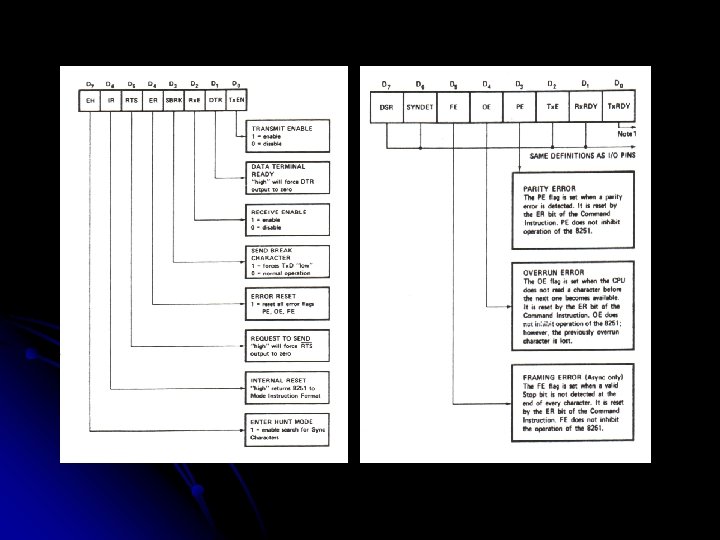

l Izgled instrukcije moda dat je slikama u zavisnosti da li je prenos sinhroni ili asinhroni.

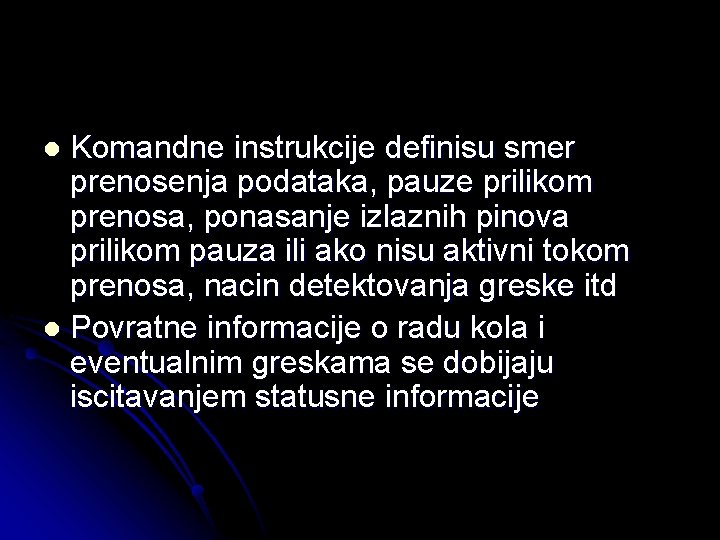

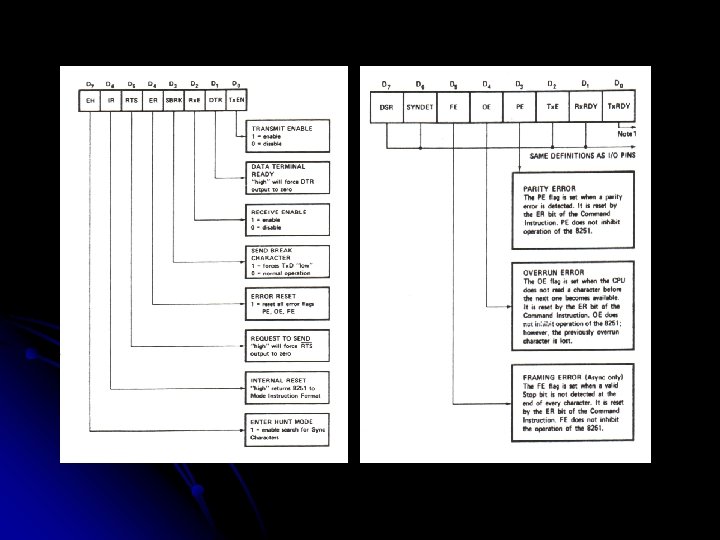

Komandne instrukcije definisu smer prenosenja podataka, pauze prilikom prenosa, ponasanje izlaznih pinova prilikom pauza ili ako nisu aktivni tokom prenosa, nacin detektovanja greske itd l Povratne informacije o radu kola i eventualnim greskama se dobijaju iscitavanjem statusne informacije l

STANDARDNI METODI ZA DETEKCIJU I KOREKCIJU GRESAKA KOD SERIJSKOG PRENOSA l provera kod udaljene povratne petlje l EDAC (error detection and correction) l FCS (forward error correction) l detekcija i korekcija

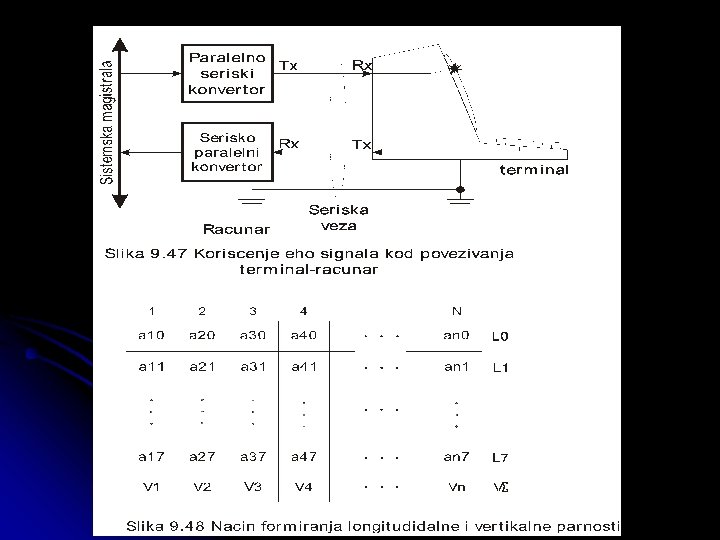

2 D PARNOST – VRC I LRC PARNOST l Kodovi parnosti su: l Parna parnost l Neparna parnost

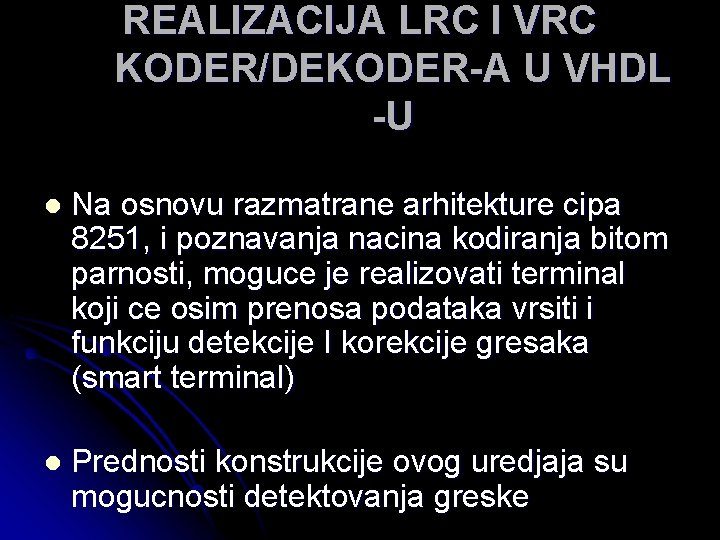

REALIZACIJA LRC I VRC KODER/DEKODER-A U VHDL -U l Na osnovu razmatrane arhitekture cipa 8251, i poznavanja nacina kodiranja bitom parnosti, moguce je realizovati terminal koji ce osim prenosa podataka vrsiti i funkciju detekcije I korekcije gresaka (smart terminal) l Prednosti konstrukcije ovog uredjaja su mogucnosti detektovanja greske

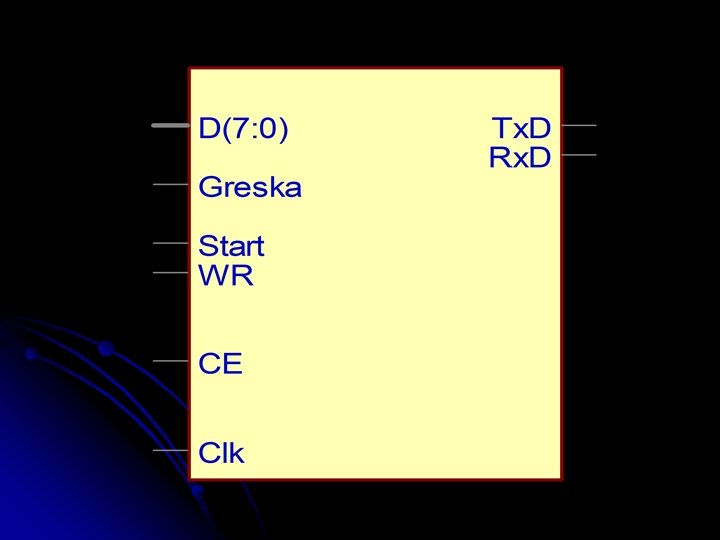

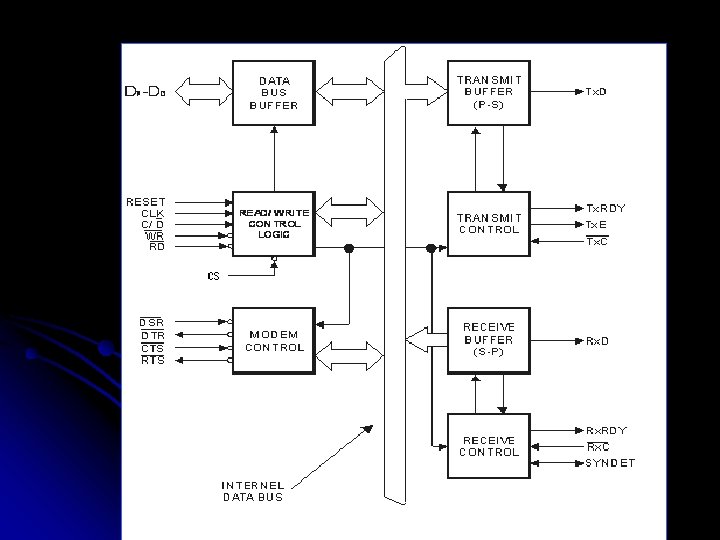

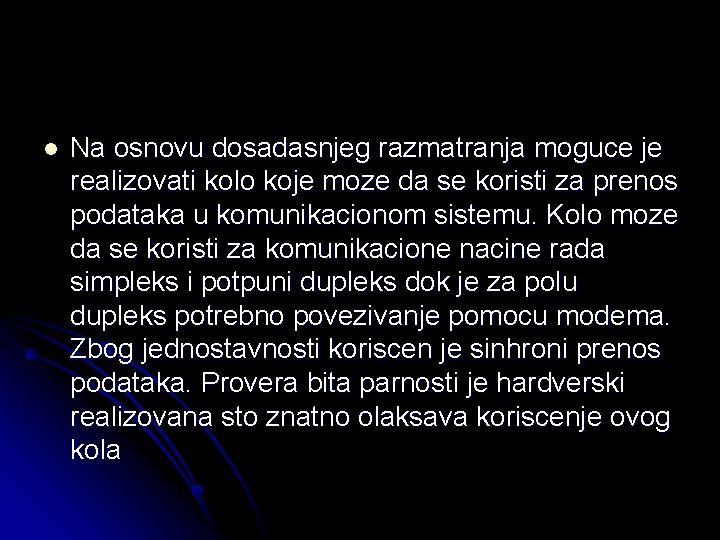

l Na osnovu dosadasnjeg razmatranja moguce je realizovati kolo koje moze da se koristi za prenos podataka u komunikacionom sistemu. Kolo moze da se koristi za komunikacione nacine rada simpleks i potpuni dupleks dok je za polu dupleks potrebno povezivanje pomocu modema. Zbog jednostavnosti koriscen je sinhroni prenos podataka. Provera bita parnosti je hardverski realizovana sto znatno olaksava koriscenje ovog kola

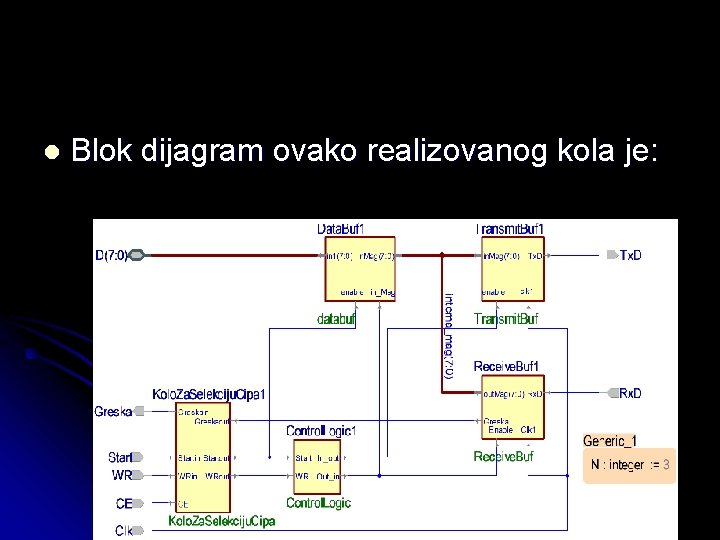

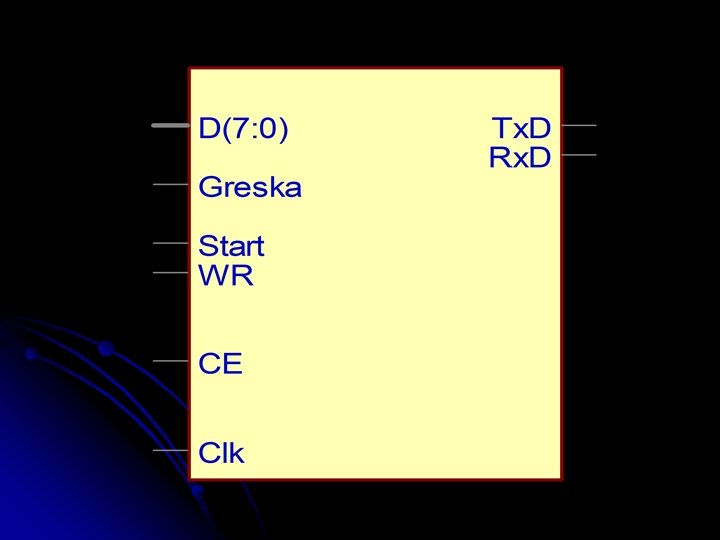

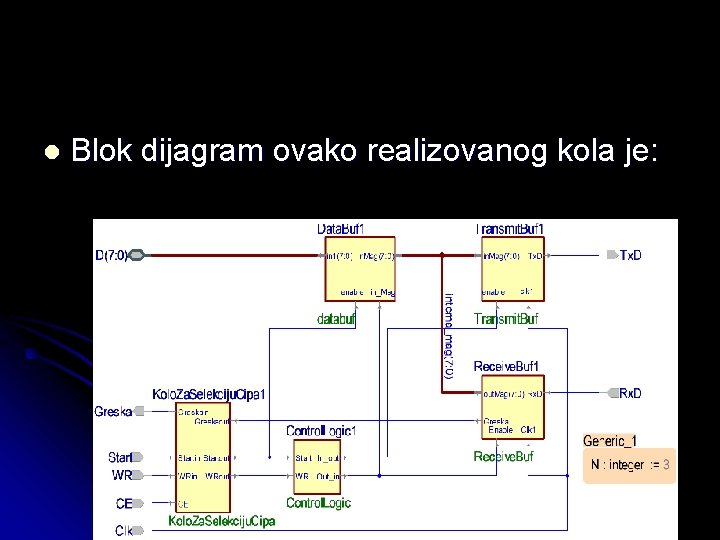

l Blok dijagram ovako realizovanog kola je:

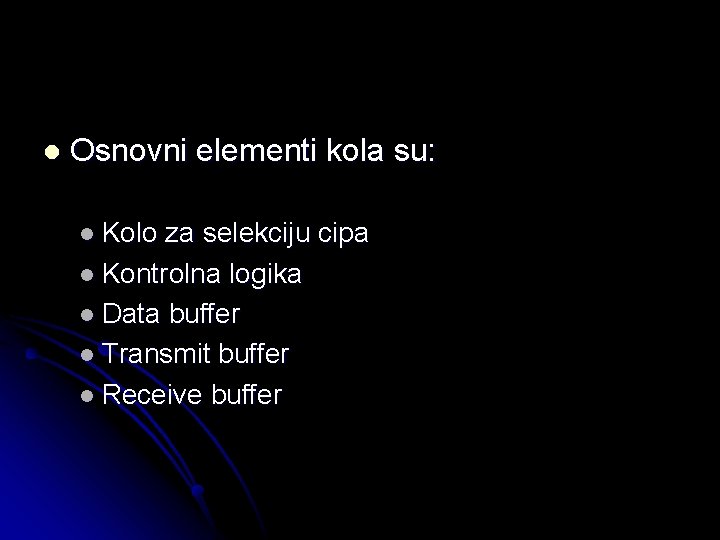

l Osnovni elementi kola su: l Kolo za selekciju cipa l Kontrolna logika l Data buffer l Transmit buffer l Receive buffer

Kolo za selekciju cipa obezbedjuje aktivnost kola l Kontrolna logika ima upravljacku I kontrolnu funkciju l Data buffer obezbedjuje pravilan smer prenosenja podataka izmedju ulazne i interne magistrale l

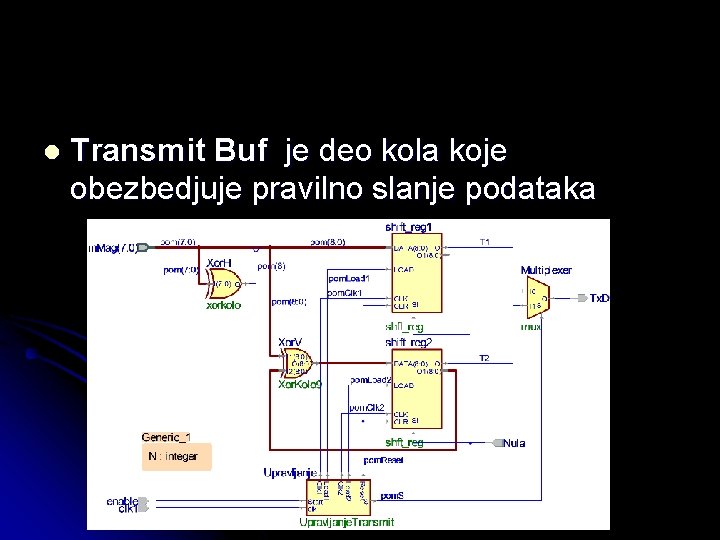

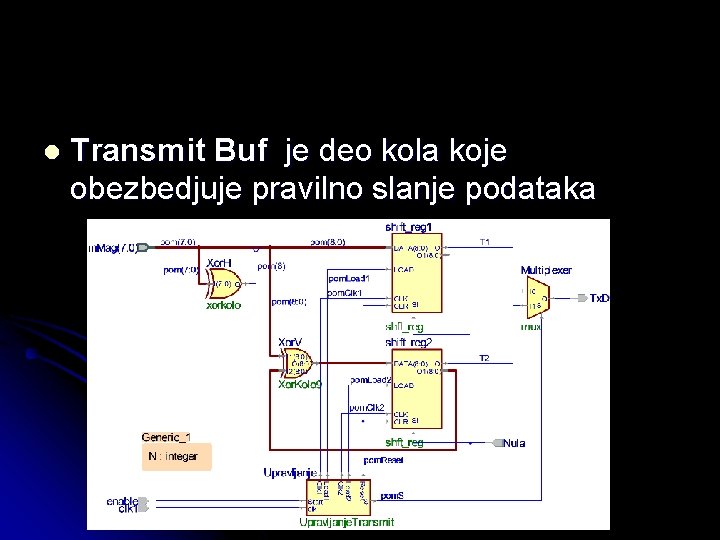

l Transmit Buf je deo kola koje obezbedjuje pravilno slanje podataka

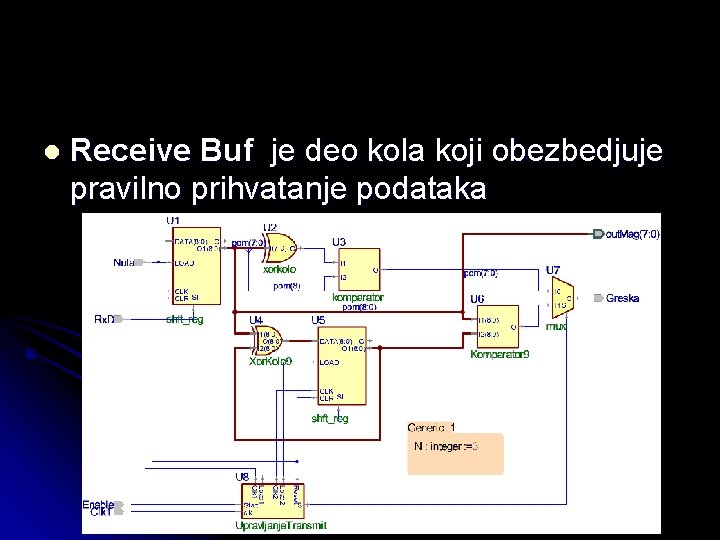

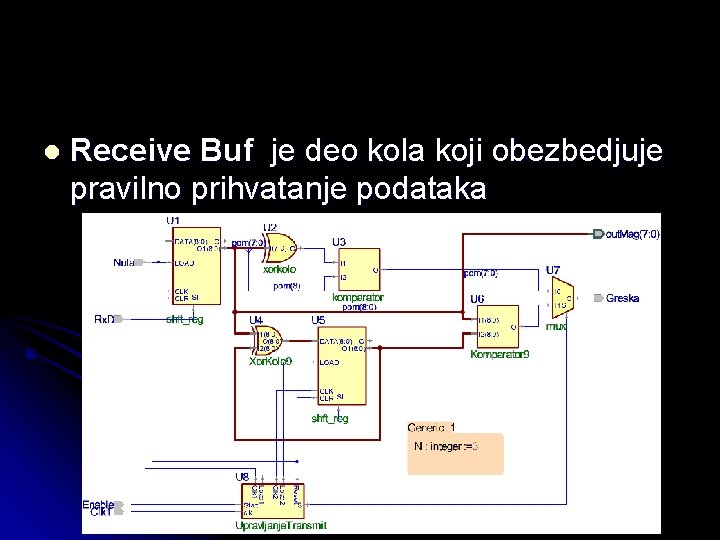

l Receive Buf je deo kola koji obezbedjuje pravilno prihvatanje podataka

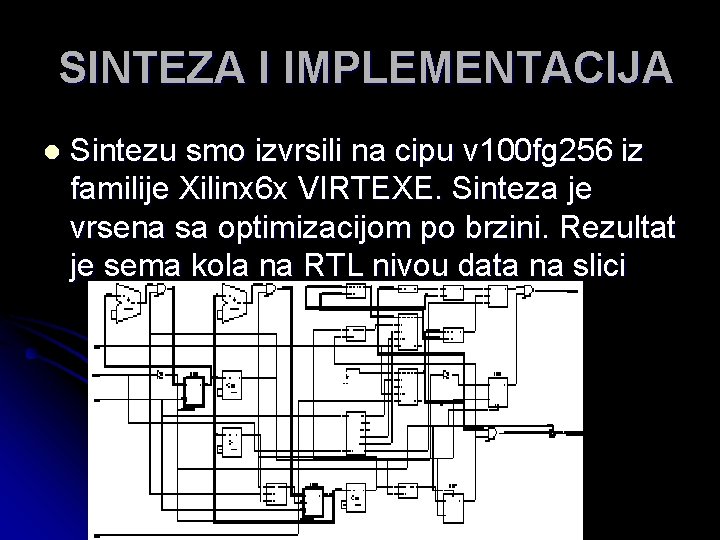

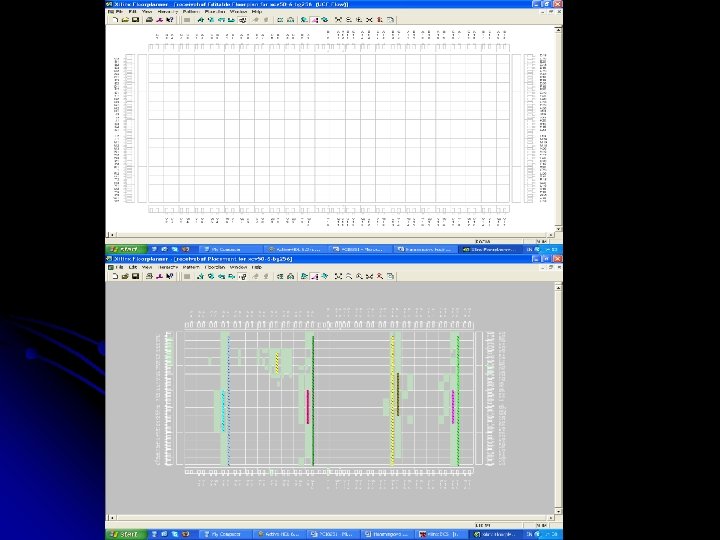

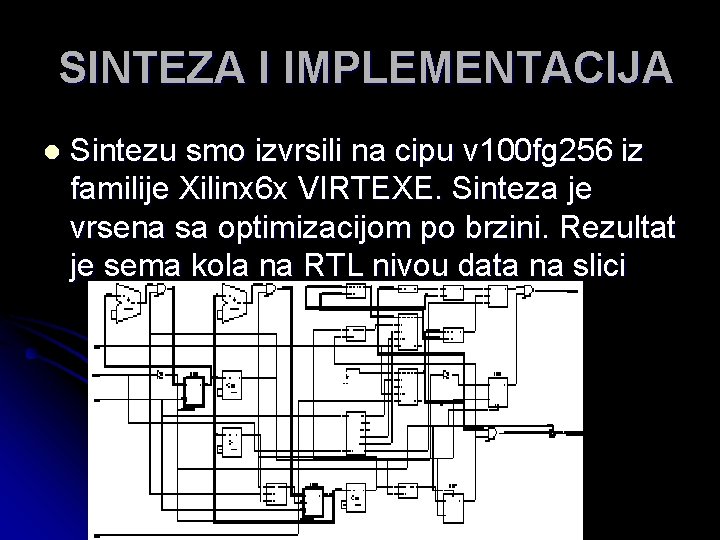

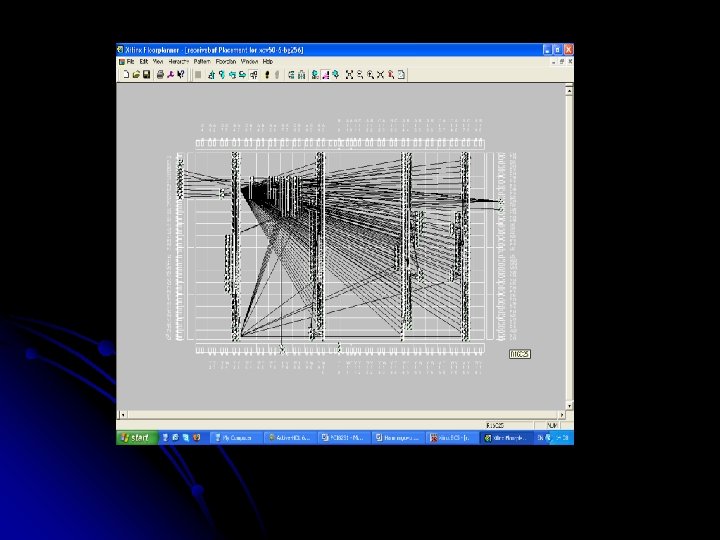

SINTEZA I IMPLEMENTACIJA l Sintezu smo izvrsili na cipu v 100 fg 256 iz familije Xilinx 6 x VIRTEXE. Sinteza je vrsena sa optimizacijom po brzini. Rezultat je sema kola na RTL nivou data na slici

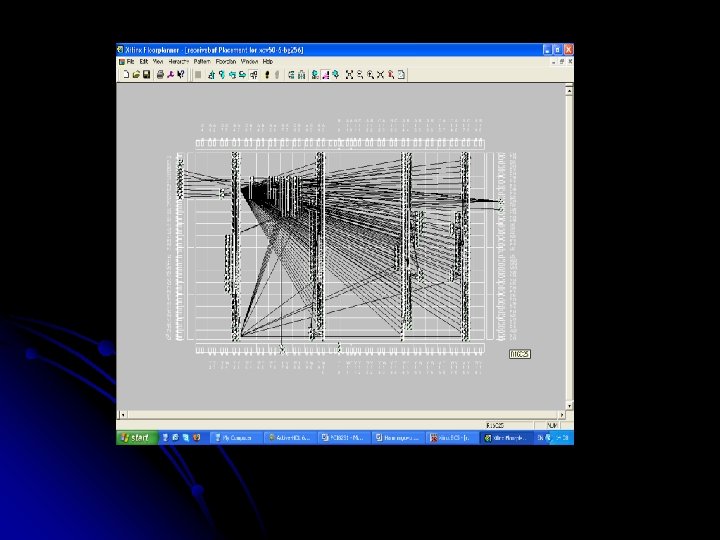

l zauzece resursa na cipu je 22% a propagaciono kasnjenje 5. 615 ns. Izgled strukture cipa zauzetost celija i veze izmedju njih date su na sledecim semama

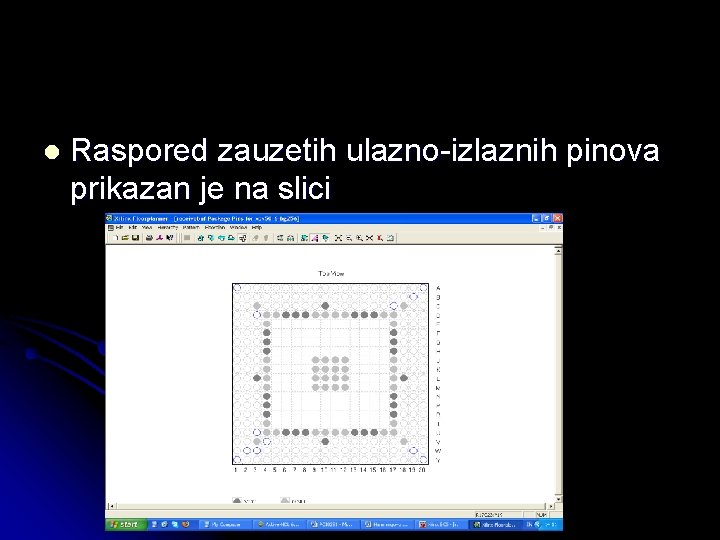

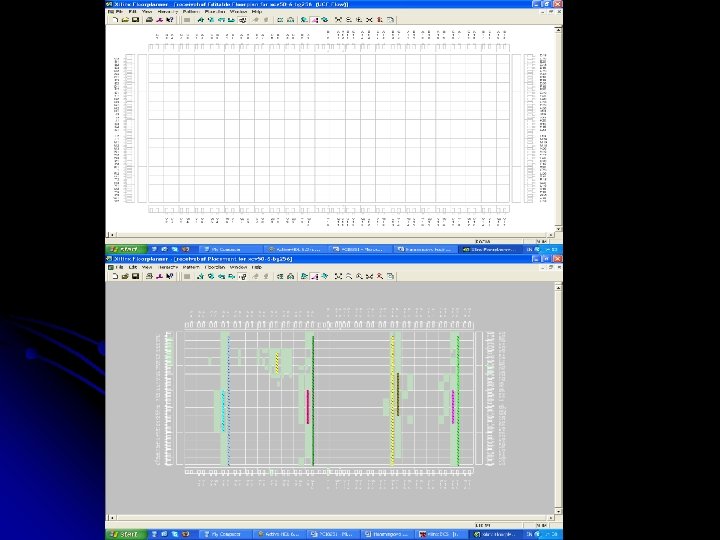

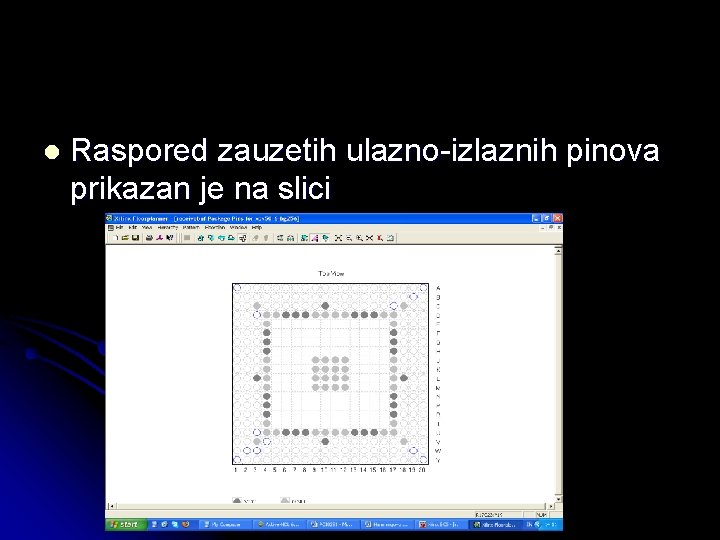

l Raspored zauzetih ulazno-izlaznih pinova prikazan je na slici

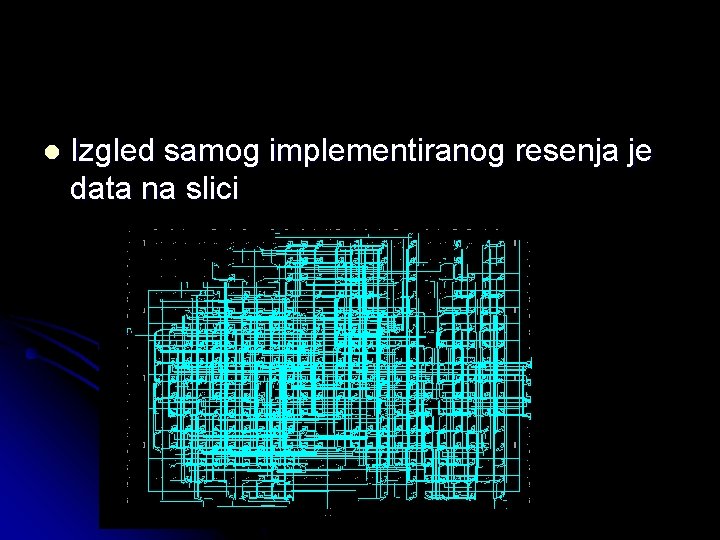

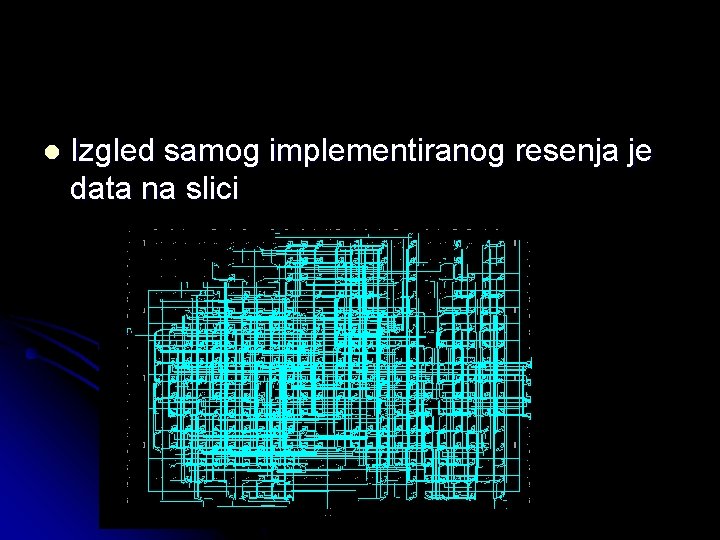

l Izgled samog implementiranog resenja je data na slici

ZAKLJUCAK Ovakvim koder/dekoder-om omogucen je pravilan I pouzdan prenos podataka l Prednost ovakve realizacije je u tome sto je moguce detektovati I korigovati jednu gresku koja se moze javiti u toku prenosa l Ovakva struktura nalazi siroku primenu u praksi l