Lowvoltage techniques Mohammad Sharifkhani Reading Text Book I

Low-voltage techniques Mohammad Sharifkhani

Reading • Text Book I, Chapter 4 • Text Book II, Section 11. 7

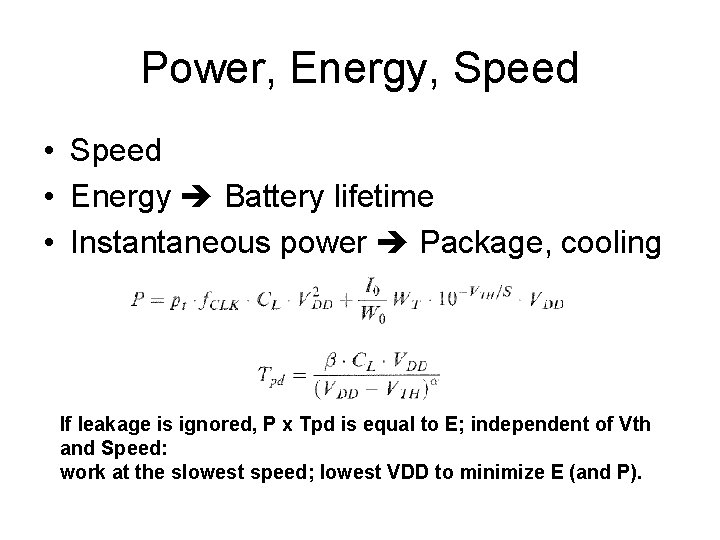

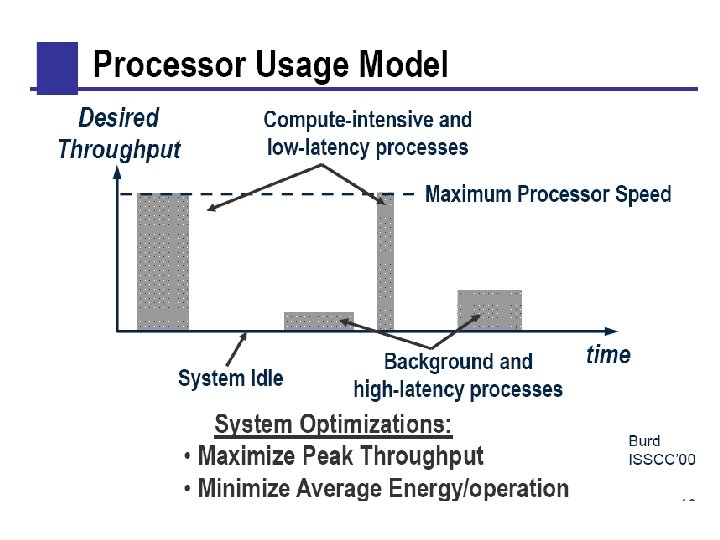

Power, Energy, Speed • Energy Battery lifetime • Instantaneous power Package, cooling If leakage is ignored, P x Tpd is equal to E; independent of Vth and Speed: work at the slowest speed; lowest VDD to minimize E (and P).

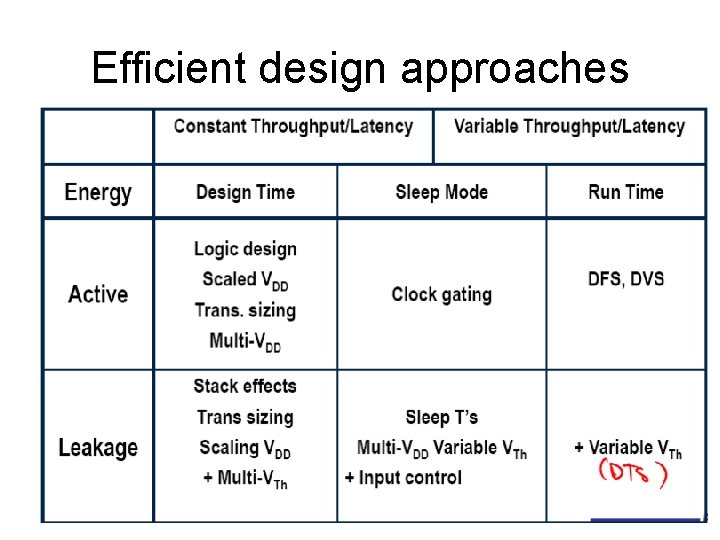

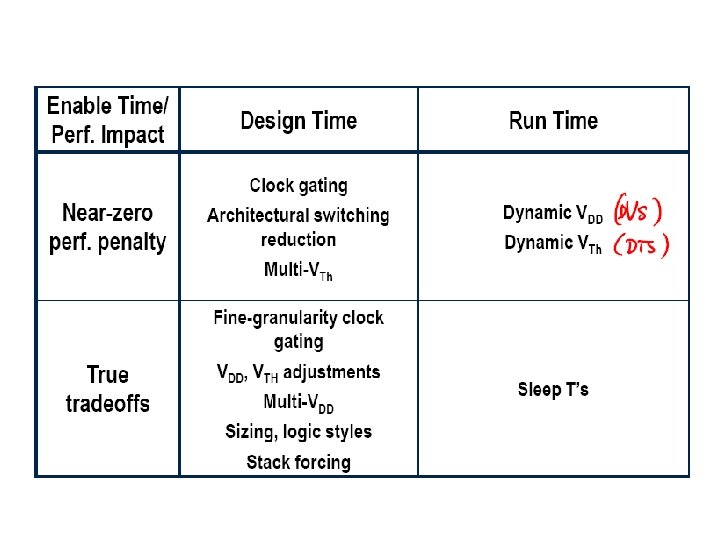

Efficient design approaches

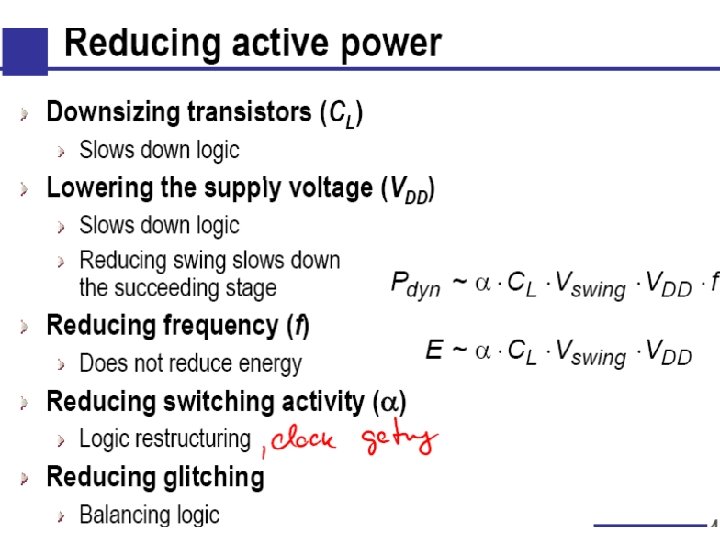

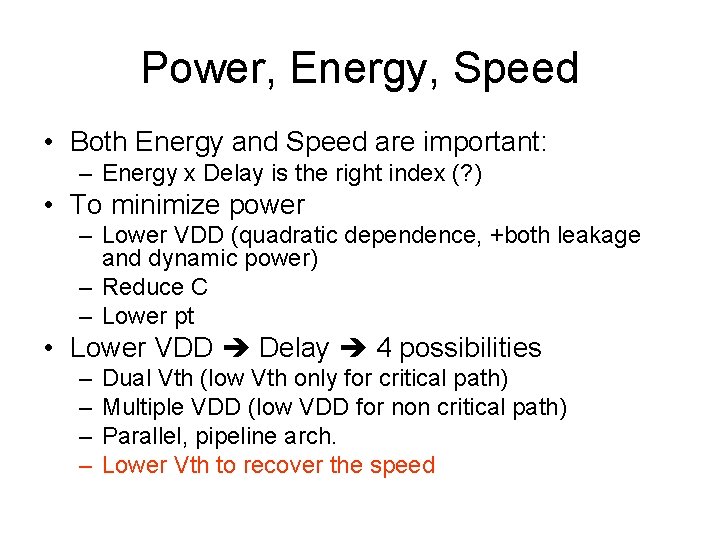

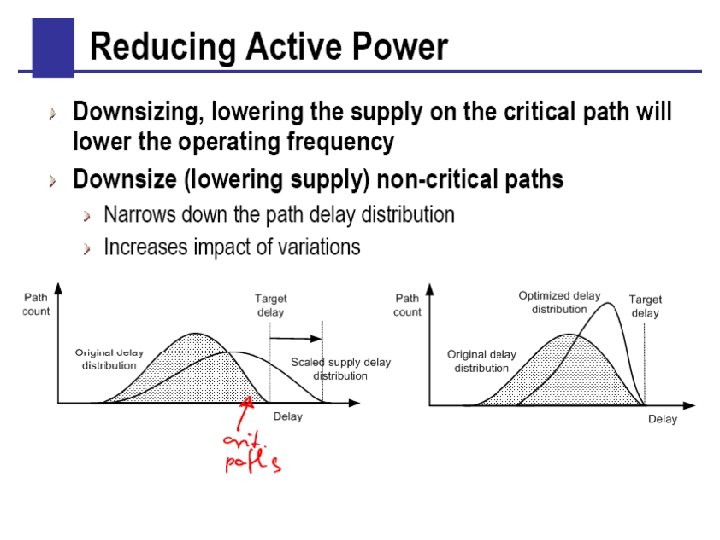

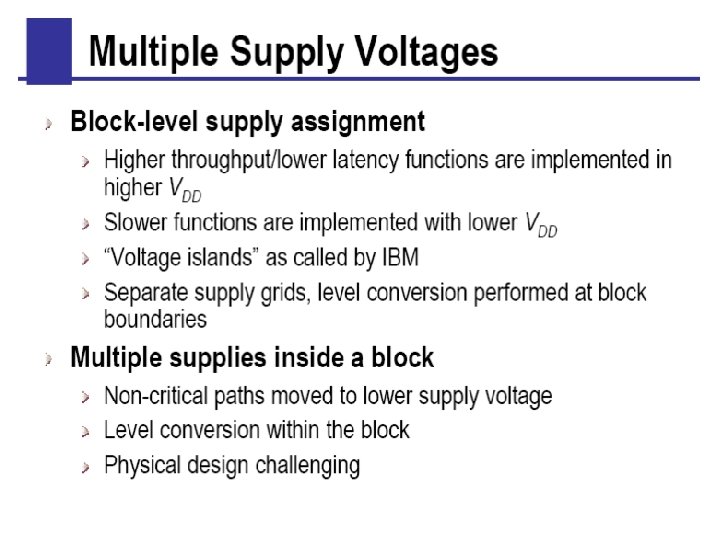

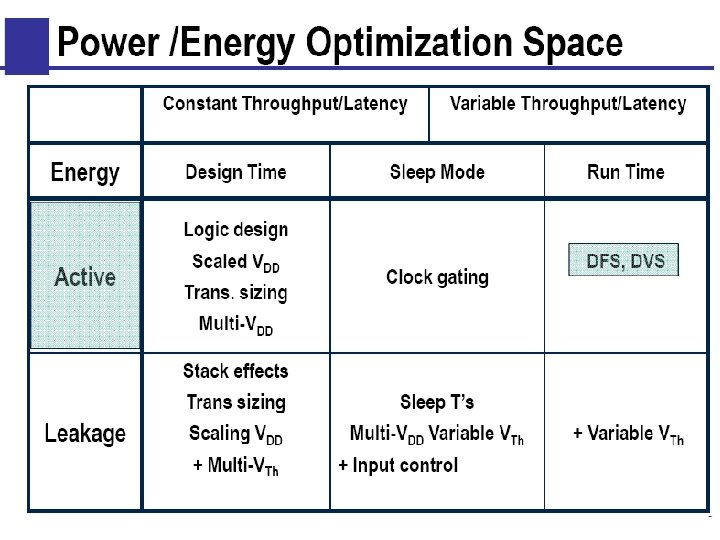

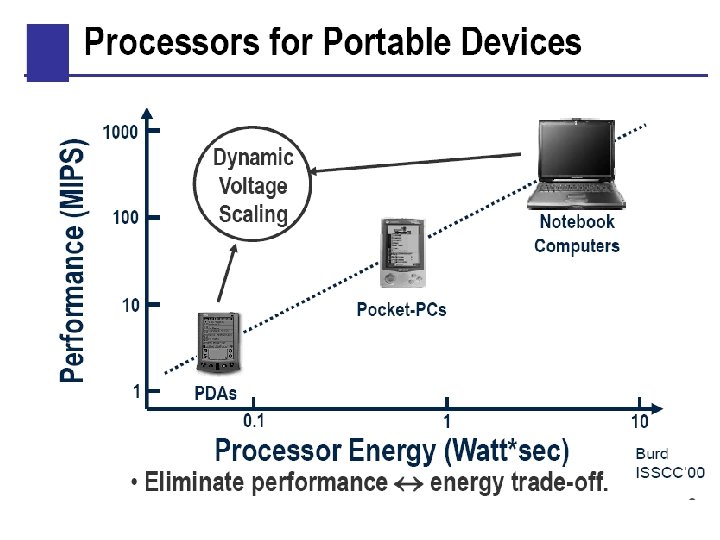

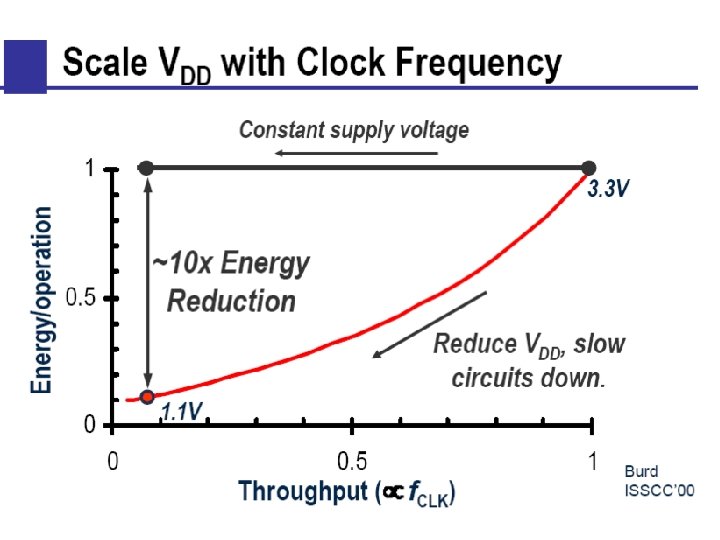

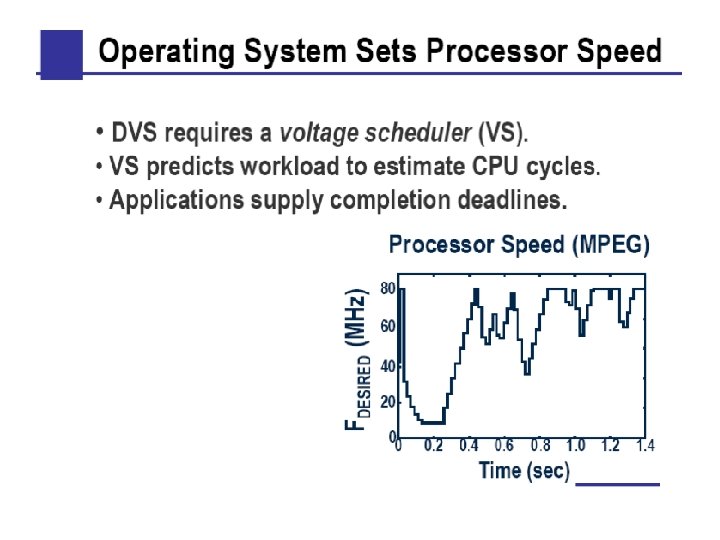

Power, Energy, Speed • Both Energy and Speed are important: – Energy x Delay is the right index (? ) • To minimize power – Lower VDD (quadratic dependence, +both leakage and dynamic power) – Reduce C – Lower pt • Lower VDD Delay 4 possibilities – – Dual Vth (low Vth only for critical path) Multiple VDD (low VDD for non critical path) Parallel, pipeline arch. Lower Vth to recover the speed

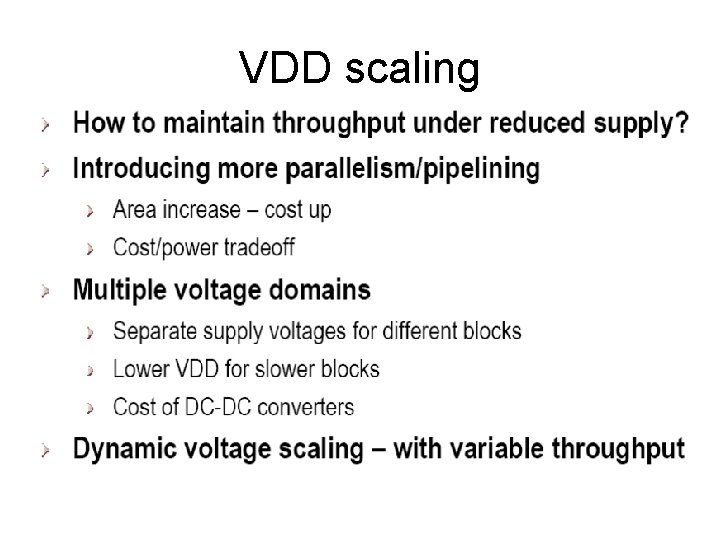

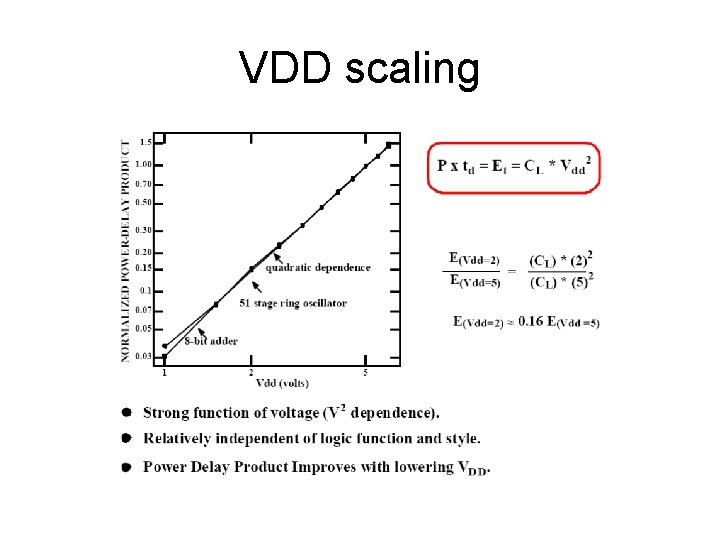

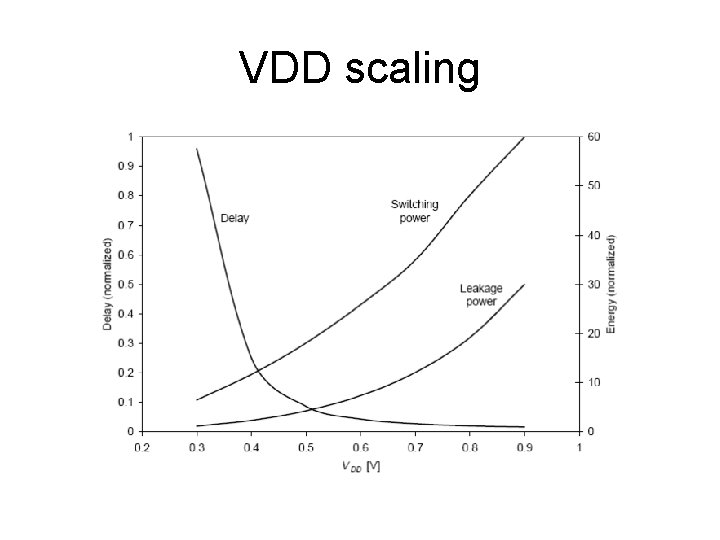

VDD scaling

VDD scaling

VDD scaling

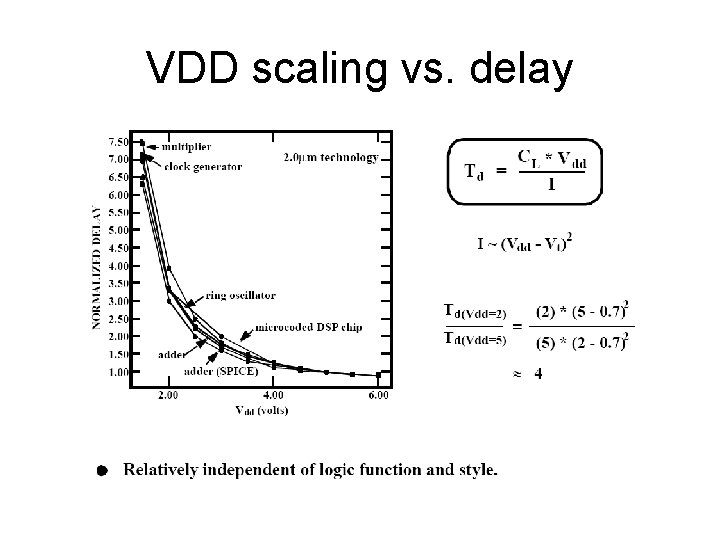

VDD scaling vs. delay

Processing options

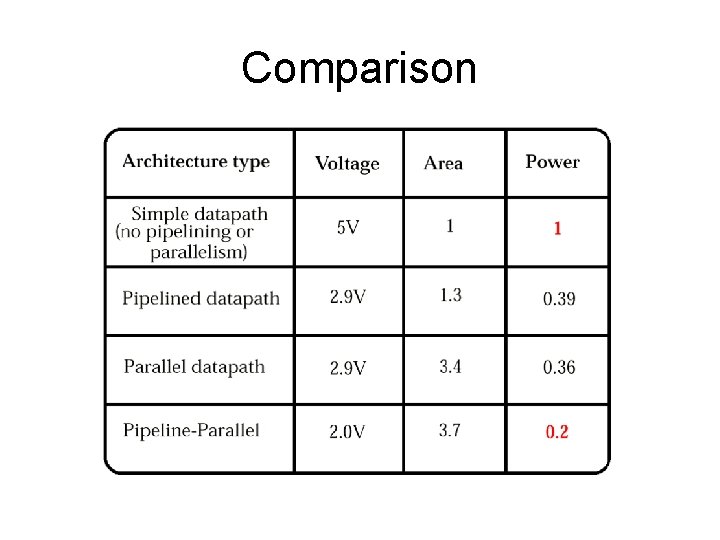

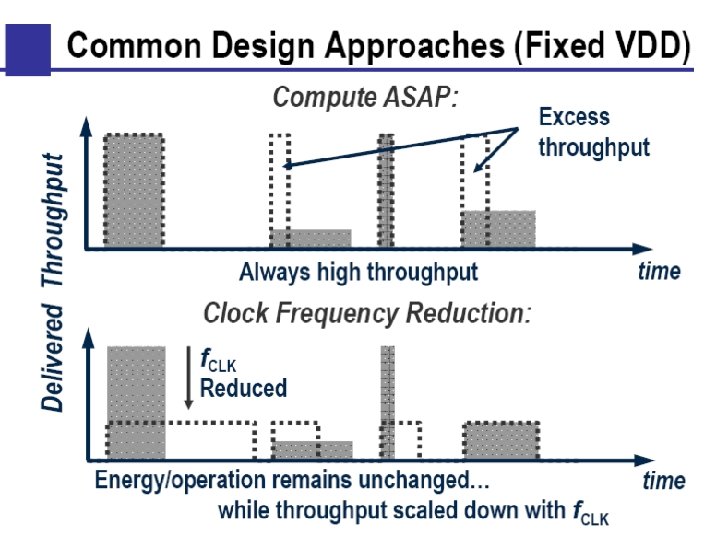

Architecture Trade-off for Fixed-rate Processing Reference Datapath

Parallel data path

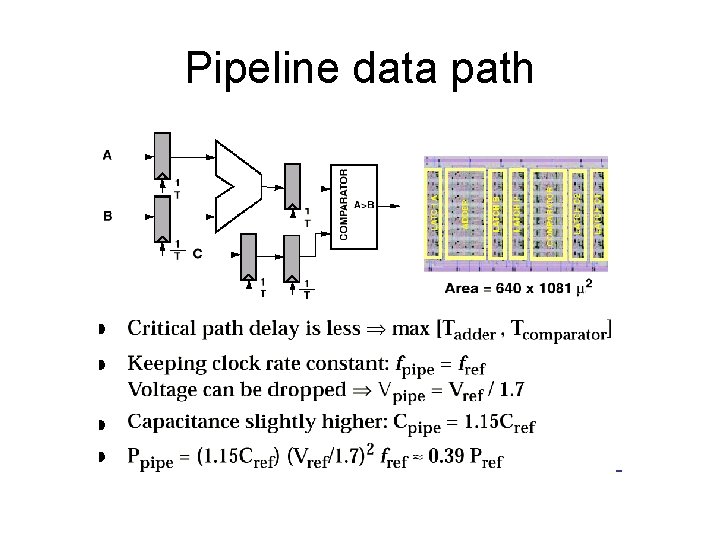

Pipeline data path

Comparison

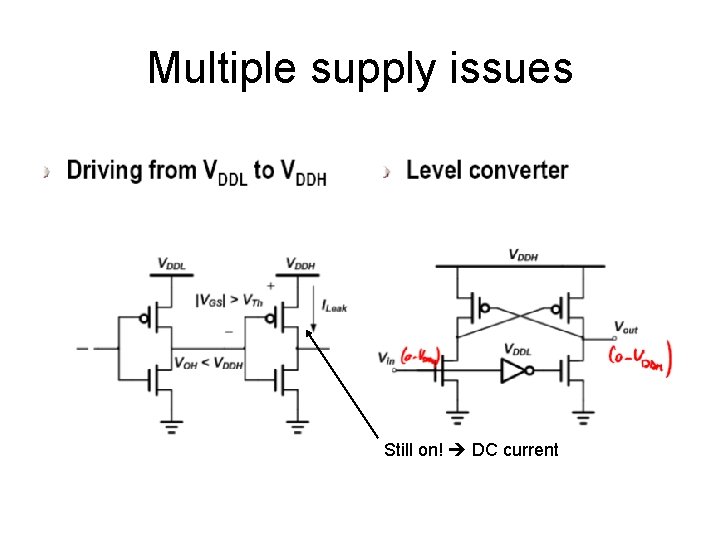

Multiple supply issues Still on! DC current

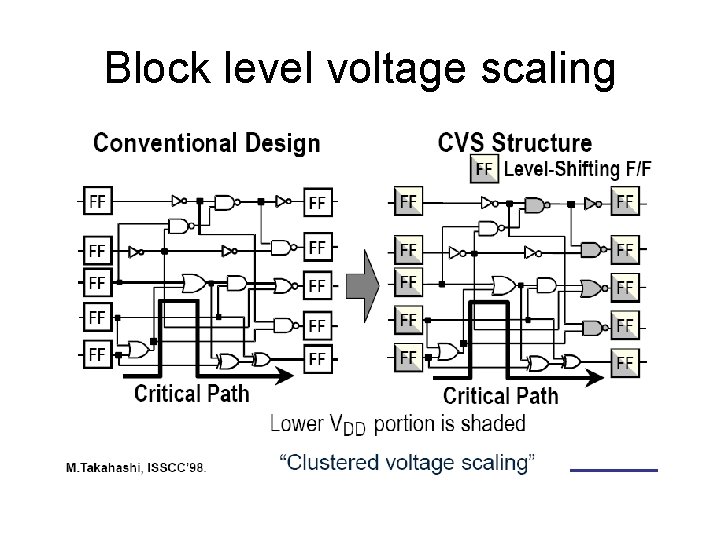

Block level voltage scaling

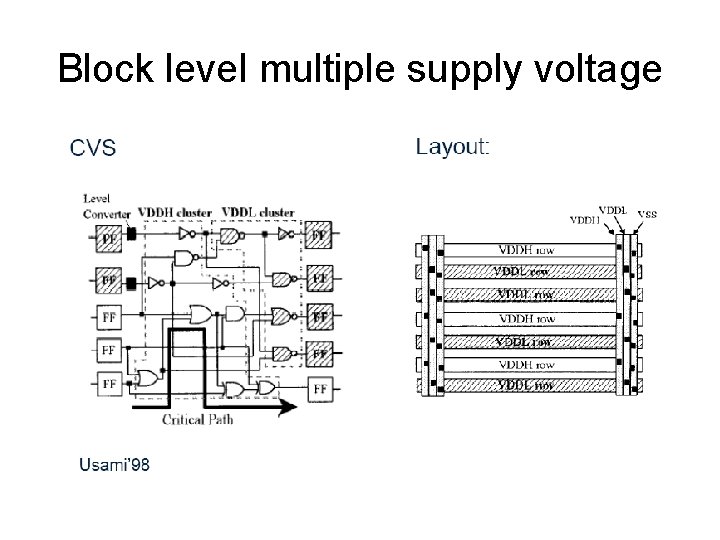

Block level multiple supply voltage

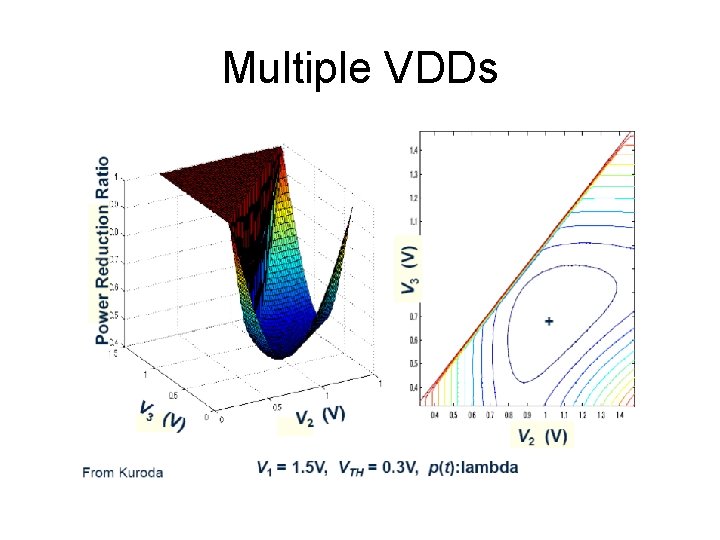

Multiple VDDs

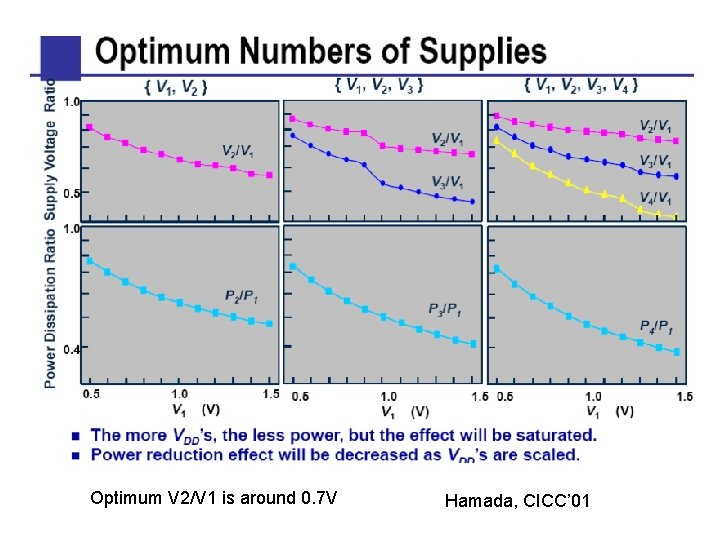

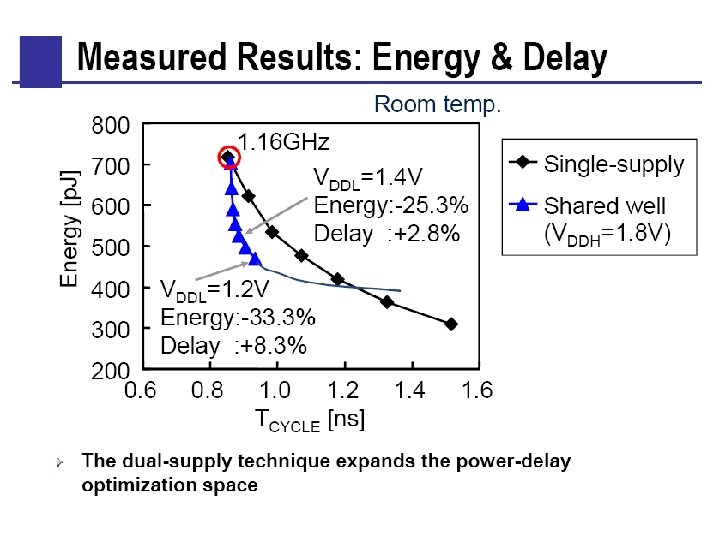

Optimum V 2/V 1 is around 0. 7 V Hamada, CICC’ 01

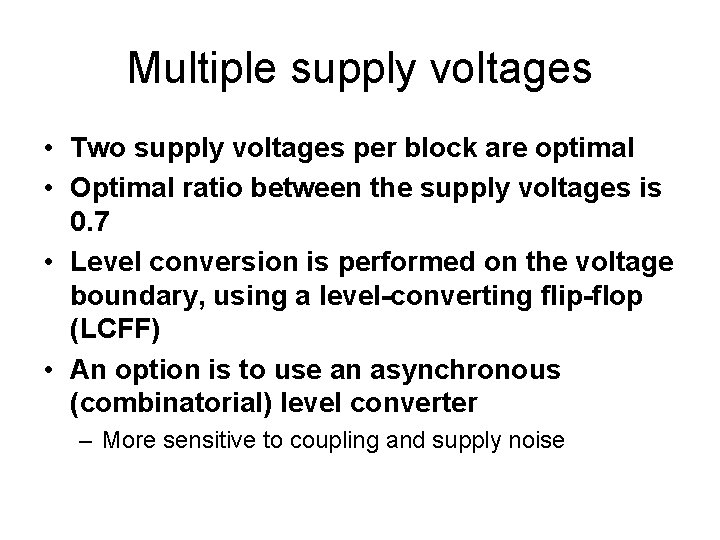

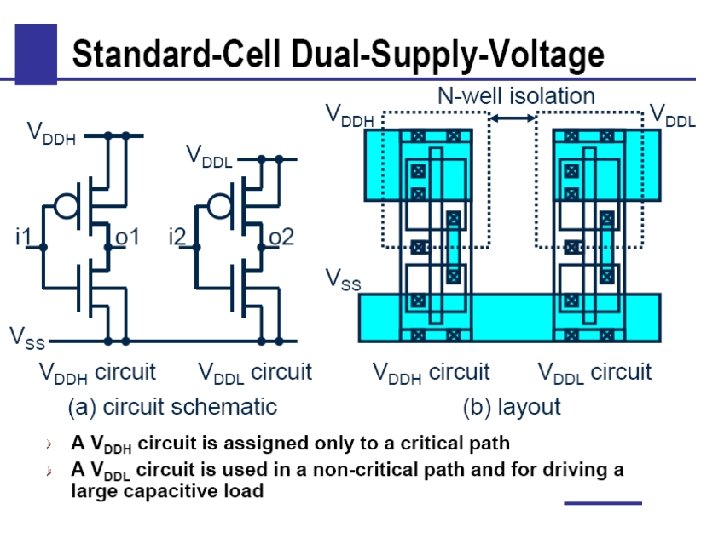

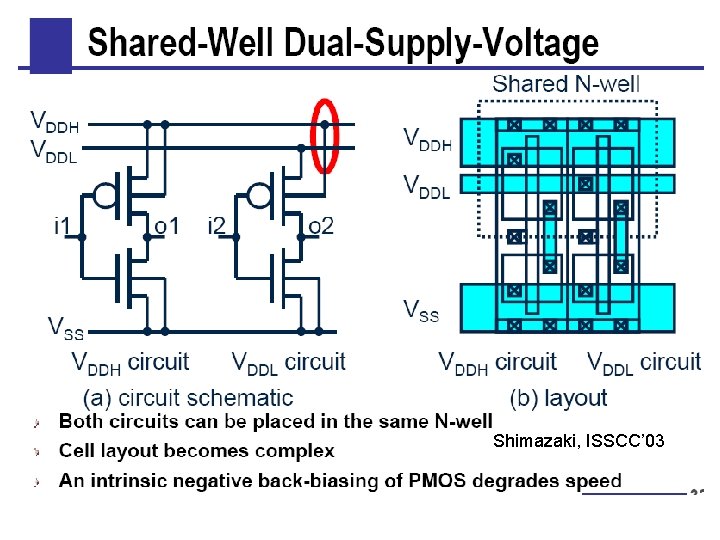

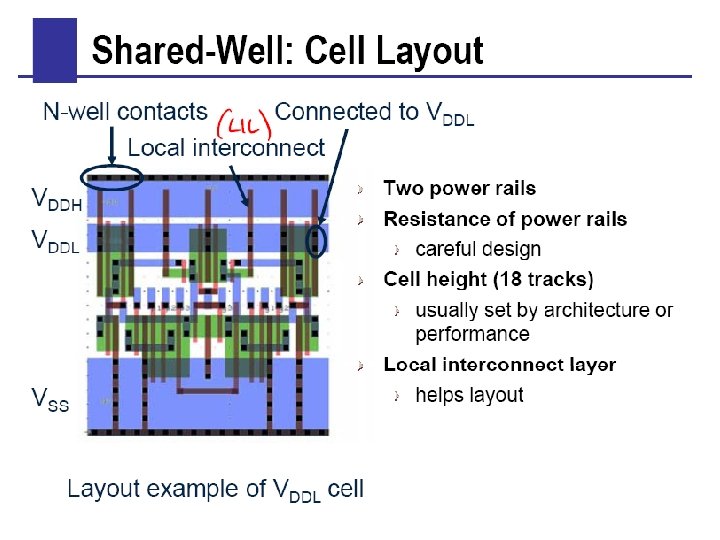

Multiple supply voltages • Two supply voltages per block are optimal • Optimal ratio between the supply voltages is 0. 7 • Level conversion is performed on the voltage boundary, using a level-converting flip-flop (LCFF) • An option is to use an asynchronous (combinatorial) level converter – More sensitive to coupling and supply noise

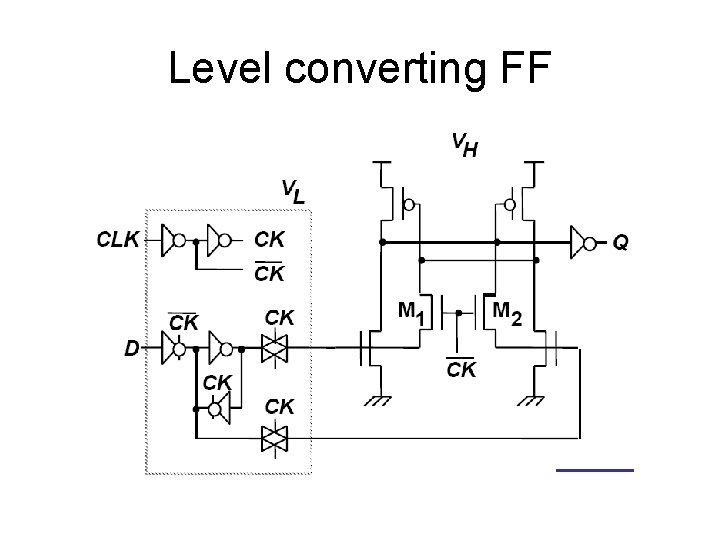

Level converting FF

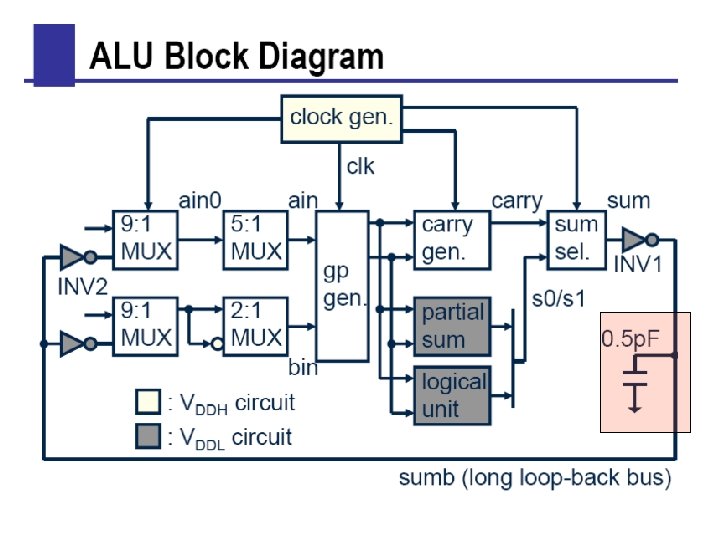

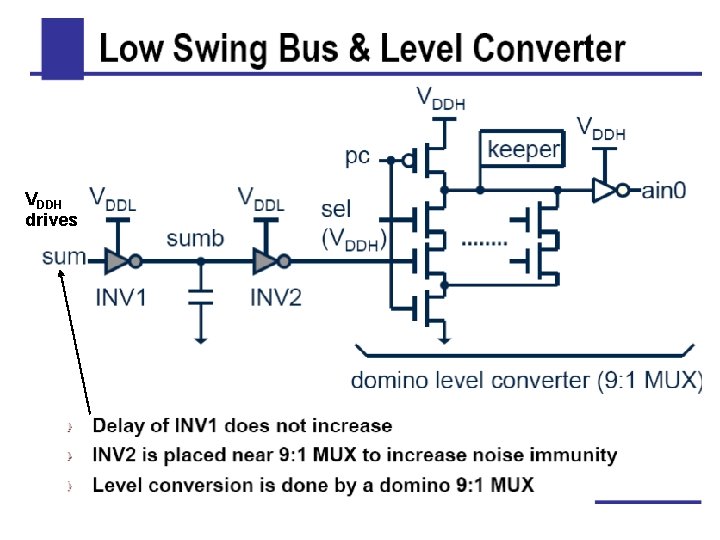

Shimazaki, ISSCC’ 03

VDDH drives

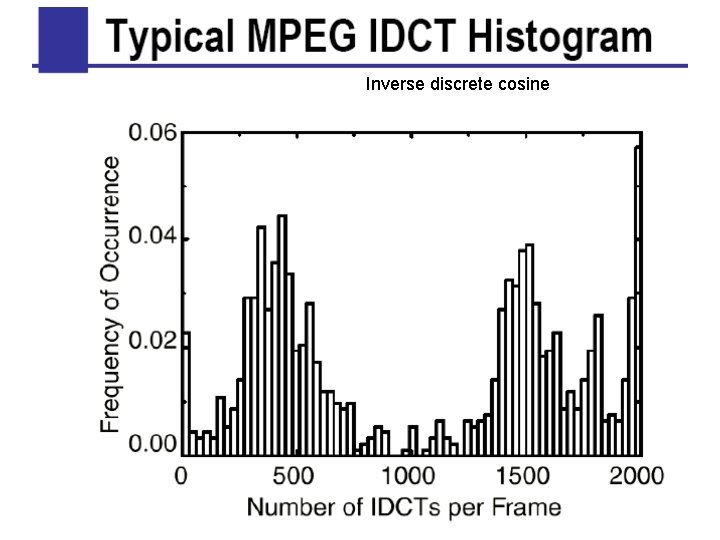

Inverse discrete cosine

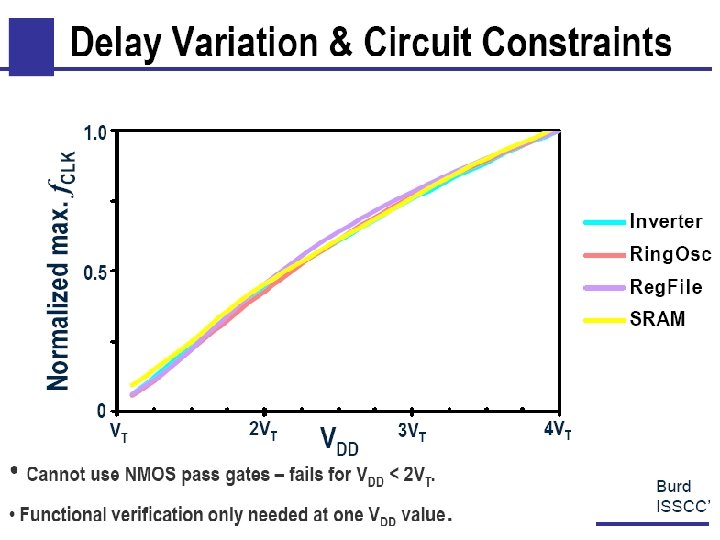

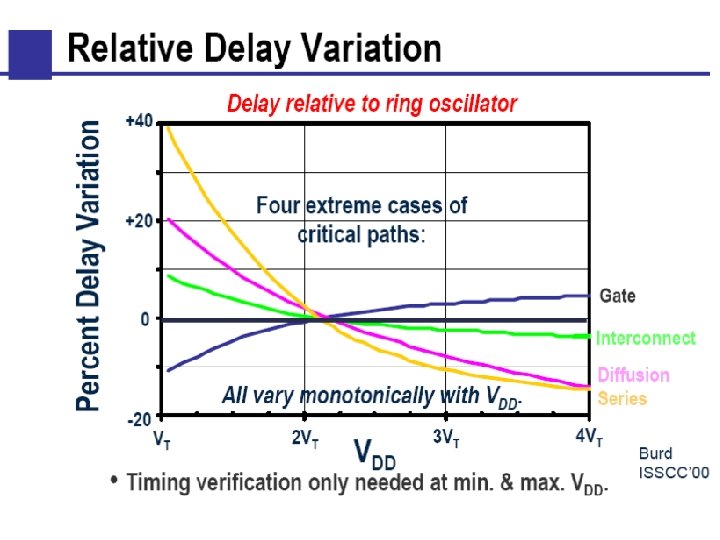

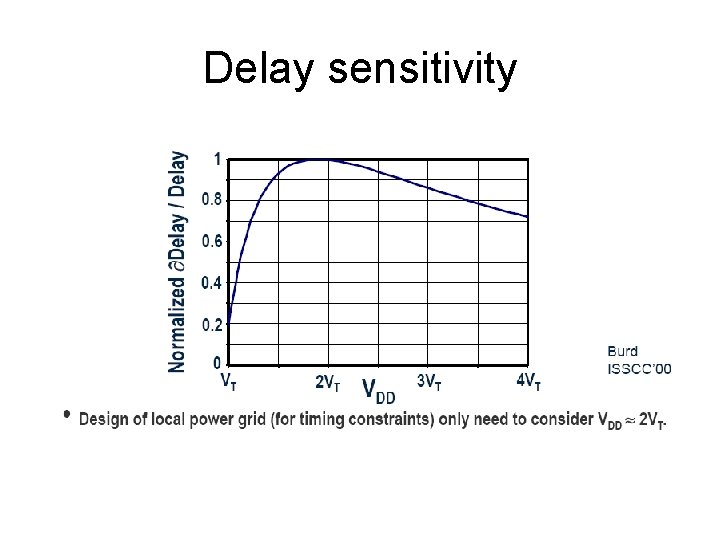

Delay sensitivity

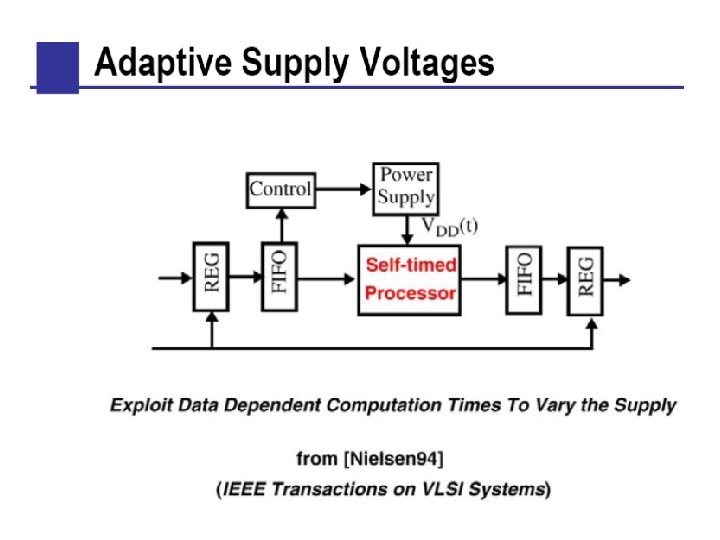

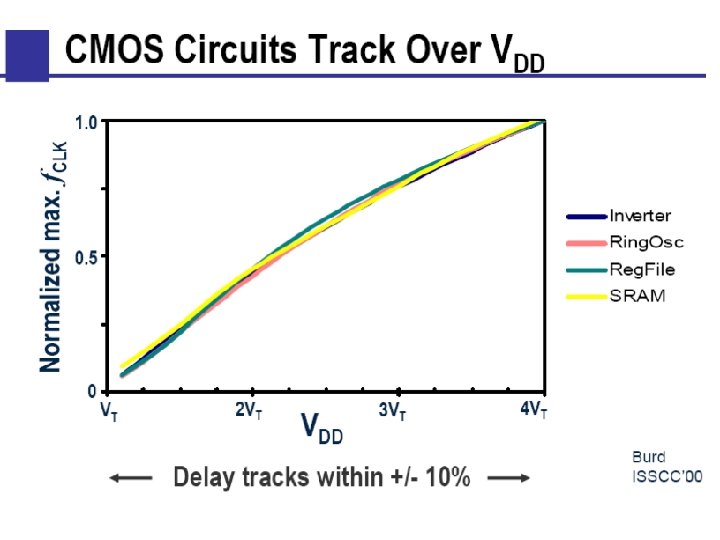

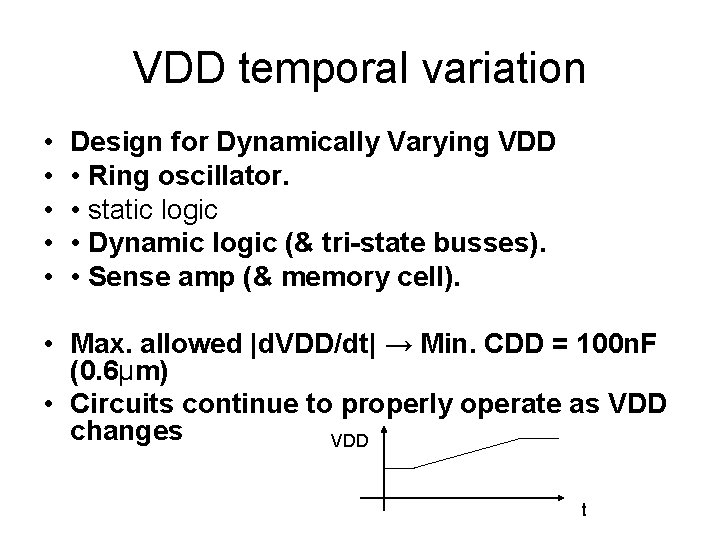

VDD temporal variation • • • Design for Dynamically Varying VDD • Ring oscillator. • static logic • Dynamic logic (& tri-state busses). • Sense amp (& memory cell). • Max. allowed |d. VDD/dt| → Min. CDD = 100 n. F (0. 6μm) • Circuits continue to properly operate as VDD changes VDD t

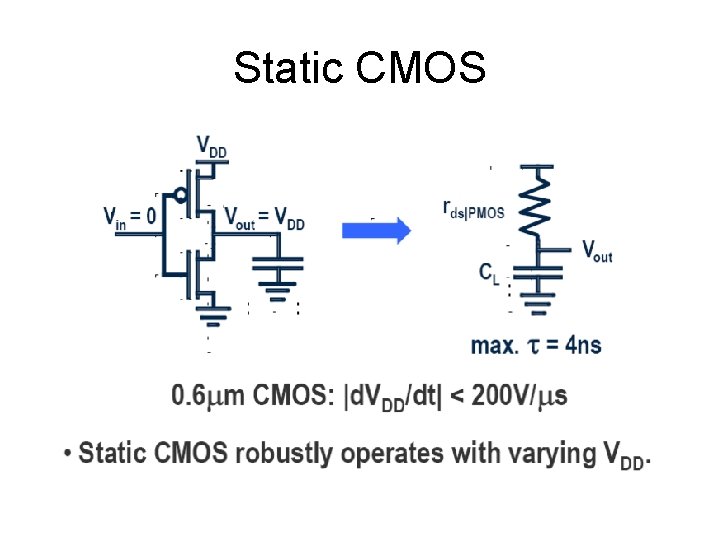

Static CMOS

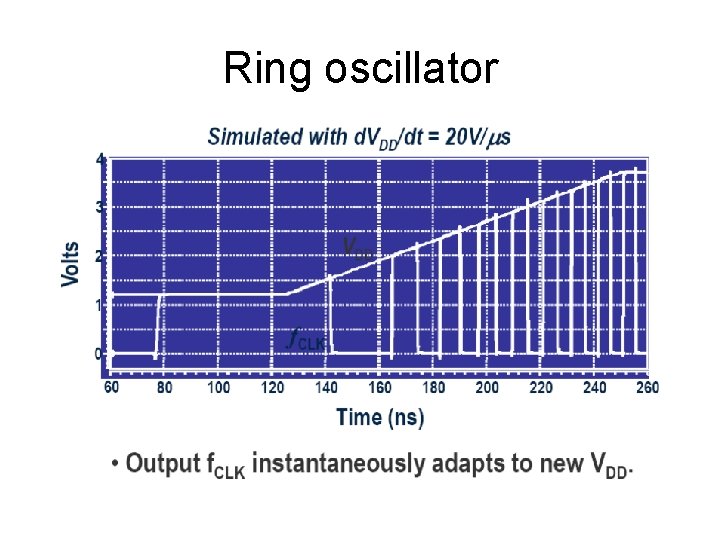

Ring oscillator

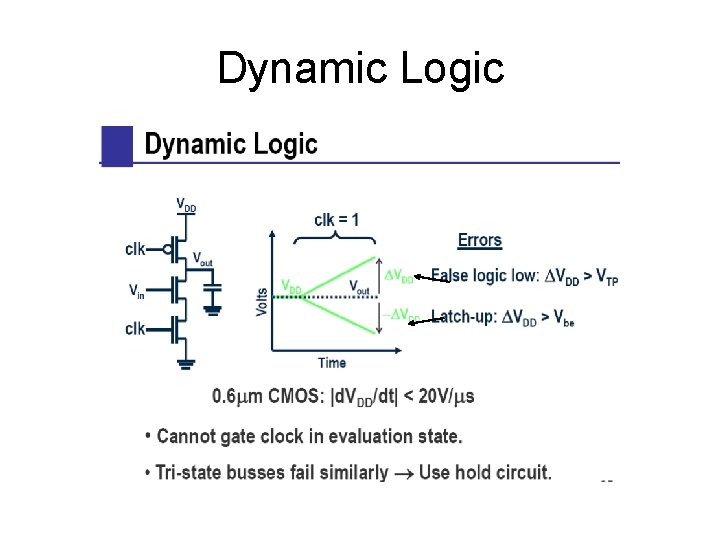

Dynamic Logic

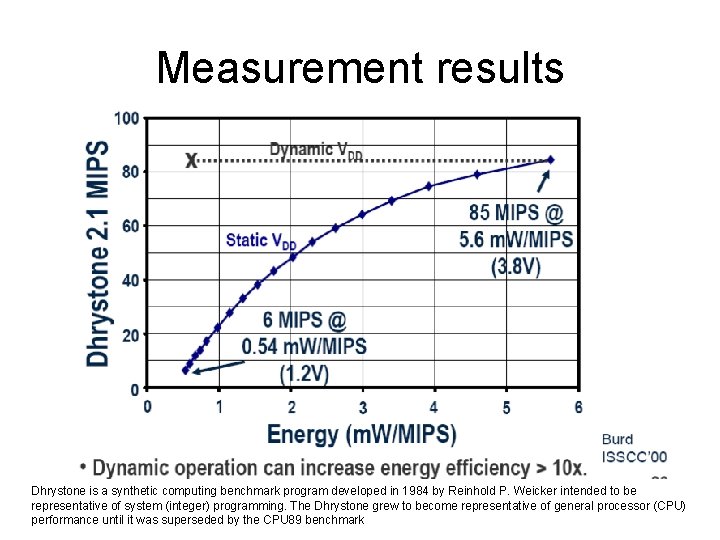

Measurement results Dhrystone is a synthetic computing benchmark program developed in 1984 by Reinhold P. Weicker intended to be representative of system (integer) programming. The Dhrystone grew to become representative of general processor (CPU) performance until it was superseded by the CPU 89 benchmark

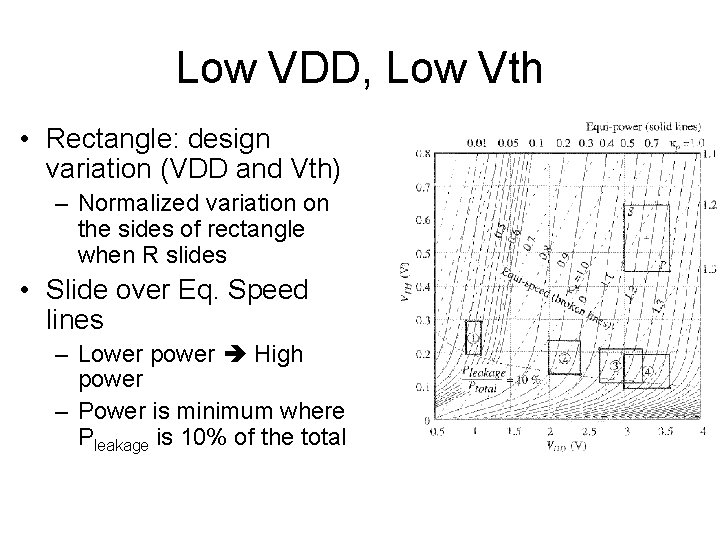

Low VDD, Low Vth • Rectangle: design variation (VDD and Vth) – Normalized variation on the sides of rectangle when R slides • Slide over Eq. Speed lines – Lower power High power – Power is minimum where Pleakage is 10% of the total

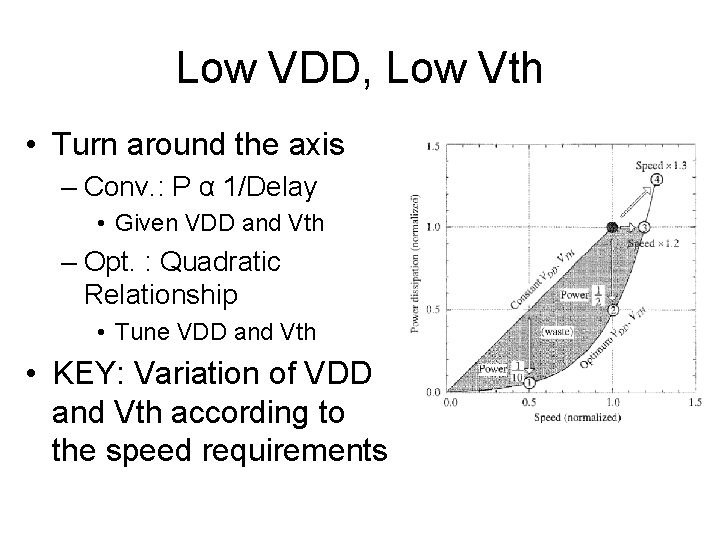

Low VDD, Low Vth • Turn around the axis – Conv. : P α 1/Delay • Given VDD and Vth – Opt. : Quadratic Relationship • Tune VDD and Vth • KEY: Variation of VDD and Vth according to the speed requirements

3 Challenges • High standby current in low Vth • IDDQ testing failure • Degradation of worst case speed due to Vth variation @ low Vth – Vth scaling to keep delay constant: for 3 V => 2 V change 25% Vth reduction is needed

- Slides: 57