LowPower IC Design Ch 4 CircuitLevel LowPower Design

- Slides: 18

Low-Power IC Design Ch. 4 Circuit-Level Low-Power Design Tsung-Chu Huang Dep’t of Electronic Eng. , Nat’l Changhua Univ. Spring 2007 Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 1 NCUE EDAT

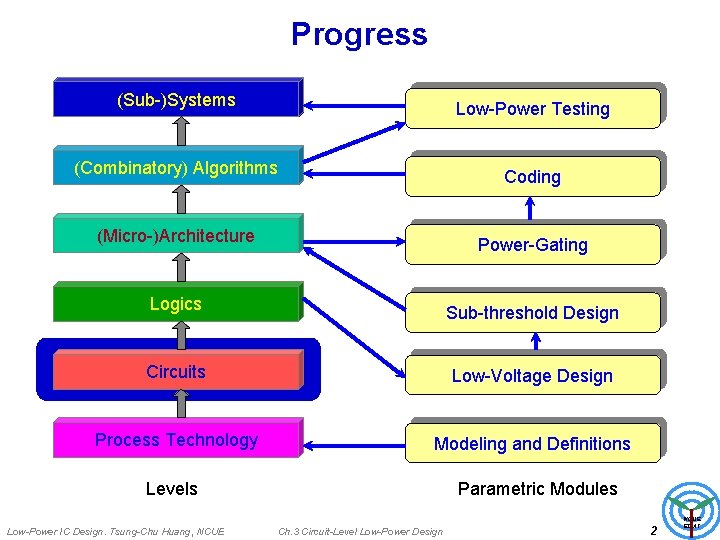

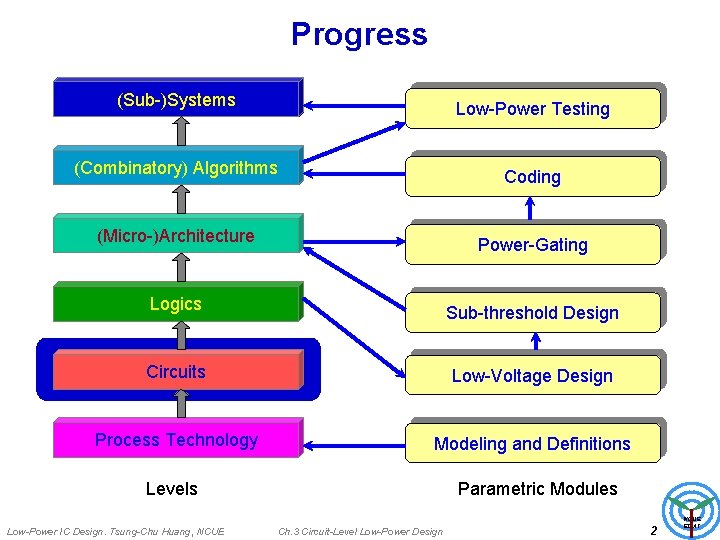

Progress (Sub-)Systems Low-Power Testing (Combinatory) Algorithms Coding (Micro-)Architecture Power-Gating Logics Sub-threshold Design Circuits Low-Voltage Design Process Technology Modeling and Definitions Levels Parametric Modules Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 2 NCUE EDAT

Circuit-Level Power Reduction • Logic Structures/Styles • Transistor-Level – Transistor Sizing – Transistor Ratio – Transistor Ordering, Pin Ordering, X/Y Flip, etc. • Quasi-Circuit (sometimes btw gate-transistor) Level – Input • Control vector, skew (interleaved), positive-feedback pulled – Output • Look-forward pulled, – etc. • Circuit-Level Analogue IC Design – – – Ø Current-mode Switch-capacitor Weak-inversion Design Most circuit-level power reduction methods are via low voltage approaches. See later sections. Ø Skipped in this lecture and refer to Analogue IC Design. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 3 NCUE EDAT

History • Bipolar transistors: Bardeen (1947), Schockley (1949), replace Vacuum tube because – low power consumption – More reliable – Larger integrated capacity • First Bipolar digital logic: Harris (1956) • First Bipolar digital logic (combination of transistors): Harris (1956) • 1960 Commercial logic gates: Fairchild Micrologic family (lots of Intel folks originally from here) • IC Logic family: – Transistor-Transistor Logic (TTL) 1962 (higher integration) – Emitter-Coupled Logic (ECL) 1971 better performance-(sub nanosecond) – Integrated Injection Logic (I 2 L) 1972 (high density, low power bipolar) Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 4 NCUE EDAT

History • Basic principle: J. Lilienfeld (1925) – Fail due to insufficient knowledge of the materials and gate stability problems • PMOS and NMOS transistors on the same substrate: Weimer (1962), Waniass (1965)-- better integrated capacity • CMOS logic introduced at 1963 – did not take off for more than two decades due to manufacture issues • MOSFET Take off at early 1970 s – – PMOS-only logic popular first NMOS-only logic 1972 by Intel Corp. (higher speed) High density (4 Kbit!) MOS memory in 1970 CMOS popular in late 1970 (low power) • Bi. CMOS: Combination of CMOS and Bipolar (high performance) • Gallium Arsenide: (high performance) Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 5 NCUE EDAT

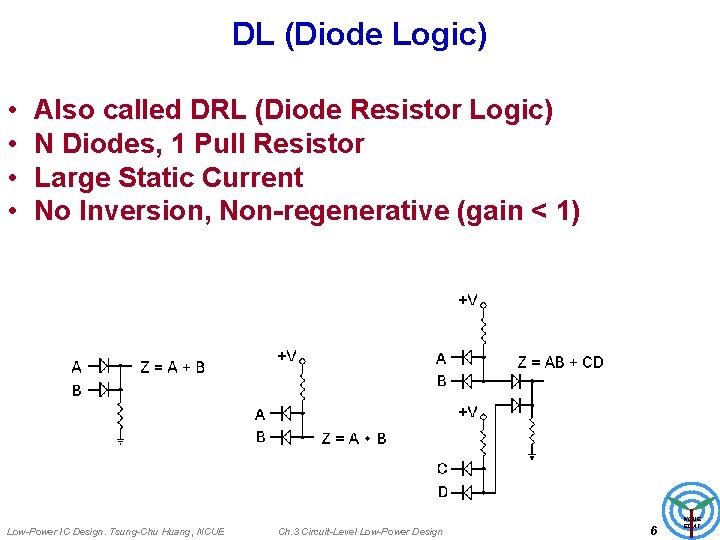

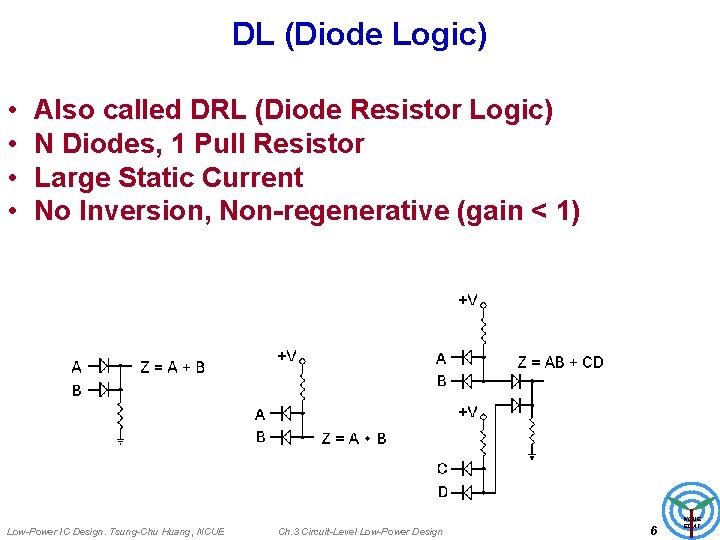

DL (Diode Logic) • • Also called DRL (Diode Resistor Logic) N Diodes, 1 Pull Resistor Large Static Current No Inversion, Non-regenerative (gain < 1) Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 6 NCUE EDAT

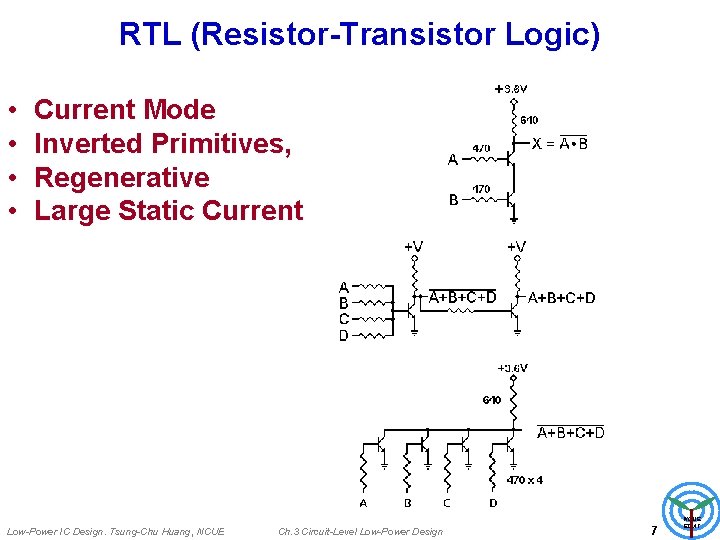

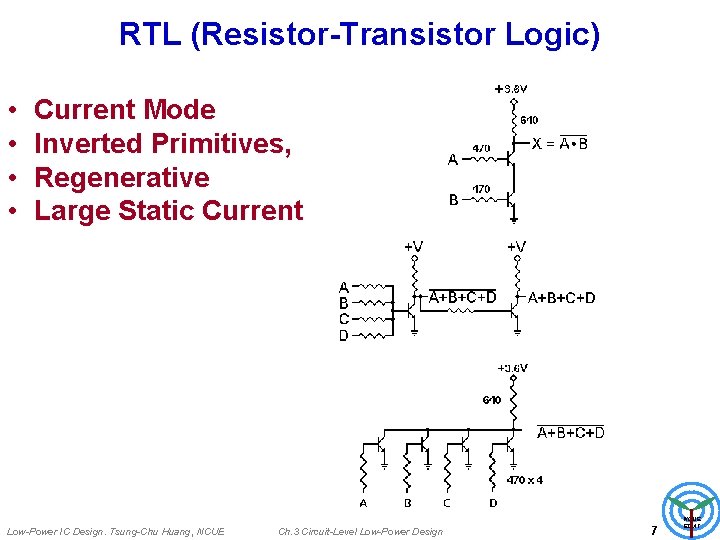

RTL (Resistor-Transistor Logic) • • Current Mode Inverted Primitives, Regenerative Large Static Current Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 7 NCUE EDAT

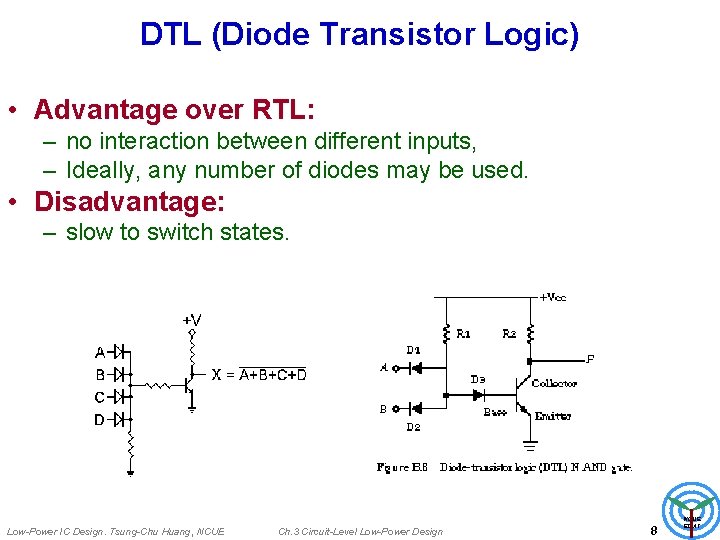

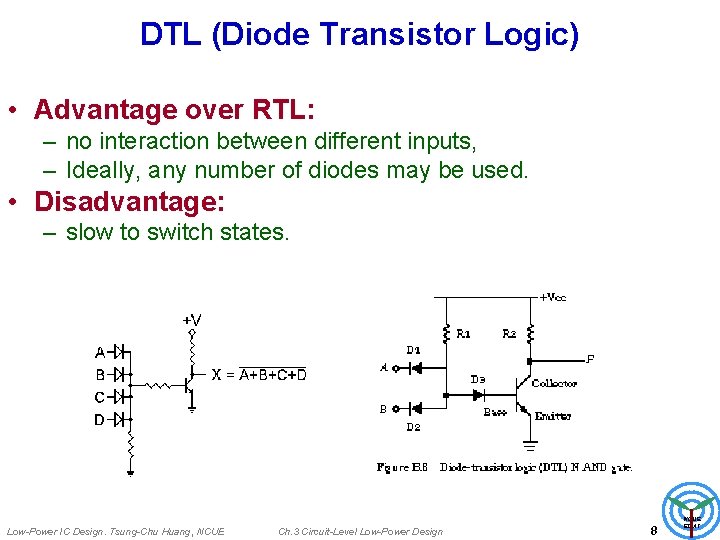

DTL (Diode Transistor Logic) • Advantage over RTL: – no interaction between different inputs, – Ideally, any number of diodes may be used. • Disadvantage: – slow to switch states. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 8 NCUE EDAT

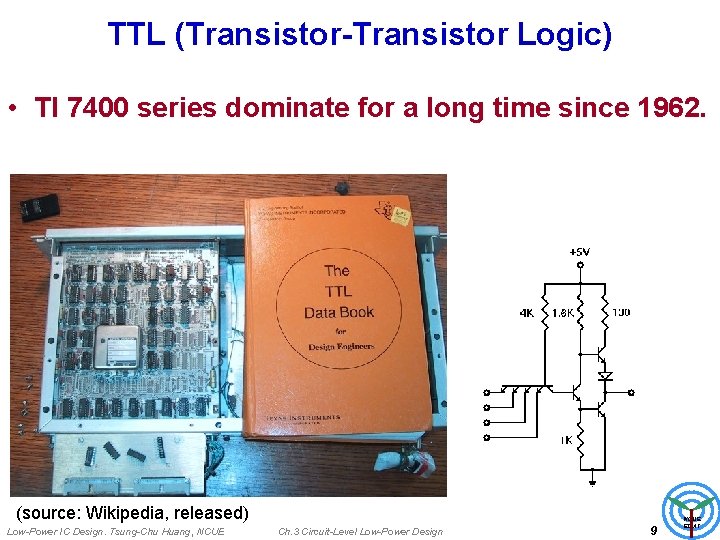

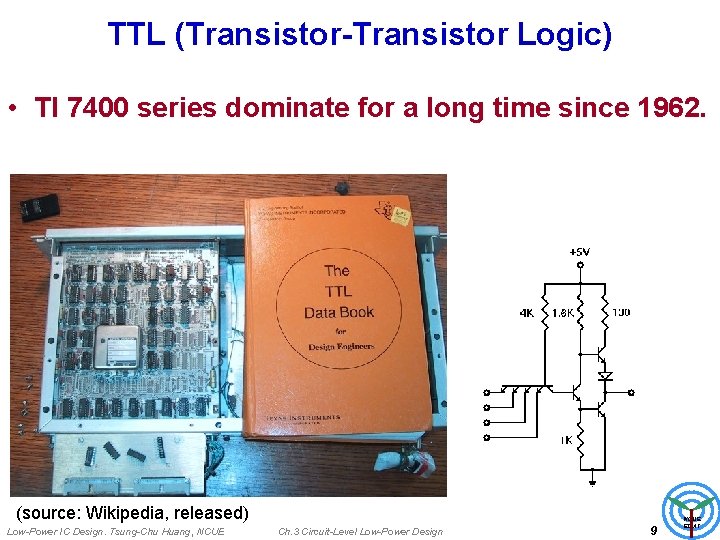

TTL (Transistor-Transistor Logic) • TI 7400 series dominate for a long time since 1962. (source: Wikipedia, released) Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 9 NCUE EDAT

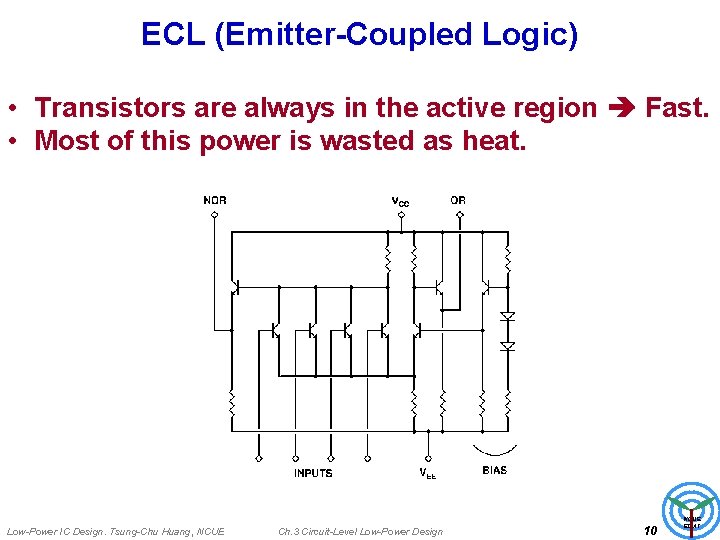

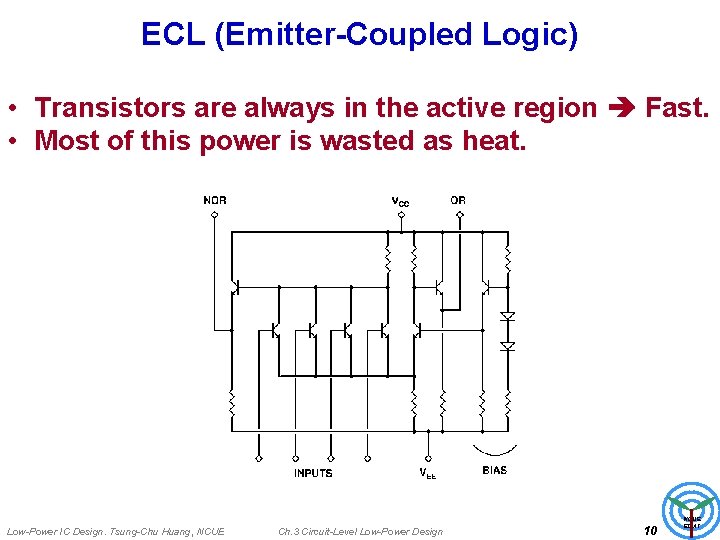

ECL (Emitter-Coupled Logic) • Transistors are always in the active region Fast. • Most of this power is wasted as heat. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 10 NCUE EDAT

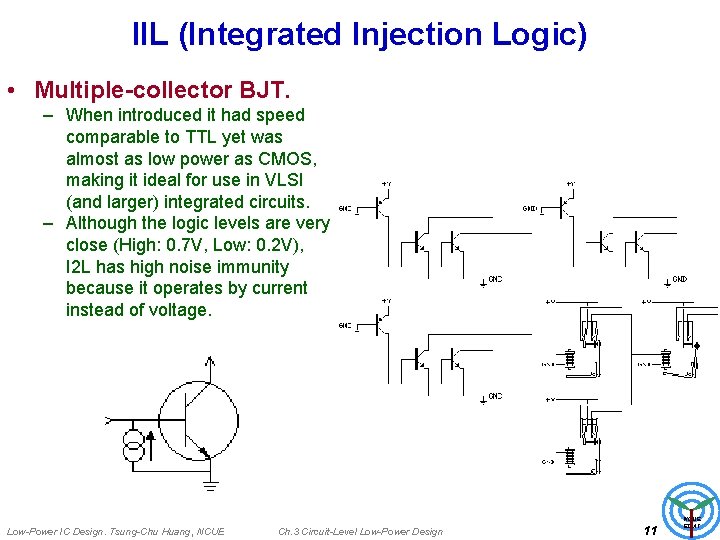

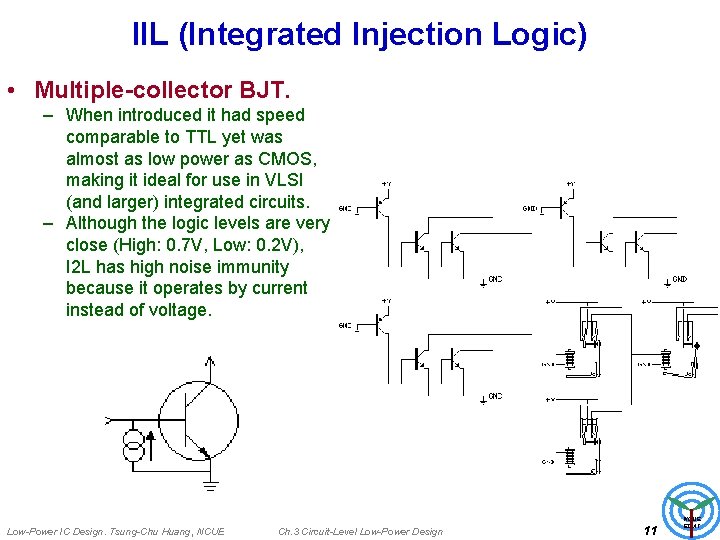

IIL (Integrated Injection Logic) • Multiple-collector BJT. – When introduced it had speed comparable to TTL yet was almost as low power as CMOS, making it ideal for use in VLSI (and larger) integrated circuits. – Although the logic levels are very close (High: 0. 7 V, Low: 0. 2 V), I 2 L has high noise immunity because it operates by current instead of voltage. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 11 NCUE EDAT

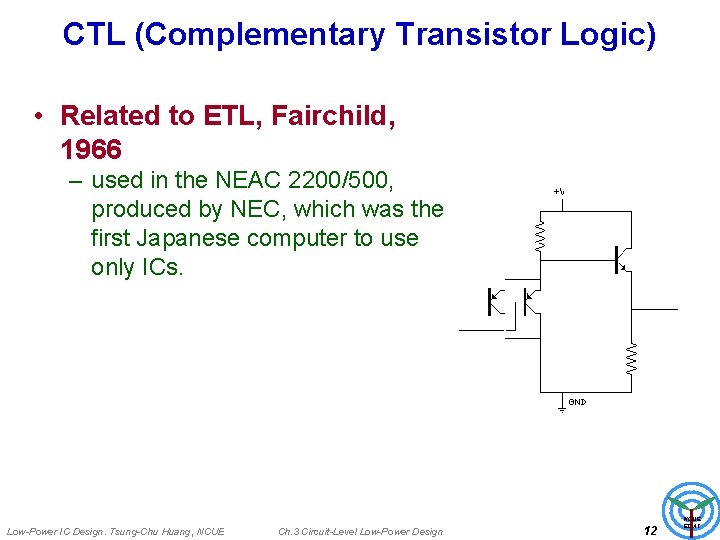

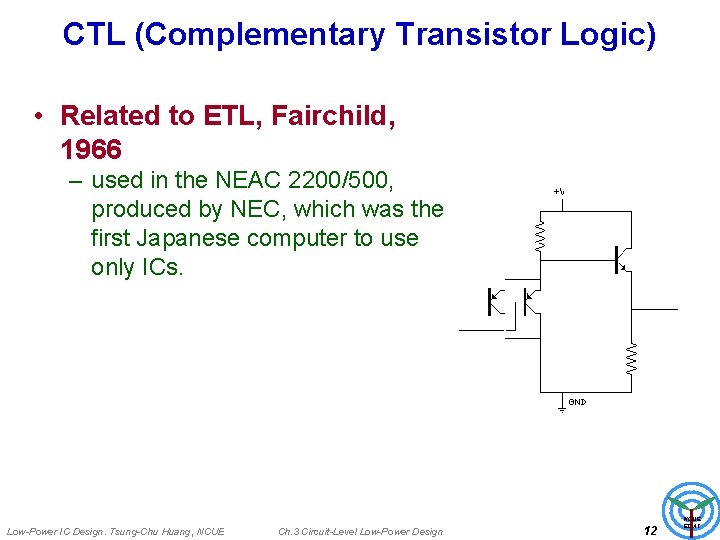

CTL (Complementary Transistor Logic) • Related to ETL, Fairchild, 1966 – used in the NEAC 2200/500, produced by NEC, which was the first Japanese computer to use only ICs. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 12 NCUE EDAT

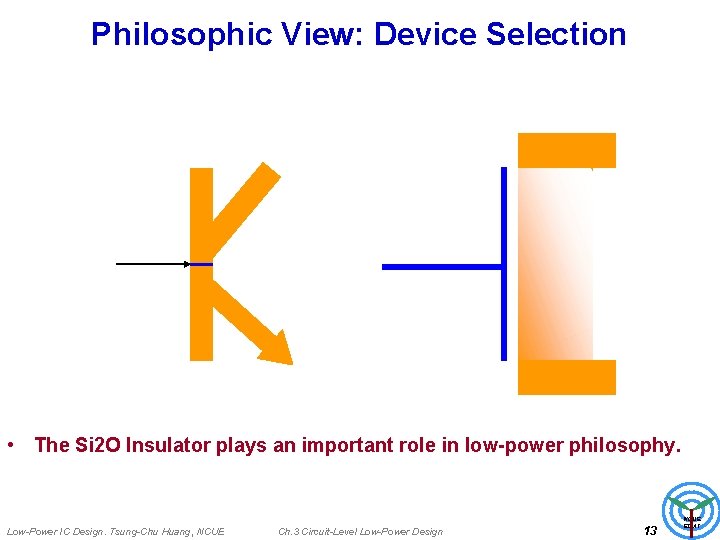

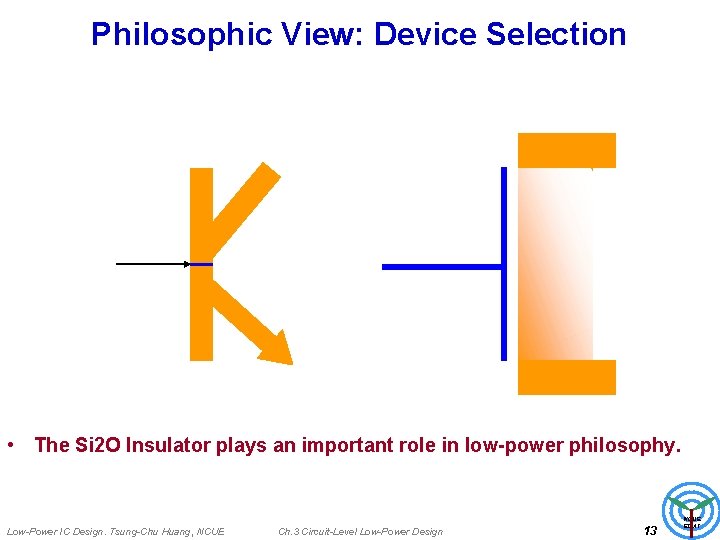

Philosophic View: Device Selection • The Si 2 O Insulator plays an important role in low-power philosophy. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 13 NCUE EDAT

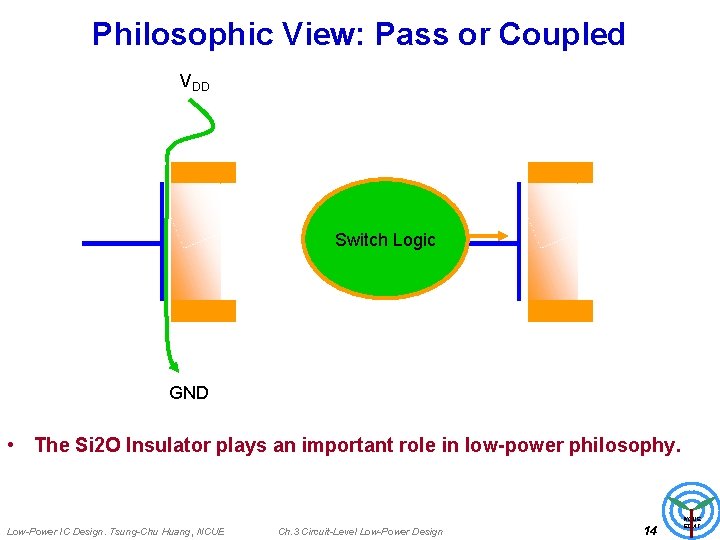

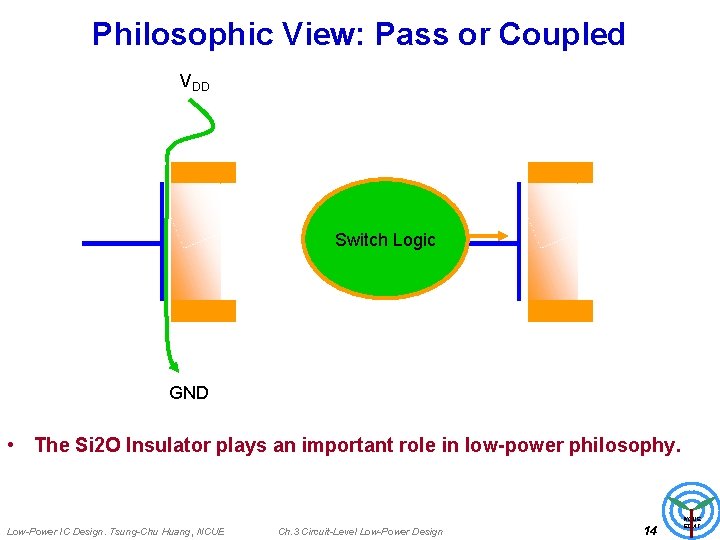

Philosophic View: Pass or Coupled VDD Switch Logic GND • The Si 2 O Insulator plays an important role in low-power philosophy. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 14 NCUE EDAT

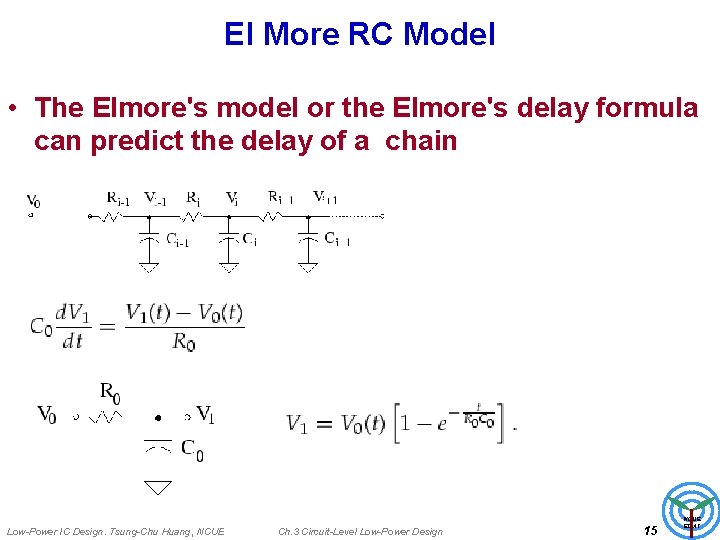

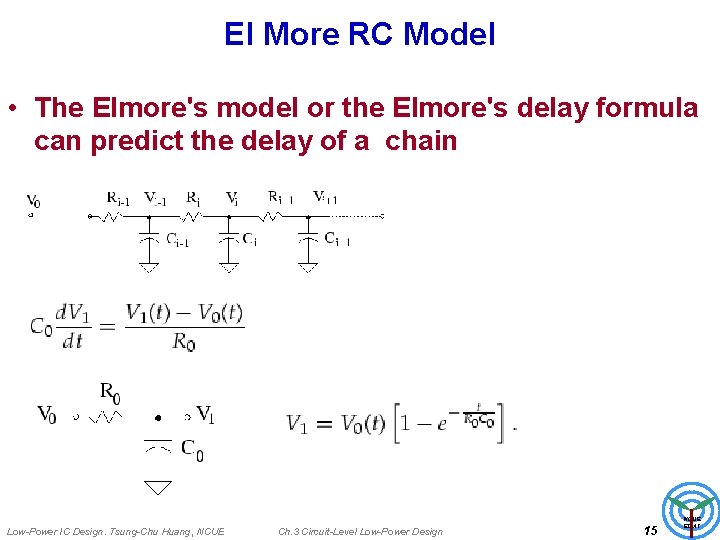

El More RC Model • The Elmore's model or the Elmore's delay formula can predict the delay of a chain Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 15 NCUE EDAT

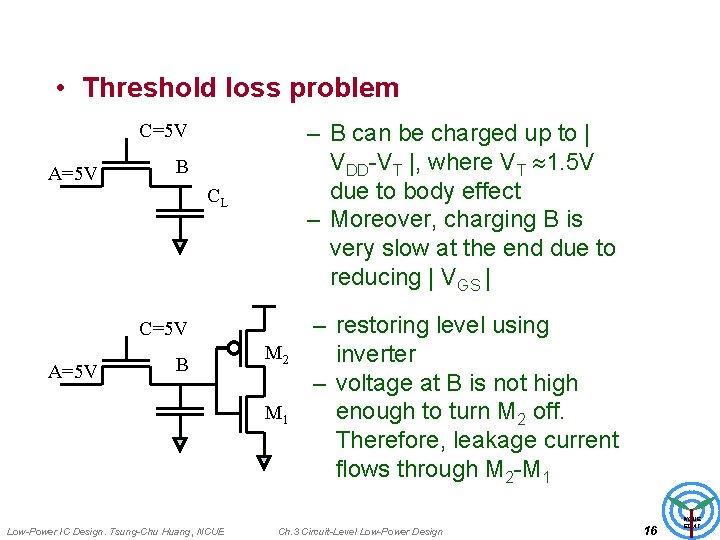

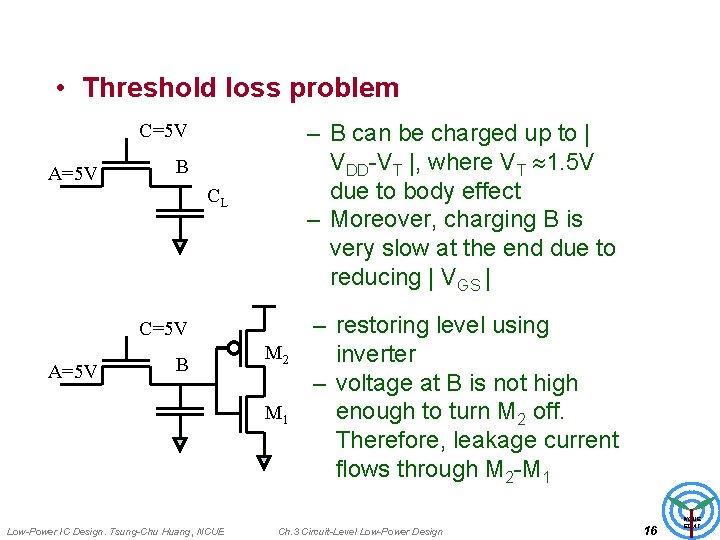

• Threshold loss problem – B can be charged up to | VDD-VT |, where VT 1. 5 V due to body effect – Moreover, charging B is very slow at the end due to reducing | VGS | C=5 V A=5 V B CL C=5 V A=5 V B M 2 M 1 Low-Power IC Design. Tsung-Chu Huang, NCUE – restoring level using inverter – voltage at B is not high enough to turn M 2 off. Therefore, leakage current flows through M 2 -M 1 Ch. 3 Circuit-Level Low-Power Design 16 NCUE EDAT

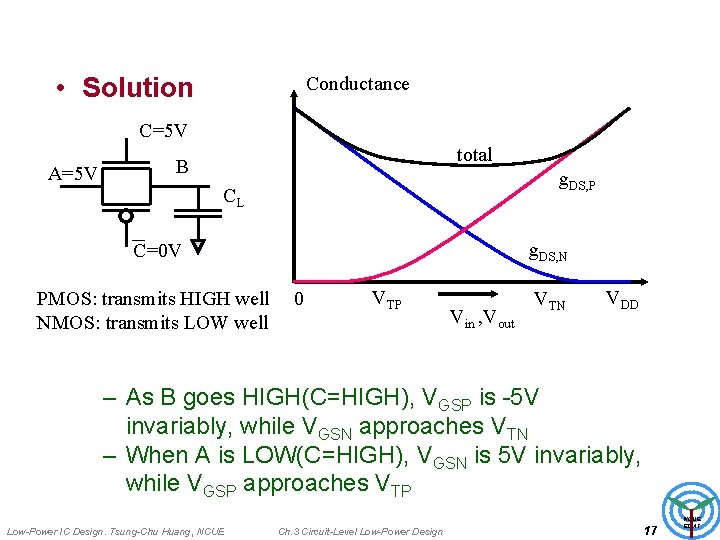

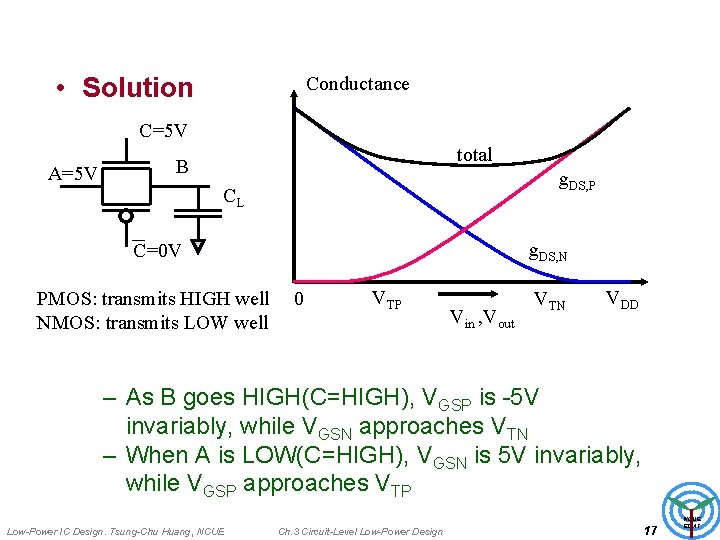

• Solution Conductance C=5 V A=5 V total B g. DS, P CL g. DS, N C=0 V PMOS: transmits HIGH well NMOS: transmits LOW well 0 VTP Vin , Vout VTN VDD – As B goes HIGH(C=HIGH), VGSP is -5 V invariably, while VGSN approaches VTN – When A is LOW(C=HIGH), VGSN is 5 V invariably, while VGSP approaches VTP Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 3 Circuit-Level Low-Power Design 17 NCUE EDAT

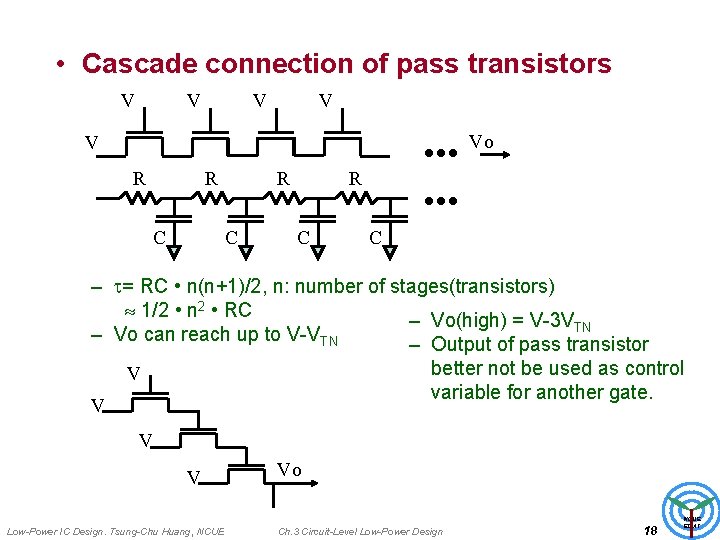

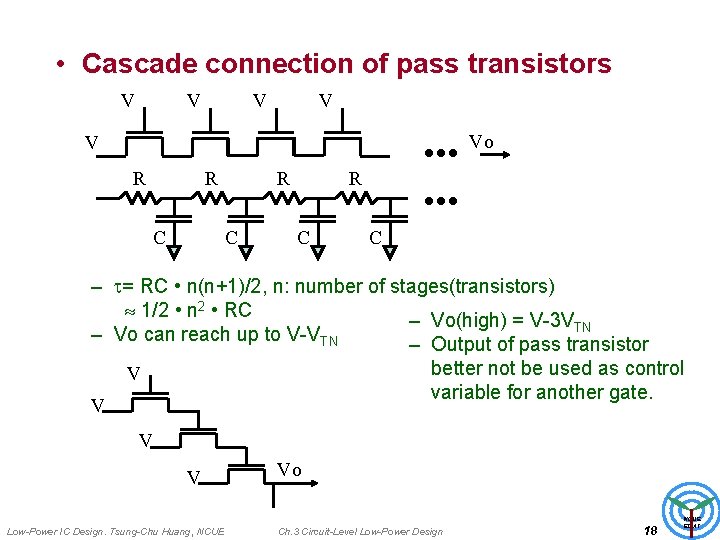

• Cascade connection of pass transistors V V Vo V R R C R C C – = RC • n(n+1)/2, n: number of stages(transistors) 1/2 • n 2 • RC – Vo(high) = V-3 VTN – Vo can reach up to V-VTN – Output of pass transistor better not be used as control variable for another gate. V V Low-Power IC Design. Tsung-Chu Huang, NCUE Vo Ch. 3 Circuit-Level Low-Power Design 18 NCUE EDAT