LowLevel Programming ICOM 4036 Lecture 4 Prof Bienvenido

Low-Level Programming ICOM 4036 Lecture 4 Prof. Bienvenido Velez Fall 2006 ICOM 4036 Programming Laguages Lecture 4 1

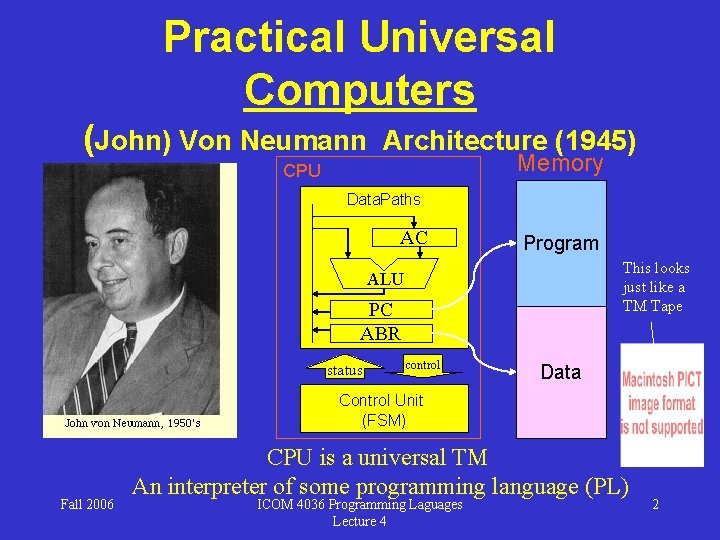

Practical Universal Computers (John) Von Neumann Architecture (1945) Memory CPU Data. Paths AC Program This looks just like a TM Tape ALU PC ABR status control Data Control Unit (FSM) Fall 2006 CPU is a universal TM An interpreter of some programming language (PL) ICOM 4036 Programming Laguages Lecture 4 2

Outline • • The Von Neumann Architecture From Voltages to Computers Low-level Programming Implementing HLL Abstractions – Control structures – Data Structures – Procedures and Functions Fall 2006 ICOM 4036 Programming Laguages Lecture 4 3

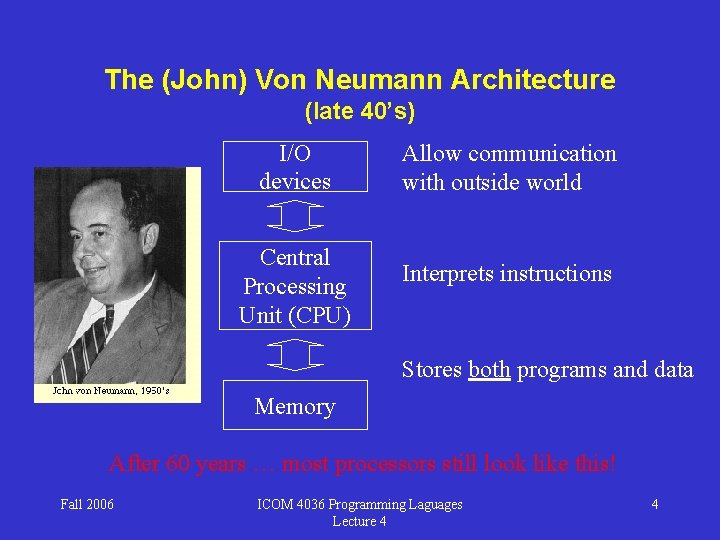

The (John) Von Neumann Architecture (late 40’s) I/O devices Central Processing Unit (CPU) Allow communication with outside world Interprets instructions Stores both programs and data Memory After 60 years … most processors still look like this! Fall 2006 ICOM 4036 Programming Laguages Lecture 4 4

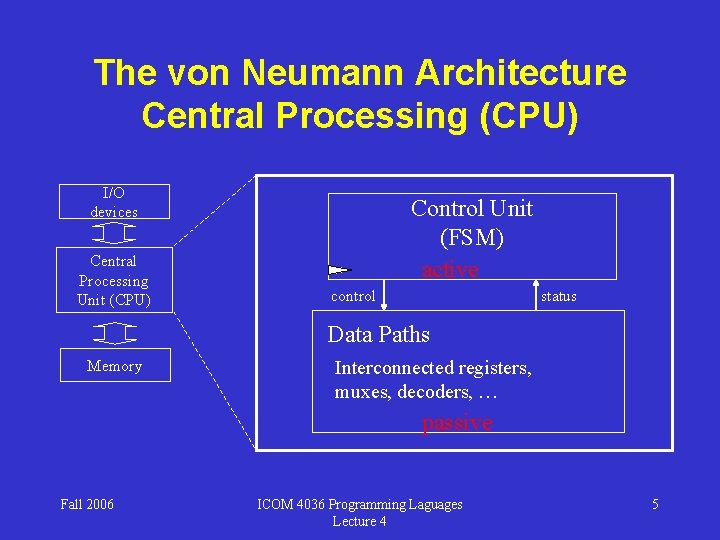

The von Neumann Architecture Central Processing (CPU) I/O devices Central Processing Unit (CPU) Control Unit (FSM) active control status Data Paths Memory Interconnected registers, muxes, decoders, … passive Fall 2006 ICOM 4036 Programming Laguages Lecture 4 5

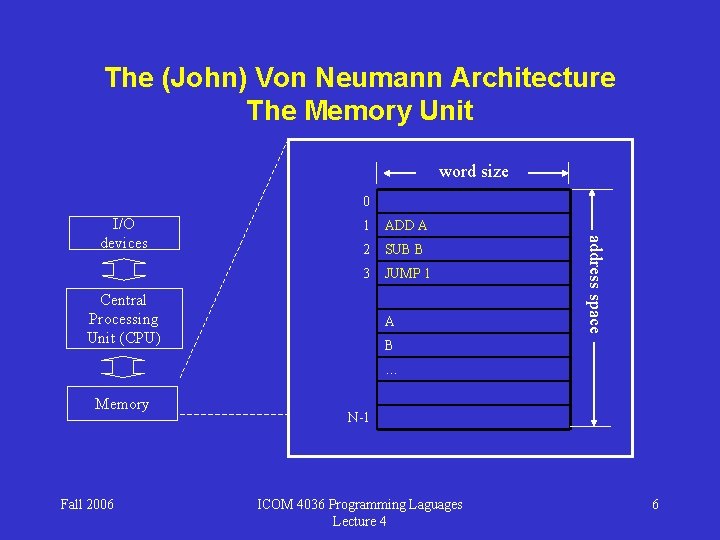

The (John) Von Neumann Architecture The Memory Unit word size 0 1 ADD A 2 SUB B 3 JUMP 1 Central Processing Unit (CPU) A address space I/O devices B … Memory Fall 2006 N-1 ICOM 4036 Programming Laguages Lecture 4 6

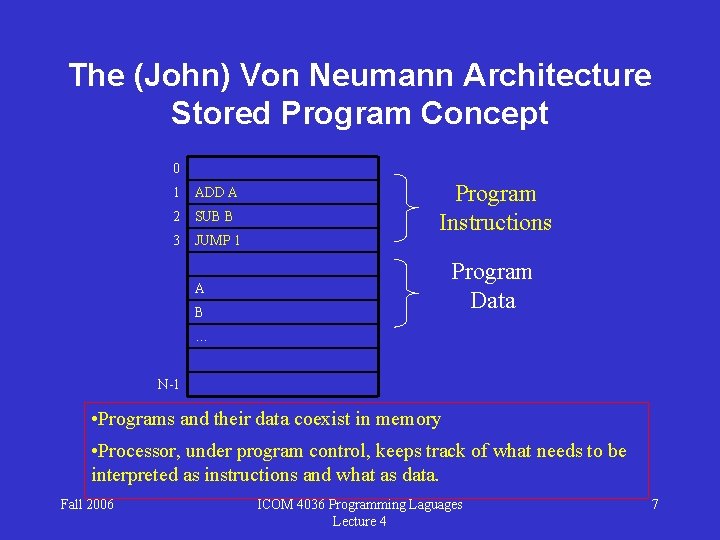

The (John) Von Neumann Architecture Stored Program Concept 0 1 ADD A 2 SUB B 3 JUMP 1 Program Instructions Program Data A B … N-1 • Programs and their data coexist in memory • Processor, under program control, keeps track of what needs to be interpreted as instructions and what as data. Fall 2006 ICOM 4036 Programming Laguages Lecture 4 7

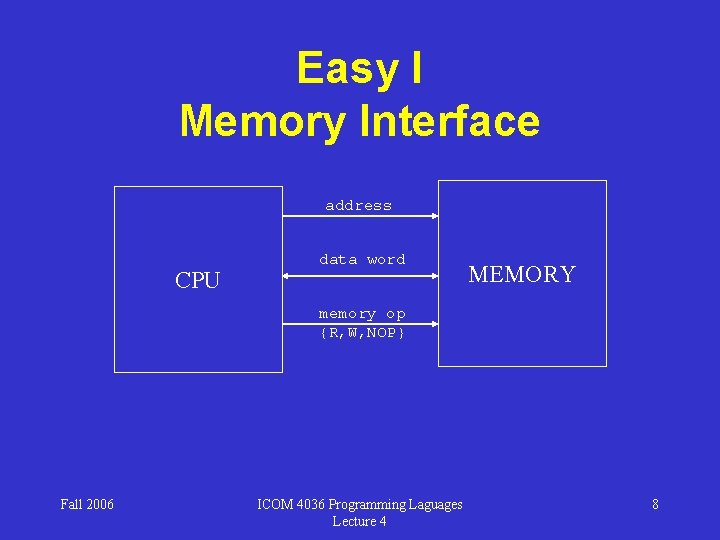

Easy I Memory Interface address CPU data word MEMORY memory op {R, W, NOP} Fall 2006 ICOM 4036 Programming Laguages Lecture 4 8

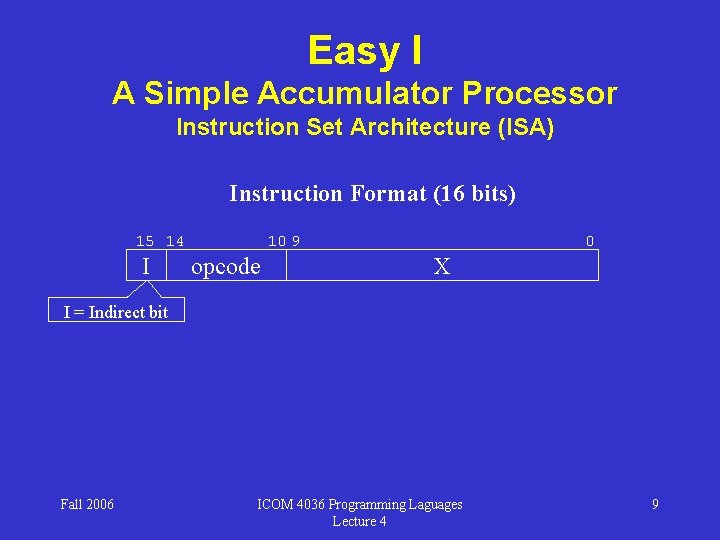

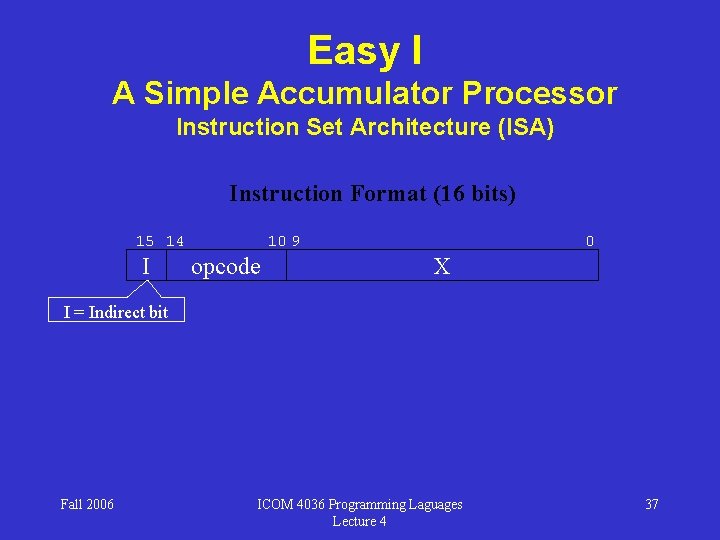

Easy I A Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Format (16 bits) 15 14 I 10 9 opcode 0 X I = Indirect bit Fall 2006 ICOM 4036 Programming Laguages Lecture 4 9

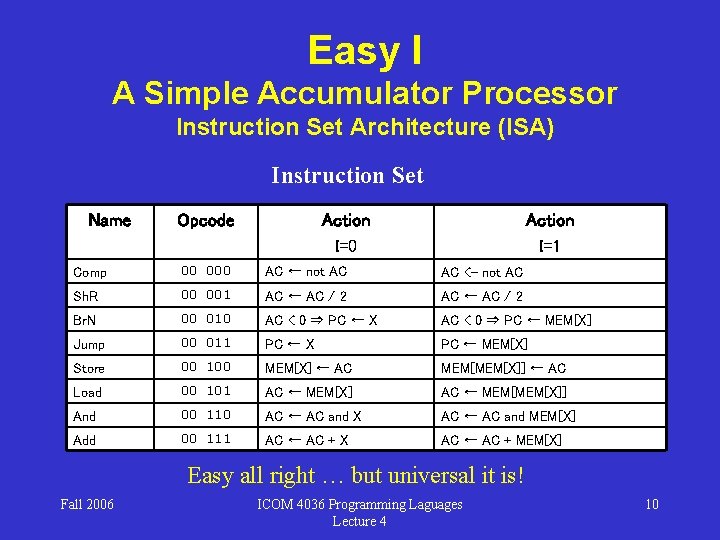

Easy I A Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Set Name Opcode Action I=0 Action I=1 Comp 00 000 AC ← not AC AC <- not AC Sh. R 00 001 AC ← AC / 2 Br. N 00 010 AC < 0 ⇒ PC ← X AC < 0 ⇒ PC ← MEM[X] Jump 00 011 PC ← X PC ← MEM[X] Store 00 100 MEM[X] ← AC MEM[X]] ← AC Load 00 101 AC ← MEM[X]] And 00 110 AC ← AC and X AC ← AC and MEM[X] Add 00 111 AC ← AC + X AC ← AC + MEM[X] Easy all right … but universal it is! Fall 2006 ICOM 4036 Programming Laguages Lecture 4 10

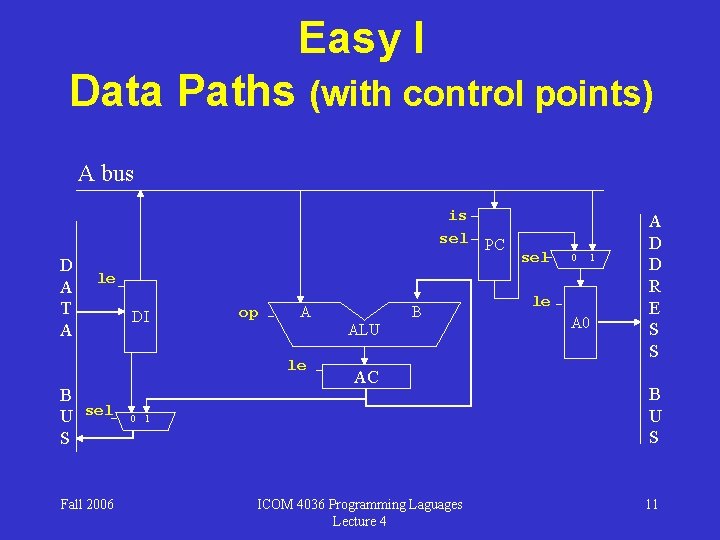

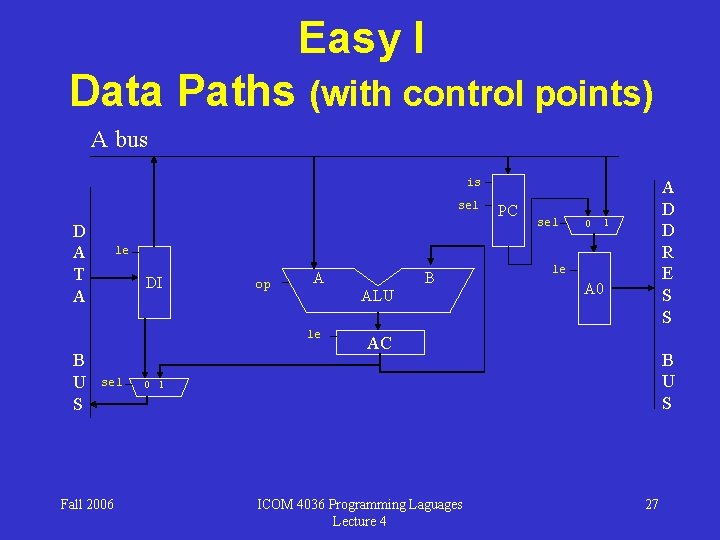

Easy I Data Paths (with control points) A bus is sel D A T A PC sel 0 le DI op A ALU le B U sel S Fall 2006 B AC 0 1 ICOM 4036 Programming Laguages Lecture 4 le A 0 1 A D D R E S S B U S 11

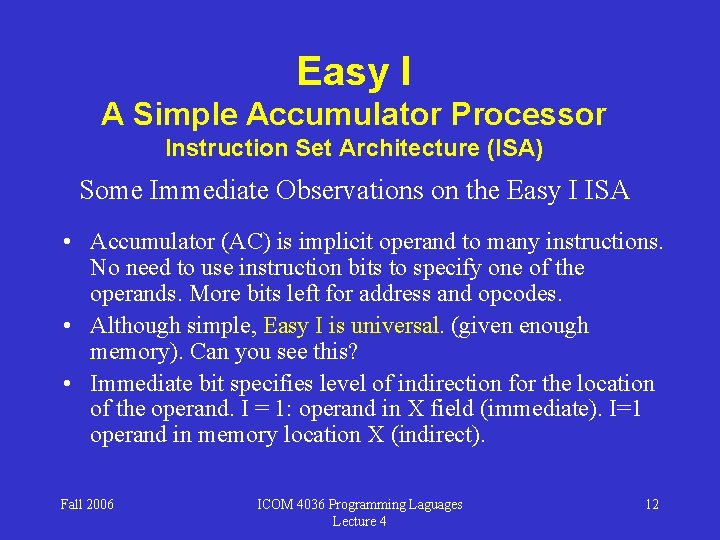

Easy I A Simple Accumulator Processor Instruction Set Architecture (ISA) Some Immediate Observations on the Easy I ISA • Accumulator (AC) is implicit operand to many instructions. No need to use instruction bits to specify one of the operands. More bits left for address and opcodes. • Although simple, Easy I is universal. (given enough memory). Can you see this? • Immediate bit specifies level of indirection for the location of the operand. I = 1: operand in X field (immediate). I=1 operand in memory location X (indirect). Fall 2006 ICOM 4036 Programming Laguages Lecture 4 12

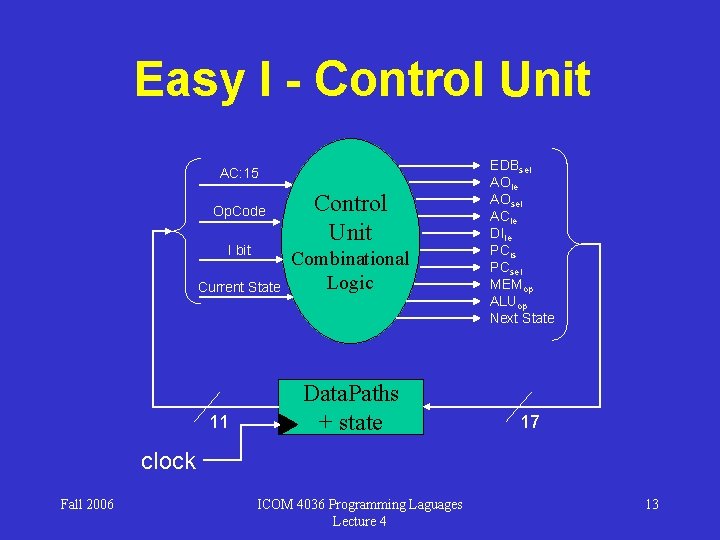

Easy I - Control Unit AC: 15 Op. Code I bit Current State 11 Control Unit Combinational Logic Data. Paths + state EDBsel AOle AOsel ACle DIle PCis PCsel MEMop ALUop Next State 17 clock Fall 2006 ICOM 4036 Programming Laguages Lecture 4 13

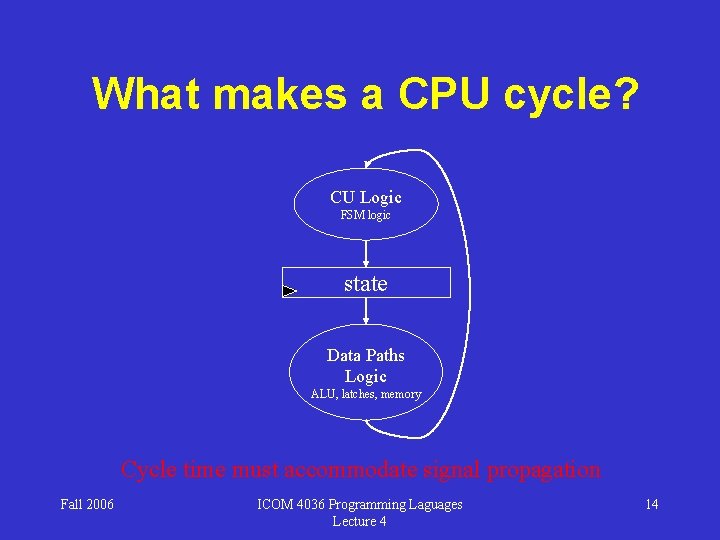

What makes a CPU cycle? CU Logic FSM logic state Data Paths Logic ALU, latches, memory Cycle time must accommodate signal propagation Fall 2006 ICOM 4036 Programming Laguages Lecture 4 14

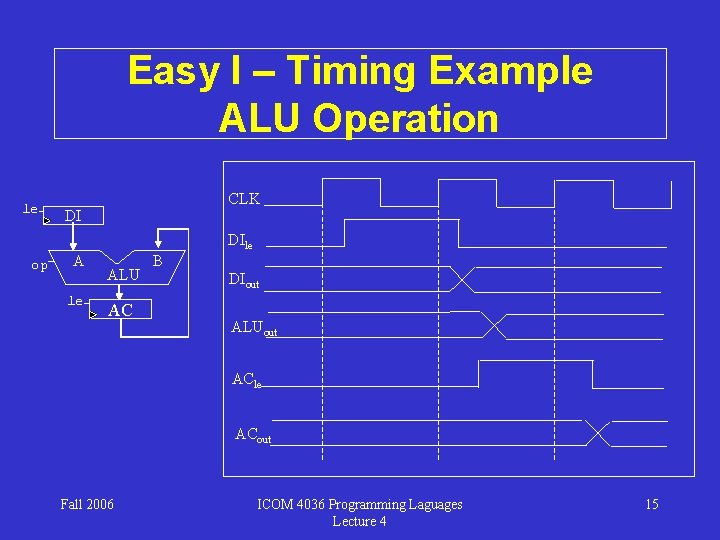

Easy I – Timing Example ALU Operation le CLK DI DIle op A le ALU AC B DIout ALUout ACle ACout Fall 2006 ICOM 4036 Programming Laguages Lecture 4 15

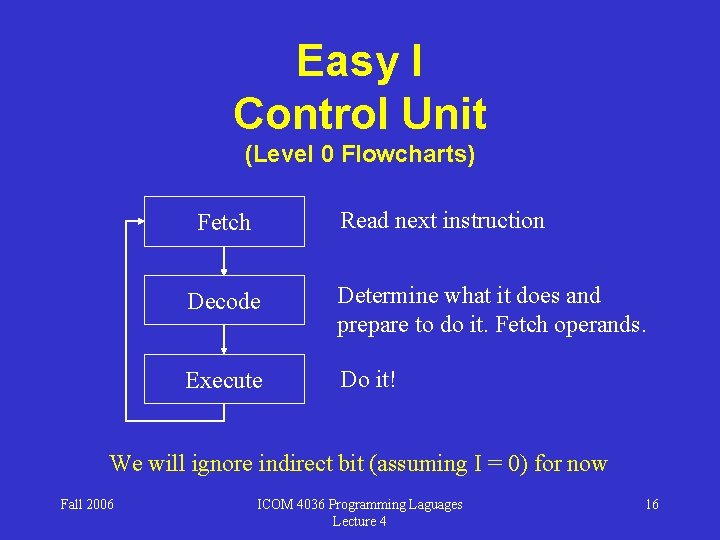

Easy I Control Unit (Level 0 Flowcharts) Read next instruction Fetch Decode Determine what it does and prepare to do it. Fetch operands. Execute Do it! We will ignore indirect bit (assuming I = 0) for now Fall 2006 ICOM 4036 Programming Laguages Lecture 4 16

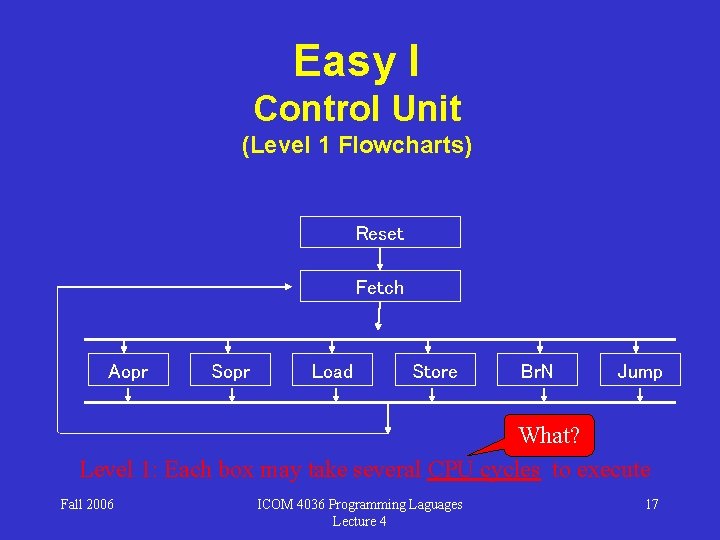

Easy I Control Unit (Level 1 Flowcharts) Reset Fetch Aopr Sopr Load Store Br. N Jump What? Level 1: Each box may take several CPU cycles to execute Fall 2006 ICOM 4036 Programming Laguages Lecture 4 17

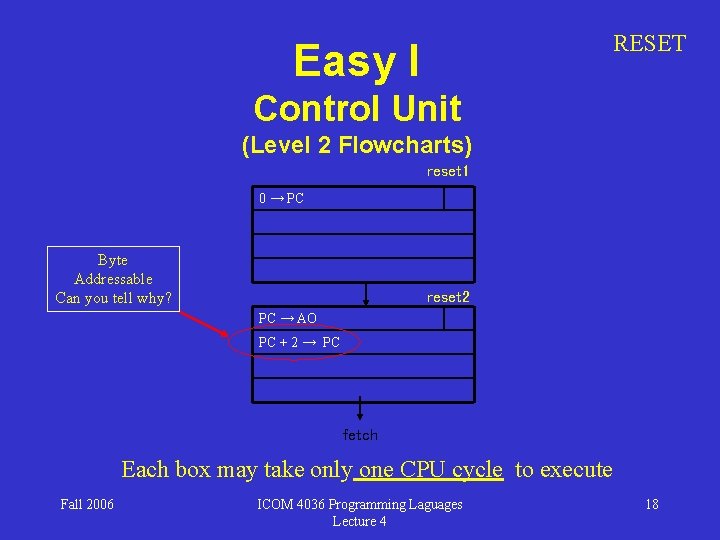

RESET Easy I Control Unit (Level 2 Flowcharts) reset 1 0 → PC Byte Addressable Can you tell why? reset 2 PC → AO PC + 2 → PC fetch Each box may take only one CPU cycle to execute Fall 2006 ICOM 4036 Programming Laguages Lecture 4 18

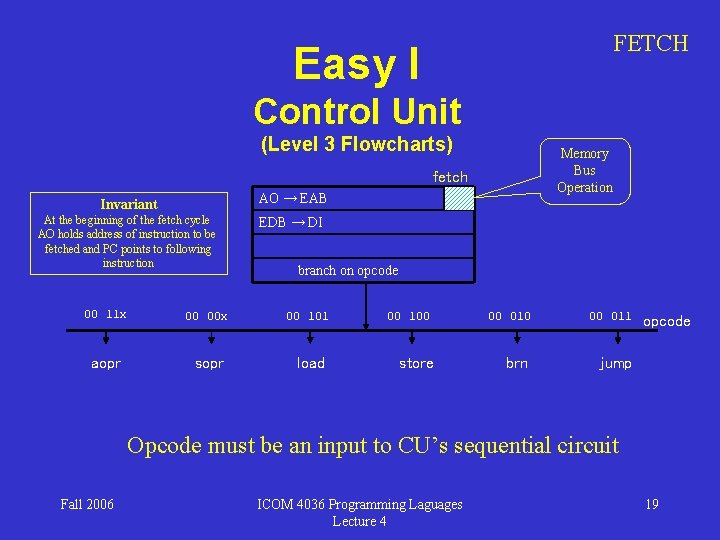

FETCH Easy I Control Unit (Level 3 Flowcharts) Memory Bus Operation fetch AO → EAB Invariant At the beginning of the fetch cycle AO holds address of instruction to be fetched and PC points to following instruction EDB → DI branch on opcode 00 11 x 00 00 x 00 101 aopr sopr load 00 100 00 011 store brn jump opcode Opcode must be an input to CU’s sequential circuit Fall 2006 ICOM 4036 Programming Laguages Lecture 4 19

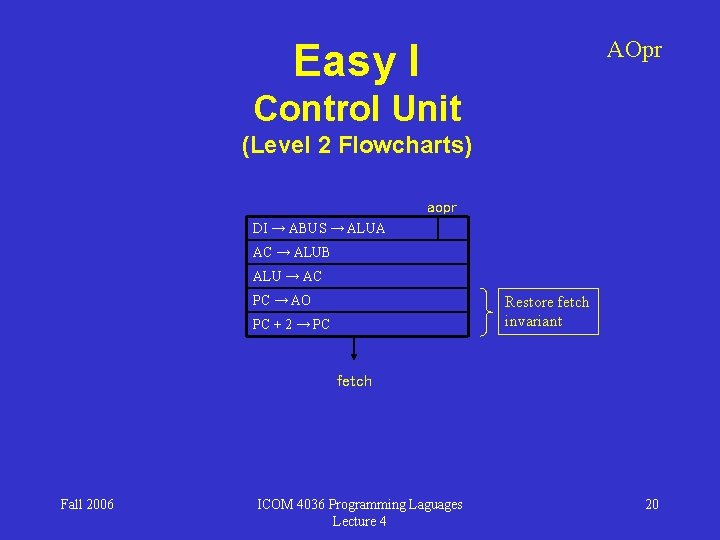

AOpr Easy I Control Unit (Level 2 Flowcharts) aopr DI → ABUS → ALUA AC → ALUB ALU → AC PC → AO Restore fetch invariant PC + 2 → PC fetch Fall 2006 ICOM 4036 Programming Laguages Lecture 4 20

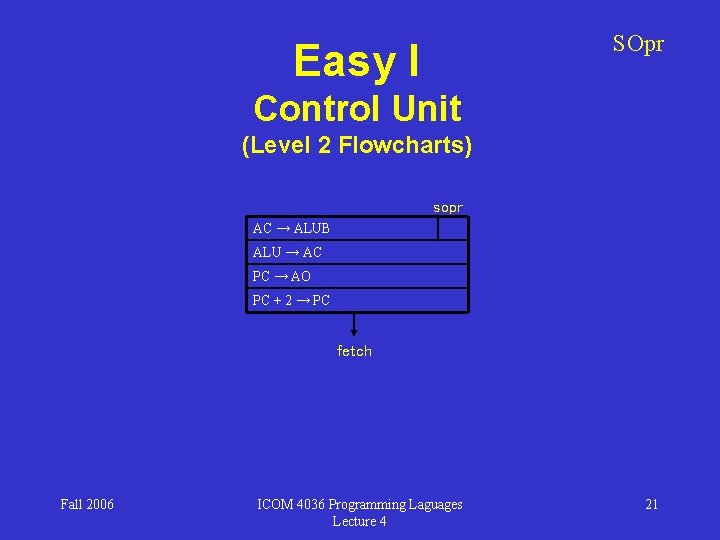

SOpr Easy I Control Unit (Level 2 Flowcharts) sopr AC → ALUB ALU → AC PC → AO PC + 2 → PC fetch Fall 2006 ICOM 4036 Programming Laguages Lecture 4 21

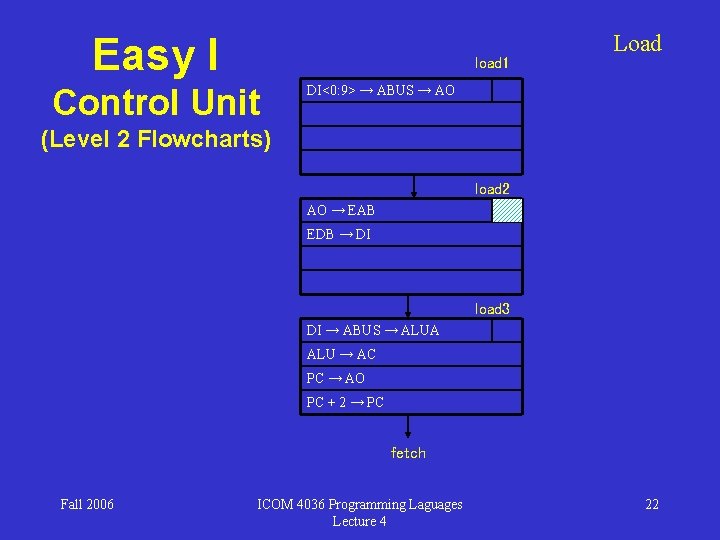

Easy I load 1 Control Unit Load DI<0: 9> → ABUS → AO (Level 2 Flowcharts) load 2 AO → EAB EDB → DI load 3 DI → ABUS → ALUA ALU → AC PC → AO PC + 2 → PC fetch Fall 2006 ICOM 4036 Programming Laguages Lecture 4 22

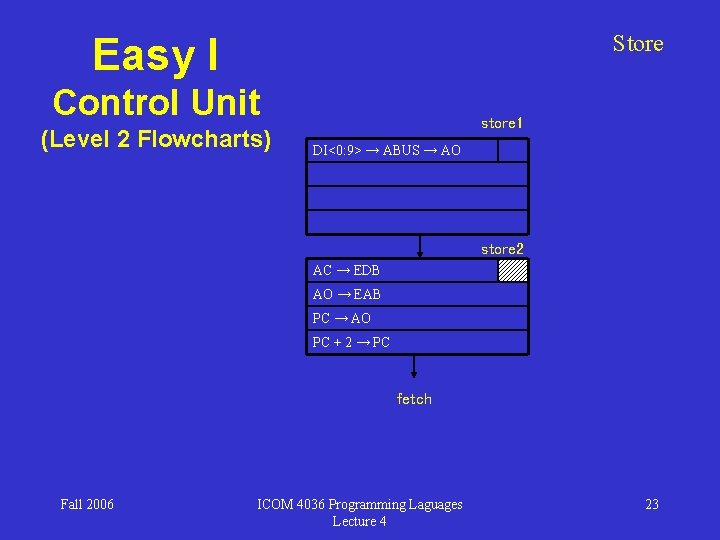

Store Easy I Control Unit (Level 2 Flowcharts) store 1 DI<0: 9> → ABUS → AO store 2 AC → EDB AO → EAB PC → AO PC + 2 → PC fetch Fall 2006 ICOM 4036 Programming Laguages Lecture 4 23

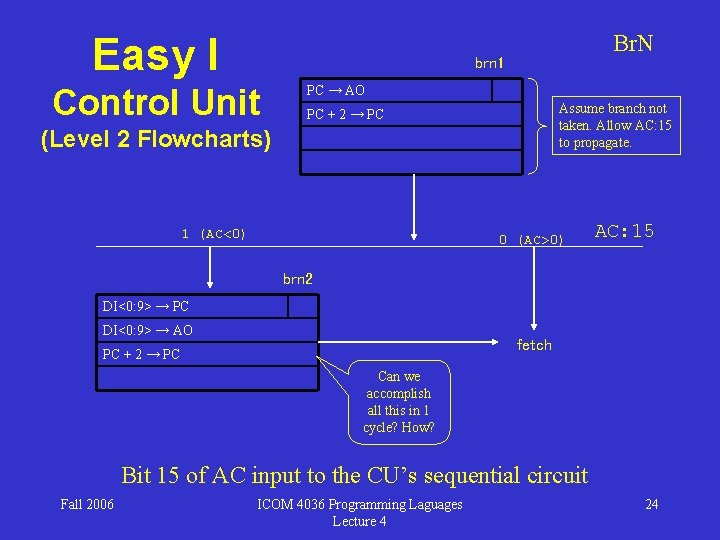

Easy I Br. N brn 1 Control Unit PC → AO Assume branch not taken. Allow AC: 15 to propagate. PC + 2 → PC (Level 2 Flowcharts) 1 (AC<0) 0 (AC>0) AC: 15 brn 2 DI<0: 9> → PC DI<0: 9> → AO fetch PC + 2 → PC Can we accomplish all this in 1 cycle? How? Bit 15 of AC input to the CU’s sequential circuit Fall 2006 ICOM 4036 Programming Laguages Lecture 4 24

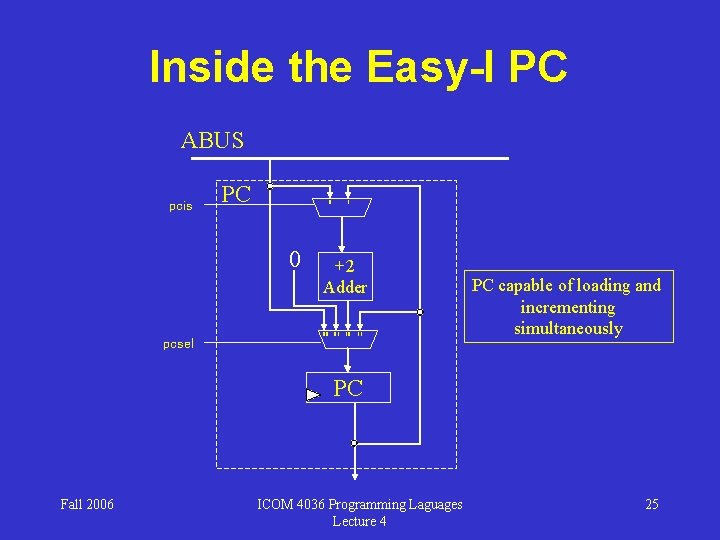

Inside the Easy-I PC ABUS pcis PC 0 0 pcsel 1 +2 Adder 00 01 10 11 PC capable of loading and incrementing simultaneously PC Fall 2006 ICOM 4036 Programming Laguages Lecture 4 25

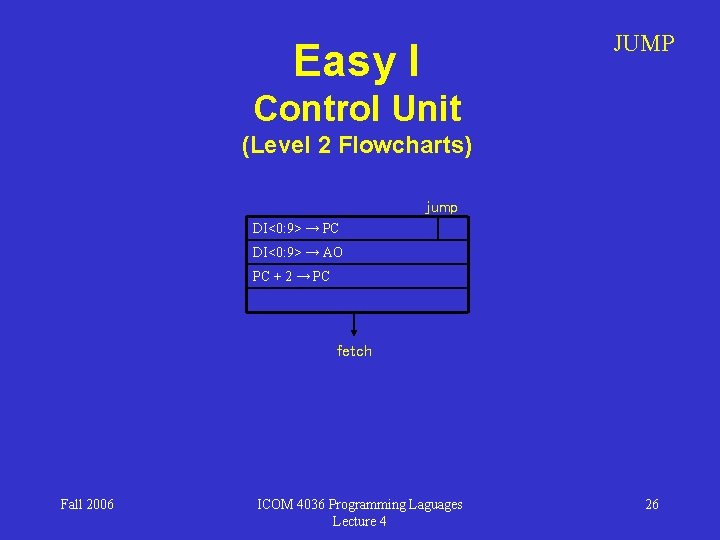

JUMP Easy I Control Unit (Level 2 Flowcharts) jump DI<0: 9> → PC DI<0: 9> → AO PC + 2 → PC fetch Fall 2006 ICOM 4036 Programming Laguages Lecture 4 26

Easy I Data Paths (with control points) A bus is sel D A T A sel 0 1 le DI op A sel Fall 2006 B ALU le B U S PC A D D R E S S le A 0 AC B U S 0 1 ICOM 4036 Programming Laguages Lecture 4 27

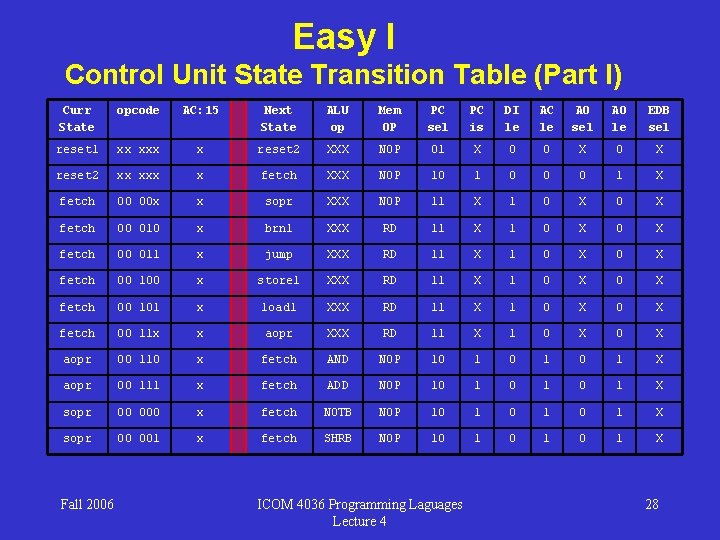

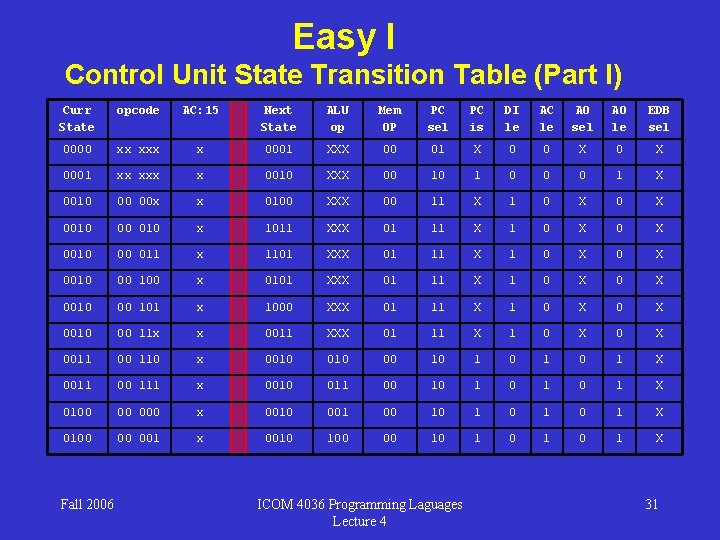

Easy I Control Unit State Transition Table (Part I) Curr State opcode AC: 15 Next State ALU op Mem OP PC sel PC is DI le AC le AO sel AO le EDB sel reset 1 xx x reset 2 XXX NOP 01 X 0 0 X reset 2 xx x fetch XXX NOP 10 1 0 0 0 1 X fetch 00 00 x x sopr XXX NOP 11 X 1 0 X fetch 00 010 x brn 1 XXX RD 11 X 1 0 X fetch 00 011 x jump XXX RD 11 X 1 0 X fetch 00 100 x store 1 XXX RD 11 X 1 0 X fetch 00 101 x load 1 XXX RD 11 X 1 0 X fetch 00 11 x x aopr XXX RD 11 X 1 0 X aopr 00 110 x fetch AND NOP 10 1 0 1 X aopr 00 111 x fetch ADD NOP 10 1 0 1 X sopr 00 000 x fetch NOTB NOP 10 1 0 1 X sopr 00 001 x fetch SHRB NOP 10 1 0 1 X Fall 2006 ICOM 4036 Programming Laguages Lecture 4 28

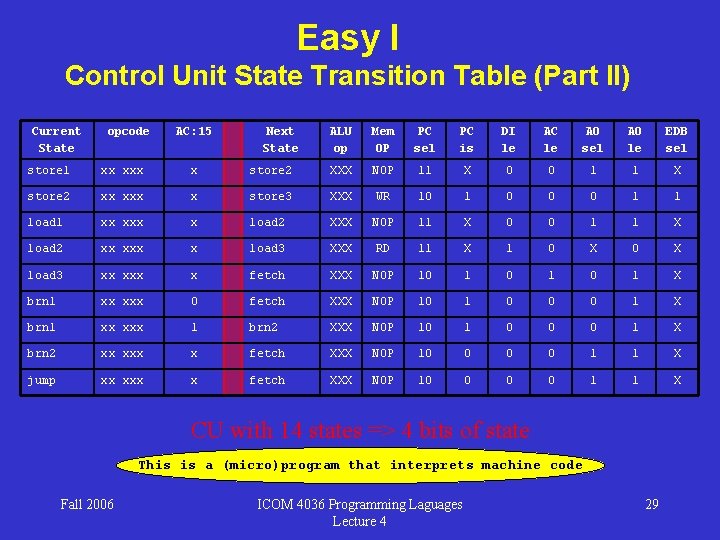

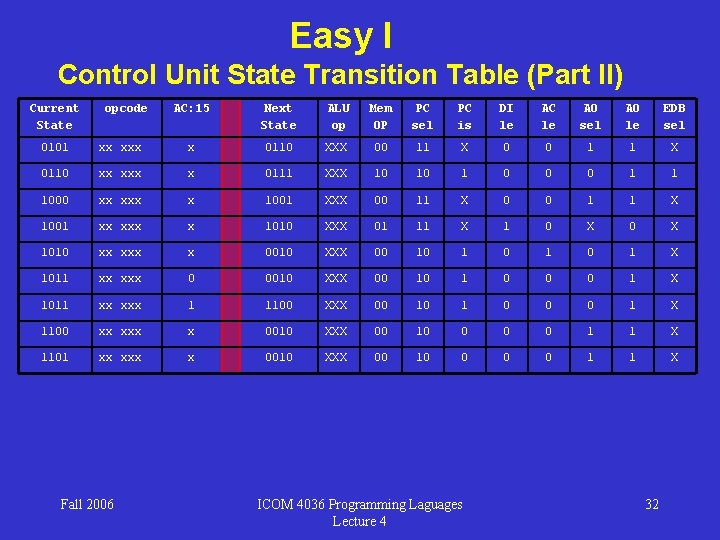

Easy I Control Unit State Transition Table (Part II) Current State opcode AC: 15 Next State ALU op Mem OP PC sel PC is DI le AC le AO sel AO le EDB sel store 1 xx x store 2 XXX NOP 11 X 0 0 1 1 X store 2 xx x store 3 XXX WR 10 1 0 0 0 1 1 load 1 xx x load 2 XXX NOP 11 X 0 0 1 1 X load 2 xx x load 3 XXX RD 11 X 1 0 X load 3 xx x fetch XXX NOP 10 1 0 1 X brn 1 xx xxx 0 fetch XXX NOP 10 1 0 0 0 1 X brn 1 xx xxx 1 brn 2 XXX NOP 10 1 0 0 0 1 X brn 2 xx x fetch XXX NOP 10 0 1 1 X jump xx x fetch XXX NOP 10 0 1 1 X CU with 14 states => 4 bits of state This is a (micro)program that interprets machine code Fall 2006 ICOM 4036 Programming Laguages Lecture 4 29

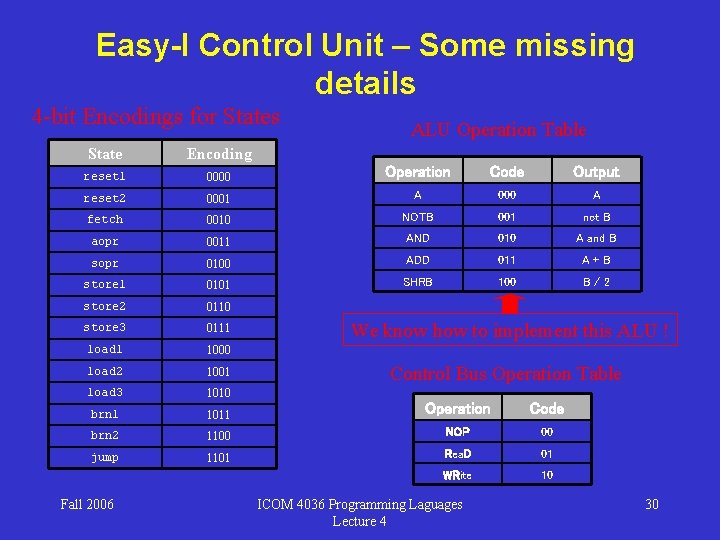

Easy-I Control Unit – Some missing details 4 -bit Encodings for States ALU Operation Table State Encoding reset 1 0000 Operation Code Output reset 2 0001 A 000 A fetch 0010 NOTB 001 not B aopr 0011 AND 010 A and B sopr 0100 ADD 011 A+B store 1 0101 SHRB 100 B/2 store 2 0110 store 3 0111 load 1 1000 load 2 1001 load 3 1010 brn 1 1011 Operation Code brn 2 1100 NOP 00 jump 1101 Rea. D 01 WRite 10 Fall 2006 We know how to implement this ALU ! Control Bus Operation Table ICOM 4036 Programming Laguages Lecture 4 30

Easy I Control Unit State Transition Table (Part I) Curr State opcode AC: 15 Next State ALU op Mem OP PC sel PC is DI le AC le AO sel AO le EDB sel 0000 xx x 0001 XXX 00 01 X 0 0 X 0001 xx x 0010 XXX 00 10 1 0 0 0 1 X 0010 00 00 x x 0100 XXX 00 11 X 1 0 X 0010 00 010 x 1011 XXX 01 11 X 1 0 X 0010 00 011 x 1101 XXX 01 11 X 1 0 X 0010 00 100 x 0101 XXX 01 11 X 1 0 X 0010 00 101 x 1000 XXX 01 11 X 1 0 X 0010 00 11 x x 0011 XXX 01 11 X 1 0 X 0011 00 110 x 0010 00 10 1 0 1 X 0011 00 111 x 0010 011 00 10 1 0 1 X 0100 00 000 x 0010 001 00 10 1 0 1 X 0100 00 001 x 0010 100 00 10 1 0 1 X Fall 2006 ICOM 4036 Programming Laguages Lecture 4 31

Easy I Control Unit State Transition Table (Part II) Current State opcode AC: 15 Next State ALU op Mem OP PC sel PC is DI le AC le AO sel AO le EDB sel 0101 xx x 0110 XXX 00 11 X 0 0 1 1 X 0110 xx x 0111 XXX 10 10 1 0 0 0 1 1 1000 xx x 1001 XXX 00 11 X 0 0 1 1 X 1001 xx x 1010 XXX 01 11 X 1 0 X 1010 xx x 0010 XXX 00 10 1 0 1 X 1011 xx xxx 0 0010 XXX 00 10 1 0 0 0 1 X 1011 xx xxx 1 1100 XXX 00 10 1 0 0 0 1 X 1100 xx x 0010 XXX 00 10 0 1 1 X 1101 xx x 0010 XXX 00 10 0 1 1 X Fall 2006 ICOM 4036 Programming Laguages Lecture 4 32

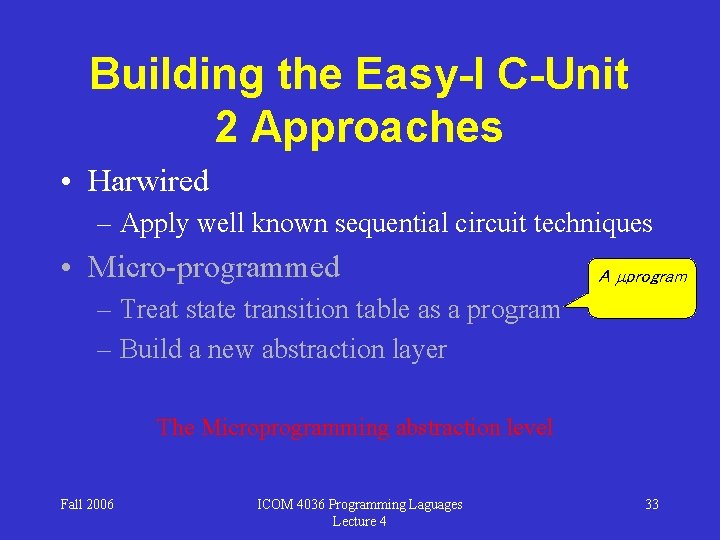

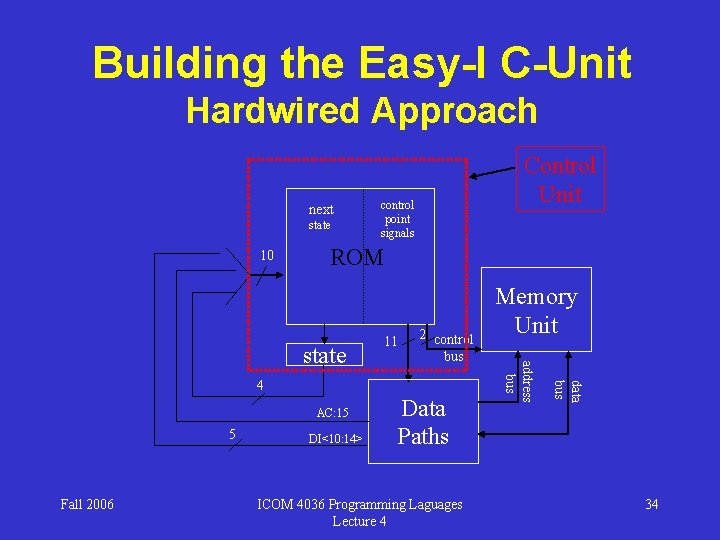

Building the Easy-I C-Unit 2 Approaches • Harwired – Apply well known sequential circuit techniques • Micro-programmed A program – Treat state transition table as a program – Build a new abstraction layer The Microprogramming abstraction level Fall 2006 ICOM 4036 Programming Laguages Lecture 4 33

Building the Easy-I C-Unit Hardwired Approach next state 10 Control Unit control point signals ROM 2 control bus AC: 15 5 Fall 2006 DI<10: 14> Data Paths ICOM 4036 Programming Laguages Lecture 4 data bus 4 address bus state 11 Memory Unit 34

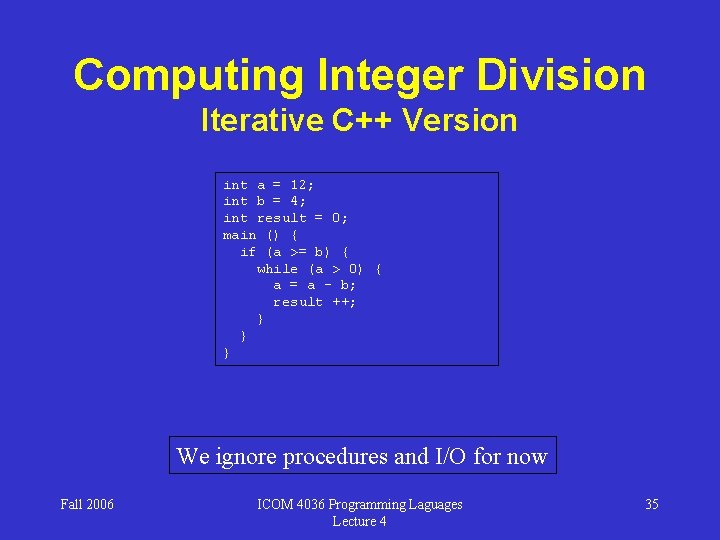

Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } We ignore procedures and I/O for now Fall 2006 ICOM 4036 Programming Laguages Lecture 4 35

Definition Instruction Set Architecture • What it is: – The programmers view of the processor – Visible registers, instruction set, execution model, memory model, I/O model • What it is not: – How the processors if build – The processor’s internal structure Fall 2006 ICOM 4036 Programming Laguages Lecture 4 36

Easy I A Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Format (16 bits) 15 14 I 10 9 opcode 0 X I = Indirect bit Fall 2006 ICOM 4036 Programming Laguages Lecture 4 37

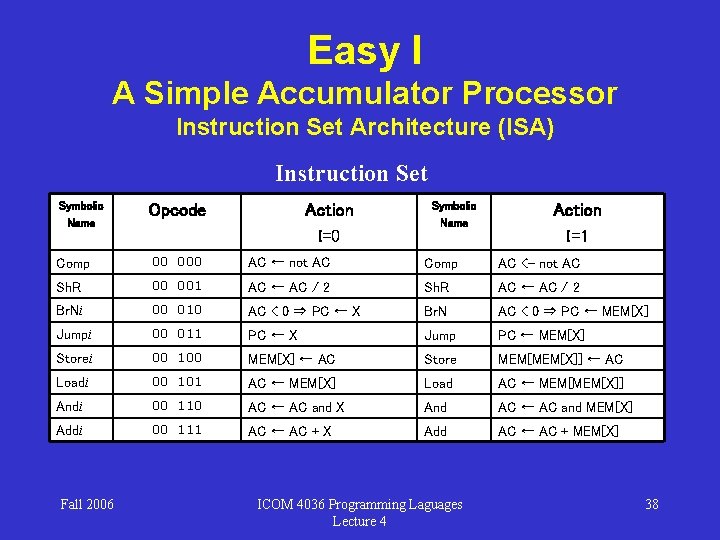

Easy I A Simple Accumulator Processor Instruction Set Architecture (ISA) Instruction Set Symbolic Name Opcode Action I=0 Symbolic Name Action I=1 Comp 00 000 AC ← not AC Comp AC <- not AC Sh. R 00 001 AC ← AC / 2 Sh. R AC ← AC / 2 Br. Ni 00 010 AC < 0 ⇒ PC ← X Br. N AC < 0 ⇒ PC ← MEM[X] Jumpi 00 011 PC ← X Jump PC ← MEM[X] Storei 00 100 MEM[X] ← AC Store MEM[X]] ← AC Loadi 00 101 AC ← MEM[X] Load AC ← MEM[X]] Andi 00 110 AC ← AC and X And AC ← AC and MEM[X] Addi 00 111 AC ← AC + X Add AC ← AC + MEM[X] Fall 2006 ICOM 4036 Programming Laguages Lecture 4 38

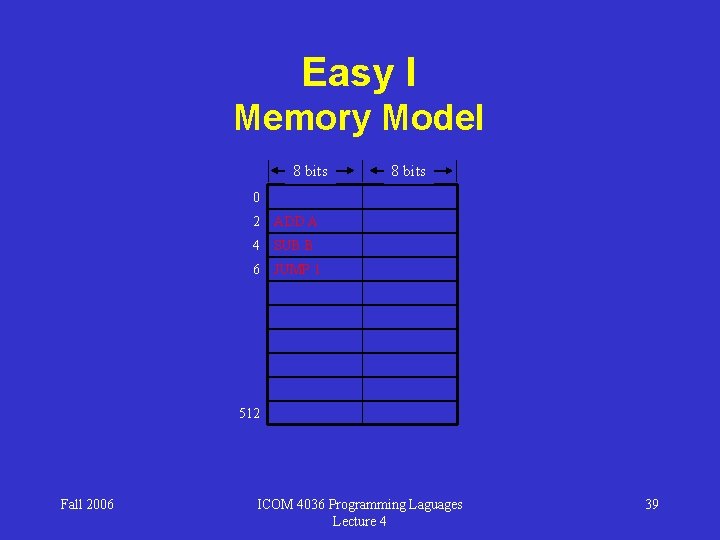

Easy I Memory Model 8 bits 0 2 ADD A 4 SUB B 6 JUMP 1 A B … 512 Fall 2006 ICOM 4036 Programming Laguages Lecture 4 39

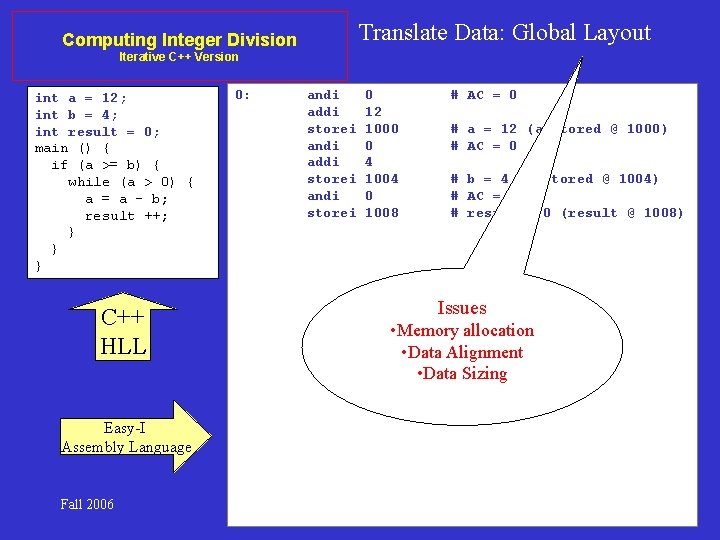

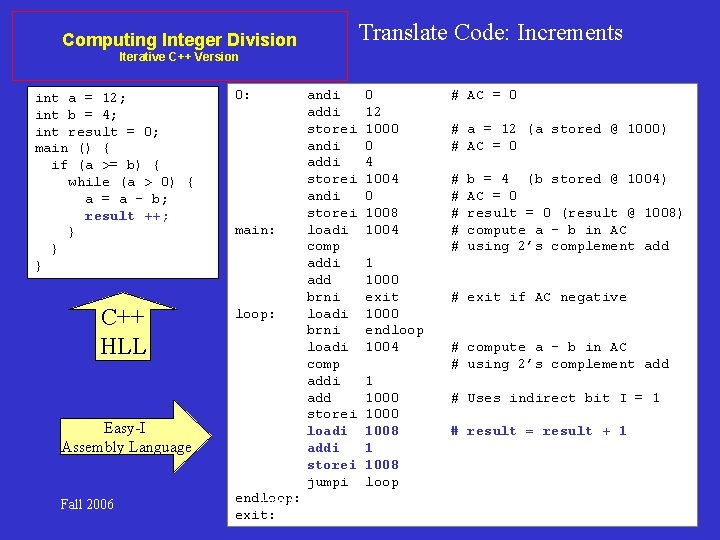

Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language Fall 2006 ICOM 4036 Programming Laguages Lecture 4 40

Translate Data: Global Layout Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL 0: andi addi storei andi storei 0 12 1000 0 4 1004 0 1008 # AC = 0 # a = 12 (a stored @ 1000) # AC = 0 # b = 4 (b stored @ 1004) # AC = 0 # result = 0 (result @ 1008) Issues • Memory allocation • Data Alignment • Data Sizing Easy-I Assembly Language Fall 2006 ICOM 4036 Programming Laguages Lecture 4 41

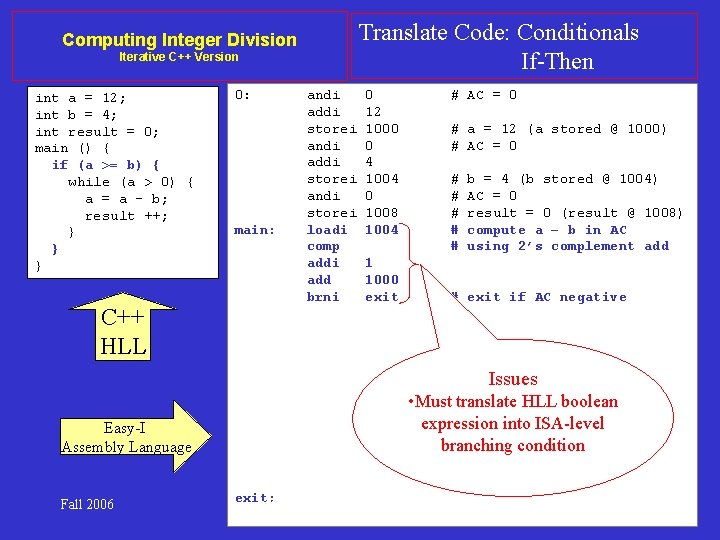

Translate Code: Conditionals If-Then Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL 0: main: andi addi storei andi storei loadi comp addi add brni 0 12 1000 0 4 1004 0 1008 1004 1 1000 exit # AC = 0 # a = 12 (a stored @ 1000) # AC = 0 # # # b = 4 (b stored @ 1004) AC = 0 result = 0 (result @ 1008) compute a – b in AC using 2’s complement add # exit if AC negative Issues Easy-I Assembly Language Fall 2006 • Must translate HLL boolean expression into ISA-level branching condition exit: ICOM 4036 Programming Laguages Lecture 4 42

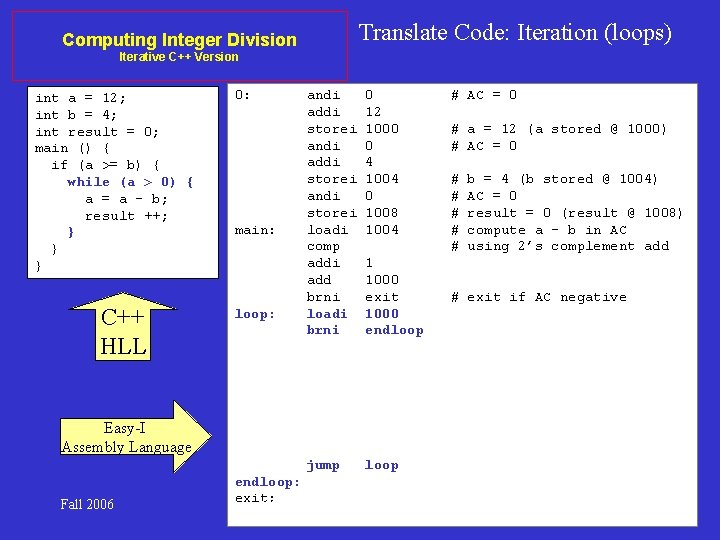

Translate Code: Iteration (loops) Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL 0: main: loop: andi addi storei andi storei loadi comp addi add brni loadi brni 0 12 1000 0 4 1004 0 1008 1004 1 1000 exit 1000 endloop jump loop # AC = 0 # a = 12 (a stored @ 1000) # AC = 0 # # # b = 4 (b stored @ 1004) AC = 0 result = 0 (result @ 1008) compute a – b in AC using 2’s complement add # exit if AC negative Easy-I Assembly Language Fall 2006 endloop: exit: ICOM 4036 Programming Laguages Lecture 4 43

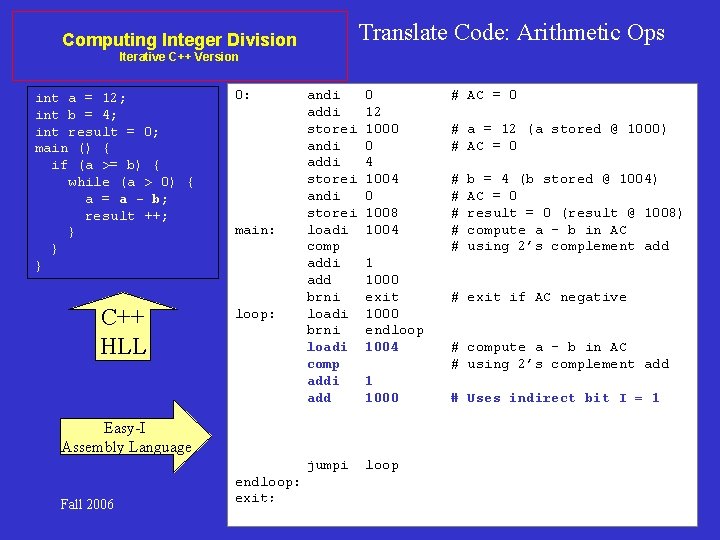

Translate Code: Arithmetic Ops Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL 0: main: loop: andi addi storei andi storei loadi comp addi add brni loadi comp addi add 0 12 1000 0 4 1004 0 1008 1004 1 1000 exit 1000 endloop 1004 1 1000 # AC = 0 # a = 12 (a stored @ 1000) # AC = 0 # # # b = 4 (b stored @ 1004) AC = 0 result = 0 (result @ 1008) compute a – b in AC using 2’s complement add # exit if AC negative # compute a – b in AC # using 2’s complement add # Uses indirect bit I = 1 Easy-I Assembly Language jumpi Fall 2006 loop endloop: exit: ICOM 4036 Programming Laguages Lecture 4 44

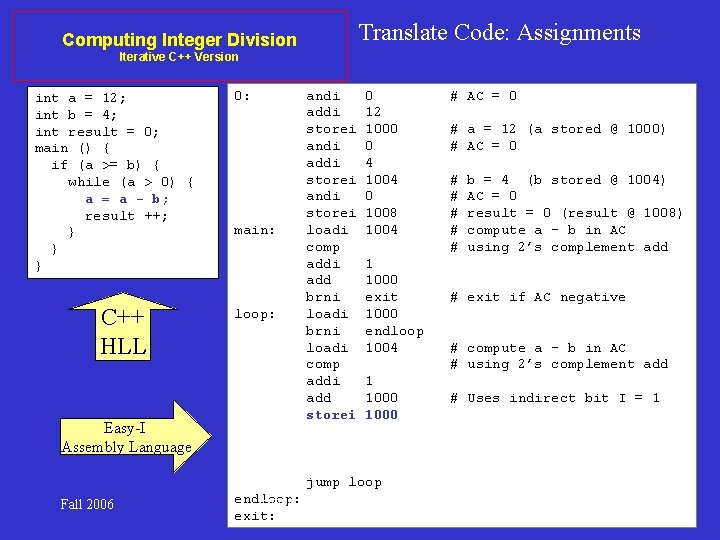

Translate Code: Assignments Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language 0: main: loop: andi addi storei andi storei loadi comp addi add brni loadi comp addi add storei 0 12 1000 0 4 1004 0 1008 1004 1 1000 exit 1000 endloop 1004 1 1000 # AC = 0 # a = 12 (a stored @ 1000) # AC = 0 # # # b = 4 (b stored @ 1004) AC = 0 result = 0 (result @ 1008) compute a – b in AC using 2’s complement add # exit if AC negative # compute a – b in AC # using 2’s complement add # Uses indirect bit I = 1 jump loop Fall 2006 endloop: ICOM 4036 Programming Laguages exit: Lecture 4 45

Translate Code: Increments Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { if (a >= b) { while (a > 0) { a = a - b; result ++; } } } C++ HLL Easy-I Assembly Language Fall 2006 0: main: loop: andi addi storei andi storei loadi comp addi add brni loadi comp addi add storei loadi addi storei jumpi 0 12 1000 0 4 1004 0 1008 1004 1 1000 exit 1000 endloop 1004 1 1000 1008 1 1008 loop # AC = 0 # a = 12 (a stored @ 1000) # AC = 0 # # # b = 4 (b stored @ 1004) AC = 0 result = 0 (result @ 1008) compute a – b in AC using 2’s complement add # exit if AC negative # compute a – b in AC # using 2’s complement add # Uses indirect bit I = 1 # result = result + 1 endloop: ICOM 4036 Programming Laguages exit: Lecture 4 46

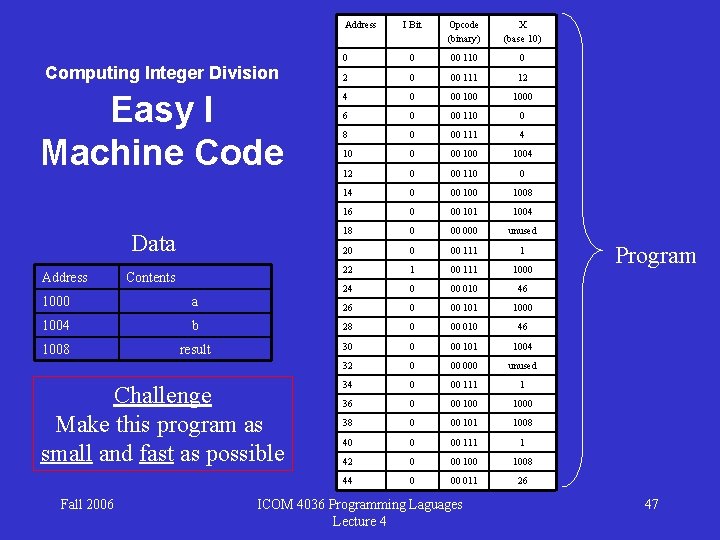

Address Computing Integer Division Easy I Machine Code Data Address Contents I Bit Opcode (binary) X (base 10) 0 0 00 110 0 2 0 00 111 12 4 0 00 1000 6 0 00 110 0 8 0 00 111 4 10 0 00 1004 12 0 00 110 0 14 0 00 1008 16 0 00 101 1004 18 0 00 000 unused 20 0 00 111 1 22 1 00 111 1000 24 0 00 010 46 26 0 00 101 1000 a 1004 b 28 0 00 010 46 1008 result 30 0 00 101 1004 32 0 00 000 unused 34 0 00 111 1 36 0 00 1000 38 0 00 101 1008 40 0 00 111 1 42 0 00 1008 44 0 00 011 26 Challenge Make this program as small and fast as possible Fall 2006 ICOM 4036 Programming Laguages Lecture 4 Program 47

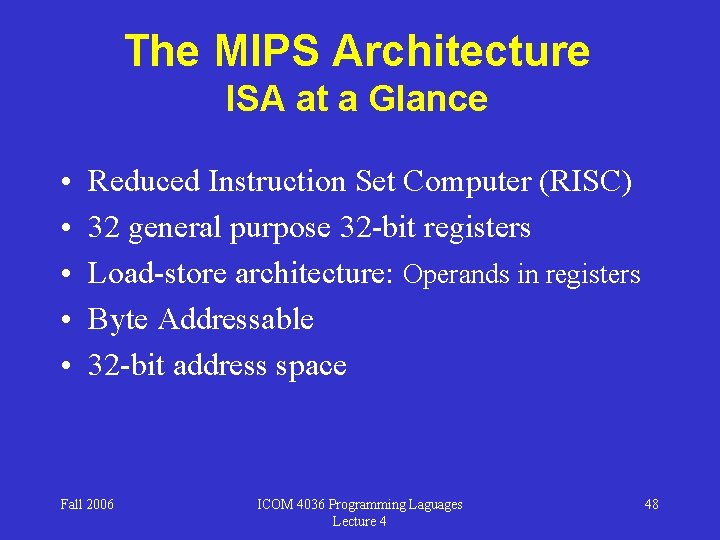

The MIPS Architecture ISA at a Glance • • • Reduced Instruction Set Computer (RISC) 32 general purpose 32 -bit registers Load-store architecture: Operands in registers Byte Addressable 32 -bit address space Fall 2006 ICOM 4036 Programming Laguages Lecture 4 48

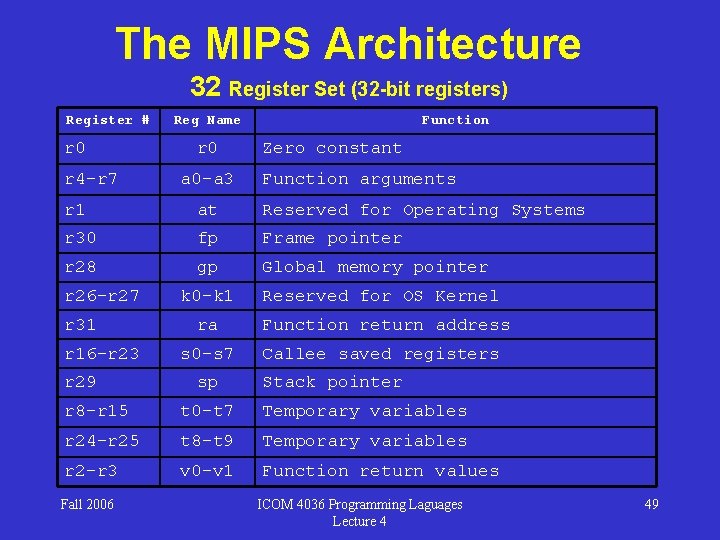

The MIPS Architecture 32 Register Set (32 -bit registers) Register # r 0 r 4 -r 7 Reg Name r 0 a 0 -a 3 Function Zero constant Function arguments r 1 at Reserved for Operating Systems r 30 fp Frame pointer r 28 gp Global memory pointer k 0 -k 1 Reserved for OS Kernel ra Function return address s 0 -s 7 Callee saved registers r 26 -r 27 r 31 r 16 -r 23 r 29 sp Stack pointer r 8 -r 15 t 0 -t 7 Temporary variables r 24 -r 25 t 8 -t 9 Temporary variables r 2 -r 3 v 0 -v 1 Function return values Fall 2006 ICOM 4036 Programming Laguages Lecture 4 49

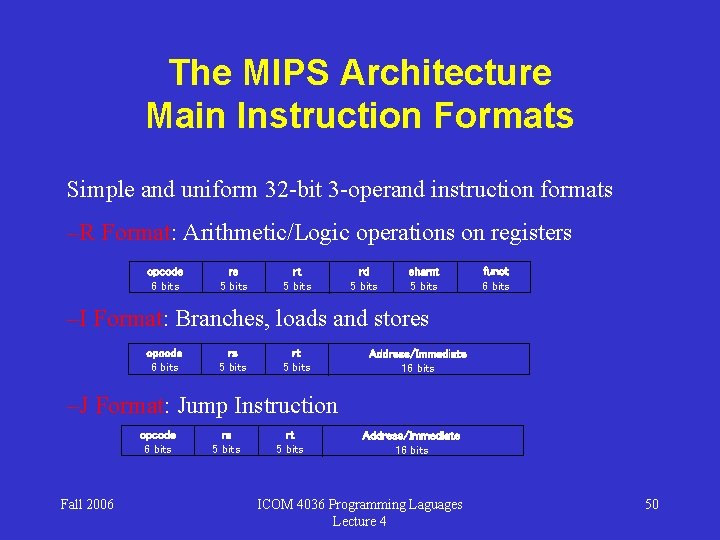

The MIPS Architecture Main Instruction Formats Simple and uniform 32 -bit 3 -operand instruction formats –R Format: Arithmetic/Logic operations on registers opcode 6 bits rs 5 bits rt 5 bits rd 5 bits shamt 5 bits funct 6 bits –I Format: Branches, loads and stores opcode 6 bits rs 5 bits rt 5 bits Address/Immediate 16 bits –J Format: Jump Instruction opcode 6 bits Fall 2006 rs 5 bits rt 5 bits Address/Immediate 16 bits ICOM 4036 Programming Laguages Lecture 4 50

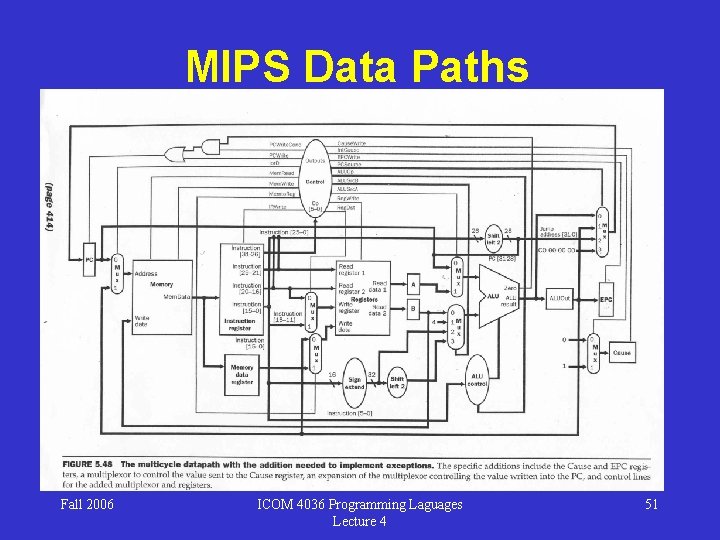

MIPS Data Paths Fall 2006 ICOM 4036 Programming Laguages Lecture 4 51

Mips Packaging Fall 2006 ICOM 4036 Programming Laguages Lecture 4 52

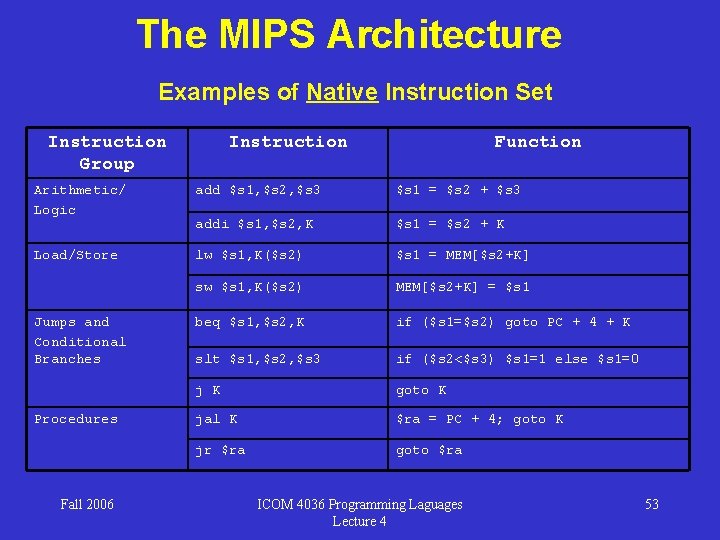

The MIPS Architecture Examples of Native Instruction Set Instruction Group Instruction Function Arithmetic/ Logic add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 addi $s 1, $s 2, K $s 1 = $s 2 + K Load/Store lw $s 1, K($s 2) $s 1 = MEM[$s 2+K] sw $s 1, K($s 2) MEM[$s 2+K] = $s 1 beq $s 1, $s 2, K if ($s 1=$s 2) goto PC + 4 + K slt $s 1, $s 2, $s 3 if ($s 2<$s 3) $s 1=1 else $s 1=0 j K goto K jal K $ra = PC + 4; goto K jr $ra goto $ra Jumps and Conditional Branches Procedures Fall 2006 ICOM 4036 Programming Laguages Lecture 4 53

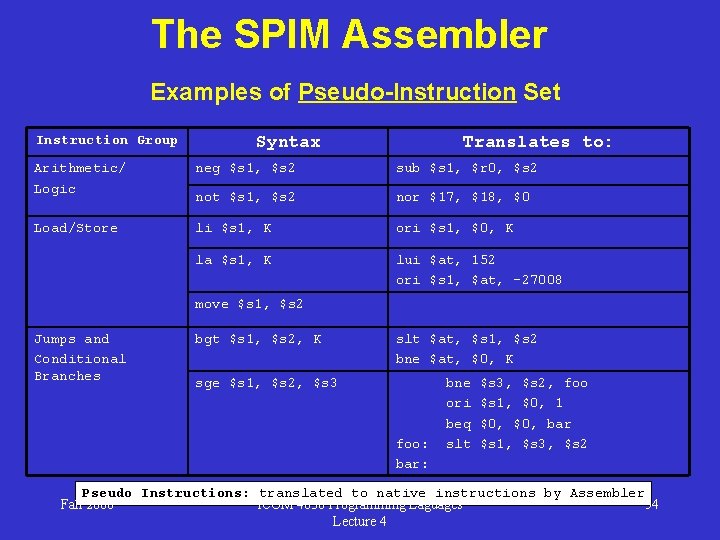

The SPIM Assembler Examples of Pseudo-Instruction Set Instruction Group Syntax Translates to: Arithmetic/ Logic neg $s 1, $s 2 sub $s 1, $r 0, $s 2 not $s 1, $s 2 nor $17, $18, $0 Load/Store li $s 1, K ori $s 1, $0, K la $s 1, K lui $at, 152 ori $s 1, $at, -27008 move $s 1, $s 2 Jumps and Conditional Branches bgt $s 1, $s 2, K slt $at, $s 1, $s 2 bne $at, $0, K sge $s 1, $s 2, $s 3 foo: bar: bne ori beq slt $s 3, $s 2, foo $s 1, $0, 1 $0, bar $s 1, $s 3, $s 2 Pseudo Instructions: translated to native instructions by Assembler Fall 2006 ICOM 4036 Programming Laguages 54 Lecture 4

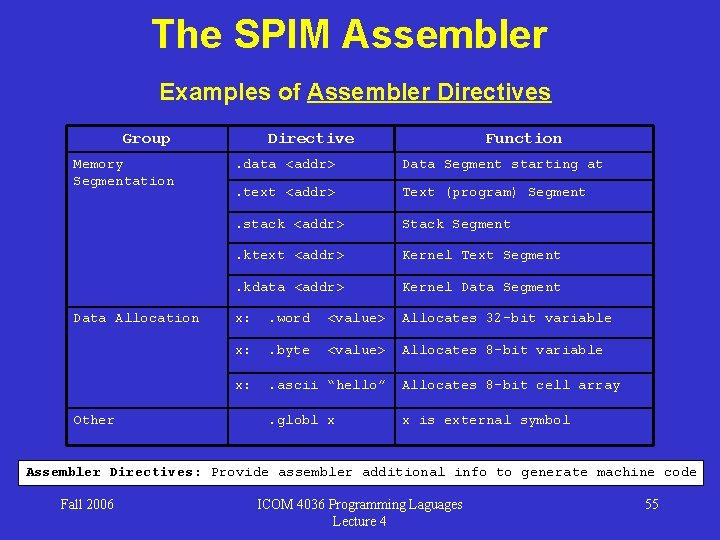

The SPIM Assembler Examples of Assembler Directives Group Memory Segmentation Data Allocation Other Directive Function . data <addr> Data Segment starting at . text <addr> Text (program) Segment . stack <addr> Stack Segment . ktext <addr> Kernel Text Segment . kdata <addr> Kernel Data Segment x: . word <value> Allocates 32 -bit variable x: . byte <value> Allocates 8 -bit variable x: . ascii “hello” Allocates 8 -bit cell array . globl x x is external symbol Assembler Directives: Provide assembler additional info to generate machine code Fall 2006 ICOM 4036 Programming Laguages Lecture 4 55

Handy MIPS ISA References Fall 2006 • Appendix A: Patterson & Hennessy • SPIM ISA Summary on class website • Patterson & Hennessy Back Cover ICOM 4036 Programming Laguages Lecture 4 56

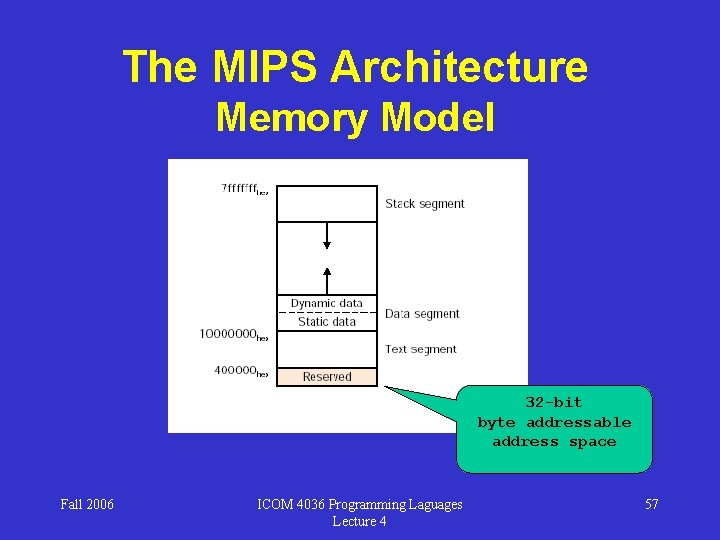

The MIPS Architecture Memory Model 32 -bit byte addressable address space Fall 2006 ICOM 4036 Programming Laguages Lecture 4 57

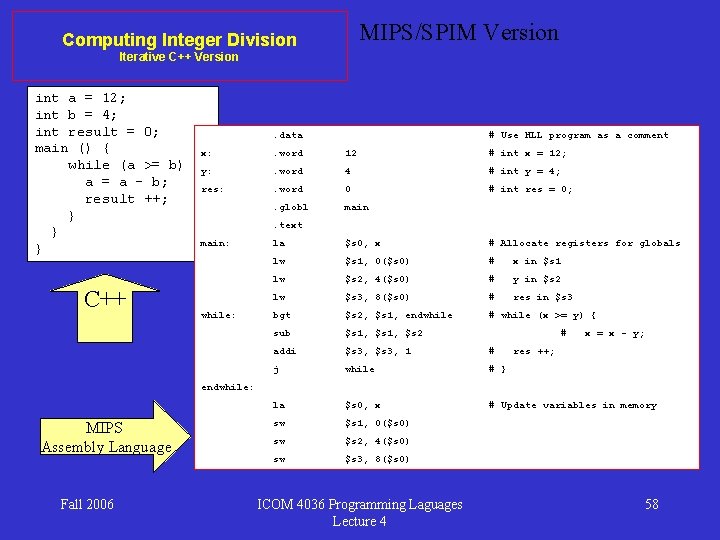

MIPS/SPIM Version Computing Integer Division Iterative C++ Version int a = 12; int b = 4; int result = 0; main () { x: while (a >= b) {y: a = a - b; res: result ++; } } main: } C++ while: . data # Use HLL program as a comment . word 12 # int x = 12; . word 4 # int y = 4; . word 0 # int res = 0; . globl main . text la $s 0, x # Allocate registers for globals lw $s 1, 0($s 0) # x in $s 1 lw $s 2, 4($s 0) # y in $s 2 lw $s 3, 8($s 0) # res in $s 3 bgt $s 2, $s 1, endwhile # while (x >= y) { sub $s 1, $s 2 addi $s 3, 1 # j while # } la $s 0, x # Update variables in memory sw $s 1, 0($s 0) sw $s 2, 4($s 0) sw $s 3, 8($s 0) # x = x - y; res ++; endwhile: MIPS Assembly Language Fall 2006 ICOM 4036 Programming Laguages Lecture 4 58

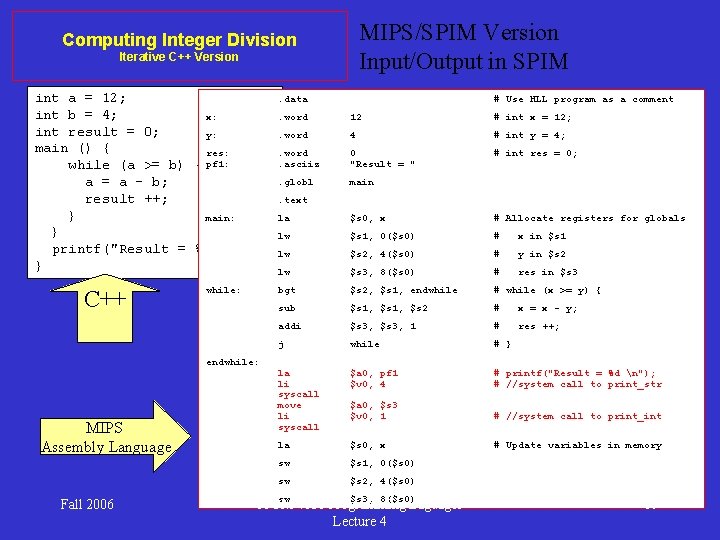

MIPS/SPIM Version Input/Output in SPIM Computing Integer Division Iterative C++ Version int a = 12; int b = 4; x: int result = 0; y: main () { res: while (a >= b) { pf 1: a = a - b; result ++; } main: } printf("Result = %d n"); } C++ while: endwhile: MIPS Assembly Language Fall 2006 . data # Use HLL program as a comment . word 12 # int x = 12; . word 4 # int y = 4; . word. asciiz 0 "Result = " # int res = 0; . globl main . text la $s 0, x # Allocate registers for globals lw $s 1, 0($s 0) # x in $s 1 lw $s 2, 4($s 0) # y in $s 2 lw $s 3, 8($s 0) # res in $s 3 bgt $s 2, $s 1, endwhile # while (x >= y) { sub $s 1, $s 2 # x = x - y; addi $s 3, 1 # res ++; j while # } la li syscall move li syscall $a 0, pf 1 $v 0, 4 # printf("Result = %d n"); # //system call to print_str $a 0, $s 3 $v 0, 1 # //system call to print_int la $s 0, x # Update variables in memory sw $s 1, 0($s 0) sw $s 2, 4($s 0) sw $s 3, 8($s 0) ICOM 4036 Programming Laguages Lecture 4 59

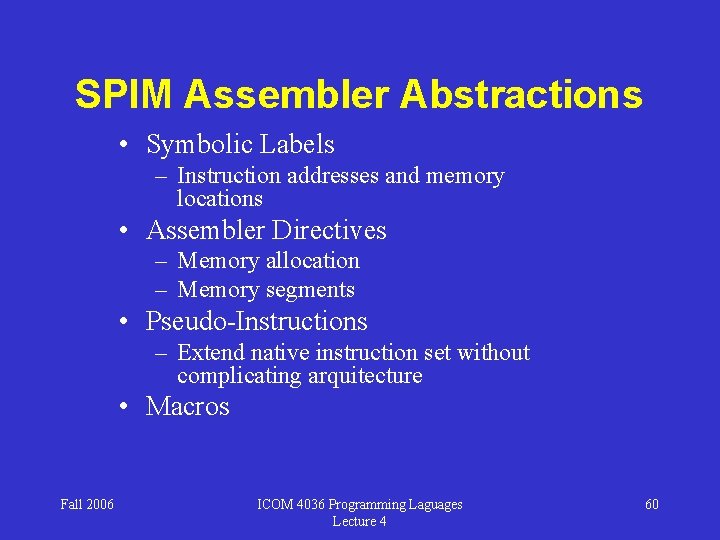

SPIM Assembler Abstractions • Symbolic Labels – Instruction addresses and memory locations • Assembler Directives – Memory allocation – Memory segments • Pseudo-Instructions – Extend native instruction set without complicating arquitecture • Macros Fall 2006 ICOM 4036 Programming Laguages Lecture 4 60

- Slides: 60