Low Voltage Low Power Dram Robert Mills Presentation

Low Voltage Low Power Dram Robert Mills Presentation for: High Speed and Low Power VLSI design course Instructor: Prof. M. Shams

Introduction t. Rapidly growing area of Power Aware systems t. DRAM Design Evolution t. Goal: Identify Power Sources in Drams t. Present Design Solutions t. Examine Ultra Low Power issues (Future Concerns) t. Proposed Project Plan and Schedule

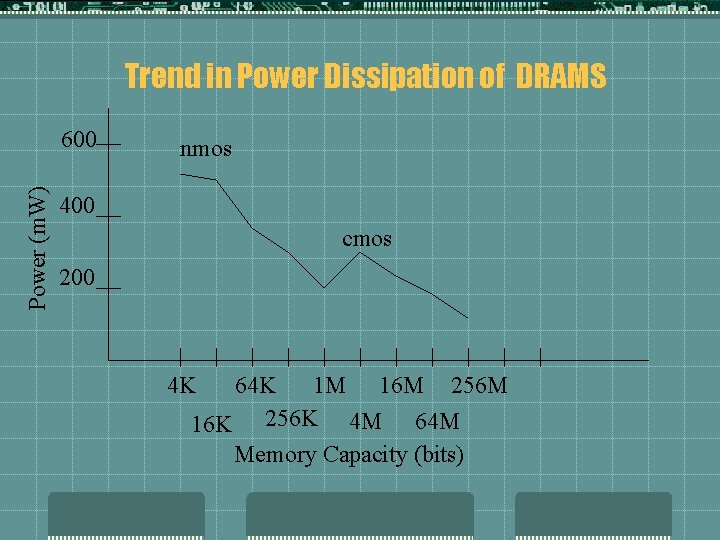

DRAM Evolution t Market t 1973 t 1986 object: Minimize cost / bit stored 4 Kb, NMOS, 1 T 1 C Cell, 460 m. W, 300 ns 1 Mb, CMOS, Boosted circuits, Vdd / 2 bit line reference, 200 m. W, 100 ns t 1996 64 Mb, Cell over bit line, 512 cells per column, 180 m. W, 60 ns t 2001 4 Gb, Twisted Open Bit line, 270 m. W, trc= 70 ns

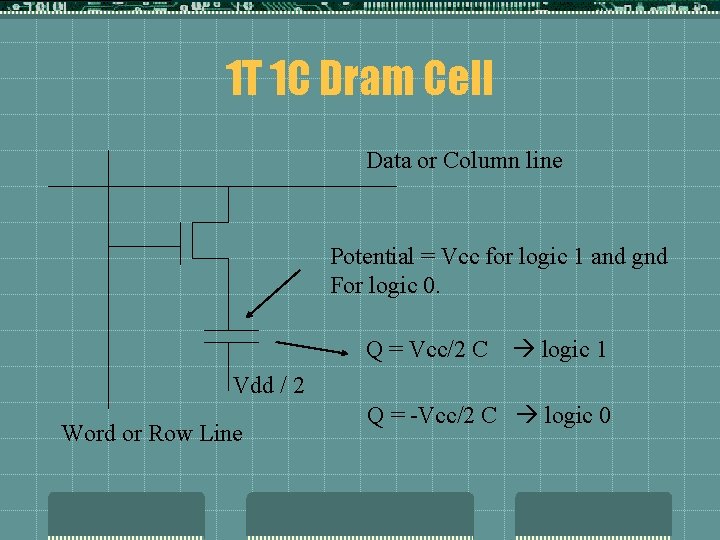

1 T 1 C Dram Cell Data or Column line Potential = Vcc for logic 1 and gnd For logic 0. Q = Vcc/2 C logic 1 Vdd / 2 Word or Row Line Q = -Vcc/2 C logic 0

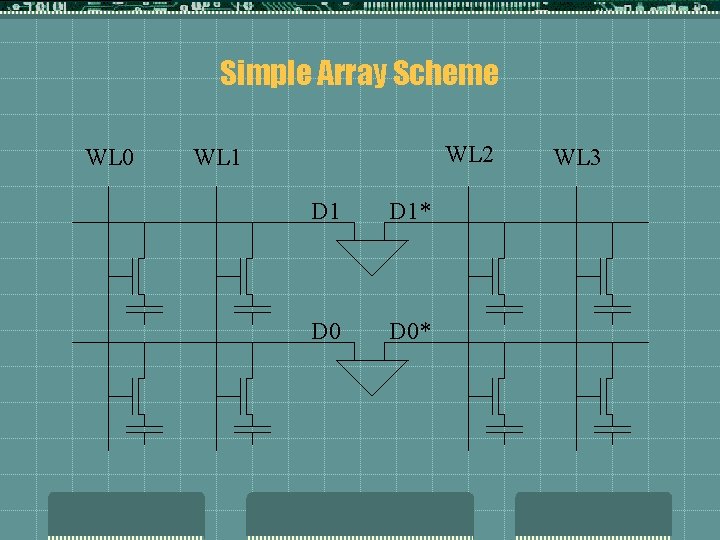

Simple Array Scheme WL 0 WL 2 WL 1 D 1* D 0* WL 3

Trend in Power Dissipation of DRAMS Power (m. W) 600 nmos 400 cmos 200 4 K 64 K 1 M 16 M 256 M 16 K 256 K 4 M 64 M Memory Capacity (bits)

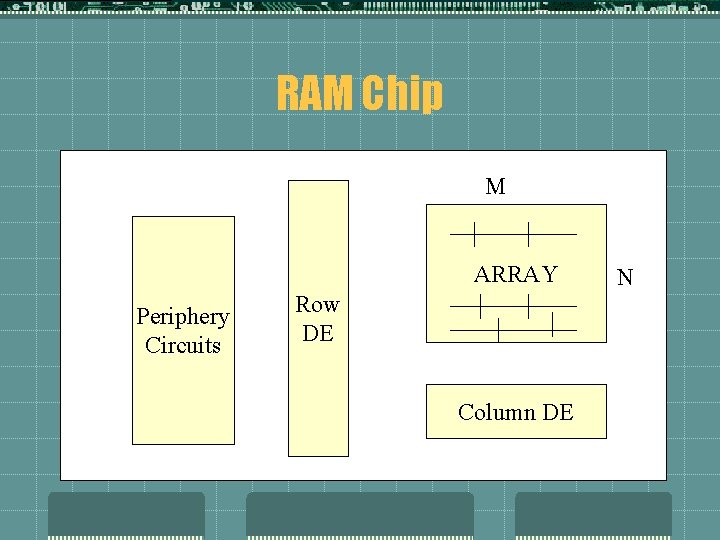

RAM Chip M ARRAY Periphery Circuits Row DE Column DE N

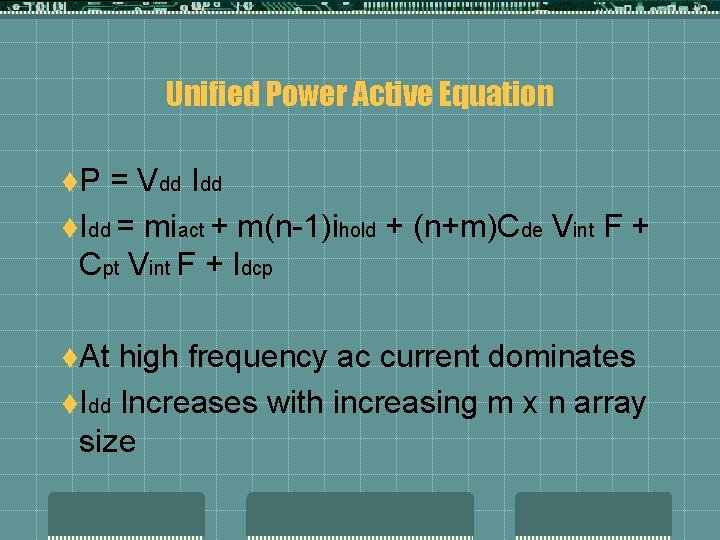

Unified Power Active Equation t. P = Vdd Idd t. Idd = miact + m(n-1)ihold + (n+m)Cde Vint F + Cpt Vint F + Idcp t. At high frequency ac current dominates t. Idd Increases with increasing m x n array size

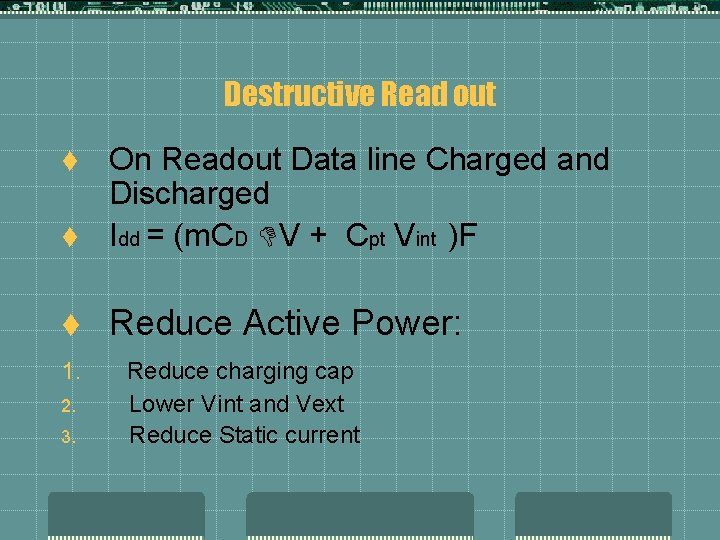

Destructive Read out t On Readout Data line Charged and Discharged Idd = (m. CD DV + Cpt Vint )F t Reduce Active Power: t 1. 2. 3. Reduce charging cap Lower Vint and Vext Reduce Static current

Data Retention Power sources t. The Refresh Operation reads data of m cells on the nth word line t. An Idd flows each time m cells are refreshed t. Frequency refresh current is n / tref

Low Power Dram Circuits t. Charge Capacitance Reduction by partial activation of Multi-divided data line. t. Increase in memory cells directly increases the CD t. Divide one data line into several sections & activate only one sub-section.

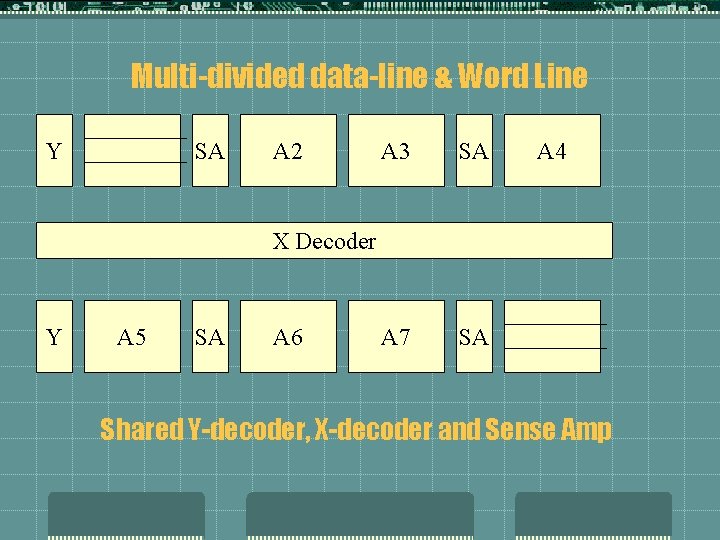

Multi-divided data-line & Word Line Y SA A 2 A 3 SA A 7 SA A 4 X Decoder Y A 5 SA A 6 Shared Y-decoder, X-decoder and Sense Amp

Reduction in CDT & QDT t. Employing Partial Activation + t. Multi divided data line and Word lines t. For 256 Mb DRAM design Cdt expected drop from 3000 pf to 100 pf. t. Charge Reduction on Qdt from 3100 p. C to 102 p. C for experimental 256 Mb DRAM

Operating Voltage Reduction t. Reduction in Vdd helps reduces Decoder and Perpheral logic power. t. CMOS vs n. MOS decoders t. Half Vdd data-line pre charge lower power in memory array t. CMOS circuit - P = 0. 46 : A = 0. 7 t. NMOS circuit - P = 1 : A = 1

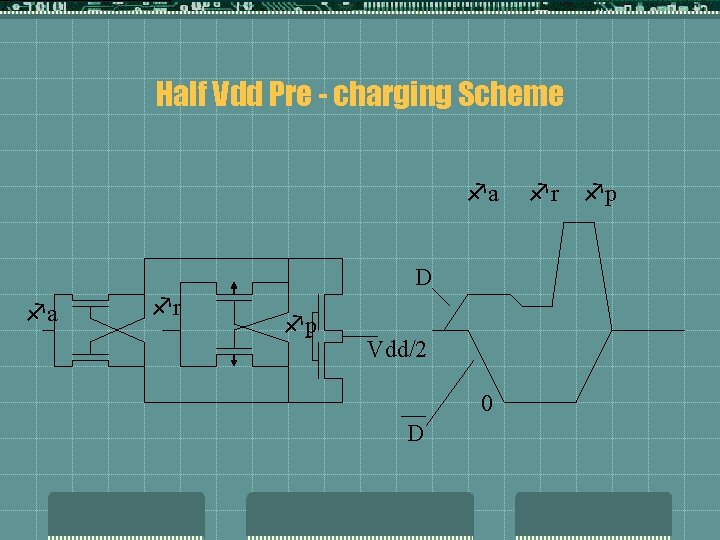

Half Vdd Pre - charging Scheme fa D fa fr fp Vdd/2 0 D fr fp

DC Current Reduction t. Column signal path circuitry main source of static current. t. DC current flows from the I/O line load to the data lines while column is switched on. t. Use Address Transition Detection (ATD) circuitry to activate column switch and main amplifier.

Data Reduction Power Retention t. Use Voltage conversion circuits t. Use Refresh Time extension t. Refresh Charge Reduction

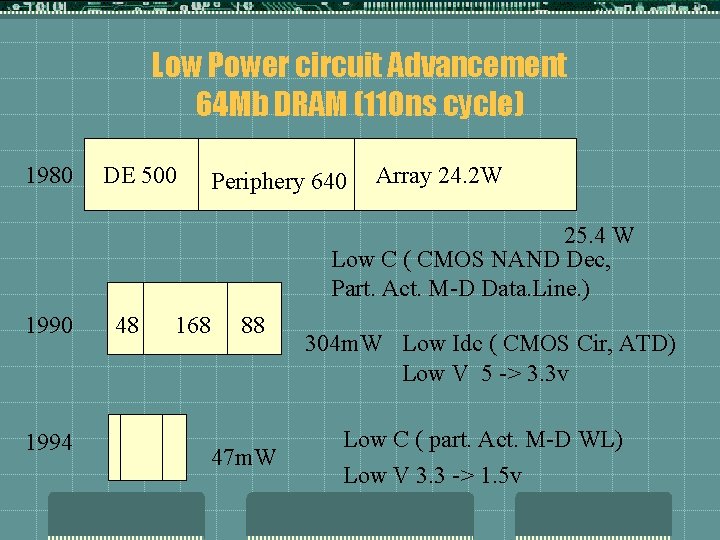

Low Power circuit Advancement 64 Mb DRAM (110 ns cycle) 1980 DE 500 Periphery 640 Array 24. 2 W 25. 4 W Low C ( CMOS NAND Dec, Part. Act. M-D Data. Line. ) 1990 1994 48 168 88 47 m. W 304 m. W Low Idc ( CMOS Cir, ATD) Low V 5 -> 3. 3 v Low C ( part. Act. M-D WL) Low V 3. 3 -> 1. 5 v

Ultra Low Power Concerns t. V t Scaling is major concern for achieving ultra-low voltage power VLSI’s. t. DC chip current due to sub threshold current Idc increases exponentially with Vt reduction when Vdd is lowered. t. This problem affects data retention current as well as active current.

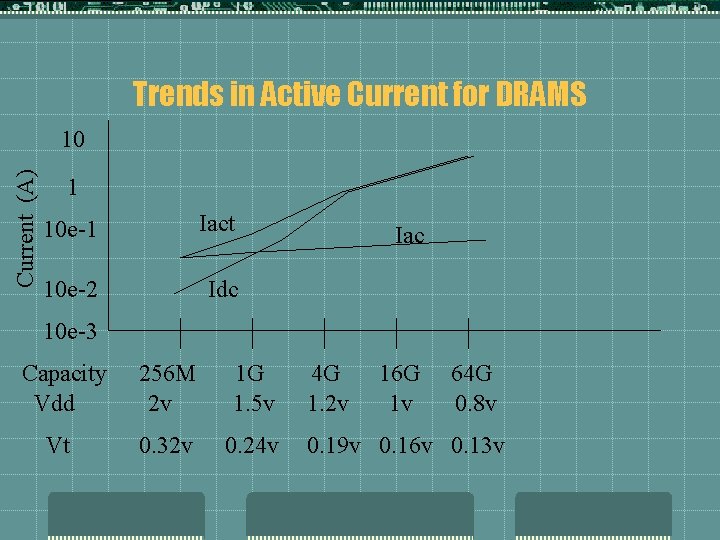

Trends in Active Current for DRAMS Current (A) 10 1 10 e-1 Iact 10 e-2 Idc Iac 10 e-3 Capacity Vdd 256 M 2 v 1 G 1. 5 v Vt 0. 32 v 0. 24 v 4 G 1. 2 v 16 G 1 v 64 G 0. 8 v 0. 19 v 0. 16 v 0. 13 v

Retention Problem t. In a Cell, sub-threshold leakage current flow from the capacitor to the data line. t. This degrades the data retention time t. Drams cells require highest Vt DL 0 WL 1 Cs

Two Reduction schemes t. The dynamic Vt scheme t. In active mode Vt is set low. In stand-by mode the Vt is raised t. The Static Vt scheme t. Categorized as power-switch and multi Vt scheme.

Conclusion t. Source for power dissipation in Drams have been examined t. Architectures and Circuits have been reviewed to address these power hungry area. t. Future Dram designer need to address Increasing sub-threshold current as Idc >> Iac.

Project Plan & Schedule t Design an Address Decoder and Optimize for low power DRAM application. t Define design problem: 1 st – 7 th April t Optimize & design Decoder: 8 -15 th April t Simulate both designs: 16 -22 th April t Present Results week of 23 rd April t Submit in report on 5 th May

References t t t “Fast Low Power Decoders for Rams”, M. Horowitz, IEEE JSSC, Vol, 36, No. 10, Oct 2001 “Low Voltage Memories for Power-Aware Systems”, Itoh, ISLPED ’ 02, August 12 -14, 2002, Monterey, California, USA. “A 4 Gb DDR SDRAM with Gain controlled Pre-Sensing and Ref. Bitline Calibration Schemes in the twisted Open Bitline Architecture”, H. Yoon et al. , IEEE, ISSCC-2001 Session 24/DRAM/24. 1, Feb. 2001 “Limitations and Challenges of Multigigabit DRAM Chip Design”, Itoh, IEEE JSSC, Vol. 32, No. 5, May 1997. “Trends in Low Power RAM Circuit Technologies”, Itoh et al, Proceedings of the IEEE, Vol. 83, No. 4 April 1995.

- Slides: 25