Low PowerEnergy Scheduling for RealTime Systems Aleksandra Teanovi

- Slides: 19

Low Power/Energy Scheduling for Real-Time Systems Aleksandra Tešanović Real-Time Systems Laboratory Department of Computer and Information Science Linköpings universitet Sweden Aleksandra Tešanović

Talk Outline • Variable Voltage Processors • Static Voltage Scheduling • Dynamic Voltage Scheduling Aleksandra Tešanović 2

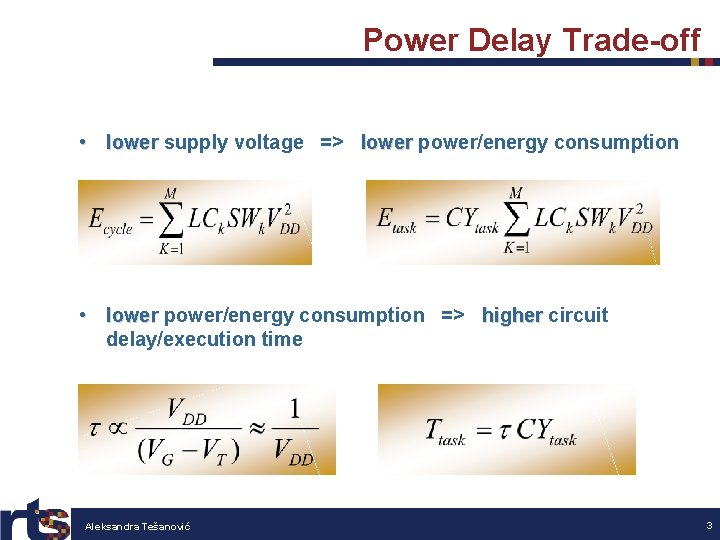

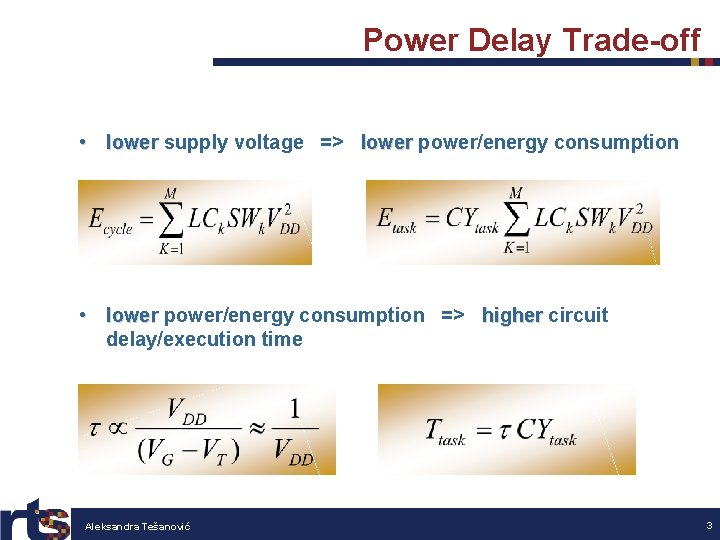

Power Delay Trade-off • lower supply voltage => lower power/energy consumption • lower power/energy consumption => higher circuit delay/execution time Aleksandra Tešanović 3

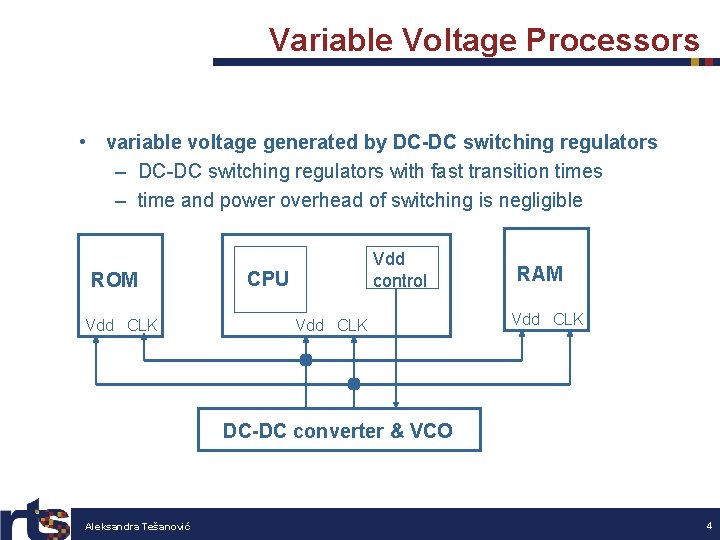

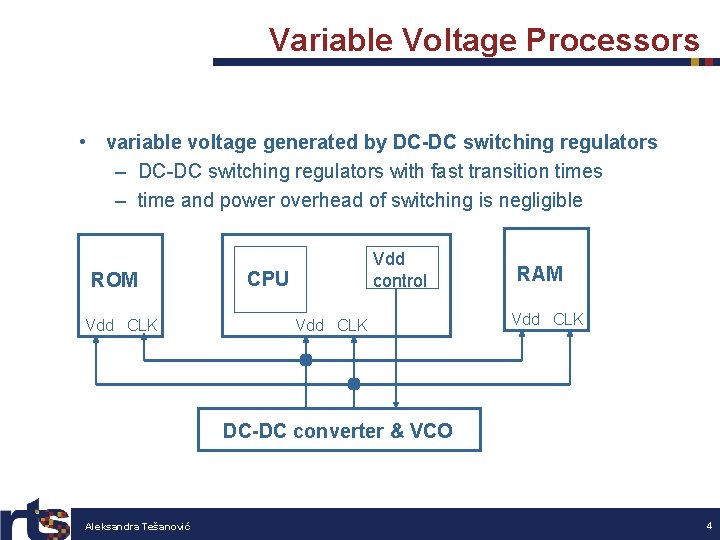

Variable Voltage Processors • variable voltage generated by DC-DC switching regulators – DC-DC switching regulators with fast transition times – time and power overhead of switching is negligible ROM Vdd CLK Vdd control CPU Vdd CLK RAM Vdd CLK DC-DC converter & VCO Aleksandra Tešanović 4

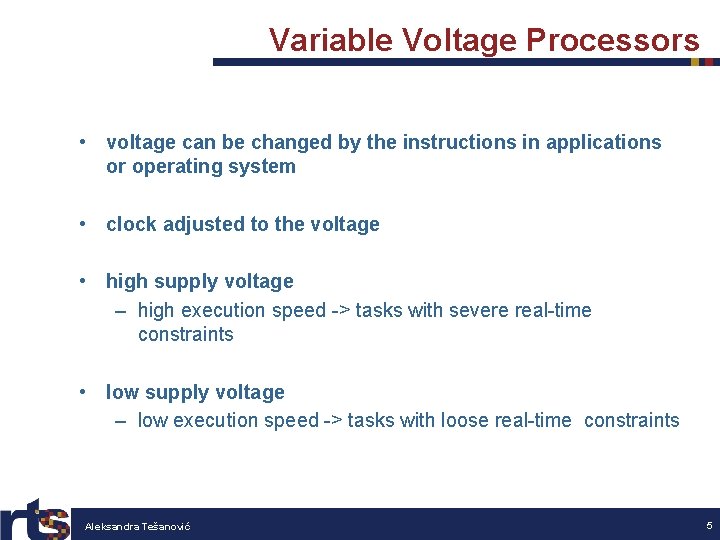

Variable Voltage Processors • voltage can be changed by the instructions in applications or operating system • clock adjusted to the voltage • high supply voltage – high execution speed -> tasks with severe real-time constraints • low supply voltage – low execution speed -> tasks with loose real-time constraints Aleksandra Tešanović 5

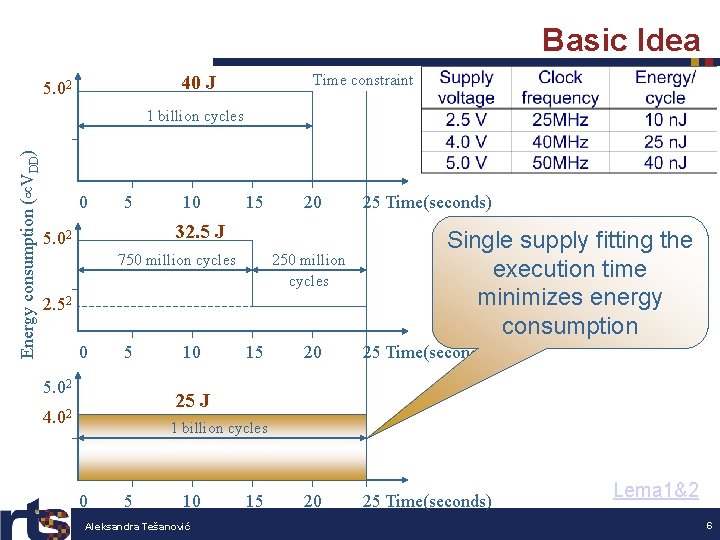

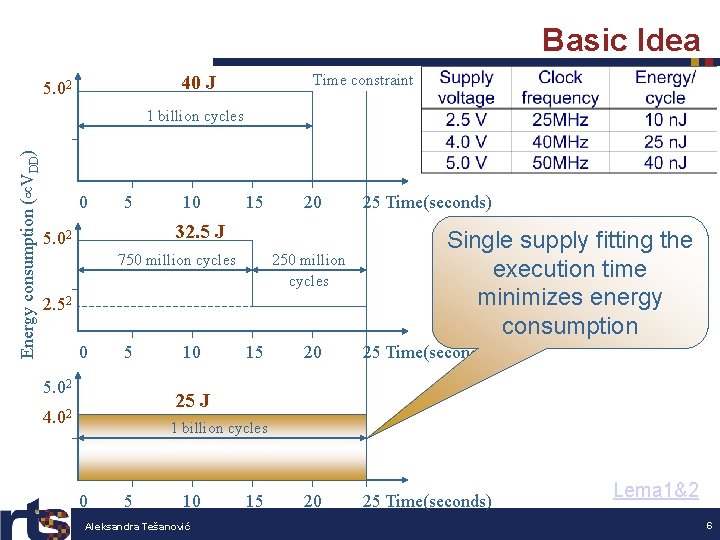

Basic Idea Time constraint 40 J 5. 02 Energy consumption ( VDD) 1 billion cycles 0 5 10 15 20 32. 5 J 5. 02 250 million cycles 750 million cycles 2. 52 0 5 5. 02 10 15 25 Time(seconds) Single supply fitting the execution time minimizes energy consumption 20 25 Time(seconds) 25 J 4. 02 1 billion cycles 0 5 10 Aleksandra Tešanović 15 Lema 1&2 6

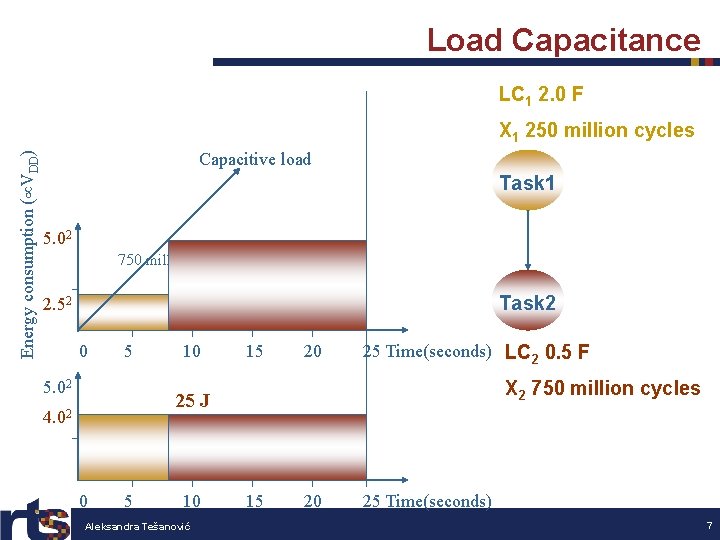

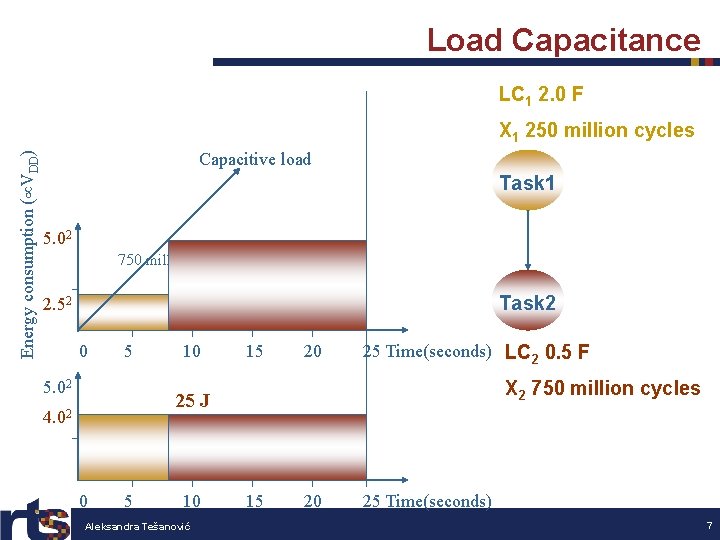

Load Capacitance LC 1 2. 0 F Energy consumption ( VDD) X 1 250 million cycles Capacitive load Task 1 5. 02 250 million cycles 750 million cycles Task 2 2. 52 0 5 5. 02 10 15 20 25 Time(seconds) LC 2 0. 5 F X 2 750 million cycles 25 J 4. 02 1 billion cycles 0 5 10 Aleksandra Tešanović 15 20 25 Time(seconds) 7

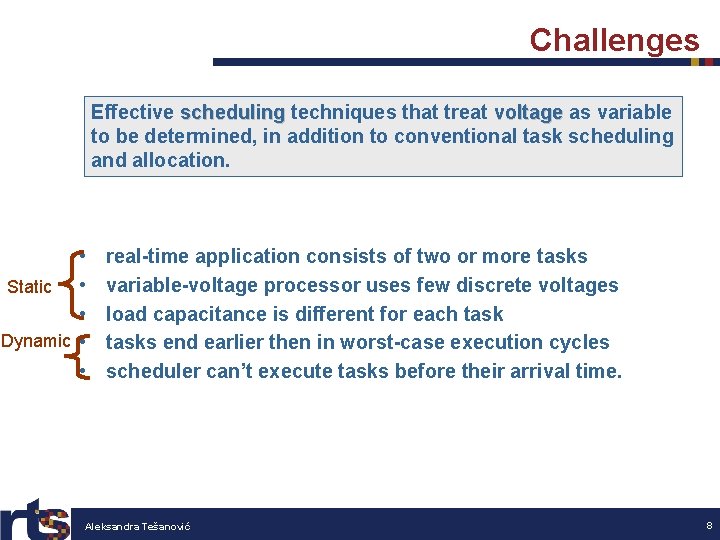

Challenges Effective scheduling techniques that treat voltage as variable to be determined, in addition to conventional task scheduling and allocation. • • Static • Dynamic • • real-time application consists of two or more tasks variable-voltage processor uses few discrete voltages load capacitance is different for each tasks end earlier then in worst-case execution cycles scheduler can’t execute tasks before their arrival time. Aleksandra Tešanović 8

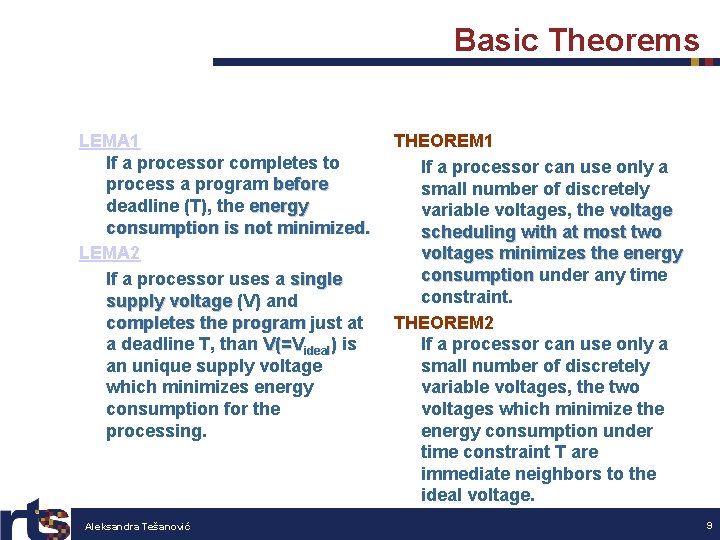

Basic Theorems LEMA 1 If a processor completes to process a program before deadline (T), the energy consumption is not minimized. LEMA 2 If a processor uses a single supply voltage (V) and completes the program just at a deadline T, than V(=Videal) is an unique supply voltage which minimizes energy consumption for the processing. Aleksandra Tešanović THEOREM 1 If a processor can use only a small number of discretely variable voltages, the voltage scheduling with at most two voltages minimizes the energy consumption under any time constraint. THEOREM 2 If a processor can use only a small number of discretely variable voltages, the two voltages which minimize the energy consumption under time constraint T are immediate neighbors to the ideal voltage. 9

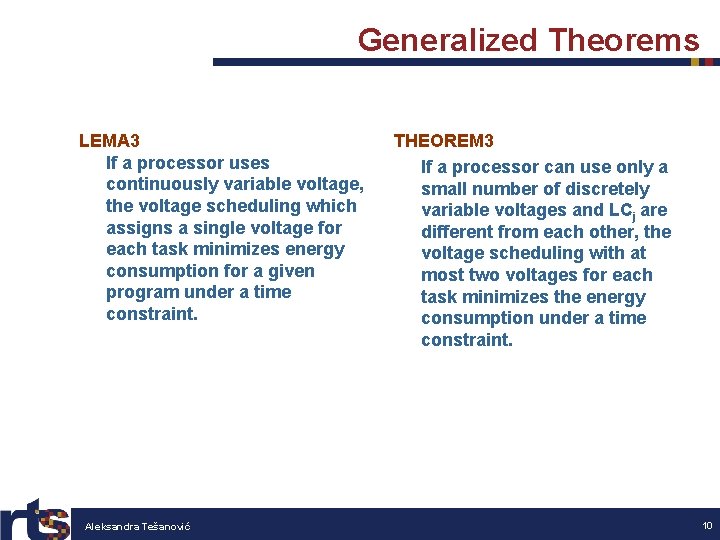

Generalized Theorems LEMA 3 If a processor uses continuously variable voltage, the voltage scheduling which assigns a single voltage for each task minimizes energy consumption for a given program under a time constraint. Aleksandra Tešanović THEOREM 3 If a processor can use only a small number of discretely variable voltages and LCj are different from each other, the voltage scheduling with at most two voltages for each task minimizes the energy consumption under a time constraint. 10

Voltage Scheduling Techniques • static voltage scheduling – target systems – ILP problem formulation • dynamic voltage scheduling – target systems – algorithms (SD and DD) Aleksandra Tešanović 11

Static Scheduling - Target System • • hard real-time system can vary its supply voltage dynamically uses only one supply voltage at a time few discrete voltages adaptive clock scheme worst-case execution cycles can be estimated statically no power overhead due to DC-DC switches no time overhead due to voltage and clock changing Aleksandra Tešanović 12

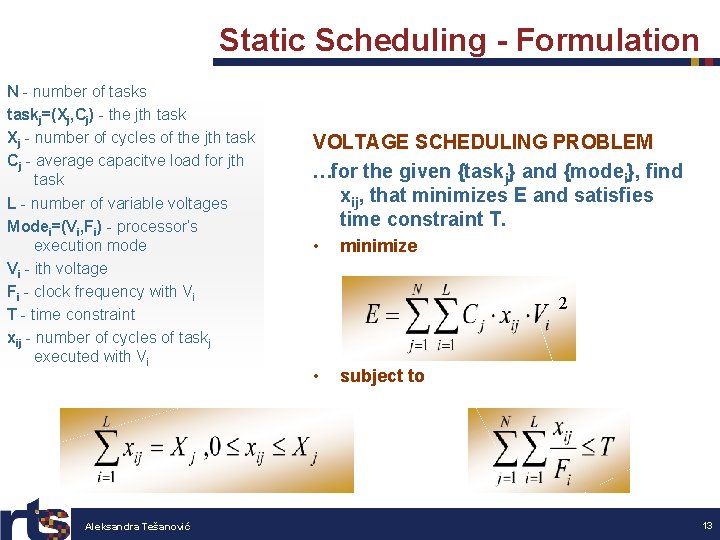

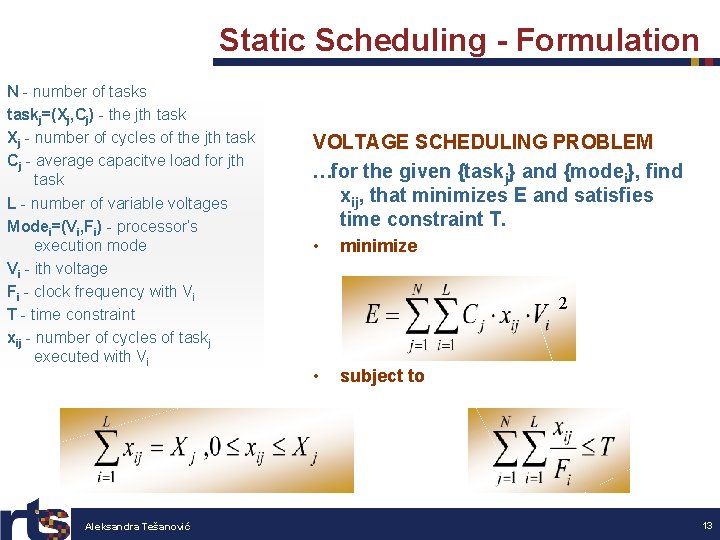

Static Scheduling - Formulation N - number of tasks taskj=(Xj, Cj) - the jth task Xj - number of cycles of the jth task Cj - average capacitve load for jth task L - number of variable voltages Modei=(Vi, Fi) - processor’s execution mode Vi - ith voltage Fi - clock frequency with Vi T - time constraint xij - number of cycles of taskj executed with Vi Aleksandra Tešanović VOLTAGE SCHEDULING PROBLEM …for the given {taskj} and {modei}, find xij, that minimizes E and satisfies time constraint T. • minimize 2 • subject to 13

Static Scheduling - Experimental Results • high number of variable voltages => power reduction • suitable voltage for the time constraint => significant power reduction • tasks with lower capacitance, assigned higher voltage => 30% reduction of energy consumption Aleksandra Tešanović 14

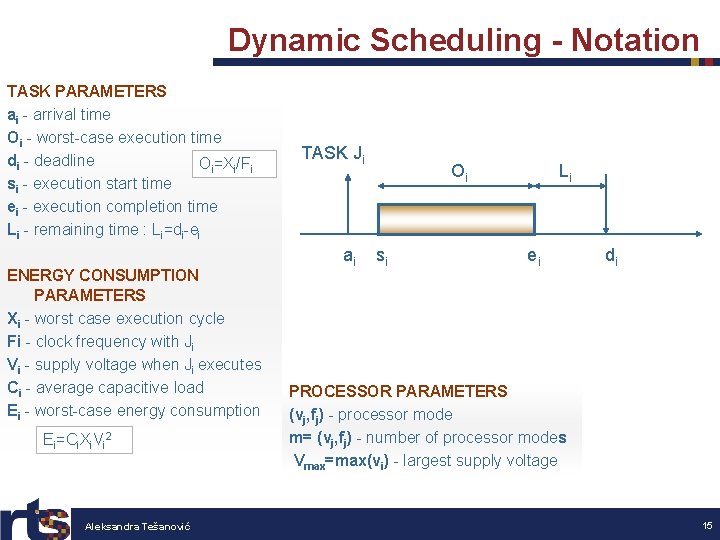

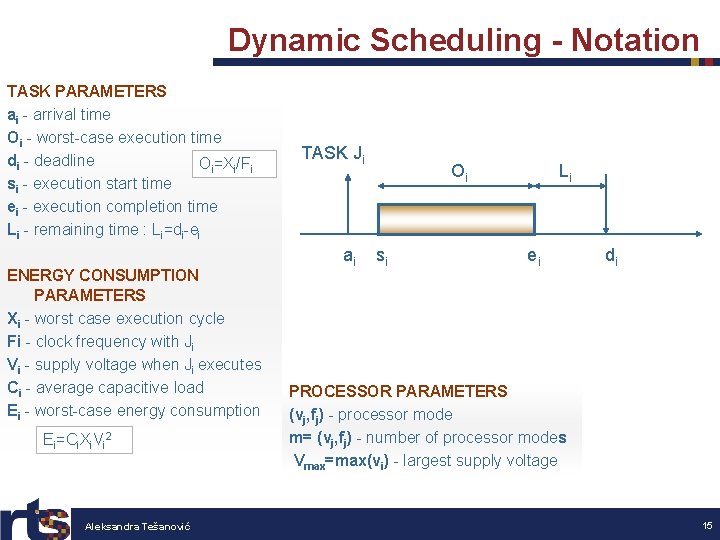

Dynamic Scheduling - Notation TASK PARAMETERS ai - arrival time Oi - worst-case execution time di - deadline Oi=Xi/Fi si - execution start time ei - execution completion time Li - remaining time : Li=di-ei ENERGY CONSUMPTION PARAMETERS Xi - worst case execution cycle Fi - clock frequency with Ji Vi - supply voltage when Ji executes Ci - average capacitive load Ei - worst-case energy consumption Ei=Ci. Xi. Vi 2 Aleksandra Tešanović TASK Ji ai Oi si Li ei di PROCESSOR PARAMETERS (vj, fj) - processor mode m= (vj, fj) - number of processor modes Vmax=max(vi) - largest supply voltage 15

Dynamic Scheduling Algorithms • SD algorithm – arrival times of tasks known • DD algorithm – arrival times of tasks unknown • target systems – real-time system (RTOS + applications) – application programs divided in tasks – task can vary supply voltage – preemptive tasks Aleksandra Tešanović 16

Algorithm Steps • CPU time allocation – all tasks execute on Vmax – execution cycle = worst case • end-time prediction – time slot’s end time for next executed task is predicted • start-time assignment – time slot’s start-time is determined – time slot can be lengthened if the previous task finishes earlier Aleksandra Tešanović 17

Experimental Results • SD algorithm – better results than the normal case – looser deadline constraints => better energy reduction • DD algorithm – better results than the normal case – power consumption independent of deadline constraints Aleksandra Tešanović 18

Summary Aleksandra Tešanović 19