Low Power via SubThreshold Circuits Mike Pridgen Logic

Low Power via Sub-Threshold Circuits Mike Pridgen

• “Logic Circuits Operating in Subthreshold Voltages” – Jabulani Nyathi and Brent Bero • “Sub-Threshold Design: The Challenges of Minimizing Circuit Energy” – B. H. Calhoun, A. Wang, N. Verma, and A. Chandrakasan 2

Goal of Sub-Threshold Circuits • Minimize energy – Utilize leakage currents – Sacrifice speed 3

Uses of Sub-Threshold Circuits • Standalone, low power devices – Wireless sensor nodes – RFID tags • Burst-mode applications – Short, intensive bursts – Long, near-idle periods 4

Sub-Threshold FFT • • • 16 bit FFT lengths of 128 to 1024 350 m. V VDD 10 k. Hz 155 n. J / FFT – 350 x better than microprocessor – 8 x better than ASIC 5

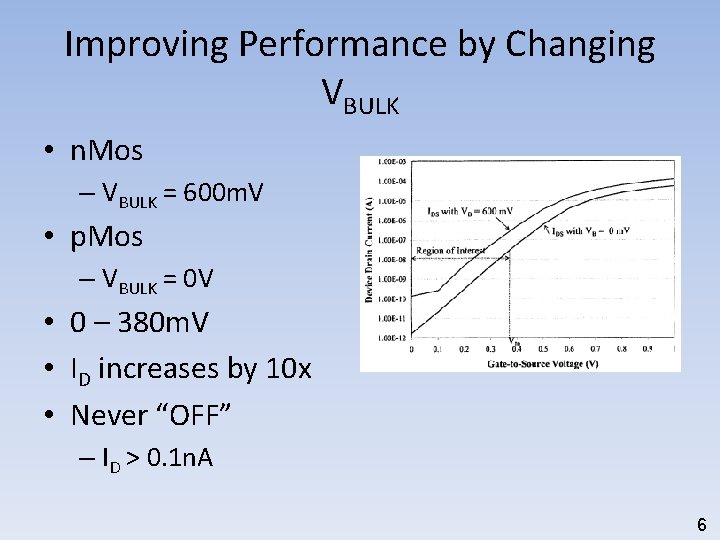

Improving Performance by Changing VBULK • n. Mos – VBULK = 600 m. V • p. Mos – VBULK = 0 V • 0 – 380 m. V • ID increases by 10 x • Never “OFF” – ID > 0. 1 n. A 6

Body Biasing Types • Traditional • Three main variations – SBB – DTMOS – ABB • Plus many others 7

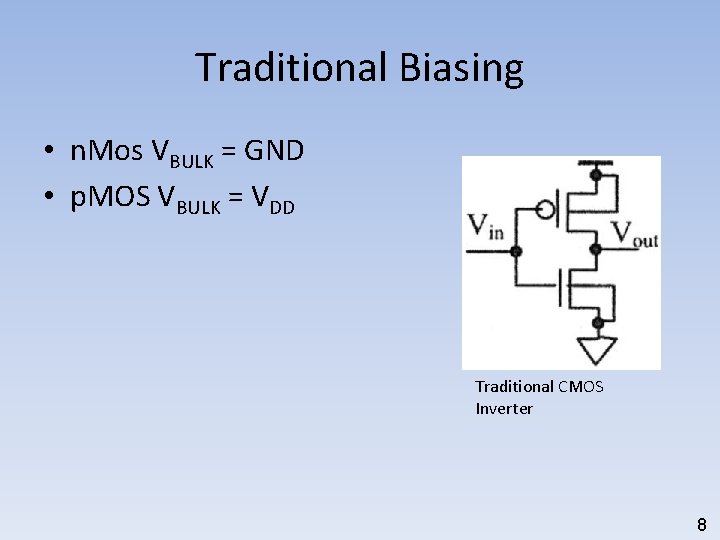

Traditional Biasing • n. Mos VBULK = GND • p. MOS VBULK = VDD Traditional CMOS Inverter 8

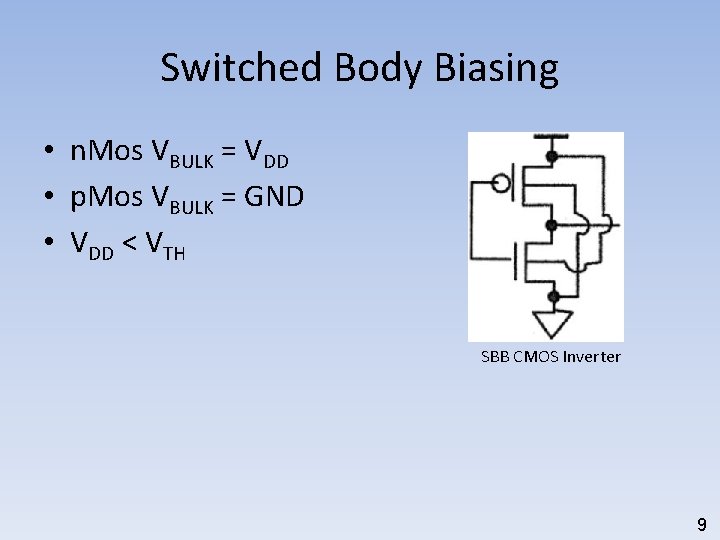

Switched Body Biasing • n. Mos VBULK = VDD • p. Mos VBULK = GND • VDD < VTH SBB CMOS Inverter 9

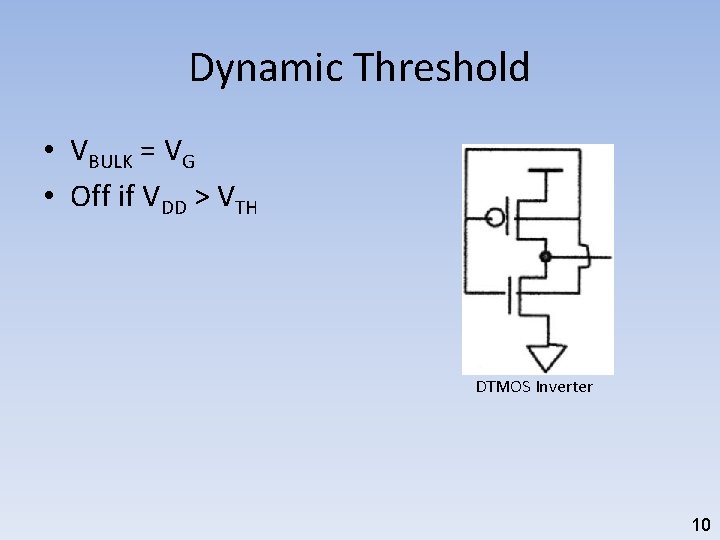

Dynamic Threshold • VBULK = VG • Off if VDD > VTH DTMOS Inverter 10

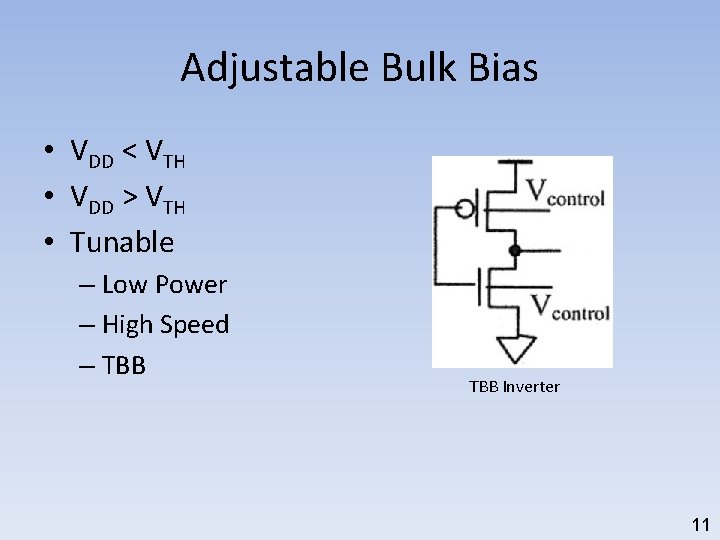

Adjustable Bulk Bias • VDD < VTH • VDD > VTH • Tunable – Low Power – High Speed – TBB Inverter 11

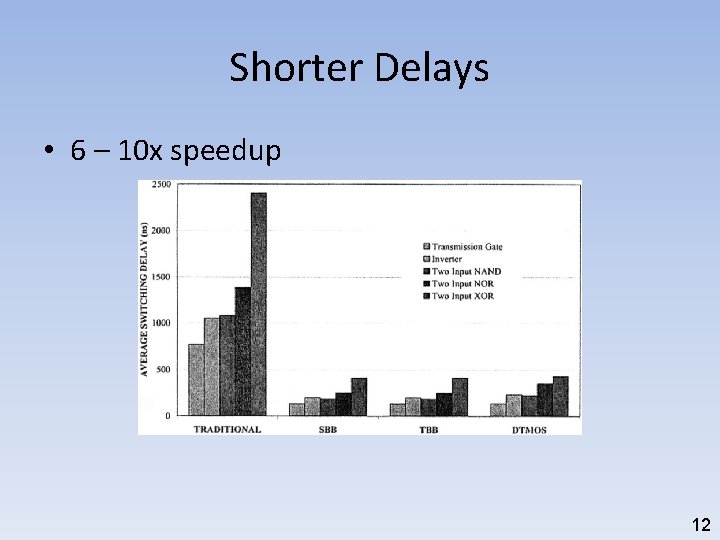

Shorter Delays • 6 – 10 x speedup 12

Improving Performance • Increased VDD = Increased Speed • VDD =. 75 VTH versus VDD =. 5 VTH – 8 x faster • Bias scheme irrelevant – More power 13

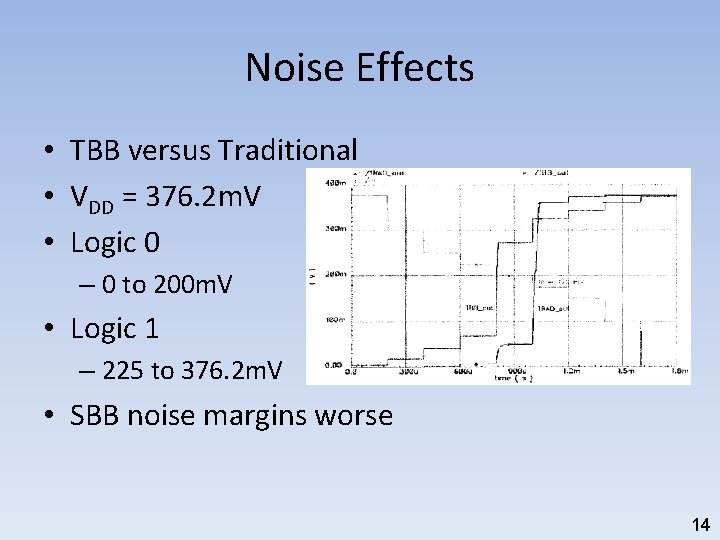

Noise Effects • TBB versus Traditional • VDD = 376. 2 m. V • Logic 0 – 0 to 200 m. V • Logic 1 – 225 to 376. 2 m. V • SBB noise margins worse 14

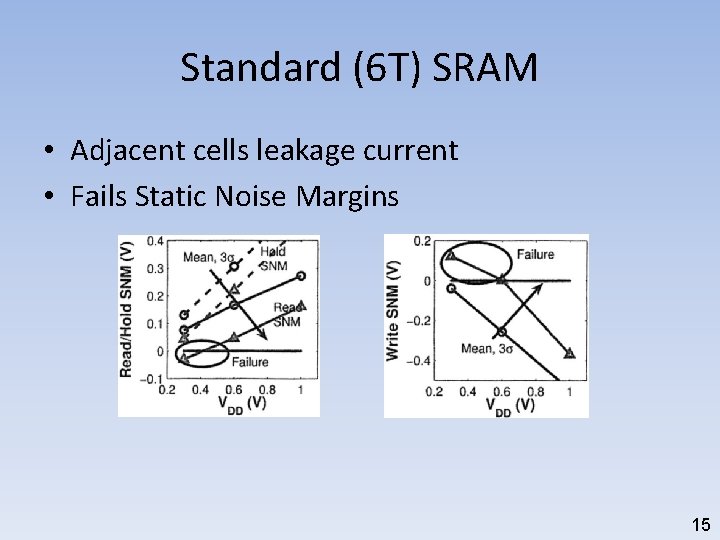

Standard (6 T) SRAM • Adjacent cells leakage current • Fails Static Noise Margins 15

Conclusions • • Bias schemes increase performance Speed versus Power Slight increase in noise 6 T SRAMS unusable 16

Questions

- Slides: 17