Low Power Lookup Table Using Power Gating and

Low Power Lookup Table Using Power Gating and Forward Body Biasing Techniques Kejia Li, Yang Fu University of Virginia Department of Electrical and Computer Engineering Charlottesville, VA 22904 ECE 6332 VLSI Design Final Presentation 1 of 16

Outline • Introduction • System components – – – Mux structure Well Driver for FBB Power gating circuitry Output buffer Level converter • Simulation results – – High power mode 1 High power mode 2 Low power mode Sleep mode • Summary ECE 6332 VLSI Design Final Presentation 2 of 16

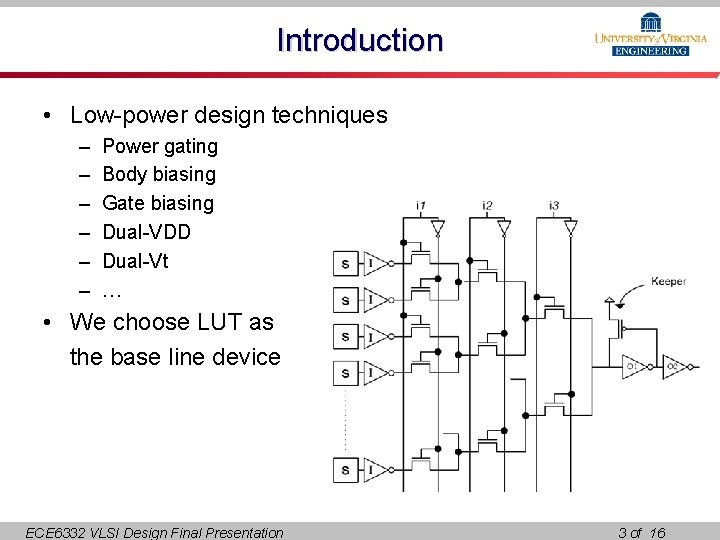

Introduction • Low-power design techniques – – – Power gating Body biasing Gate biasing Dual-VDD Dual-Vt … • We choose LUT as the base line device ECE 6332 VLSI Design Final Presentation 3 of 16

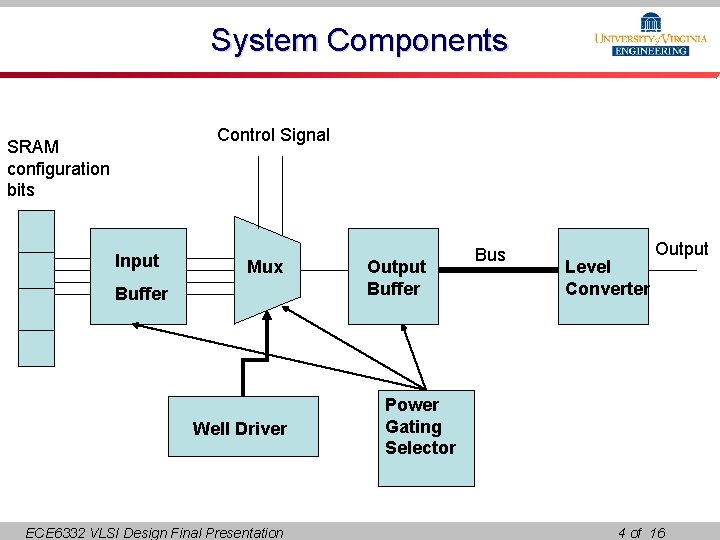

System Components Control Signal SRAM configuration bits Input Mux Buffer Well Driver ECE 6332 VLSI Design Final Presentation Output Buffer Bus Level Converter Output Power Gating Selector 4 of 16

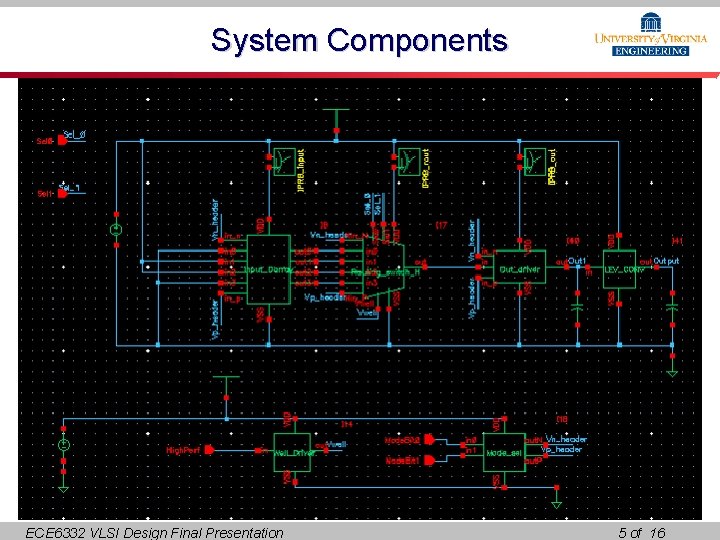

System Components ECE 6332 VLSI Design Final Presentation 5 of 16

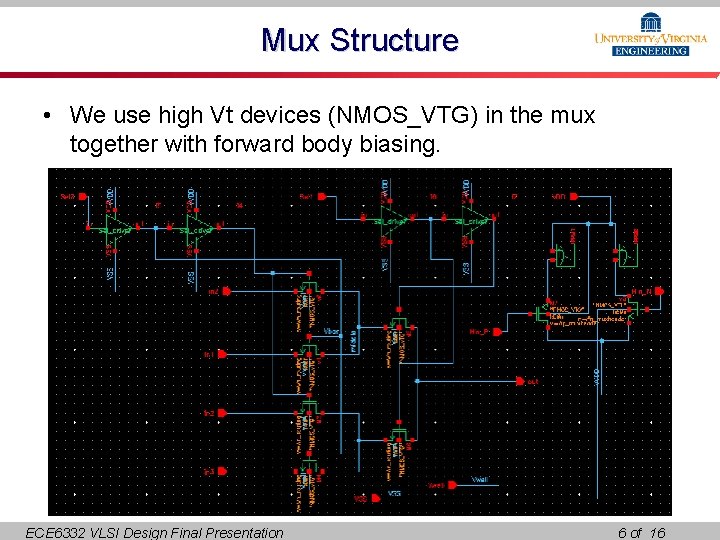

Mux Structure • We use high Vt devices (NMOS_VTG) in the mux together with forward body biasing. ECE 6332 VLSI Design Final Presentation 6 of 16

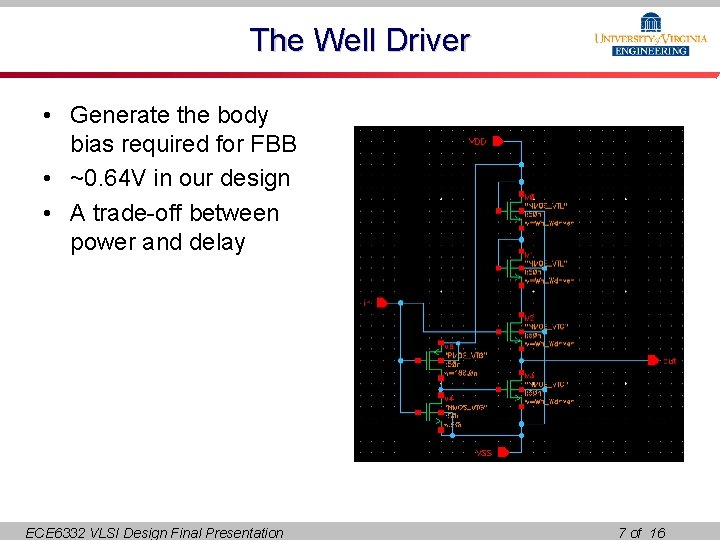

The Well Driver • Generate the body bias required for FBB • ~0. 64 V in our design • A trade-off between power and delay ECE 6332 VLSI Design Final Presentation 7 of 16

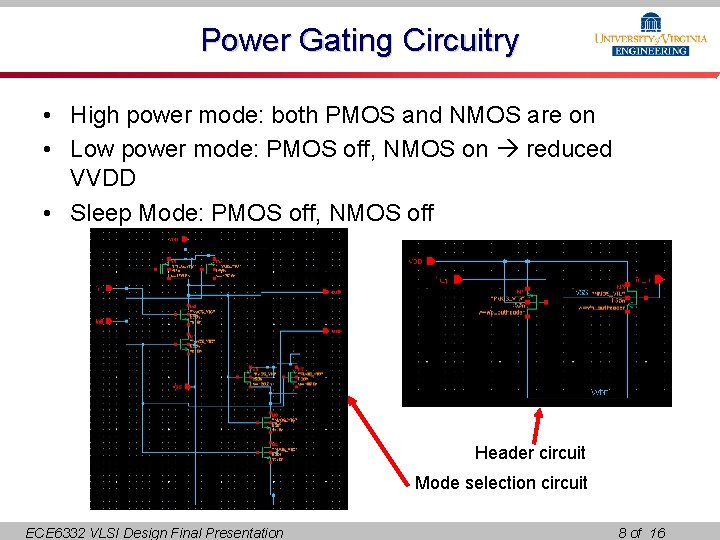

Power Gating Circuitry • High power mode: both PMOS and NMOS are on • Low power mode: PMOS off, NMOS on reduced VVDD • Sleep Mode: PMOS off, NMOS off Header circuit Mode selection circuit ECE 6332 VLSI Design Final Presentation 8 of 16

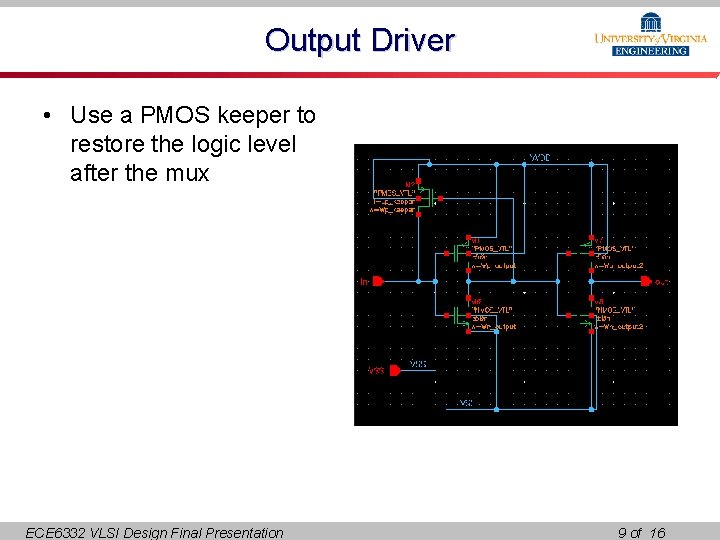

Output Driver • Use a PMOS keeper to restore the logic level after the mux ECE 6332 VLSI Design Final Presentation 9 of 16

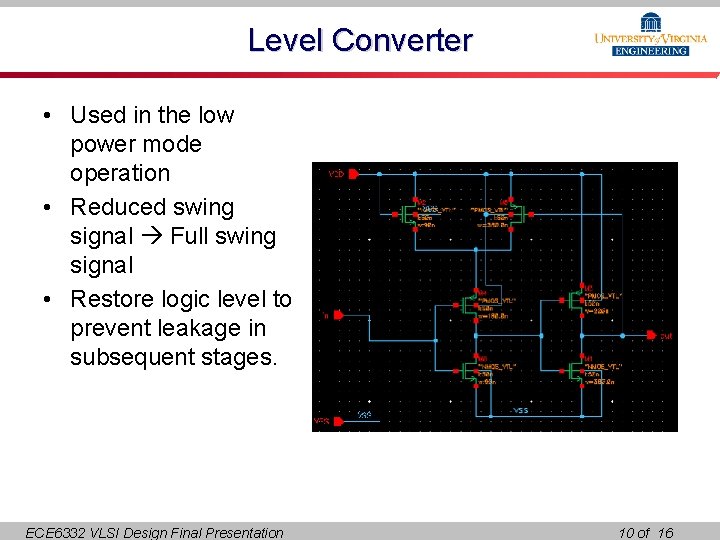

Level Converter • Used in the low power mode operation • Reduced swing signal Full swing signal • Restore logic level to prevent leakage in subsequent stages. ECE 6332 VLSI Design Final Presentation 10 of 16

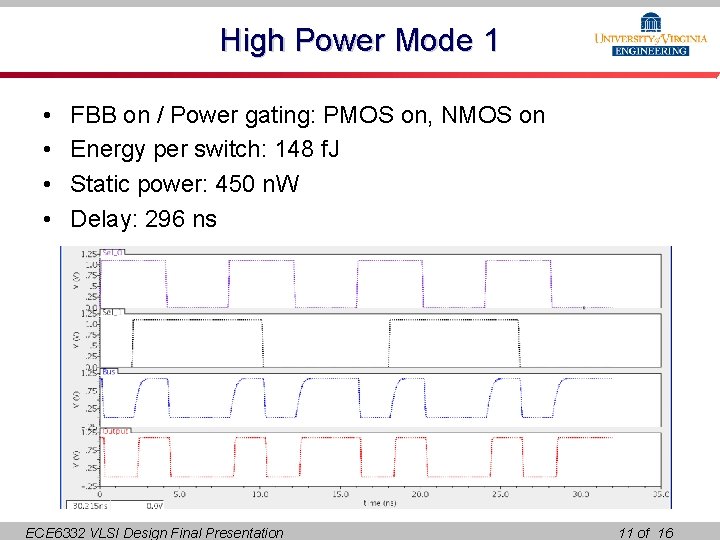

High Power Mode 1 • • FBB on / Power gating: PMOS on, NMOS on Energy per switch: 148 f. J Static power: 450 n. W Delay: 296 ns ECE 6332 VLSI Design Final Presentation 11 of 16

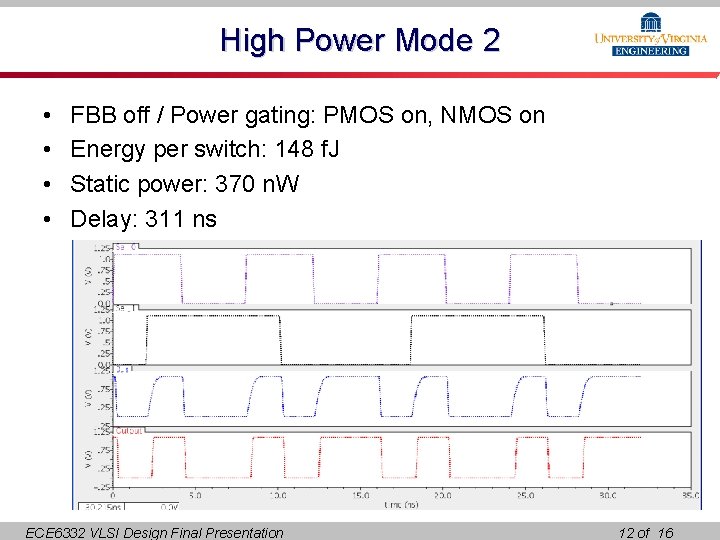

High Power Mode 2 • • FBB off / Power gating: PMOS on, NMOS on Energy per switch: 148 f. J Static power: 370 n. W Delay: 311 ns ECE 6332 VLSI Design Final Presentation 12 of 16

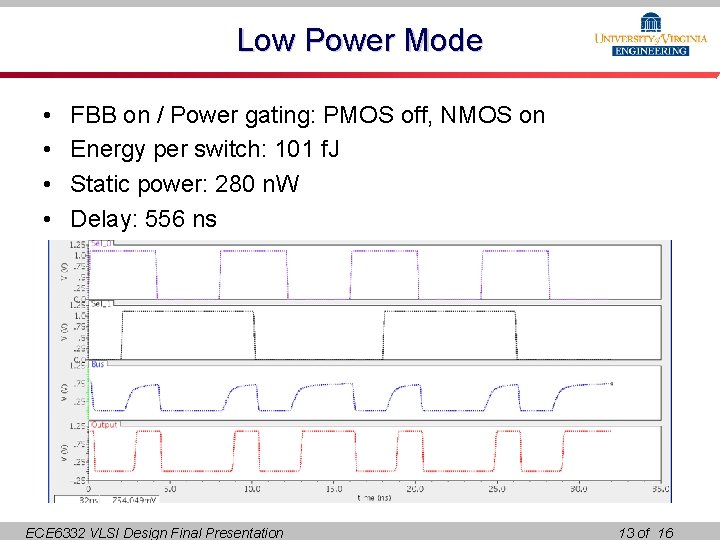

Low Power Mode • • FBB on / Power gating: PMOS off, NMOS on Energy per switch: 101 f. J Static power: 280 n. W Delay: 556 ns ECE 6332 VLSI Design Final Presentation 13 of 16

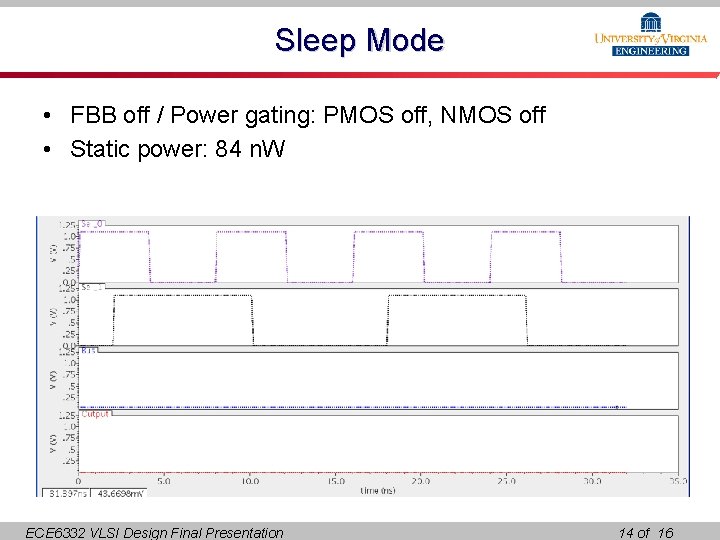

Sleep Mode • FBB off / Power gating: PMOS off, NMOS off • Static power: 84 n. W ECE 6332 VLSI Design Final Presentation 14 of 16

Summary • We have designed a low power lookup table using power gating and forward body biasing techniques. • Four different operation modes are available, depending on the power/delay requirement. • Future work needed to optimize the performance (like reducing leakage). ECE 6332 VLSI Design Final Presentation 15 of 16

The End • Thank you! ECE 6332 VLSI Design Final Presentation 16 of 16

- Slides: 16