Low Power Design for a 64 point FFT

![Computation Discrete/Digital FT X(ej ) = x[n]* e-j n DFT Algorithm O(n 2) [Blue] Computation Discrete/Digital FT X(ej ) = x[n]* e-j n DFT Algorithm O(n 2) [Blue]](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-6.jpg)

![Radix 8 FFT Flow Graph X[0] M=1 M=2 M=3 Y[0] X[1] Y[4] X[2] Y[2] Radix 8 FFT Flow Graph X[0] M=1 M=2 M=3 Y[0] X[1] Y[4] X[2] Y[2]](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-9.jpg)

![FFT Computation • 64 point FFT => 6 stages [log 2(n)] • Each stage FFT Computation • 64 point FFT => 6 stages [log 2(n)] • Each stage](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-11.jpg)

![Constants k= 0 -31; (0 -N/2 -1) [ 32 constants] 1. In the design Constants k= 0 -31; (0 -N/2 -1) [ 32 constants] 1. In the design](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-16.jpg)

- Slides: 19

Low Power Design for a 64 point FFT Processor Arish Alreja

Overview We will discuss • Motivation • Fourier Transforms and FFTs (briefly) • A low power 64 point FFT Processor. Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 2

Motivation o Orthogonal Frequency Division Multiplexing (OFDM) is used in 802. 11 a Wi. Fi chipsets to achieve higher resiliency against errors due to multipath fading by encoding data over multiple carrier frequencies Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 3

Motivation o FFT is the most computationally intensive part of OFDM o 802. 11 a Wi. Fi standard requires 64 point FFT for OFDM o Low Power FFT improves battery life on mobile devices Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 4

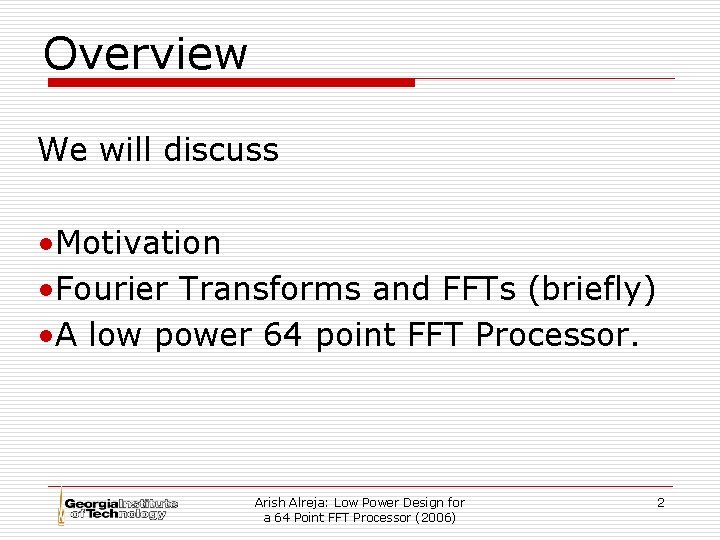

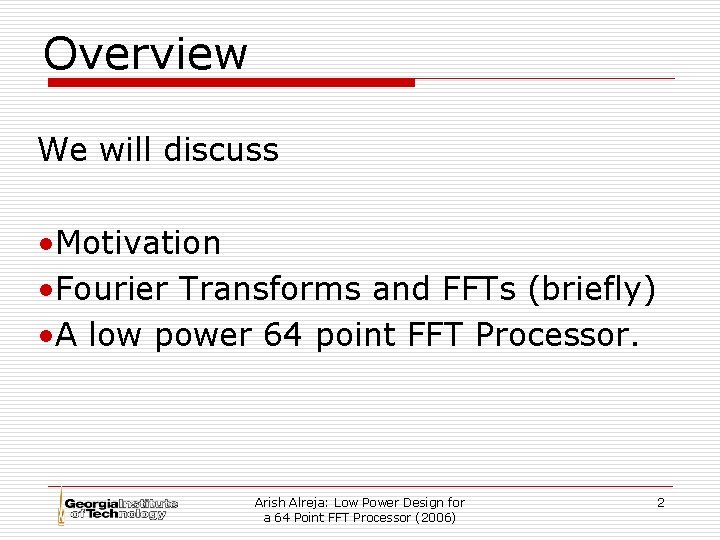

Fourier Transforms allow Frequency Domain representation of a signal in the Time Domain Frequency Domain Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 5

![Computation DiscreteDigital FT Xej xn ej n DFT Algorithm On 2 Blue Computation Discrete/Digital FT X(ej ) = x[n]* e-j n DFT Algorithm O(n 2) [Blue]](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-6.jpg)

Computation Discrete/Digital FT X(ej ) = x[n]* e-j n DFT Algorithm O(n 2) [Blue] With some Mathematical rearrangements we get the Fast Fourier Transform Algorithm FFT Algorithm O(nlog 2 n) [Red] Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 6

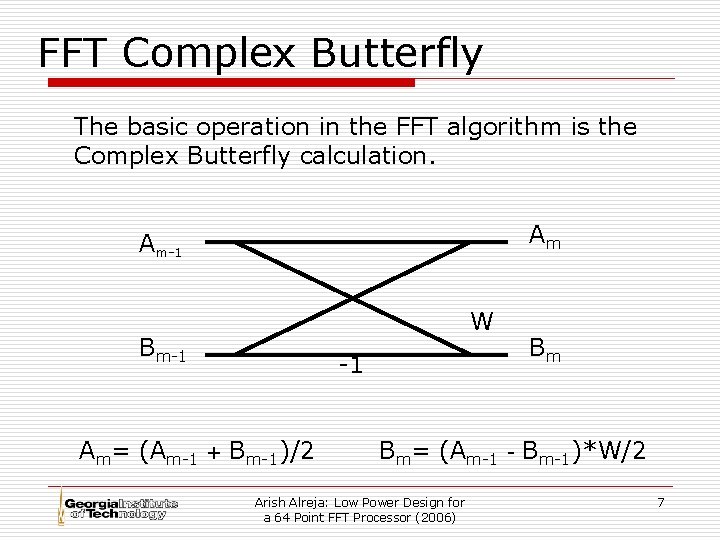

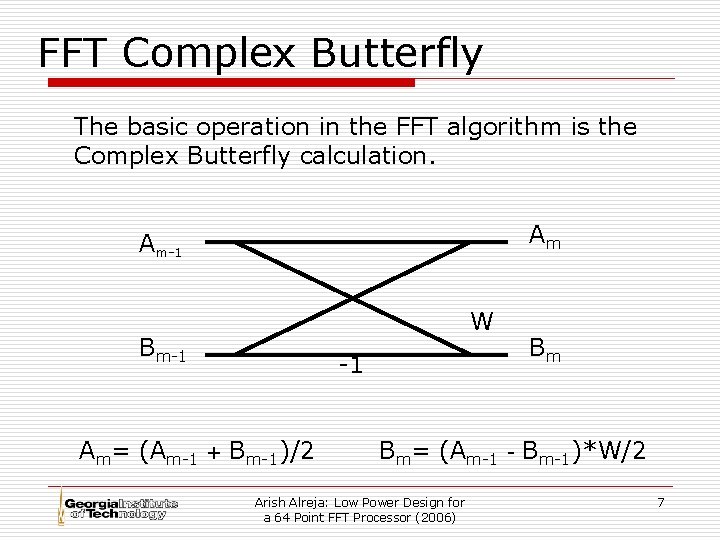

FFT Complex Butterfly The basic operation in the FFT algorithm is the Complex Butterfly calculation. Am Am-1 W Bm-1 -1 Am= (Am-1 + Bm-1)/2 Bm Bm= (Am-1 - Bm-1)*W/2 Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 7

FFT Complex Butterfly 1. Why do we divide by 2? To avoid arithmetic overflow Am-1 Bm 1 Am W Bm -1 2. What is W ? W is the constant “twiddle factor” K = 0: N/2 -1 3. What are A & B? A and B are the terms that are undergoing the computation (In Place computation) 4. What is m? “m” represents the resulting stage of the FFT Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 8

![Radix 8 FFT Flow Graph X0 M1 M2 M3 Y0 X1 Y4 X2 Y2 Radix 8 FFT Flow Graph X[0] M=1 M=2 M=3 Y[0] X[1] Y[4] X[2] Y[2]](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-9.jpg)

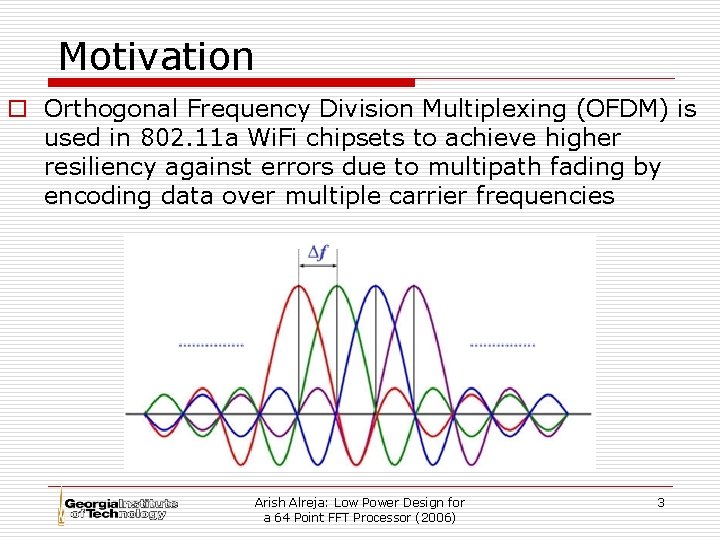

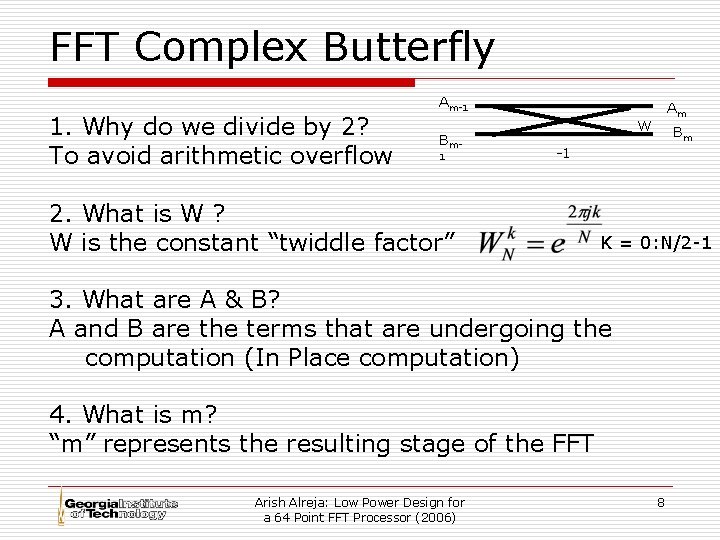

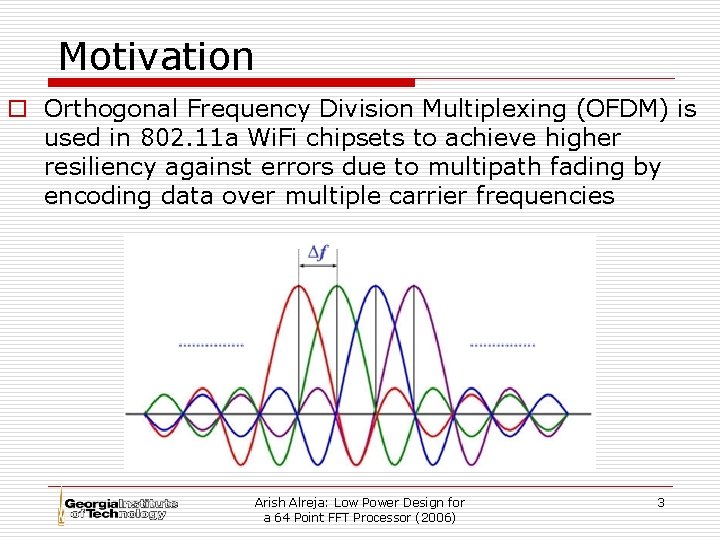

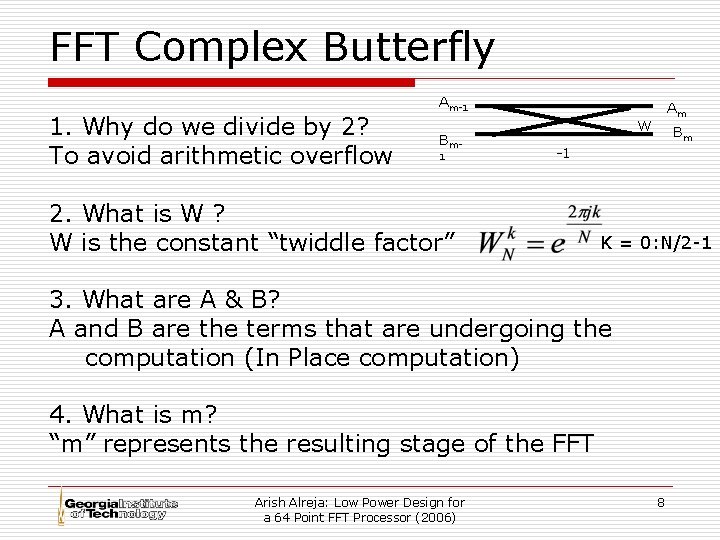

Radix 8 FFT Flow Graph X[0] M=1 M=2 M=3 Y[0] X[1] Y[4] X[2] Y[2] X[3] Y[6] X[4] Y[1] X[5] Y[5] X[6] Y[3] X[7] Time Domain Bit reversal of indexes after in place computation Y[7] Frequency Domain Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 9

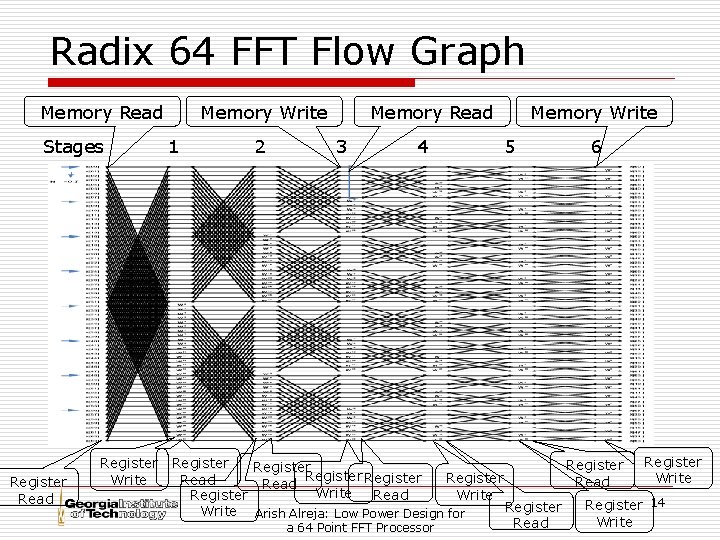

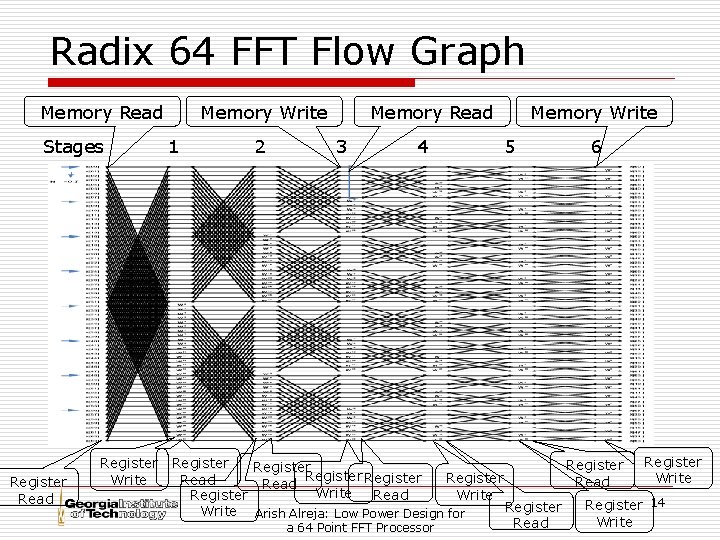

Radix 64 FFT Flow Graph Arish Alreja: Low Power Design for a 64 Point FFT Processor (2006) 10

![FFT Computation 64 point FFT 6 stages log 2n Each stage FFT Computation • 64 point FFT => 6 stages [log 2(n)] • Each stage](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-11.jpg)

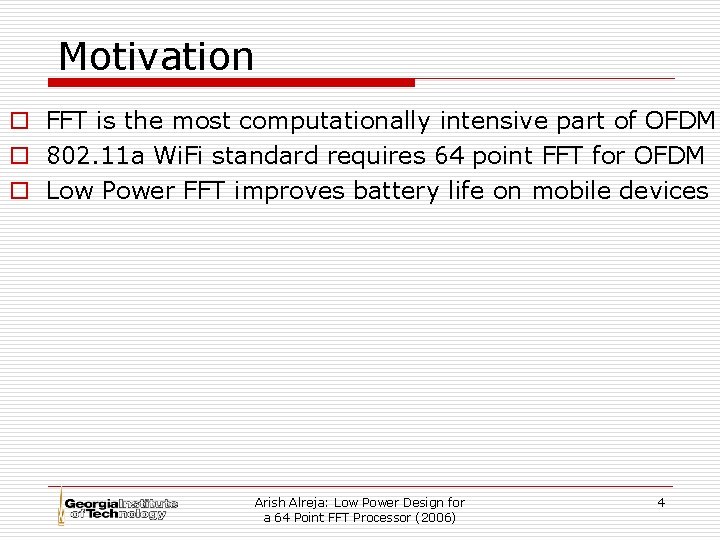

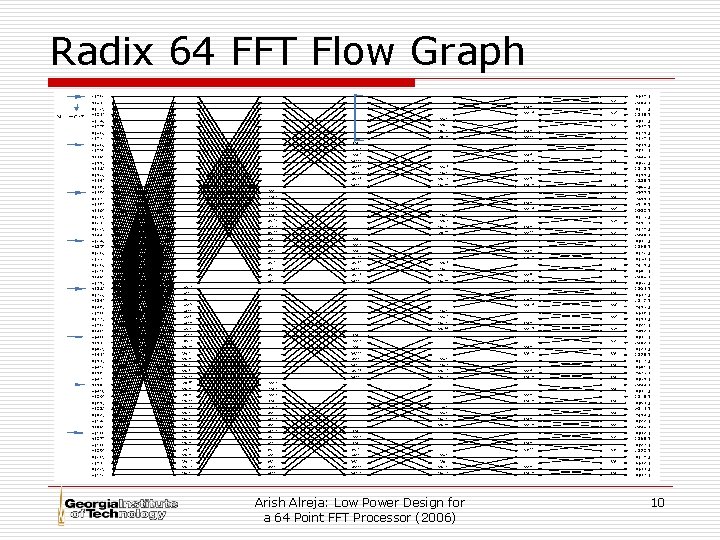

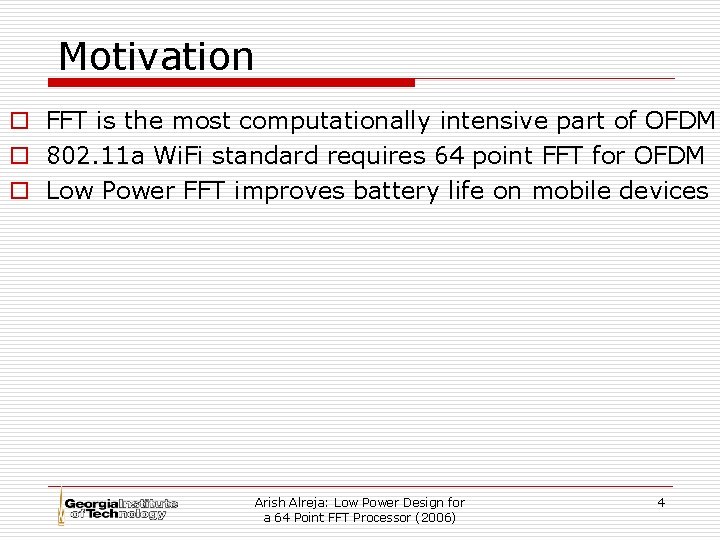

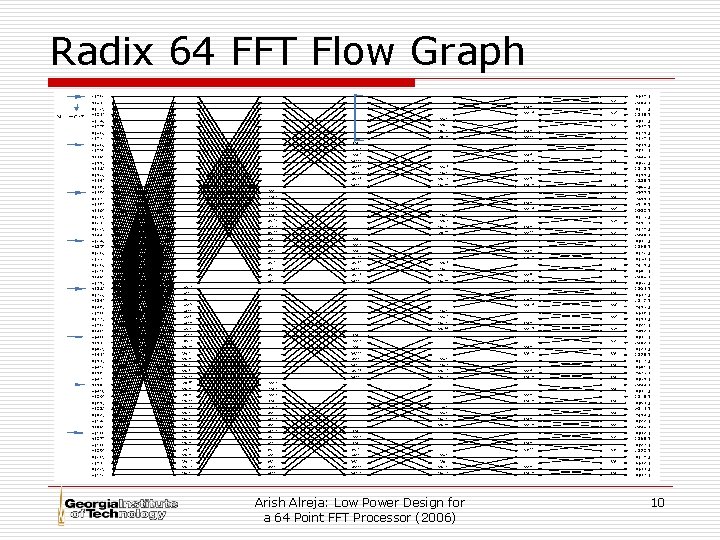

FFT Computation • 64 point FFT => 6 stages [log 2(n)] • Each stage => 32 Butterfly computations • 1 Butterfly computation • 1 complex multiplication • 2 complex additions We have 32 constants k= 0 -31; (0 -N/2 -1) Arish Alreja: Low Power Design for a 64 Point FFT Processor 11

Design Constraints Focus on low power consumption 1. Reduce memory Reads/Writes Keep Data in Pipeline longer 2. Eliminate Digital Multiplier 64 point FFT => 32 constants (W’s). Achieve multiplication with known constants by using combination of shifters and adders Arish Alreja: Low Power Design for a 64 Point FFT Processor 12

Processor Datapath D_Input Register Select D_RS 1 D_RS 2 D_RS 1 Mem In Choose. Mem. Register File 2 Register File 1 RS 1 Mem Out RS 1 RS 2 Input Register Select Butterfly Processor Arish Alreja: Low Power Design for a 64 Point FFT Processor 13

Radix 64 FFT Flow Graph Memory Read Stages Register Read Memory Write 1 2 Memory Read 3 4 Memory Write 5 6 Register Register Write Read Write Read Register Write Register 14 Register Write Arish Alreja: Low Power Design for Write Read a 64 Point FFT Processor

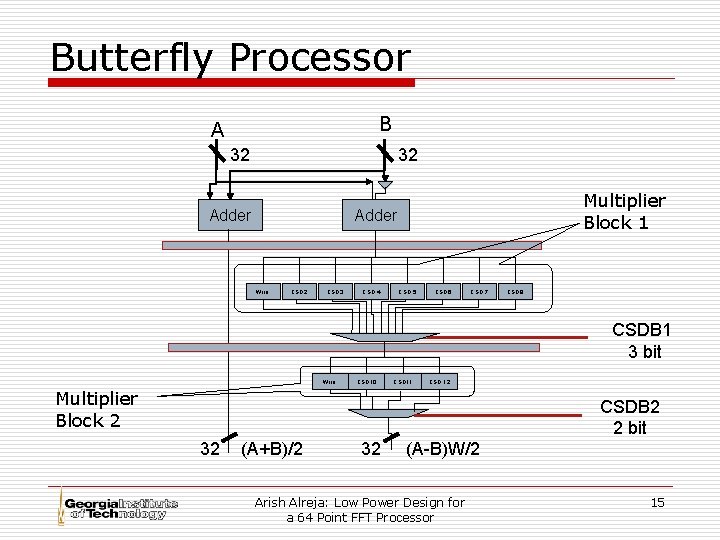

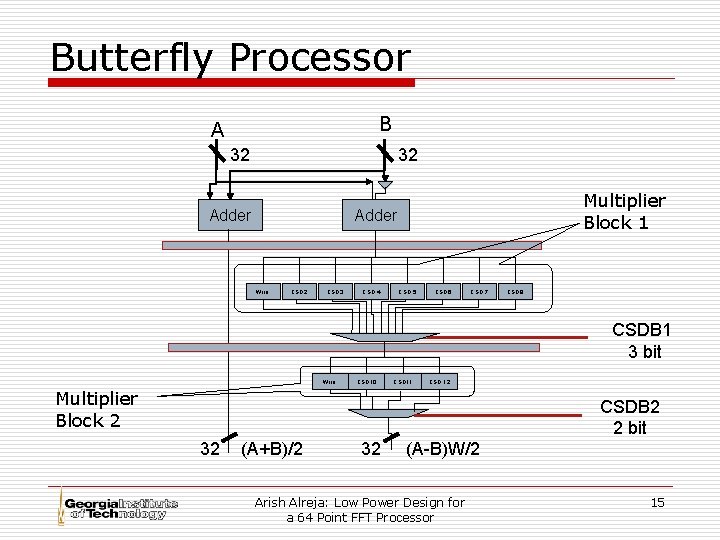

Butterfly Processor B A 32 32 Adder Multiplier Block 1 Adder Wire CSD 2 CSD 3 CSD 4 CSD 5 CSD 6 CSD 7 CSD 8 CSDB 1 3 bit Wire CSD 10 CSD 11 CSD 12 Multiplier Block 2 CSDB 2 2 bit 32 (A+B)/2 32 (A-B)W/2 Arish Alreja: Low Power Design for a 64 Point FFT Processor 15

![Constants k 0 31 0 N2 1 32 constants 1 In the design Constants k= 0 -31; (0 -N/2 -1) [ 32 constants] 1. In the design](https://slidetodoc.com/presentation_image_h/00c581a9a0ac28599e9a46152cf2c79b/image-16.jpg)

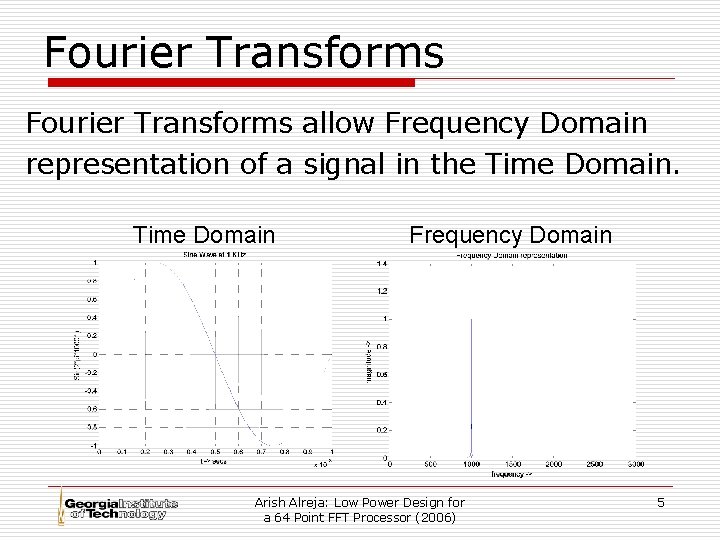

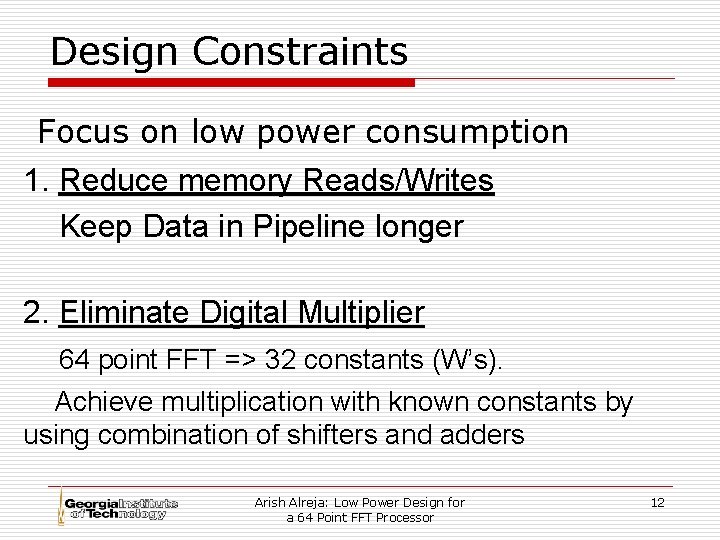

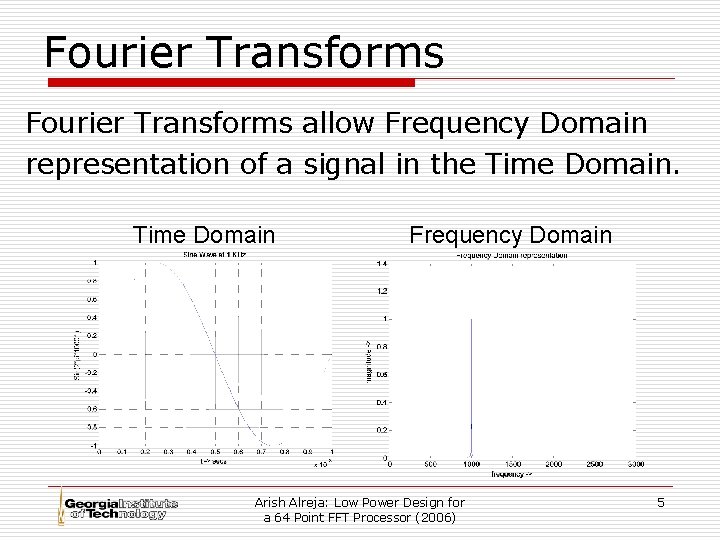

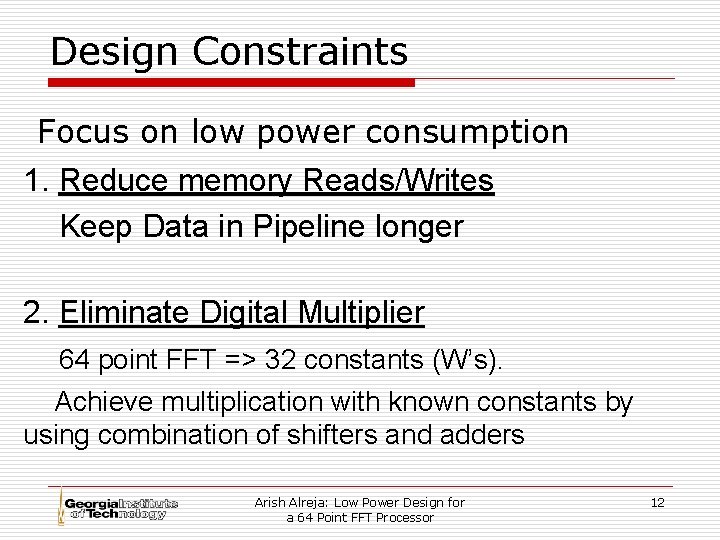

Constants k= 0 -31; (0 -N/2 -1) [ 32 constants] 1. In the design we have to hardcode only 10 constants, because 2. Also, we exploit the property to achieve any twiddle factor from using only the following 10 hard coded constants Multiplier Block 1 Arish Alreja: Low Power Design for a 64 Point FFT Processor Multiplier Block 2 16

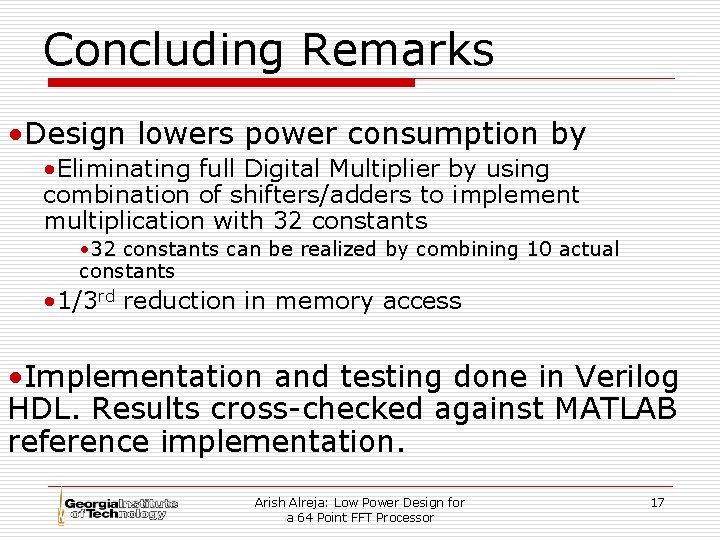

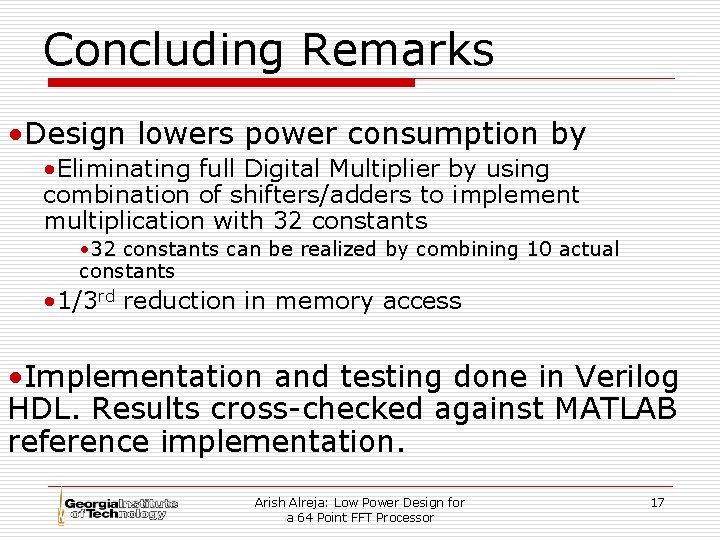

Concluding Remarks • Design lowers power consumption by • Eliminating full Digital Multiplier by using combination of shifters/adders to implement multiplication with 32 constants • 32 constants can be realized by combining 10 actual constants • 1/3 rd reduction in memory access • Implementation and testing done in Verilog HDL. Results cross-checked against MATLAB reference implementation. Arish Alreja: Low Power Design for a 64 Point FFT Processor 17

Acknowledgements o. Dr. Vijay Madisetti: Faculty Mentor o. Mohanned Sinnokrot: Graduate Mentor ohttp: //www. spiral. net: Code generation tool for optimal number of shifters and adders for multiplier constant multiplication blocks. Arish Alreja: Low Power Design for a 64 Point FFT Processor 18

Questions ? Arish Alreja: Low Power Design for a 64 Point FFT Processor 19