Low power 32 bit bus with inversion encoding

Low power 32 -bit bus with inversion encoding Wei Jiang ELEC 6270

Power Consumption by Bus n n n High capacitance lines High switching activities Reduce power dissipation by reducing the number of transitions

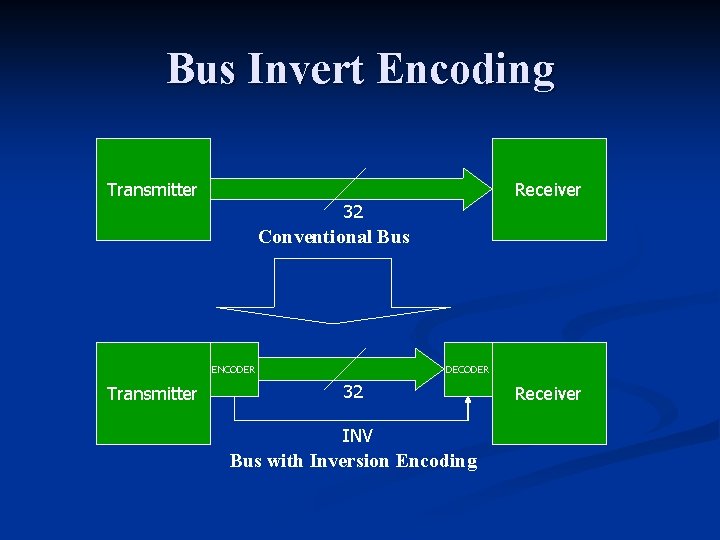

Bus Invert Encoding Transmitter Receiver 32 Conventional Bus ENCODER Transmitter DECODER 32 INV Bus with Inversion Encoding Receiver

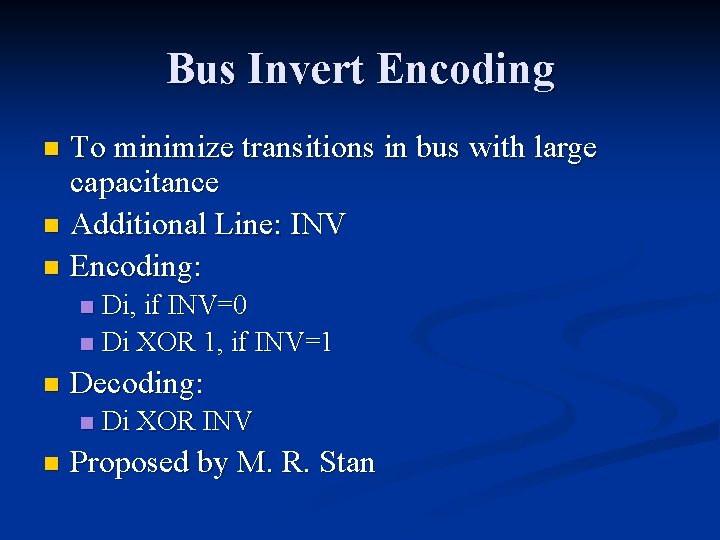

Bus Invert Encoding To minimize transitions in bus with large capacitance n Additional Line: INV n Encoding: n Di, if INV=0 n Di XOR 1, if INV=1 n n Decoding: n n Di XOR INV Proposed by M. R. Stan

Design of Encoder

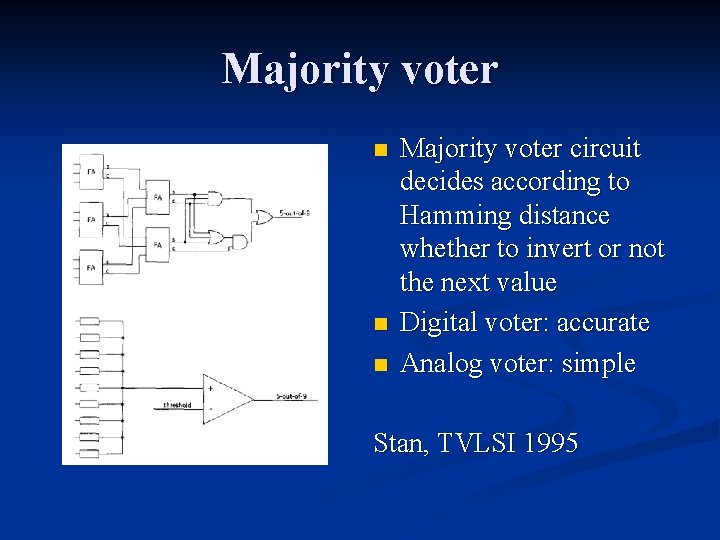

Majority voter n n n Majority voter circuit decides according to Hamming distance whether to invert or not the next value Digital voter: accurate Analog voter: simple Stan, TVLSI 1995

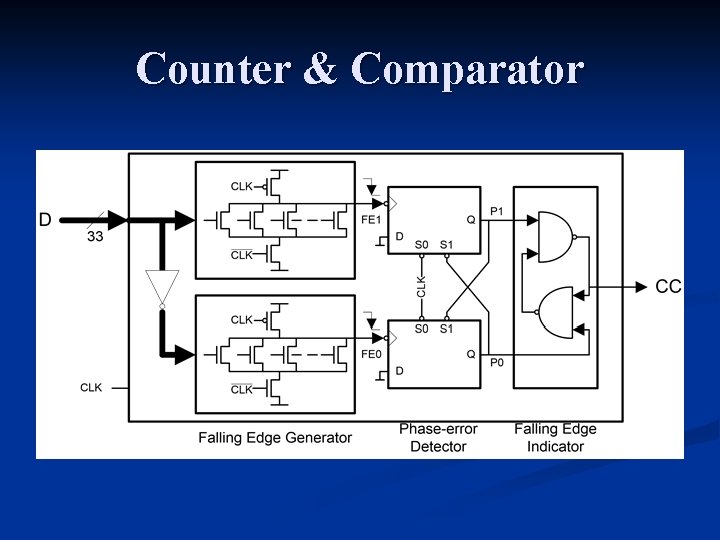

Counter & Comparator

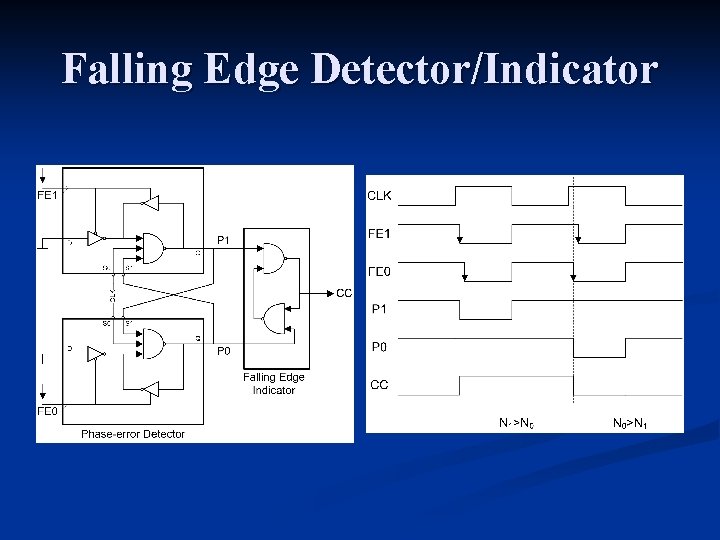

Falling Edge Detector/Indicator

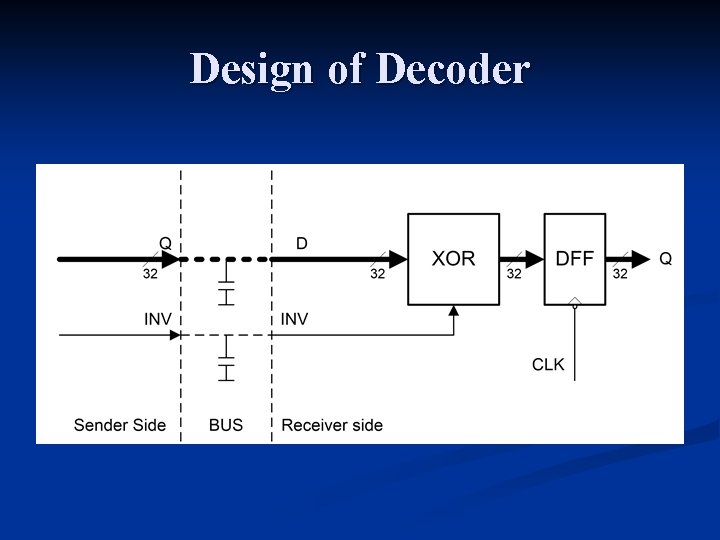

Design of Decoder

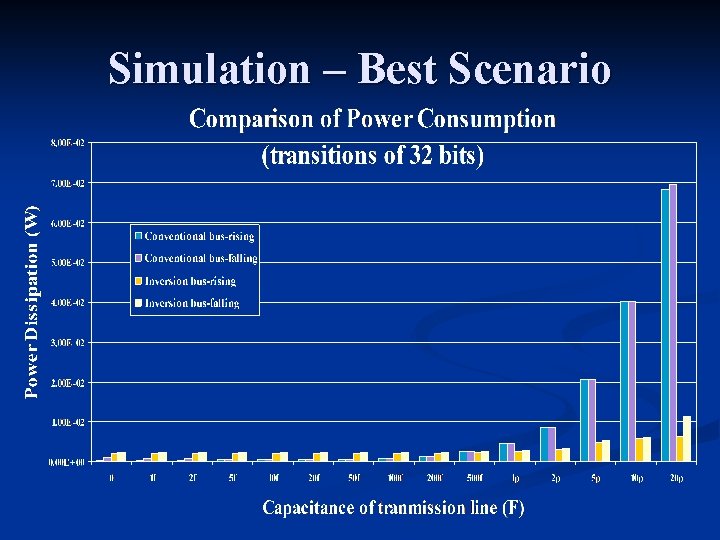

Simulation – Best Scenario

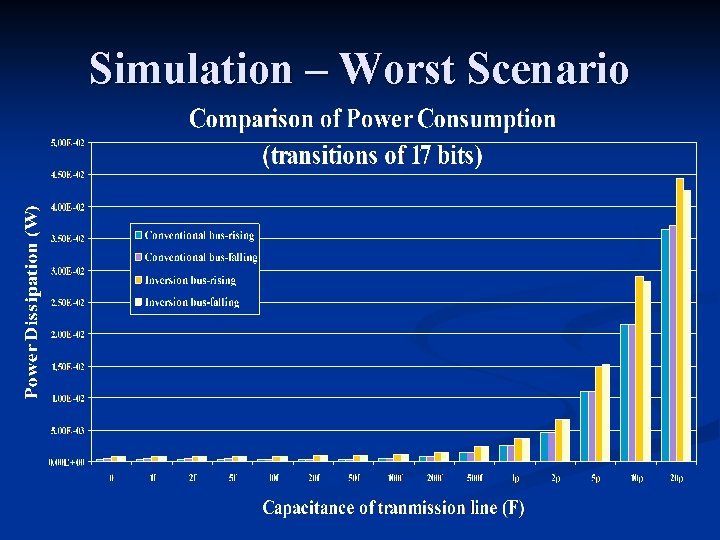

Simulation – Worst Scenario

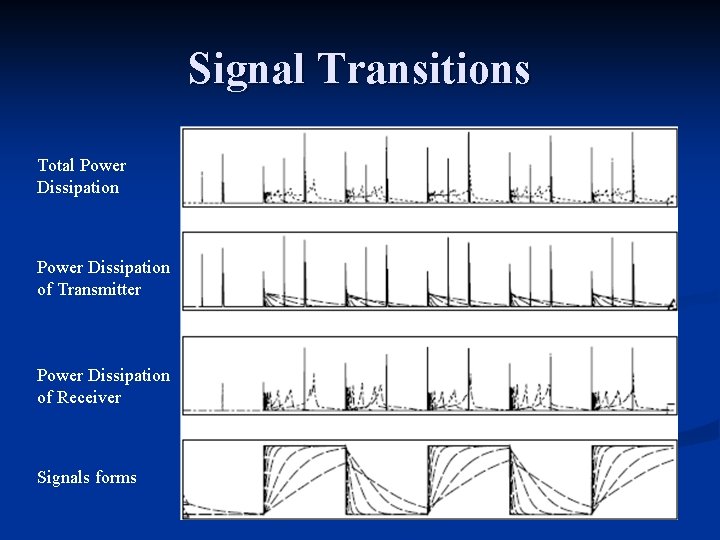

Signal Transitions Total Power Dissipation of Transmitter Power Dissipation of Receiver Signals forms

Simulation – Average

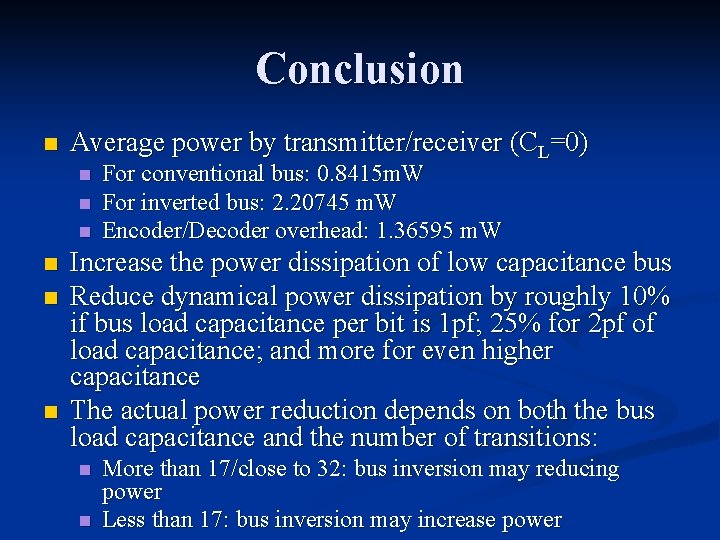

Conclusion n Average power by transmitter/receiver (CL=0) n n n For conventional bus: 0. 8415 m. W For inverted bus: 2. 20745 m. W Encoder/Decoder overhead: 1. 36595 m. W Increase the power dissipation of low capacitance bus Reduce dynamical power dissipation by roughly 10% if bus load capacitance per bit is 1 pf; 25% for 2 pf of load capacitance; and more for even higher capacitance The actual power reduction depends on both the bus load capacitance and the number of transitions: n n More than 17/close to 32: bus inversion may reducing power Less than 17: bus inversion may increase power

Thank You n Simulation n TSMC 0. 35 um Process Synopsys HSPICE References n n M. R. Stan and W. P. Burleson, “Bus-invert coding for lowpower I/O, ” IEEE Trans. On VLSI Systems, Vol. 3, No. 1, pp. 49 -58, 1995 T. Lindkvist et al, “Deep Sub-Micron Bus Invert Coding, ” NORSIG 2004, p. 133 -136, June 2004

- Slides: 15