Low Mass Rui de Oliveira CERN Cosimo Pastore

![Material budget Material Radiation length [cm] Density [gr/cc] Resistivity [uohms*cm] Gold 0. 3 19. Material budget Material Radiation length [cm] Density [gr/cc] Resistivity [uohms*cm] Gold 0. 3 19.](https://slidetodoc.com/presentation_image/d7d09d66ea79a6f11ce65e2f1a5f2338/image-3.jpg)

- Slides: 41

Low Mass Rui de Oliveira (CERN), Cosimo Pastore (INFN), Serge ferry (CERN), Wojtek Dulinsky (CNRS) 10/6/2020 Rui de Oliveira 1

Outline • Aluminum circuits – Material budget /General possibilities – Micro-via – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Micro channel 10/6/2020 Rui de Oliveira 2

![Material budget Material Radiation length cm Density grcc Resistivity uohmscm Gold 0 3 19 Material budget Material Radiation length [cm] Density [gr/cc] Resistivity [uohms*cm] Gold 0. 3 19.](https://slidetodoc.com/presentation_image/d7d09d66ea79a6f11ce65e2f1a5f2338/image-3.jpg)

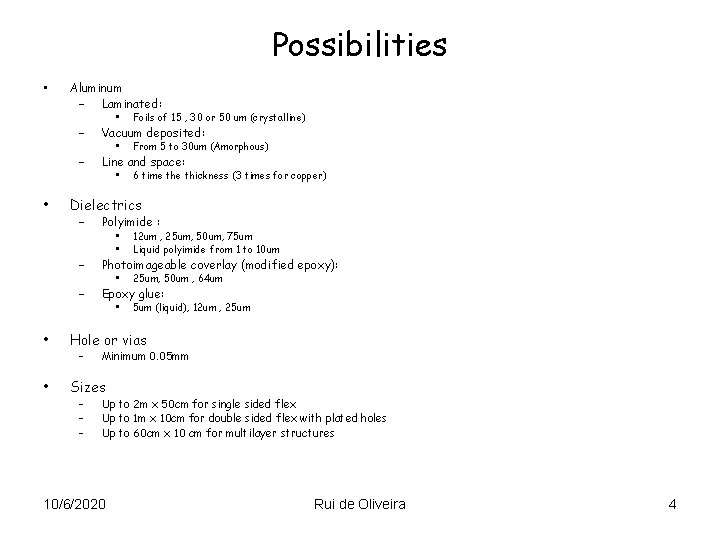

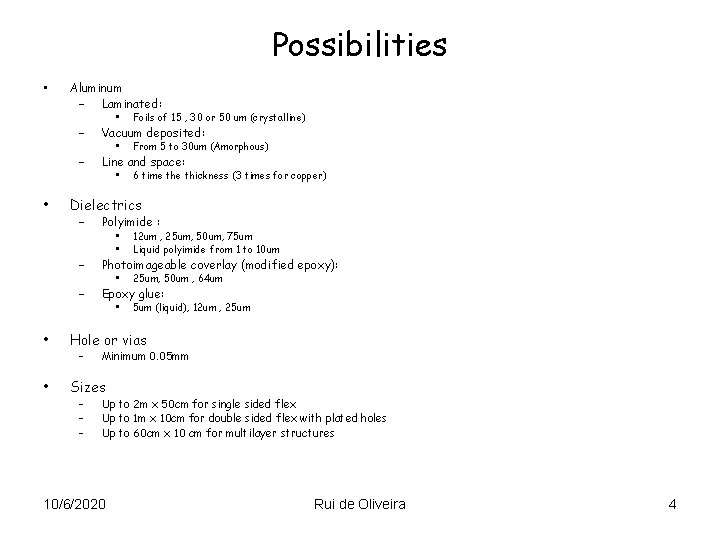

Material budget Material Radiation length [cm] Density [gr/cc] Resistivity [uohms*cm] Gold 0. 3 19. 3 2. 4 Copper 1. 4 9. 0 1. 7 Aluminum 8. 9 2. 7 Glass epoxy 19. 4 Polyimide 29. 0 Beryllium 35. 3 1. 9 3. 3 Copper is close to 6. 5 times less transparent than aluminum And aluminum has only 1. 6 times the resistivity of copper Polyimide is 1. 5 times better than glass epoxy. 10/6/2020 Rui de Oliveira 3

Possibilities • • Aluminum – Laminated: • Foils of 15 , 30 or 50 um (crystalline) • From 5 to 30 um (Amorphous) • 6 time thickness (3 times for copper) – Vacuum deposited: – Line and space: Dielectrics – Polyimide : – Photoimageable coverlay (modified epoxy): – Epoxy glue: • • 12 um , 25 um, 50 um, 75 um Liquid polyimide from 1 to 10 um • 25 um, 50 um , 64 um • 5 um (liquid), 12 um , 25 um • Hole or vias • Sizes – – Minimum 0. 05 mm Up to 2 m x 50 cm for single sided flex Up to 1 m x 10 cm for double sided flex with plated holes Up to 60 cm x 10 cm for multilayer structures 10/6/2020 Rui de Oliveira 4

Outline • Aluminium circuits – Material budget /General possibilities – Vias/Microvias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Microchannel 10/6/2020 Rui de Oliveira 5

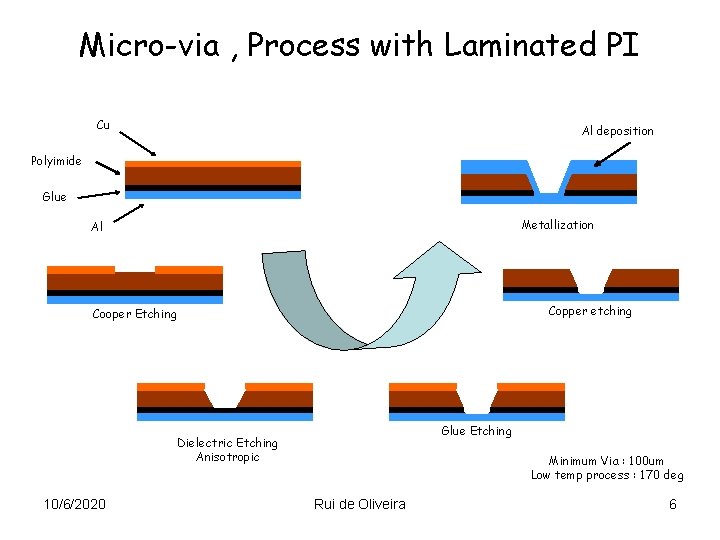

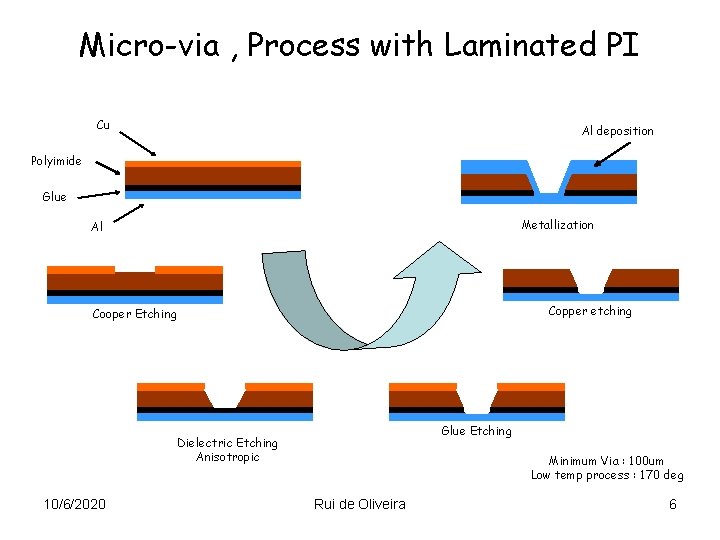

Micro-via , Process with Laminated PI Cu Al deposition Polyimide Glue Metallization Al Copper etching Cooper Etching Glue Etching Dielectric Etching Anisotropic 10/6/2020 Minimum Via : 100 um Low temp process : 170 deg Rui de Oliveira 6

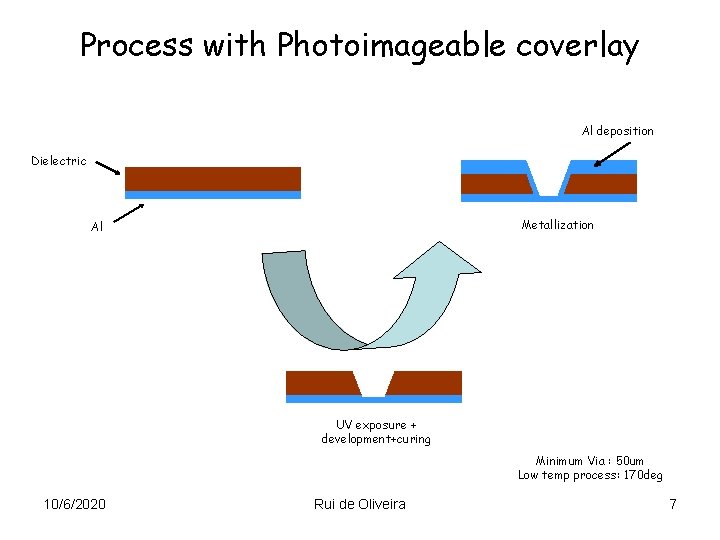

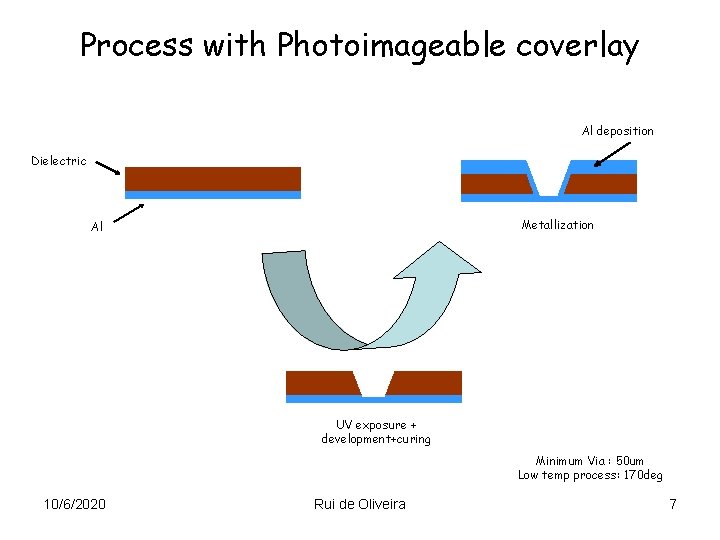

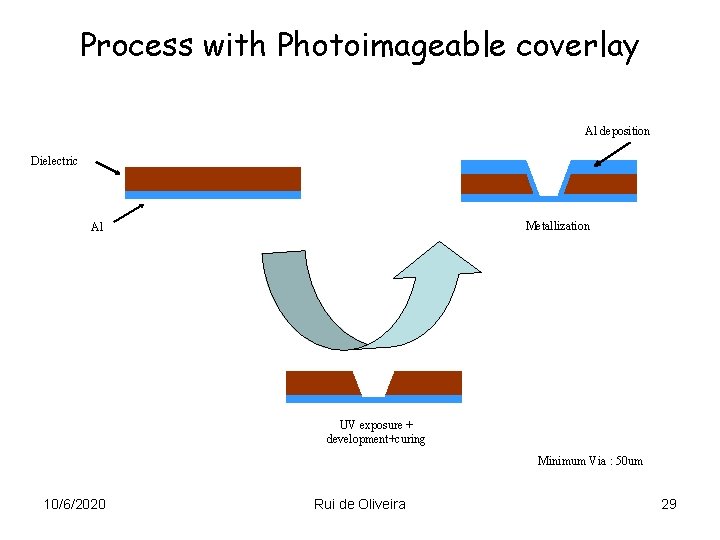

Process with Photoimageable coverlay Al deposition Dielectric Metallization Al UV exposure + development+curing Minimum Via : 50 um Low temp process: 170 deg 10/6/2020 Rui de Oliveira 7

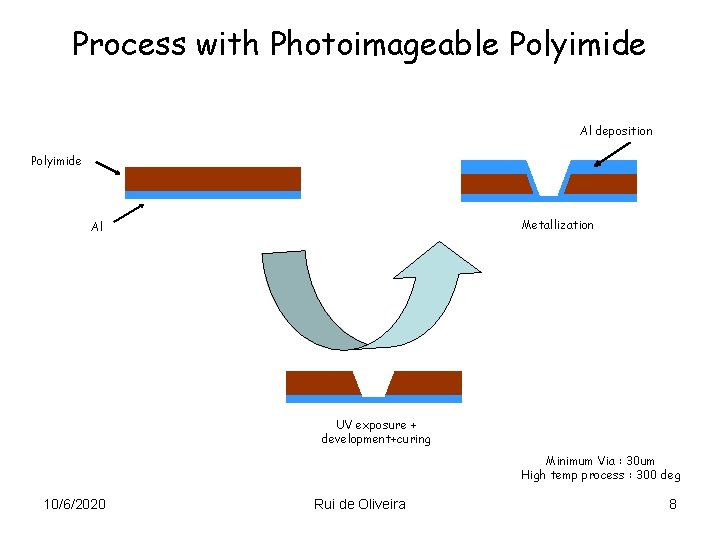

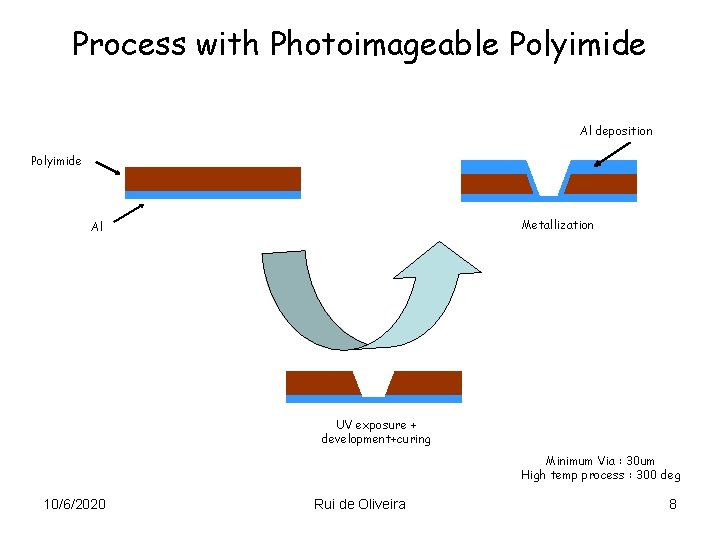

Process with Photoimageable Polyimide Al deposition Polyimide Metallization Al UV exposure + development+curing Minimum Via : 30 um High temp process : 300 deg 10/6/2020 Rui de Oliveira 8

Outline • Aluminum circuits – Material budget /General possibilities – Vias/Micro-vias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Micro-channel 10/6/2020 Rui de Oliveira 9

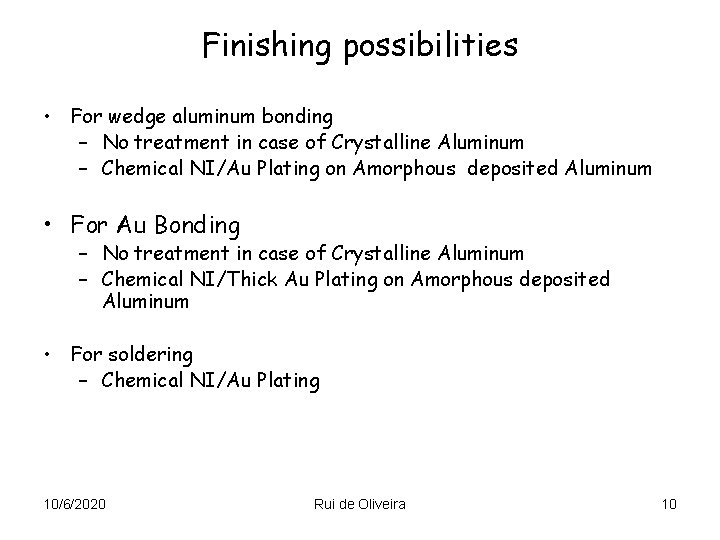

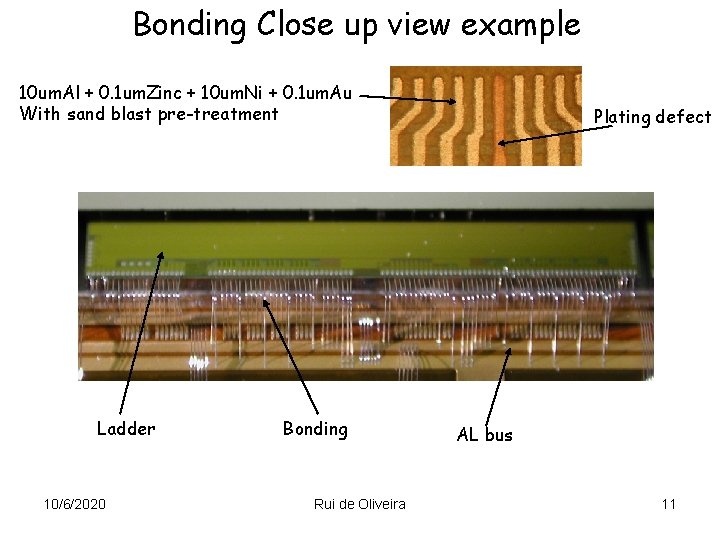

Finishing possibilities • For wedge aluminum bonding – No treatment in case of Crystalline Aluminum – Chemical NI/Au Plating on Amorphous deposited Aluminum • For Au Bonding – No treatment in case of Crystalline Aluminum – Chemical NI/Thick Au Plating on Amorphous deposited Aluminum • For soldering – Chemical NI/Au Plating 10/6/2020 Rui de Oliveira 10

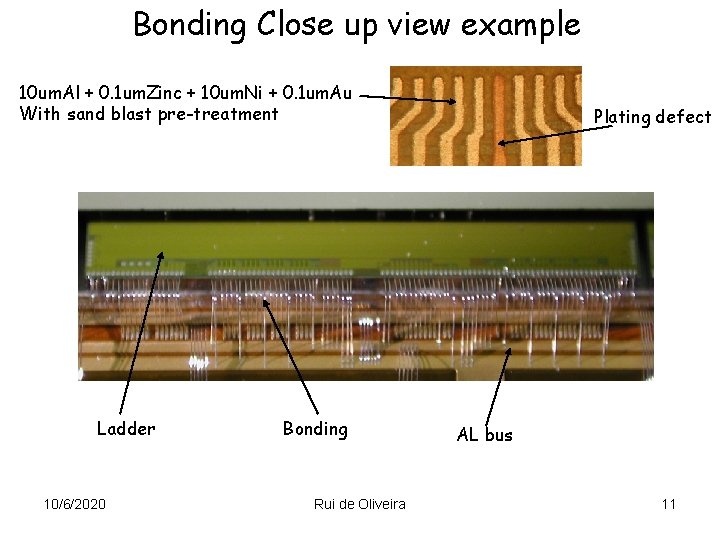

Bonding Close up view example 10 um. Al + 0. 1 um. Zinc + 10 um. Ni + 0. 1 um. Au With sand blast pre-treatment Ladder 10/6/2020 Bonding Rui de Oliveira Plating defect AL bus 11

Outline • Aluminum circuits – Material budget /General possibilities – Vias/Micro-vias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Micro-channel 10/6/2020 Rui de Oliveira 12

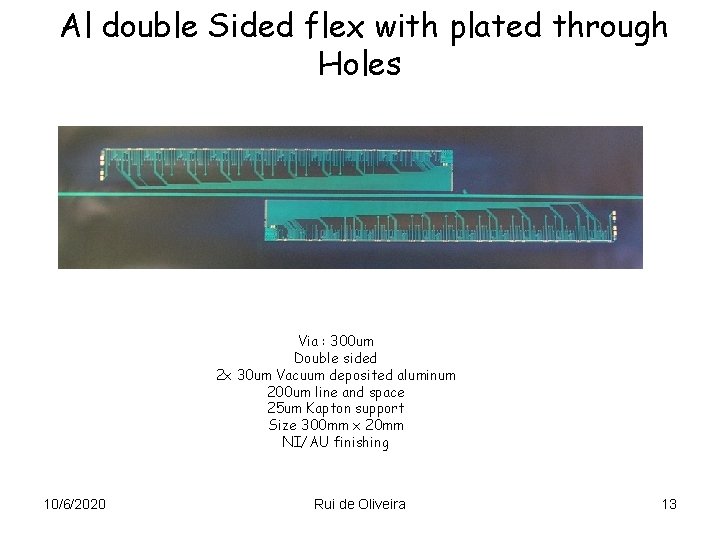

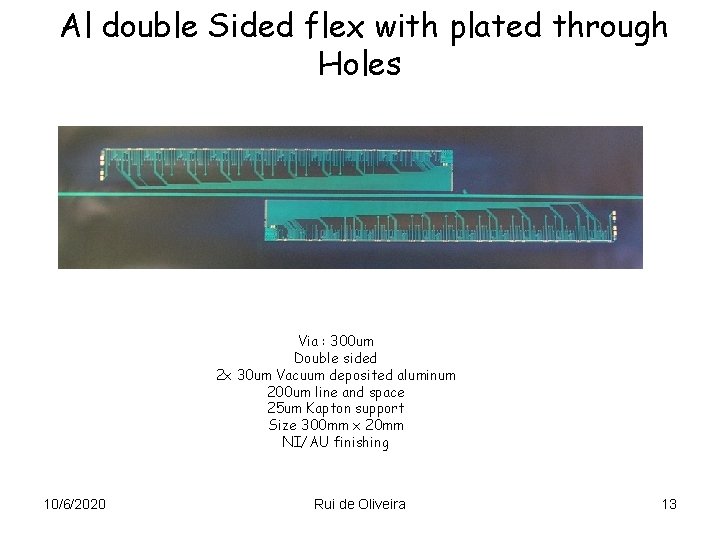

Al double Sided flex with plated through Holes Via : 300 um Double sided 2 x 30 um Vacuum deposited aluminum 200 um line and space 25 um Kapton support Size 300 mm x 20 mm NI/AU finishing 10/6/2020 Rui de Oliveira 13

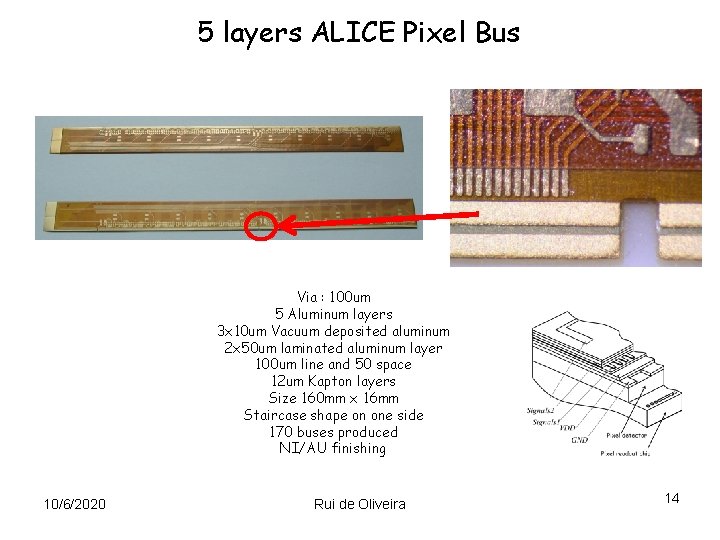

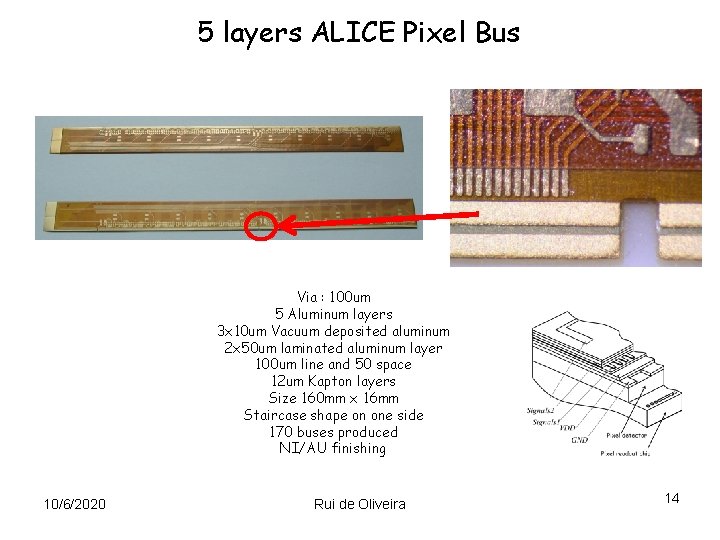

5 layers ALICE Pixel Bus Via : 100 um 5 Aluminum layers 3 x 10 um Vacuum deposited aluminum 2 x 50 um laminated aluminum layer 100 um line and 50 space 12 um Kapton layers Size 160 mm x 16 mm Staircase shape on one side 170 buses produced NI/AU finishing 10/6/2020 Rui de Oliveira 14

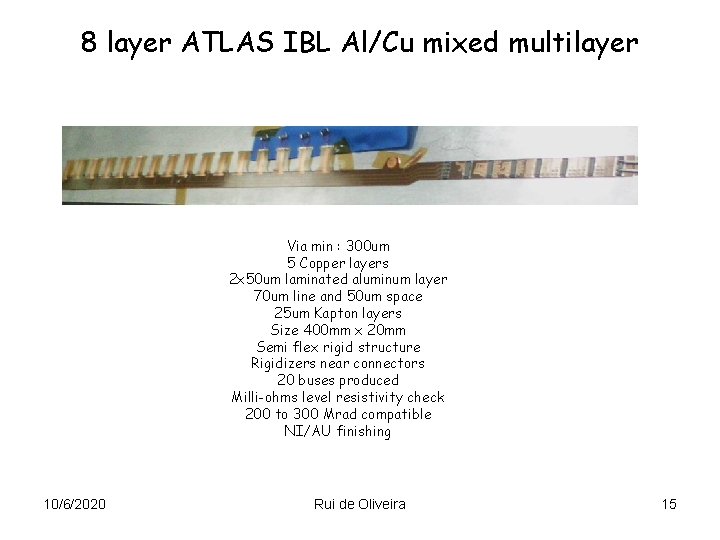

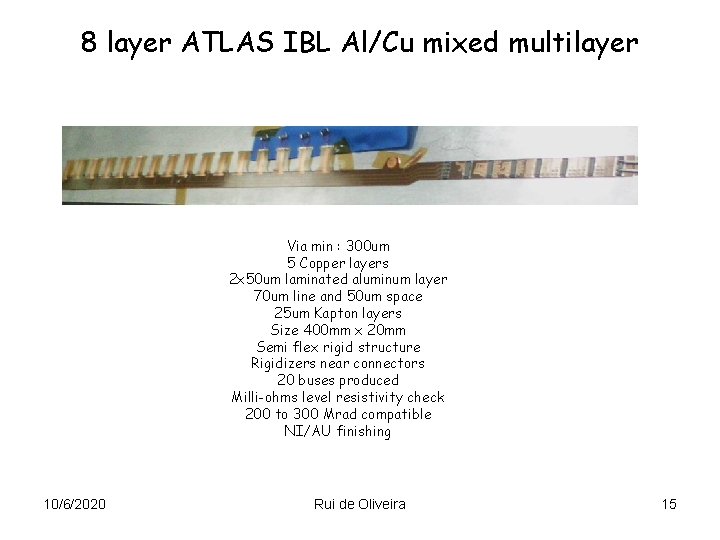

8 layer ATLAS IBL Al/Cu mixed multilayer Via min : 300 um 5 Copper layers 2 x 50 um laminated aluminum layer 70 um line and 50 um space 25 um Kapton layers Size 400 mm x 20 mm Semi flex rigid structure Rigidizers near connectors 20 buses produced Milli-ohms level resistivity check 200 to 300 Mrad compatible NI/AU finishing 10/6/2020 Rui de Oliveira 15

Outline • Aluminium circuits – Material budget /General possibilities – Vias/Microvias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Microchannel 10/6/2020 Rui de Oliveira 16

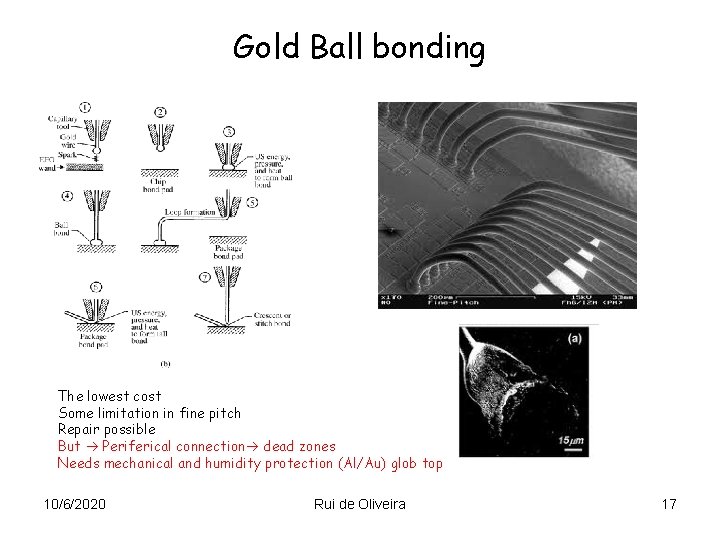

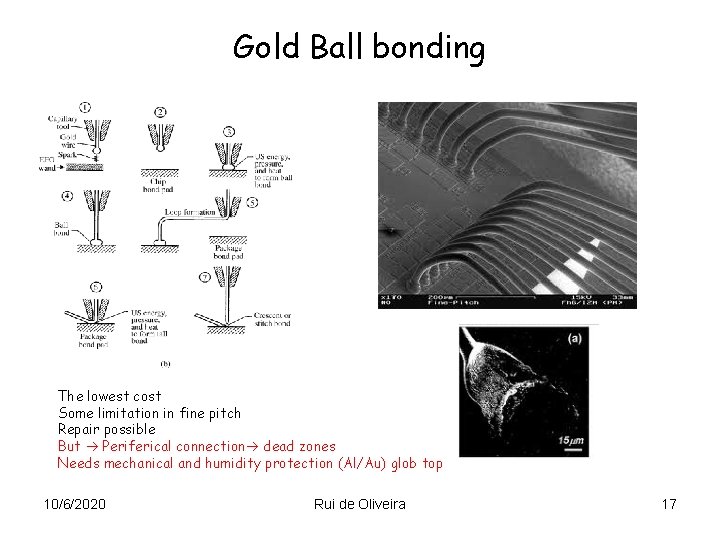

Gold Ball bonding The lowest cost Some limitation in fine pitch Repair possible But Periferical connection dead zones Needs mechanical and humidity protection (Al/Au) glob top 10/6/2020 Rui de Oliveira 17

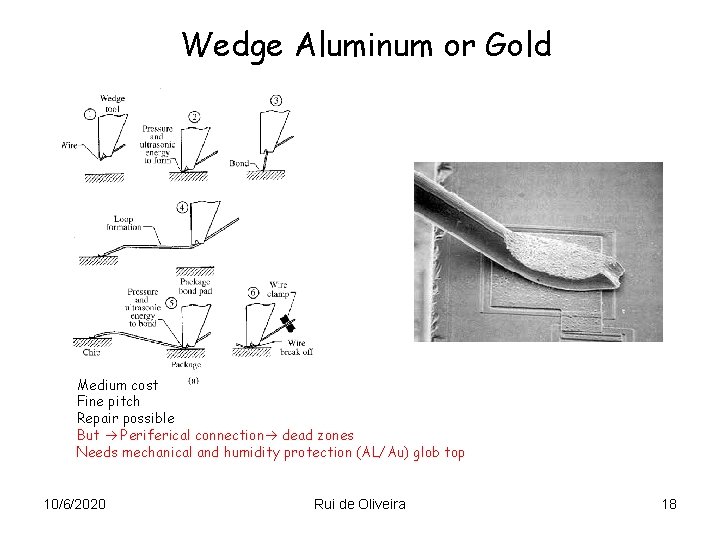

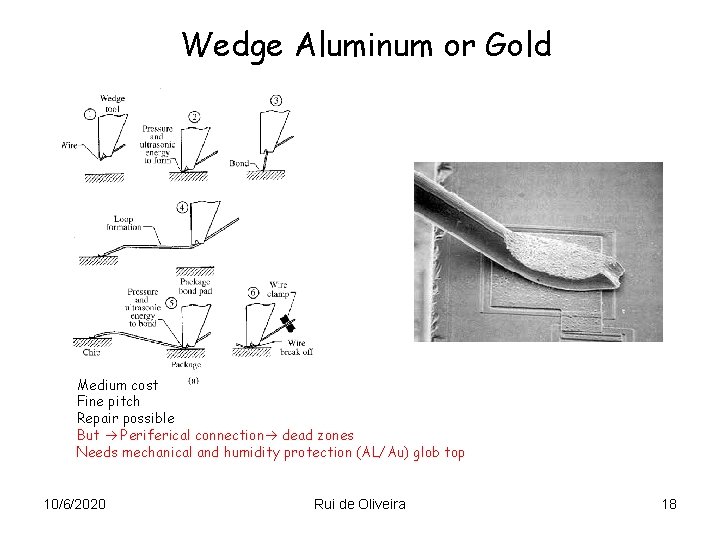

Wedge Aluminum or Gold Medium cost Fine pitch Repair possible But Periferical connection dead zones Needs mechanical and humidity protection (AL/Au) glob top 10/6/2020 Rui de Oliveira 18

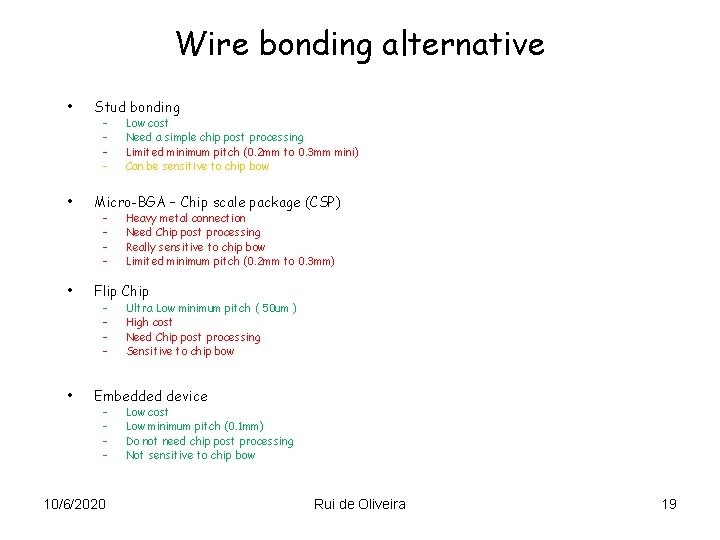

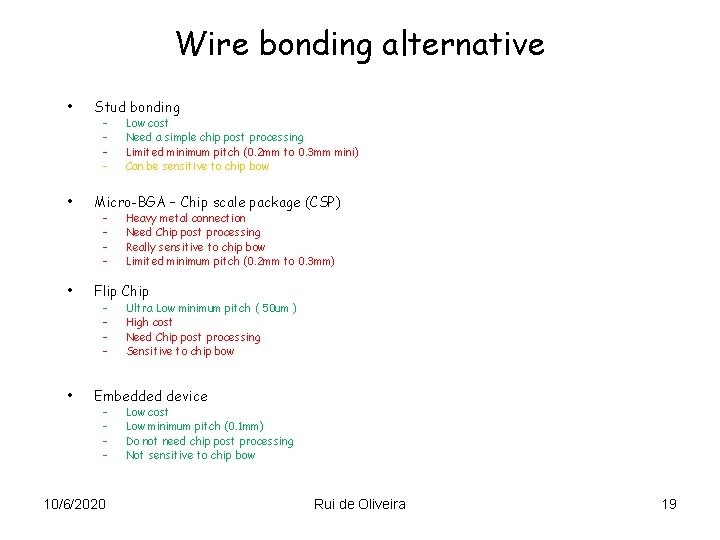

Wire bonding alternative • Stud bonding • Micro-BGA – Chip scale package (CSP) • Flip Chip • Embedded device – – – – 10/6/2020 Low cost Need a simple chip post processing Limited minimum pitch (0. 2 mm to 0. 3 mm mini) Can be sensitive to chip bow Heavy metal connection Need Chip post processing Really sensitive to chip bow Limited minimum pitch (0. 2 mm to 0. 3 mm) Ultra Low minimum pitch ( 50 um ) High cost Need Chip post processing Sensitive to chip bow Low cost Low minimum pitch (0. 1 mm) Do not need chip post processing Not sensitive to chip bow Rui de Oliveira 19

Outline • Aluminum circuits – Material budget /General possibilities – Vias/Micro-vias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding reminder – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Micro-channel 10/6/2020 Rui de Oliveira 20

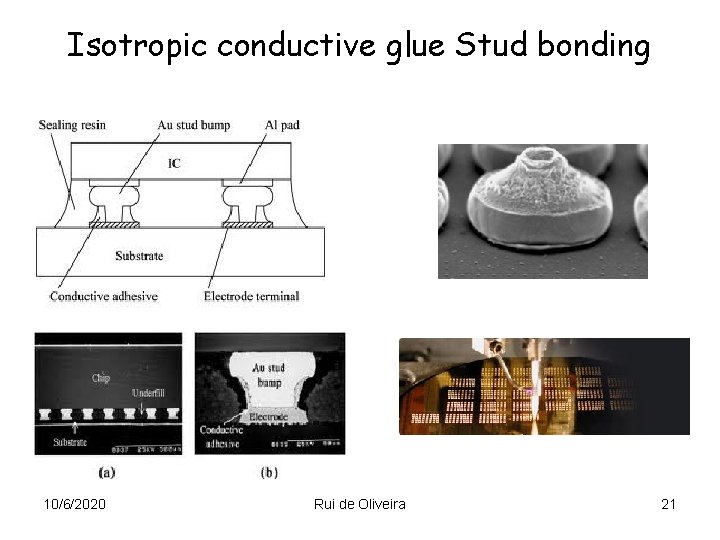

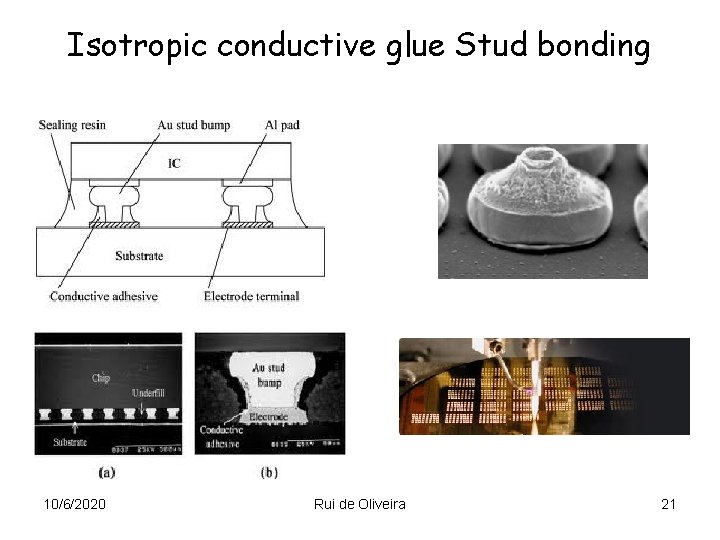

Isotropic conductive glue Stud bonding 10/6/2020 Rui de Oliveira 21

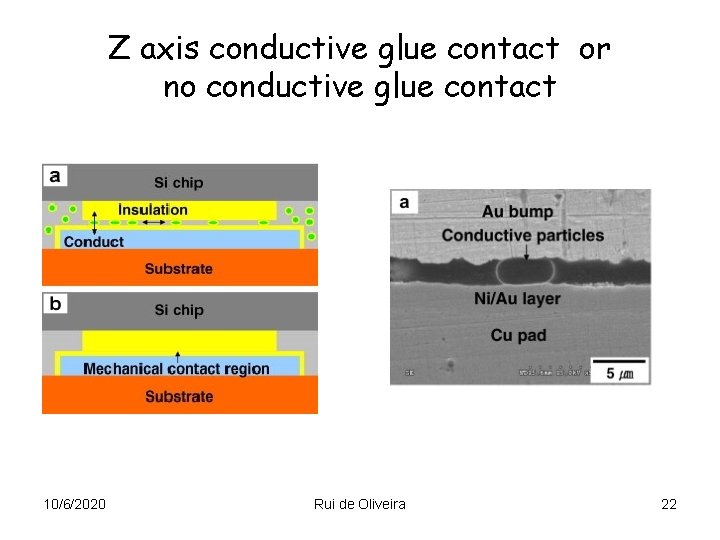

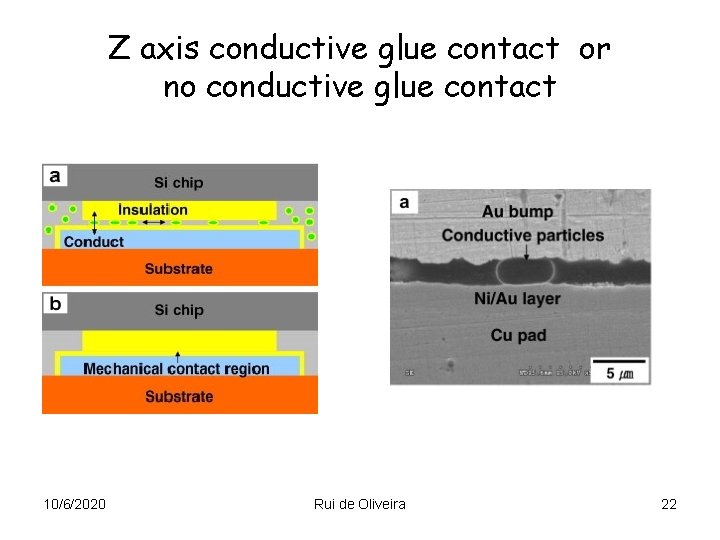

Z axis conductive glue contact or no conductive glue contact 10/6/2020 Rui de Oliveira 22

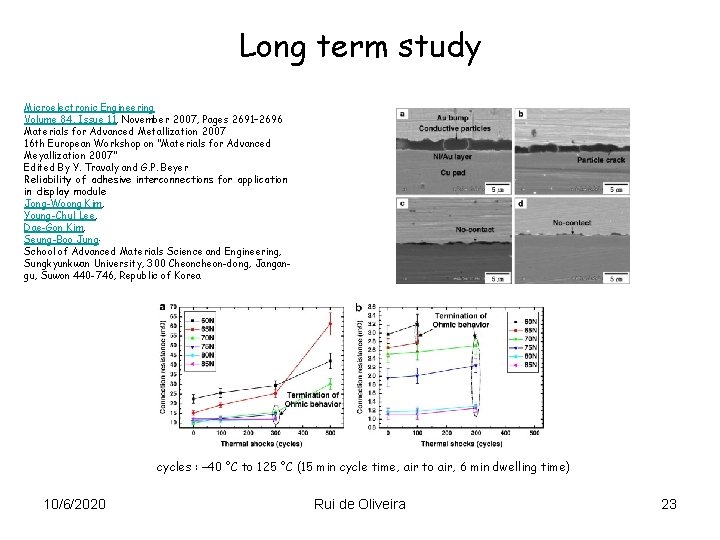

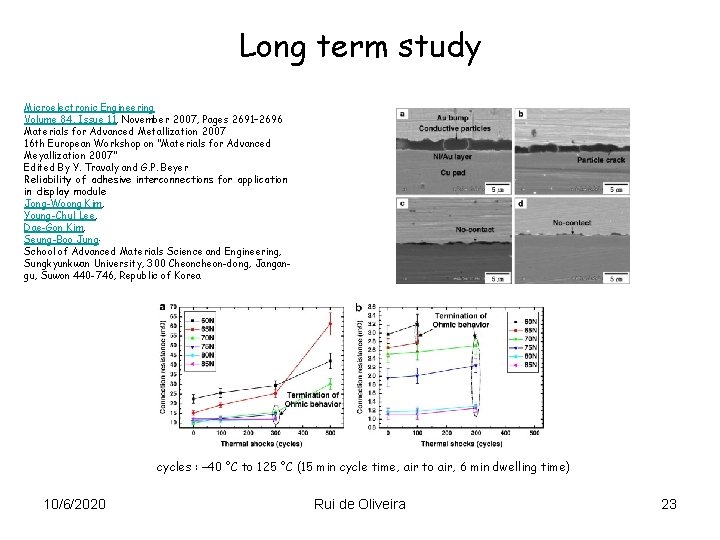

Long term study Microelectronic Engineering Volume 84, Issue 11, November 2007, Pages 2691– 2696 Materials for Advanced Metallization 2007 16 th European Workshop on “Materials for Advanced Meyallization 2007” Edited By Y. Travaly and G. P. Beyer Reliability of adhesive interconnections for application in display module Jong-Woong Kim, Young-Chul Lee, Dae-Gon Kim, Seung-Boo Jung, School of Advanced Materials Science and Engineering, Sungkyunkwan University, 300 Cheoncheon-dong, Jangangu, Suwon 440 -746, Republic of Korea cycles : − 40 °C to 125 °C (15 min cycle time, air to air, 6 min dwelling time) 10/6/2020 Rui de Oliveira 23

outline • Aluminum circuits – Material budget /General possibilities – Vias/Micro-vias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Micro-channel 10/6/2020 Rui de Oliveira 24

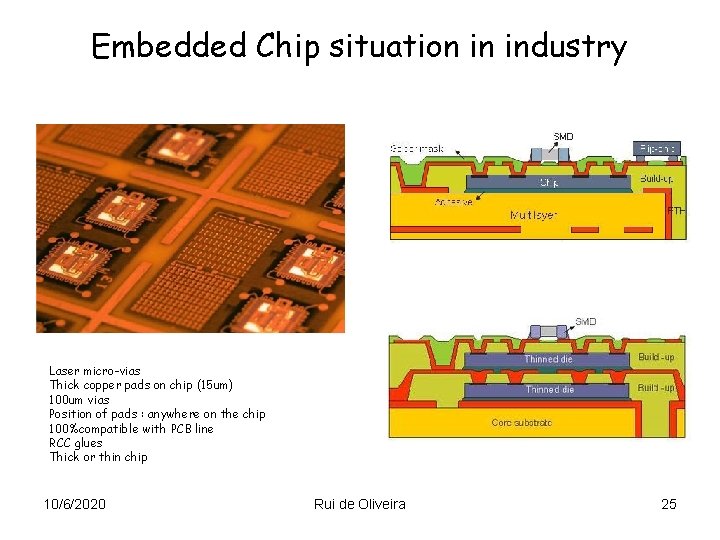

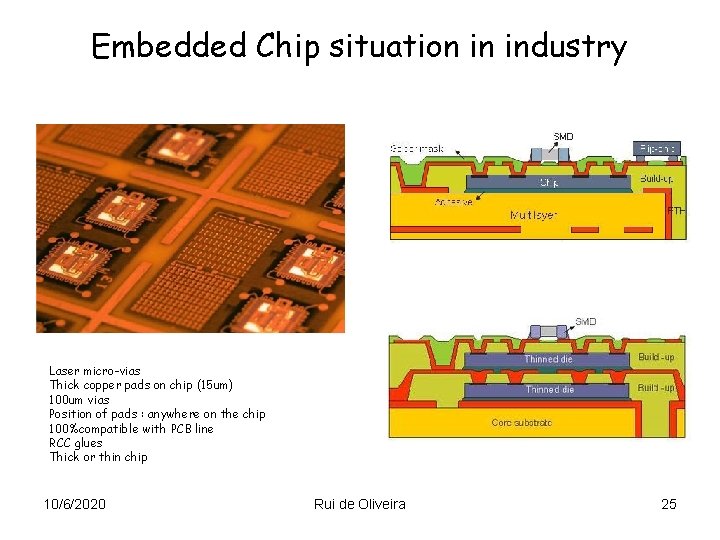

Embedded Chip situation in industry Laser micro-vias Thick copper pads on chip (15 um) 100 um vias Position of pads : anywhere on the chip 100%compatible with PCB line RCC glues Thick or thin chip 10/6/2020 Rui de Oliveira 25

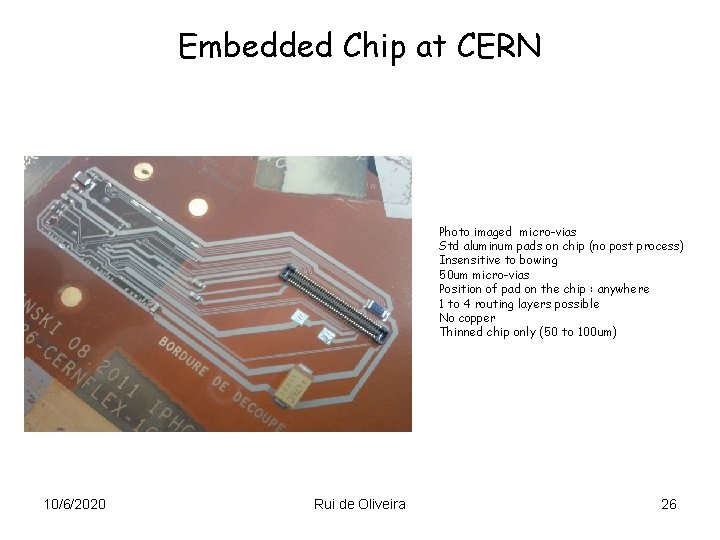

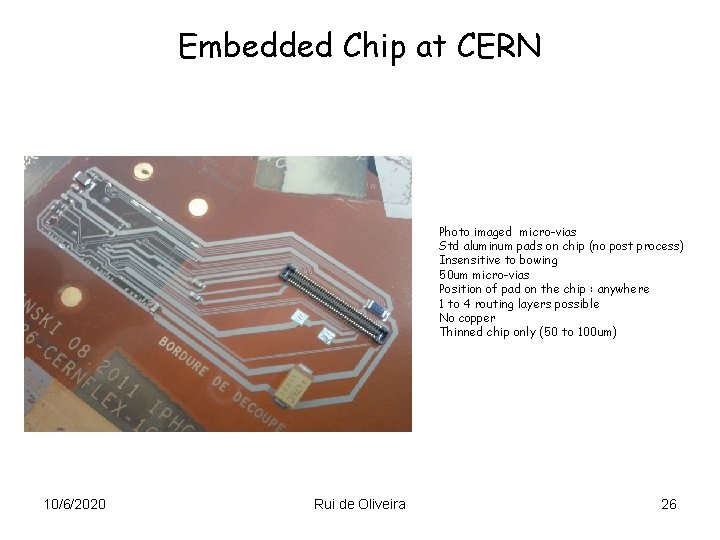

Embedded Chip at CERN Photo imaged micro-vias Std aluminum pads on chip (no post process) Insensitive to bowing 50 um micro-vias Position of pad on the chip : anywhere 1 to 4 routing layers possible No copper Thinned chip only (50 to 100 um) 10/6/2020 Rui de Oliveira 26

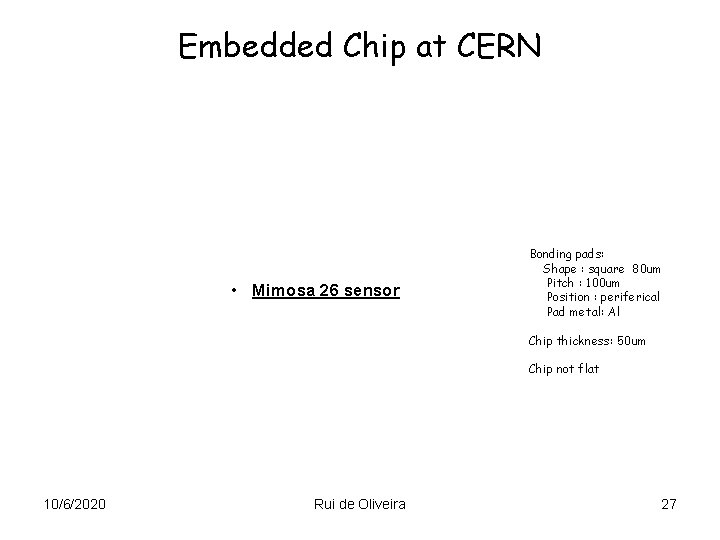

Embedded Chip at CERN • Mimosa 26 sensor Bonding pads: Shape : square 80 um Pitch : 100 um Position : periferical Pad metal: Al Chip thickness: 50 um Chip not flat 10/6/2020 Rui de Oliveira 27

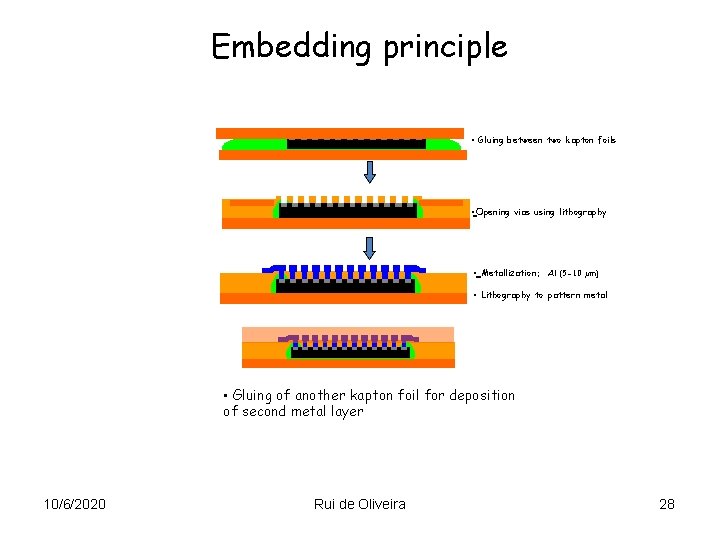

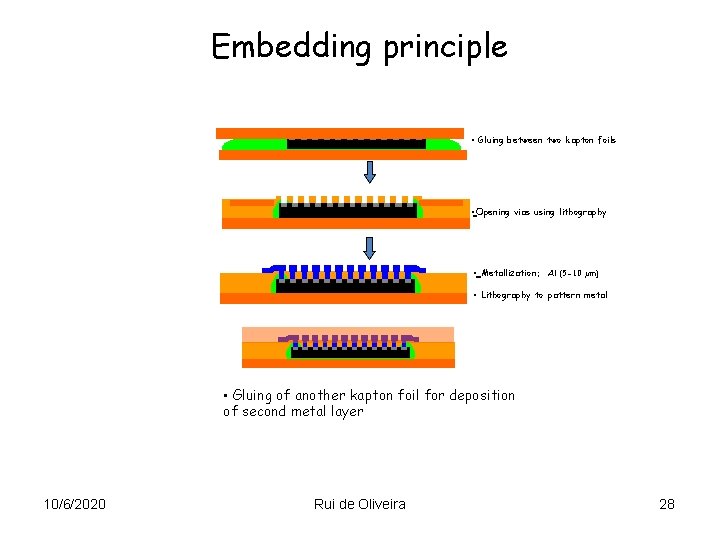

Embedding principle • Gluing between two kapton foils • Opening vias using lithography • Metallization: Al (5 -10 µm) • Lithography to pattern metal • Gluing of another kapton foil for deposition of second metal layer 10/6/2020 Rui de Oliveira 28

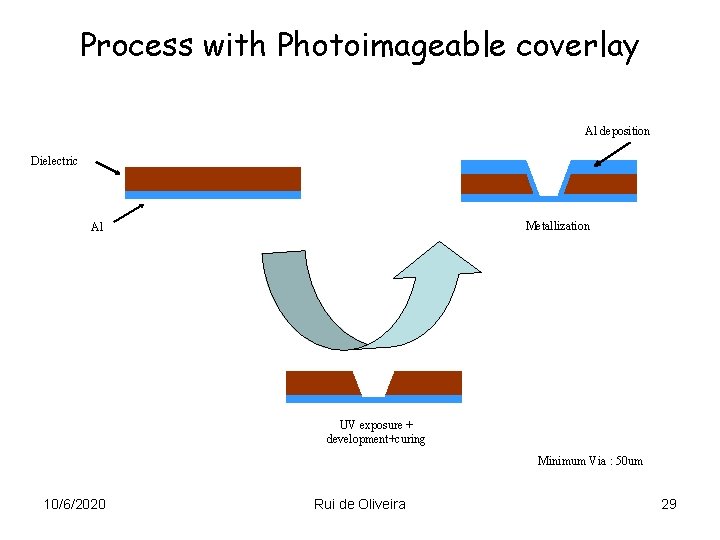

Process with Photoimageable coverlay Al deposition Dielectric Metallization Al UV exposure + development+curing Minimum Via : 50 um 10/6/2020 Rui de Oliveira 29

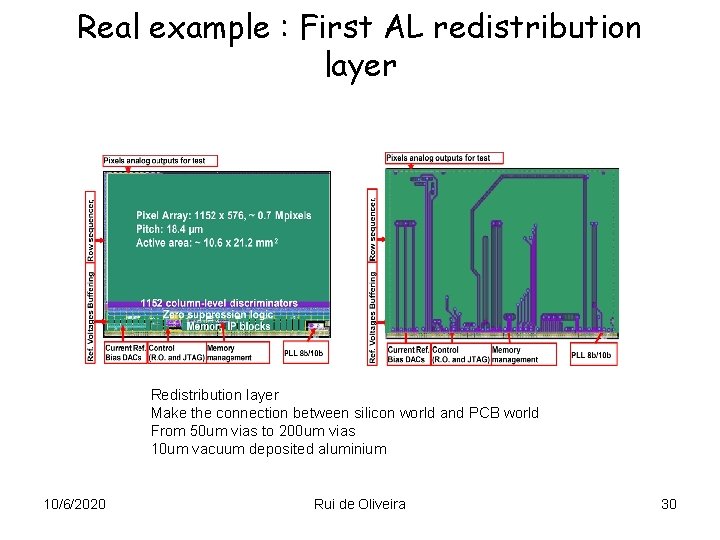

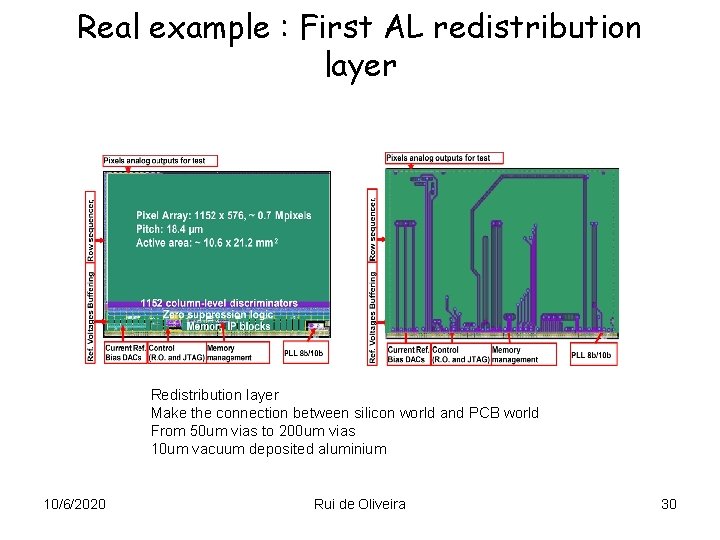

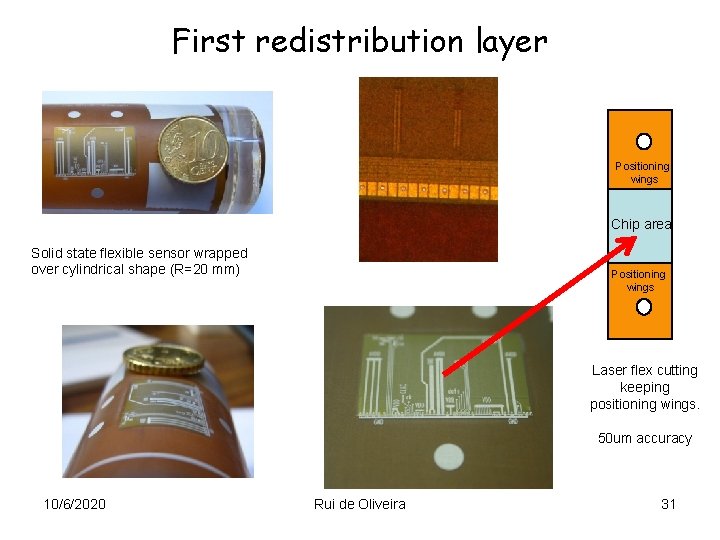

Real example : First AL redistribution layer Redistribution layer Make the connection between silicon world and PCB world From 50 um vias to 200 um vias 10 um vacuum deposited aluminium 10/6/2020 Rui de Oliveira 30

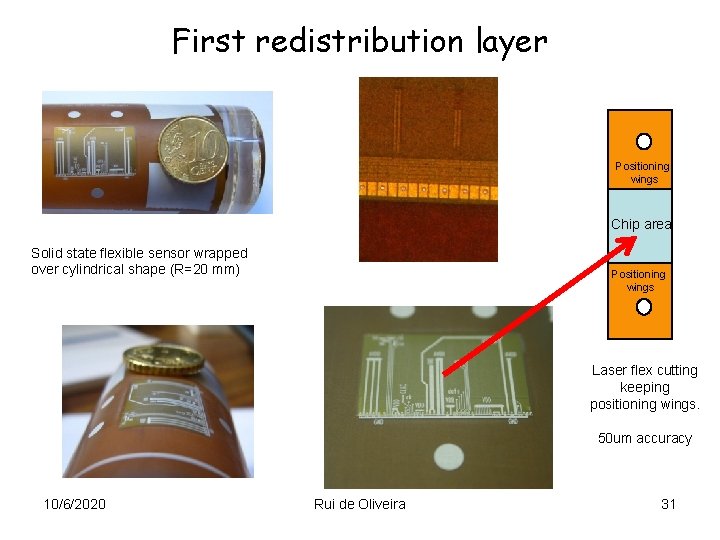

First redistribution layer Positioning wings Chip area Solid state flexible sensor wrapped over cylindrical shape (R=20 mm) Positioning wings Laser flex cutting keeping positioning wings. 50 um accuracy 10/6/2020 Rui de Oliveira 31

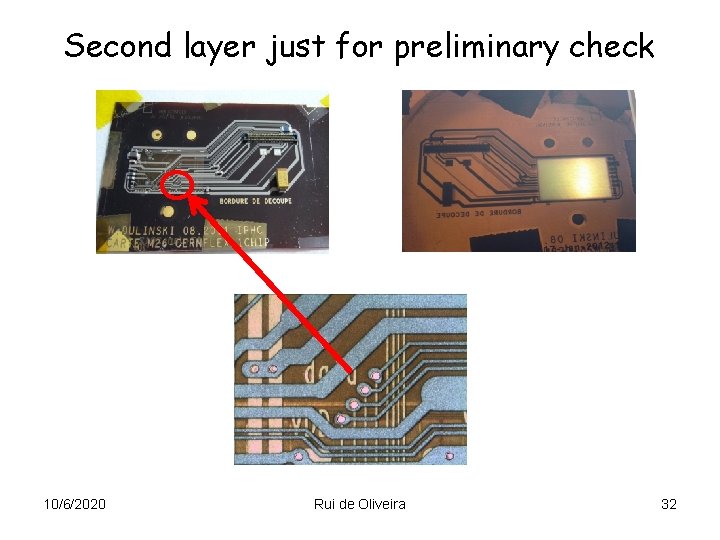

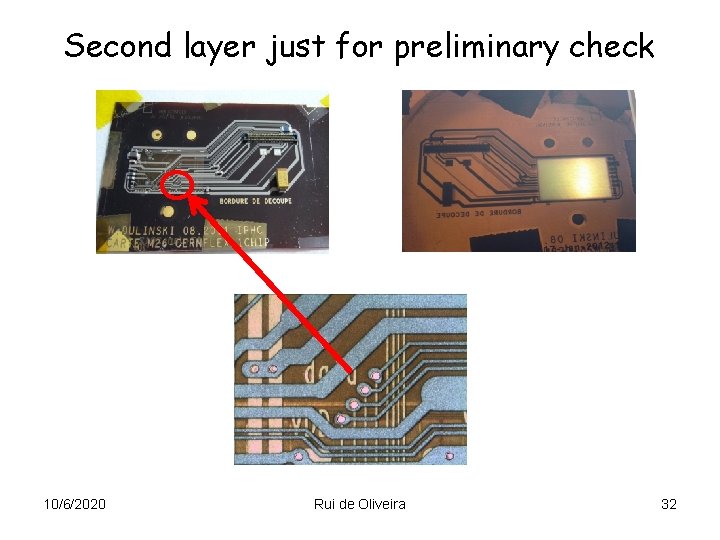

Second layer just for preliminary check 10/6/2020 Rui de Oliveira 32

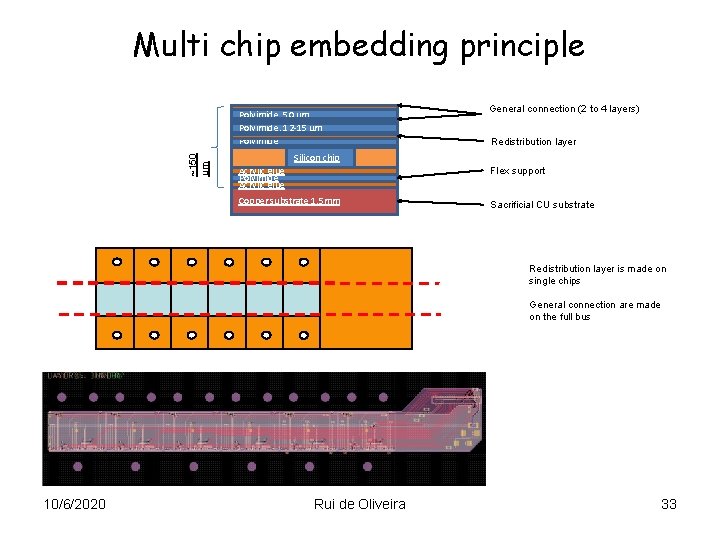

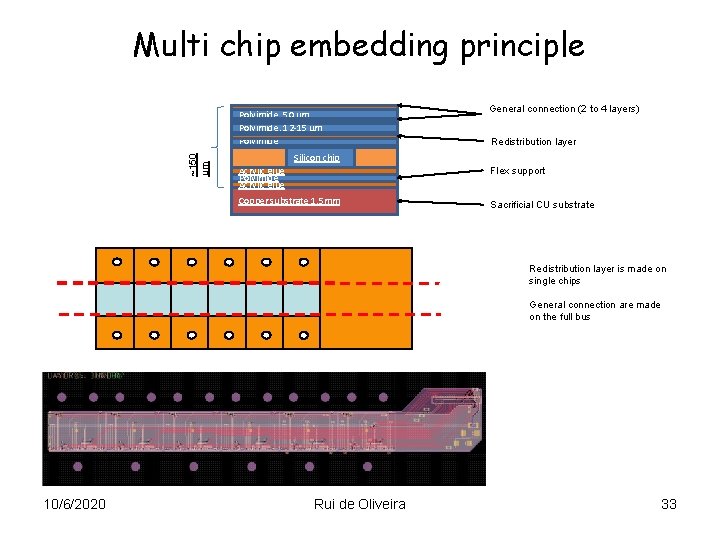

Multi chip embedding principle ~150 µm Polyimide, 12 -15 µm Polyimide General connection (2 to 4 layers) Redistribution layer Silicon chip Acrylic glue Polyimide Acrylic glue Flex support Copper substrate 1. 5 mm Sacrificial CU substrate Redistribution layer is made on single chips General connection are made on the full bus 10/6/2020 Rui de Oliveira 33

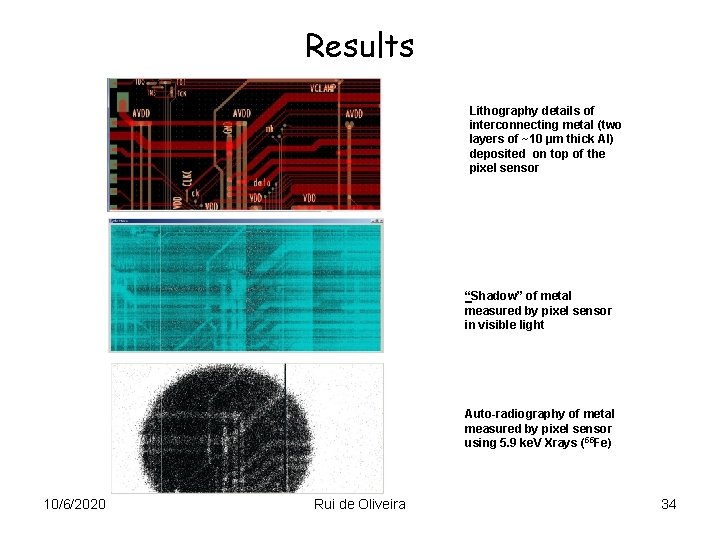

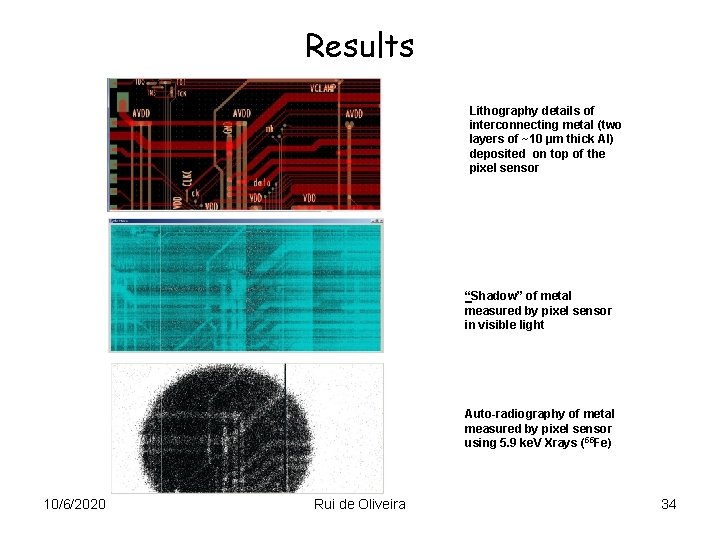

Results Lithography details of interconnecting metal (two layers of ~10 µm thick Al) deposited on top of the pixel sensor “Shadow” of metal measured by pixel sensor in visible light Auto-radiography of metal measured by pixel sensor using 5. 9 ke. V Xrays (55 Fe) 10/6/2020 Rui de Oliveira 34

outline • Aluminum circuits – Material budget /General possibilities – Vias/Micro-vias – Finishing possibilities – Different examples • Wire bonding alternatives – Wire bonding – Stud bump – Embedded active devices • Low mass cooling structures – Polymer Micro-channel 10/6/2020 Rui de Oliveira 35

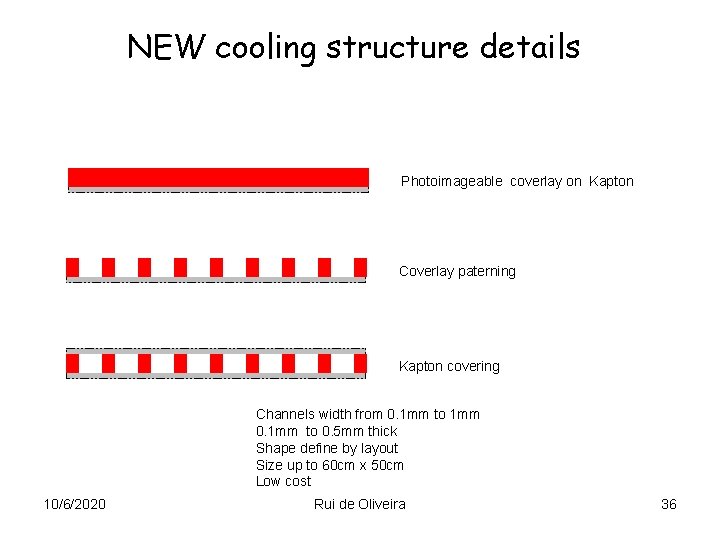

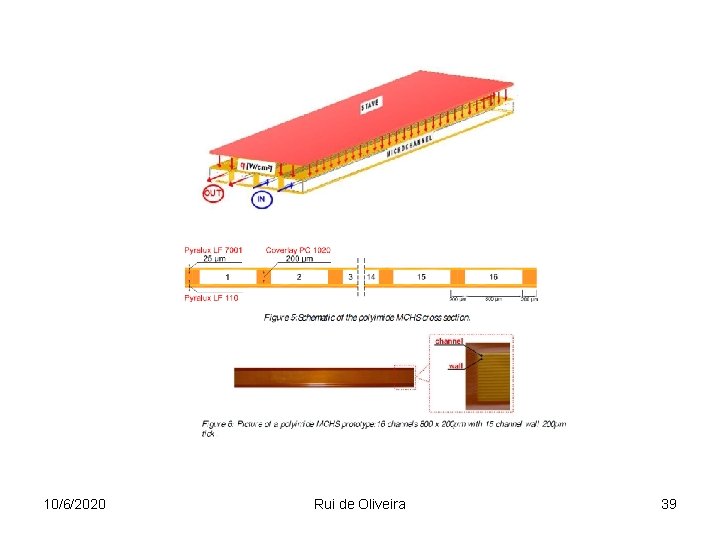

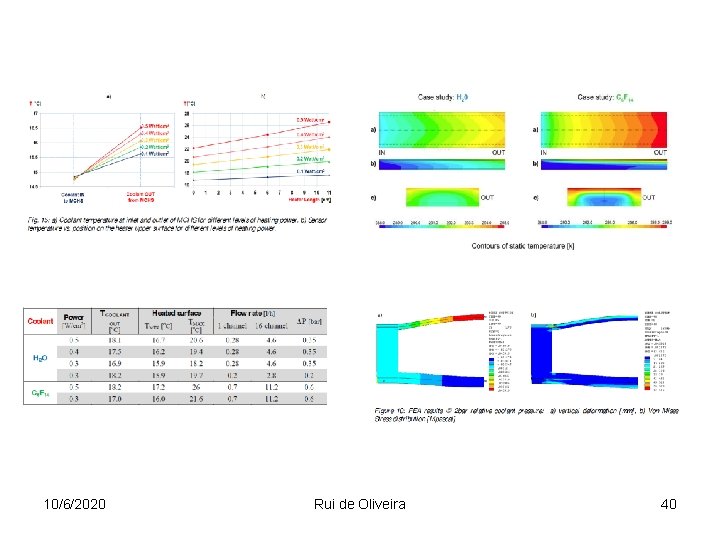

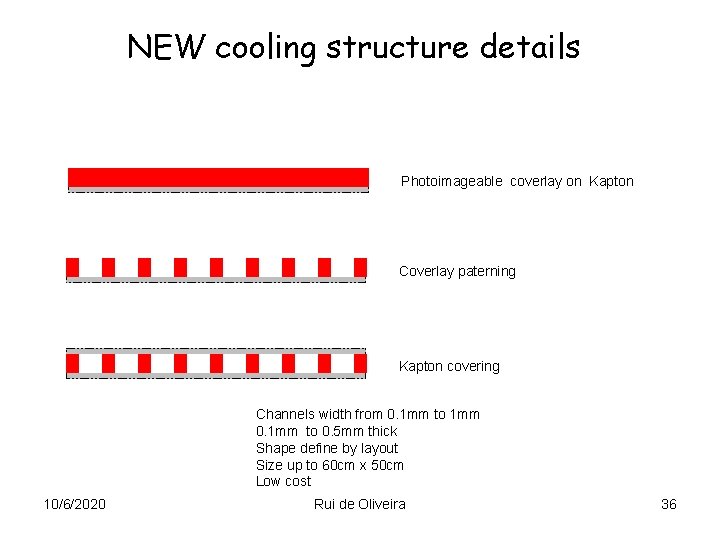

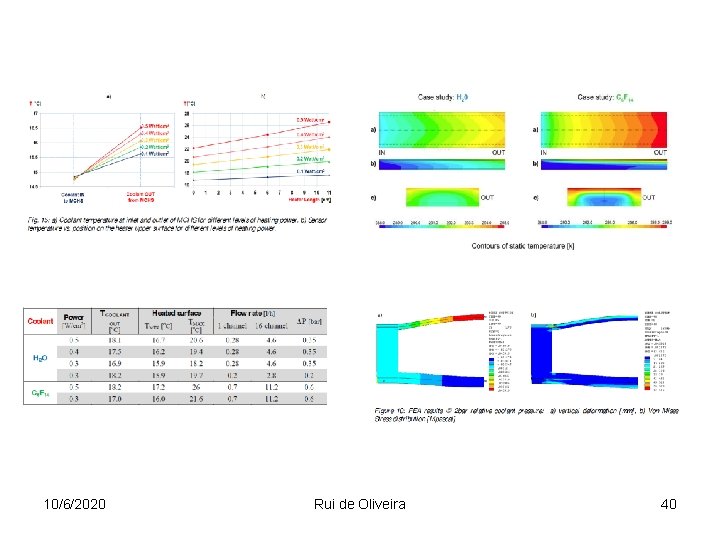

NEW cooling structure details Photoimageable coverlay on Kapton Coverlay paterning Kapton covering Channels width from 0. 1 mm to 1 mm 0. 1 mm to 0. 5 mm thick Shape define by layout Size up to 60 cm x 50 cm Low cost 10/6/2020 Rui de Oliveira 36

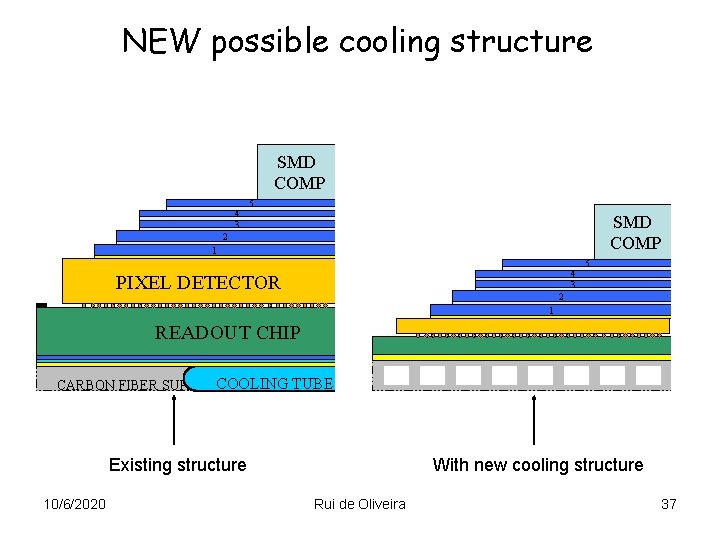

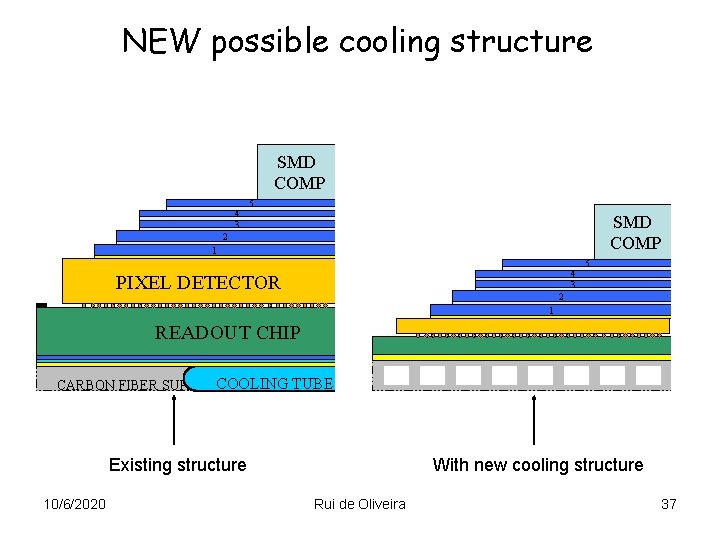

NEW possible cooling structure SMD COMP 4 3 5 SMD COMP 2 1 4 3 PIXEL DETECTOR 5 2 1 READOUT CHIP CARBON FIBER SUPPORTCOOLING TUBE Existing structure 10/6/2020 With new cooling structure Rui de Oliveira 37

10/6/2020 Rui de Oliveira 38

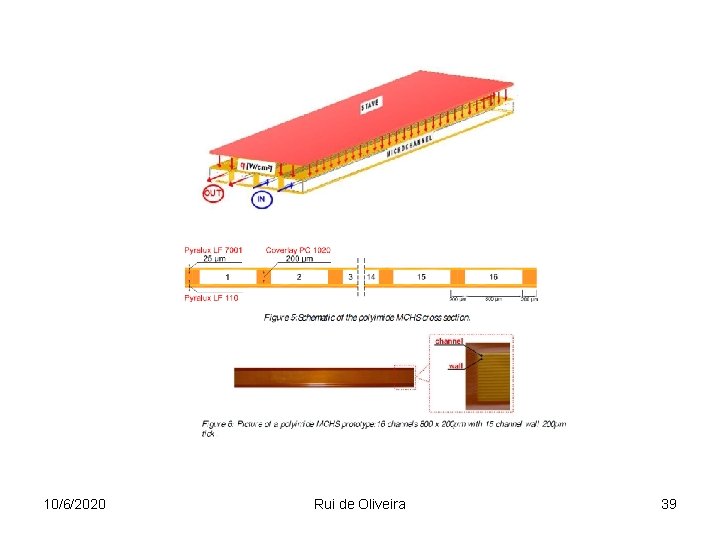

10/6/2020 Rui de Oliveira 39

10/6/2020 Rui de Oliveira 40

Future • Dedicate some equipment's for AL processes to reduce production time and costs. • Build a 2 chip Embedded structure and then probably 6 chip. • Continue characterization of Cooling device for Alice project. 10/6/2020 Rui de Oliveira 41