Logick funkce a obvody VY32INOVACEpszczolka07 3 13 generatorparity

Logické funkce a obvody VY_32_INOVACE_pszczolka_07 -3 -13 -generator_parity Autor: Pszczółka Tomáš Tento výukový materiál byl zpracován v rámci projektu EU peníze středním školám - OP VK 1. 5. CZ. 1. 07/1. 5. 00/34. 0195 – Individualizace a inovace výuky

Anotace ü Žák pozná složitější logický obvod - generátor parity a bude chápat jeho strukturu a funkci. ü Dále na základě dřívějších teoretických poznatků, bude schopen simulovat funkci obvodu.

Generátor parity - Úvod ü Patří do oblasti kombinačních logických obvodů a je realizovaný z Ex. OR logických členů. ü Je schopen rozpoznat chybu v binárním slově. ü Při přenosech číslicového signálu generátor parity generuje tzv. paritní bit (PB).

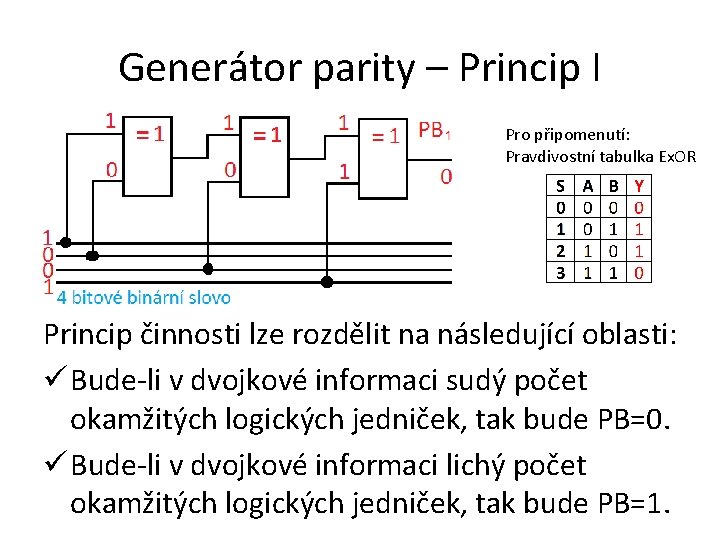

Generátor parity – Princip I Pro připomenutí: Pravdivostní tabulka Ex. OR Princip činnosti lze rozdělit na následující oblasti: ü Bude-li v dvojkové informaci sudý počet okamžitých logických jedniček, tak bude PB=0. ü Bude-li v dvojkové informaci lichý počet okamžitých logických jedniček, tak bude PB=1.

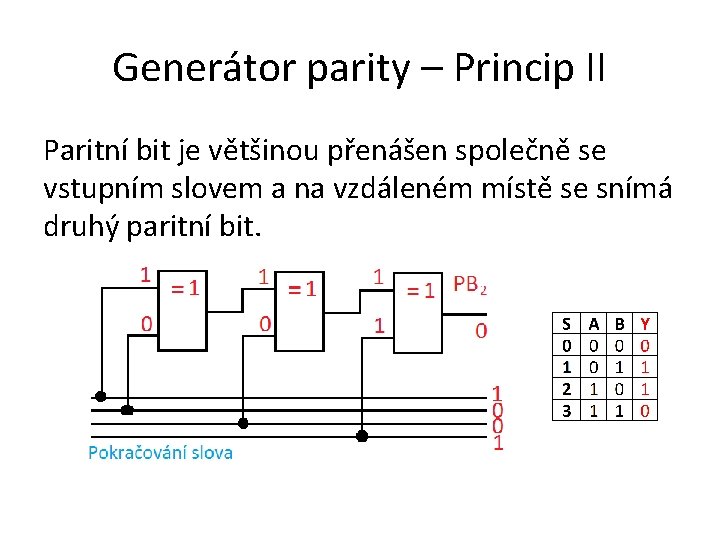

Generátor parity – Princip II Paritní bit je většinou přenášen společně se vstupním slovem a na vzdáleném místě se snímá druhý paritní bit.

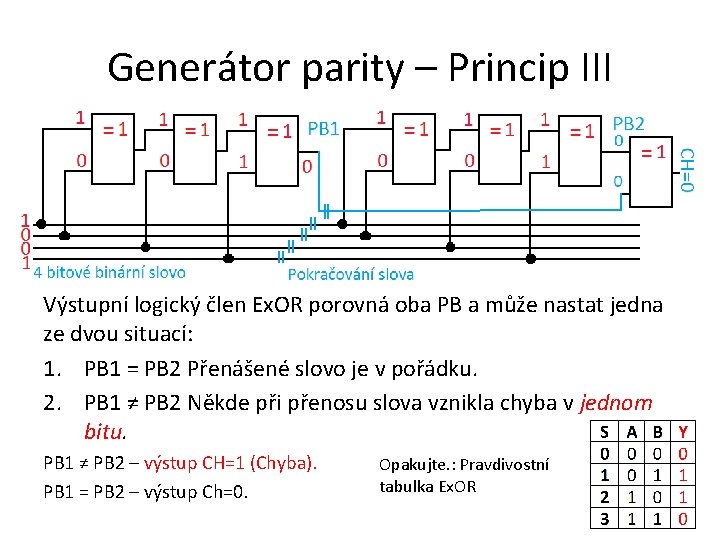

Generátor parity – Princip III Výstupní logický člen Ex. OR porovná oba PB a může nastat jedna ze dvou situací: 1. PB 1 = PB 2 Přenášené slovo je v pořádku. 2. PB 1 ≠ PB 2 Někde při přenosu slova vznikla chyba v jednom bitu. PB 1 ≠ PB 2 – výstup CH=1 (Chyba). PB 1 = PB 2 – výstup Ch=0. Opakujte. : Pravdivostní tabulka Ex. OR

Generátor Parity – Chyba ve více bitech ü Předpokládá se, že zde vznikne chyba pouze v jednom bitu přenášeného slova. ü V případě vzniku přenosové chyby ve 2, 4. . . bitech, chyba nebude odhalena! ü Tato nekorektnost je dána stavbou generátoru. Protože při dvojí chybě pořád PB zůstane stejný!

POUŽITÁ LITERATURA 1. KESL, Jan. Elektronika 3: Číslicová technika. 2. vyd. Praha: BEN - technická literatura, 2008, ISBN 978 -80 -7300 -182 -7

- Slides: 8