Logic Synthesis for Programmable Devices Onur Bay Debatosh

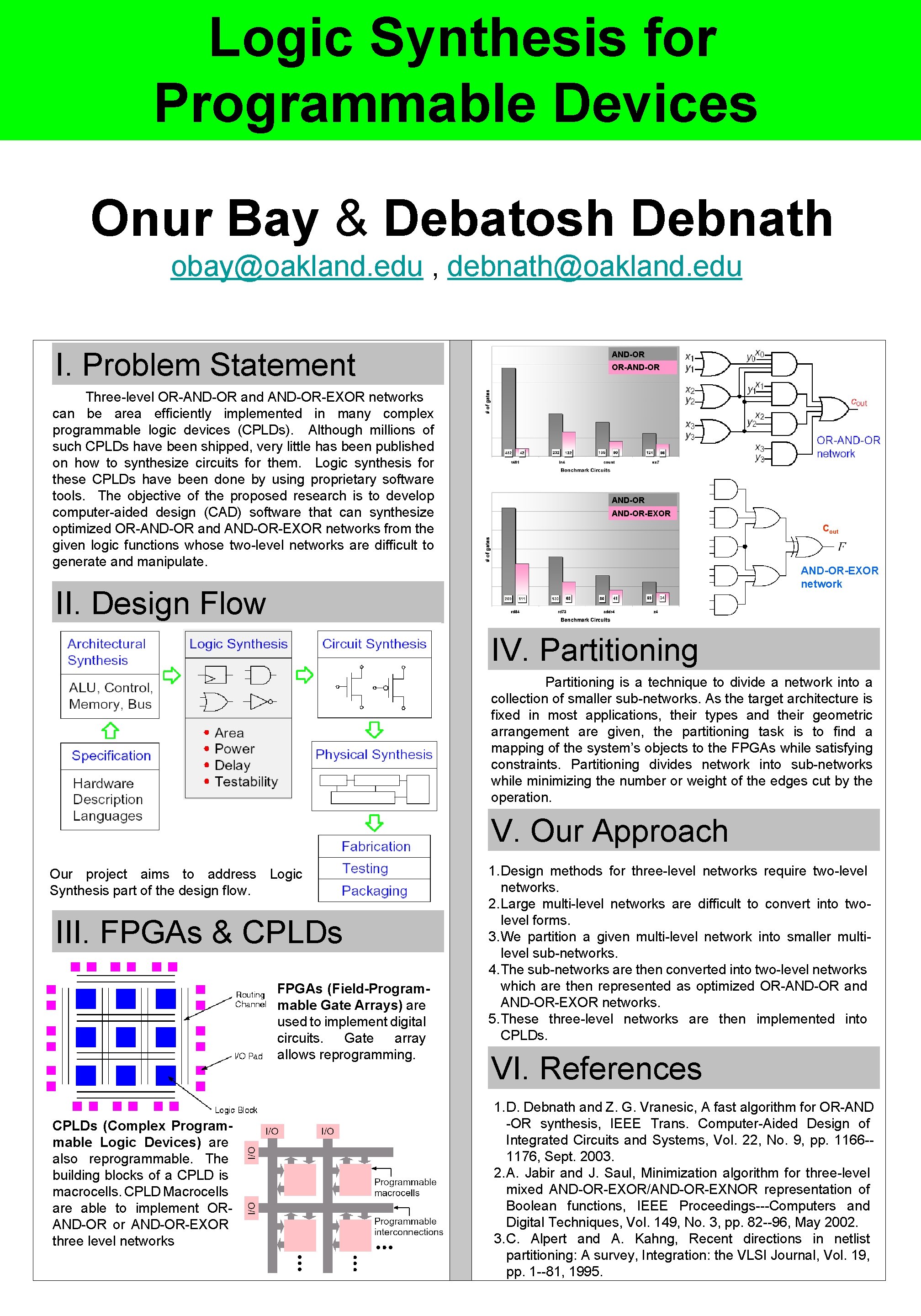

Logic Synthesis for Programmable Devices Onur Bay & Debatosh Debnath obay@oakland. edu , debnath@oakland. edu I. Problem Statement Three-level OR-AND-OR and AND-OR-EXOR networks can be area efficiently implemented in many complex programmable logic devices (CPLDs). Although millions of such CPLDs have been shipped, very little has been published on how to synthesize circuits for them. Logic synthesis for these CPLDs have been done by using proprietary software tools. The objective of the proposed research is to develop computer-aided design (CAD) software that can synthesize optimized OR-AND-OR and AND-OR-EXOR networks from the given logic functions whose two-level networks are difficult to generate and manipulate. AND-OR OR-AND-OR-EXOR Cout AND-OR-EXOR network II. Design Flow IV. Partitioning is a technique to divide a network into a collection of smaller sub-networks. As the target architecture is fixed in most applications, their types and their geometric arrangement are given, the partitioning task is to find a mapping of the system’s objects to the FPGAs while satisfying constraints. Partitioning divides network into sub-networks while minimizing the number or weight of the edges cut by the operation. V. Our Approach Our project aims to address Logic Synthesis part of the design flow. III. FPGAs & CPLDs FPGAs (Field-Programmable Gate Arrays) are used to implement digital circuits. Gate array allows reprogramming. CPLDs (Complex Programmable Logic Devices) are also reprogrammable. The building blocks of a CPLD is macrocells. CPLD Macrocells are able to implement ORAND-OR or AND-OR-EXOR three level networks 1. Design methods for three-level networks require two-level networks. 2. Large multi-level networks are difficult to convert into twolevel forms. 3. We partition a given multi-level network into smaller multilevel sub-networks. 4. The sub-networks are then converted into two-level networks which are then represented as optimized OR-AND-OR and AND-OR-EXOR networks. 5. These three-level networks are then implemented into CPLDs. VI. References 1. D. Debnath and Z. G. Vranesic, A fast algorithm for OR-AND -OR synthesis, IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, Vol. 22, No. 9, pp. 1166 -1176, Sept. 2003. 2. A. Jabir and J. Saul, Minimization algorithm for three-level mixed AND-OR-EXOR/AND-OR-EXNOR representation of Boolean functions, IEEE Proceedings---Computers and Digital Techniques, Vol. 149, No. 3, pp. 82 --96, May 2002. 3. C. Alpert and A. Kahng, Recent directions in netlist partitioning: A survey, Integration: the VLSI Journal, Vol. 19, pp. 1 --81, 1995.

- Slides: 1