LHCb upgrade Electronics Architecture Review General Architecture Front

LHCb upgrade Electronics Architecture Review General Architecture & Front -end Ken Wyllie, CERN 1 Architecture Review, 5 th Dec 2012

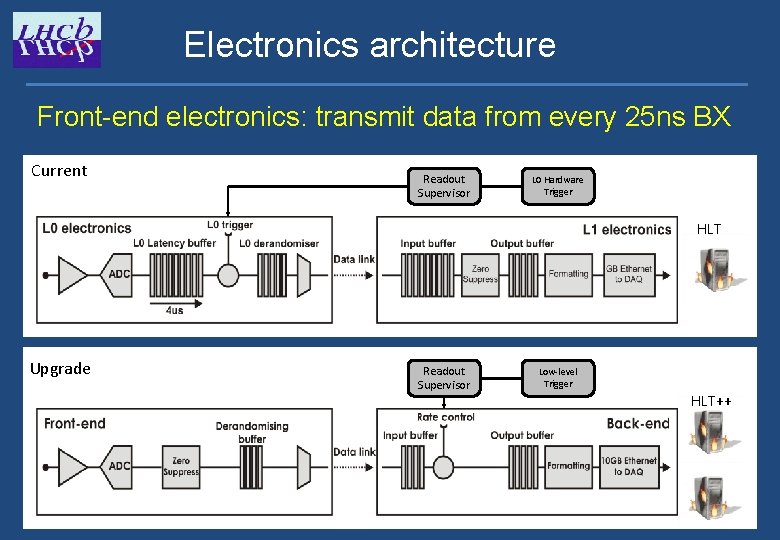

Electronics architecture Front-end electronics: transmit data from every 25 ns BX Current Readout Supervisor L 0 Hardware Trigger HLT 1 MHz event rate Upgrade Ken Wyllie, CERN Readout Supervisor 40 MHz event rate 2 Low-level Trigger HLT++ Architecture Review, 5 th Dec 2012

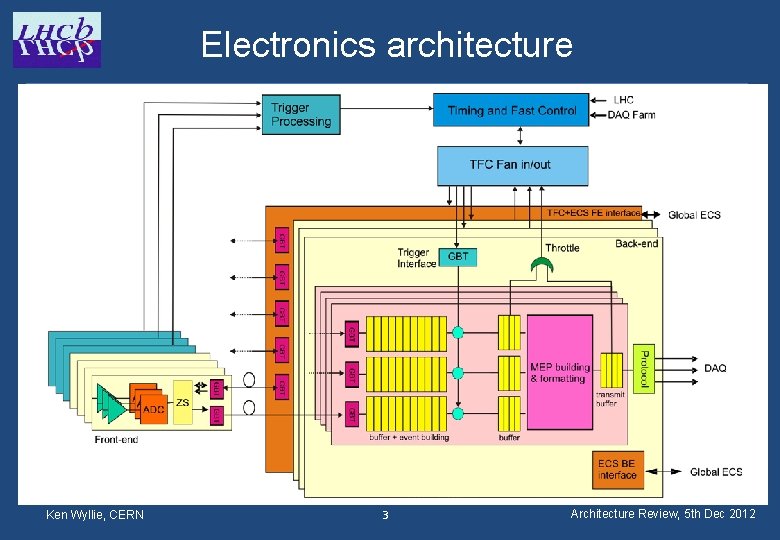

Electronics architecture Ken Wyllie, CERN 3 Architecture Review, 5 th Dec 2012

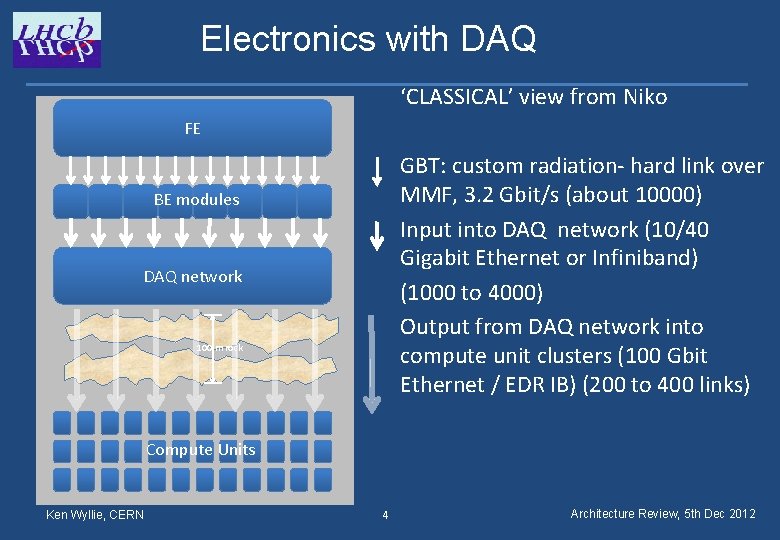

Electronics with DAQ ‘CLASSICAL’ view from Niko FE GBT: custom radiation- hard link over MMF, 3. 2 Gbit/s (about 10000) Input into DAQ network (10/40 Gigabit Ethernet or Infiniband) (1000 to 4000) Output from DAQ network into compute unit clusters (100 Gbit Ethernet / EDR IB) (200 to 400 links) BE modules DAQ network 100 m rock Compute Units Ken Wyllie, CERN 4 Architecture Review, 5 th Dec 2012

General architecture: highlights & open issues Adopted generic link for FE GBT chipset + Versatile Link (VL) optics All BE hardware will be common (carrierboard + AMCs) TELL 40 for data FE TFC/ECS interface (SOL 40) TFC LLT interface (more from Jean-Pierre) ATCA baseline technology Location of TELL 40 + switch not yet decided (pit or surface) Long distance transmission with VL under study Ken Wyllie, CERN 5 Architecture Review, 5 th Dec 2012

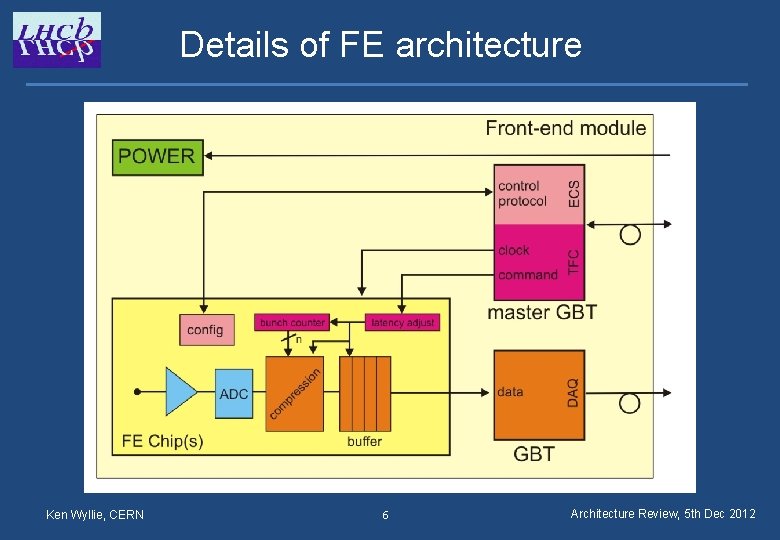

Details of FE architecture Ken Wyllie, CERN 6 Architecture Review, 5 th Dec 2012

Sub-detector specific blocks 1 Data compression Driven by cost (minimise links) Zero-suppression => clear advantage in low occupancy detectors BUT some have high occupancy => no ZS, buy links Compression recipes vary: little common overlap FE buffer Use link bandwidth efficiently Riskiest part of system (eg unforeseen background fills up bandwidth) Sub-detectors must make best estimate from simulations use safety factor make system scale-able? If buffer overflow => truncation of payload data Architecture Review, 5 th Dec 2012 7 Ken Wyllie, CERN

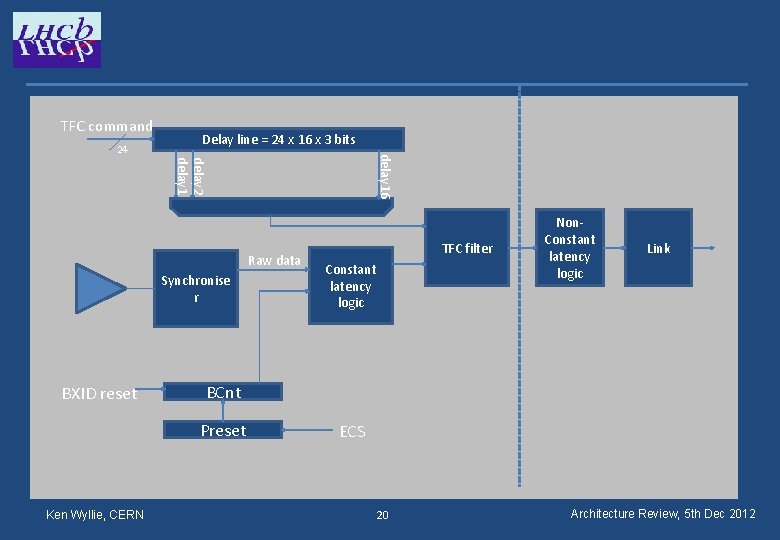

Sub-detector specific blocks 2 Non-ZS data Requested by some sub-detectors (for tuning/diagnostics) Send as part of normal data stream (controlled by TFC) Buffering implications to be understood BXID Data tagged with BXID early BXID reset is main tool for overall synchronisation All synch-checks, event building, LLT based on BXID Tune-able preset of BXID counter BXID is ALWAYS transmitted as part of header (even during truncation) Ken Wyllie, CERN 8 Architecture Review, 5 th Dec 2012

Sub-detector specific blocks 3 Fast commands from TFC (see Federico) Pre-delayed to match transmission latency Resets & other special fast commands Storing instantaneous state of FE (then read thru ECS) Running modes Configured by ECS (ie not on-the-fly) Diagnostic patterns for measuring link latencies Test features Electrical pulse, triggered light source, cosmics Digital patterns generated by FE Ken Wyllie, CERN 9 Architecture Review, 5 th Dec 2012

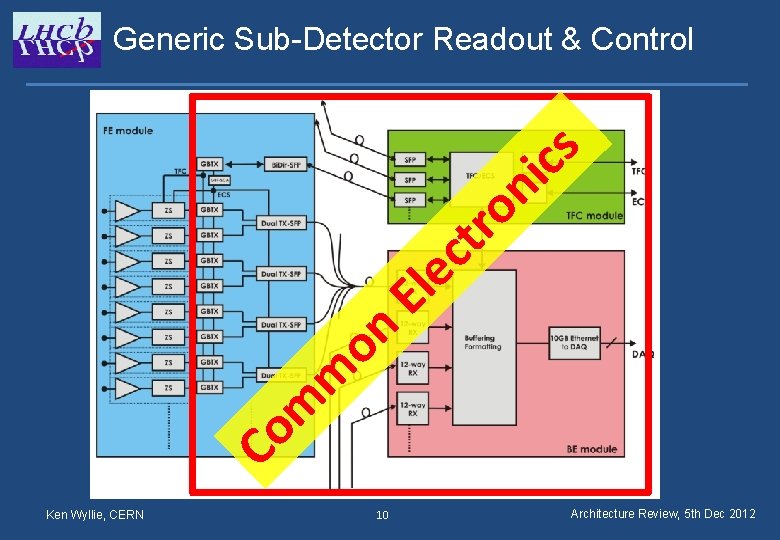

Generic Sub-Detector Readout & Control n o r t c n o e l E s ic m m o C Ken Wyllie, CERN 10 Architecture Review, 5 th Dec 2012

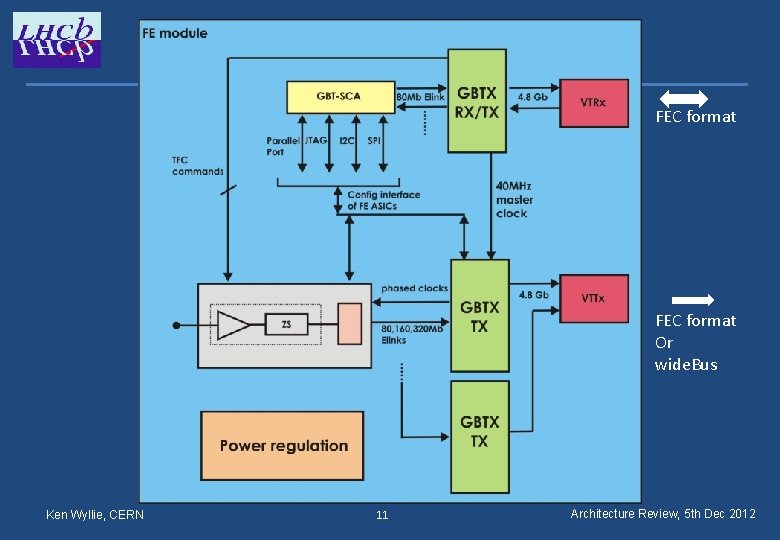

FEC format Or wide. Bus Ken Wyllie, CERN 11 Architecture Review, 5 th Dec 2012

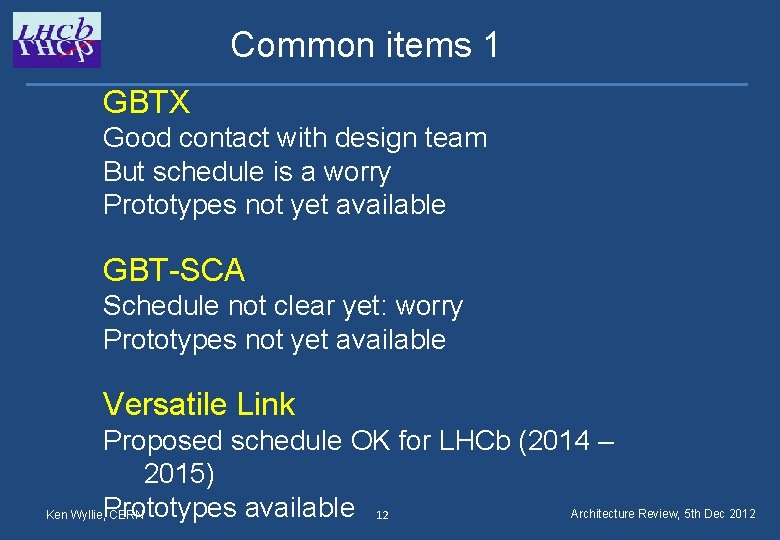

Common items 1 GBTX Good contact with design team But schedule is a worry Prototypes not yet available GBT-SCA Schedule not clear yet: worry Prototypes not yet available Versatile Link Proposed schedule OK for LHCb (2014 – 2015) available 12 Architecture Review, 5 th Dec 2012 Ken Wyllie, Prototypes CERN

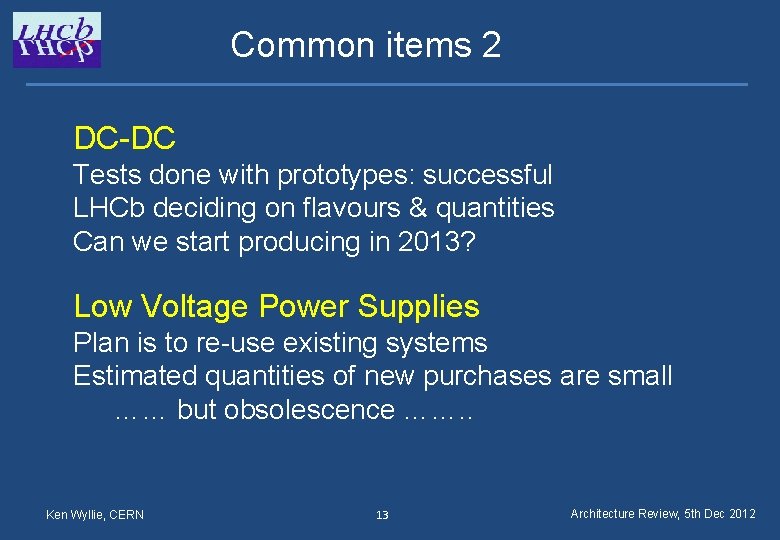

Common items 2 DC-DC Tests done with prototypes: successful LHCb deciding on flavours & quantities Can we start producing in 2013? Low Voltage Power Supplies Plan is to re-use existing systems Estimated quantities of new purchases are small …… but obsolescence ……. . Ken Wyllie, CERN 13 Architecture Review, 5 th Dec 2012

Spare slides Sub-detector details Ken Wyllie, CERN 14 Architecture Review, 5 th Dec 2012

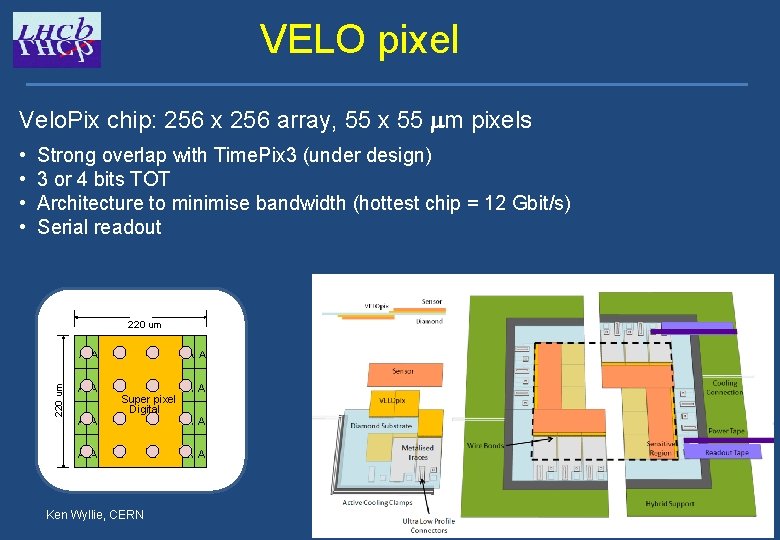

VELO pixel Velo. Pix chip: 256 x 256 array, 55 x 55 mm pixels Strong overlap with Time. Pix 3 (under design) 3 or 4 bits TOT Architecture to minimise bandwidth (hottest chip = 12 Gbit/s) Serial readout 220 um A A 220 um • • A A A Super pixel Digital A A Ken Wyllie, CERN A A A 15 Architecture Review, 5 th Dec 2012

VELO strips & Silicon Tracker SALT ASIC under design 128 -channels, each with 6 -bit ADC On-chip data compression planned (pedestal subtraction, common-mode correction) Ken Wyllie, CERN 16 Architecture Review, 5 th Dec 2012

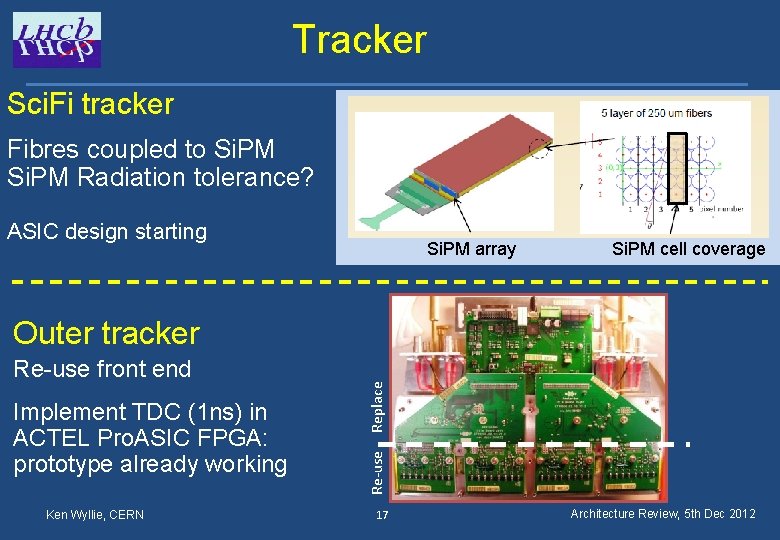

Tracker Sci. Fi tracker Fibres coupled to Si. PM Radiation tolerance? ASIC design starting Si. PM array Si. PM cell coverage Implement TDC (1 ns) in ACTEL Pro. ASIC FPGA: prototype already working Ken Wyllie, CERN Re-use front end Replace Outer tracker 17 LHCC upgrade session, 16 th February 2010 Architecture Review, 5 th Dec 2012

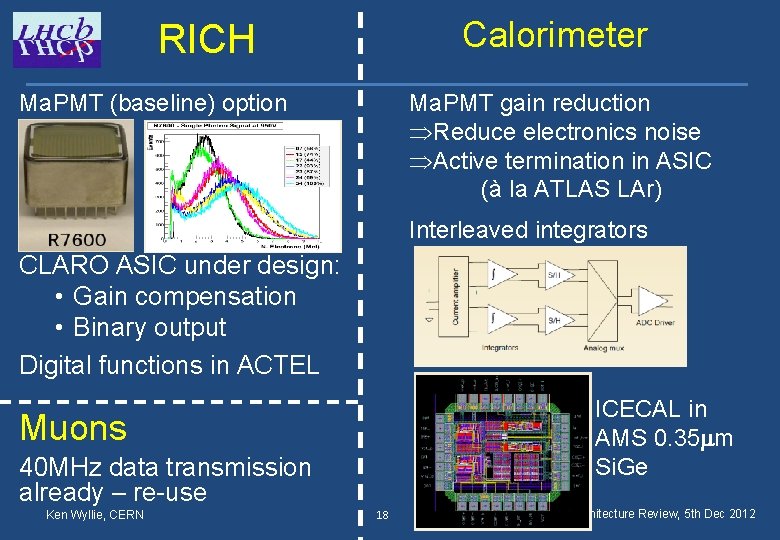

Calorimeter RICH Ma. PMT gain reduction ÞReduce electronics noise ÞActive termination in ASIC (à la ATLAS LAr) Ma. PMT (baseline) option Interleaved integrators CLARO ASIC under design: • Gain compensation • Binary output Digital functions in ACTEL ICECAL in AMS 0. 35 mm Si. Ge Muons 40 MHz data transmission already – re-use Ken Wyllie, CERN 18 Architecture Review, 5 th Dec 2012

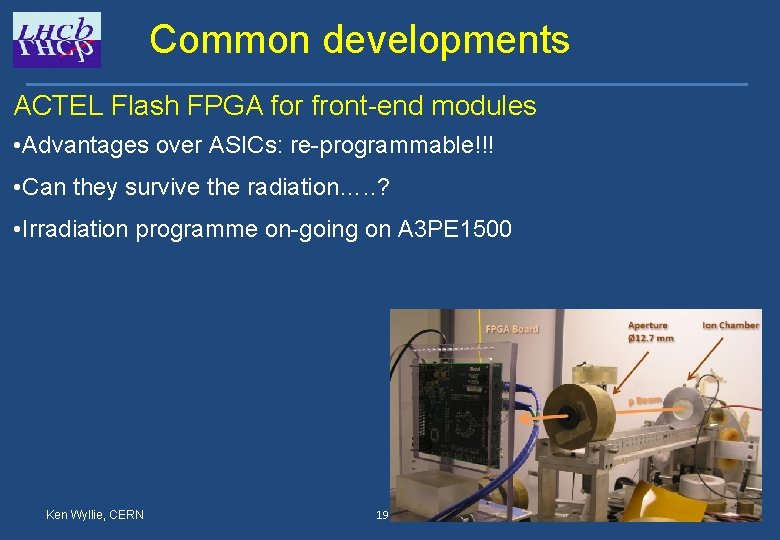

Common developments ACTEL Flash FPGA for front-end modules • Advantages over ASICs: re-programmable!!! • Can they survive the radiation…. . ? • Irradiation programme on-going on A 3 PE 1500 Ken Wyllie, CERN 19 Architecture Review, 5 th Dec 2012

TFC command Delay line = 24 x 16 x 3 bits delay 2 delay 16 24 Raw data Synchronise r BXID reset Constant latency logic Link BCnt Preset Ken Wyllie, CERN TFC filter Non. Constant latency logic ECS 20 Architecture Review, 5 th Dec 2012

- Slides: 20