Lgica Programvel e VHDL Prof Marcio Cunha Aula

- Slides: 27

Lógica Programável e VHDL Prof. Marcio Cunha Aula 05 – Projeto RTL

Agenda �Planejamento �Introdução �Projeto Lógico Combinacional �Projeto Lógico Sequencial �Projeto RTL

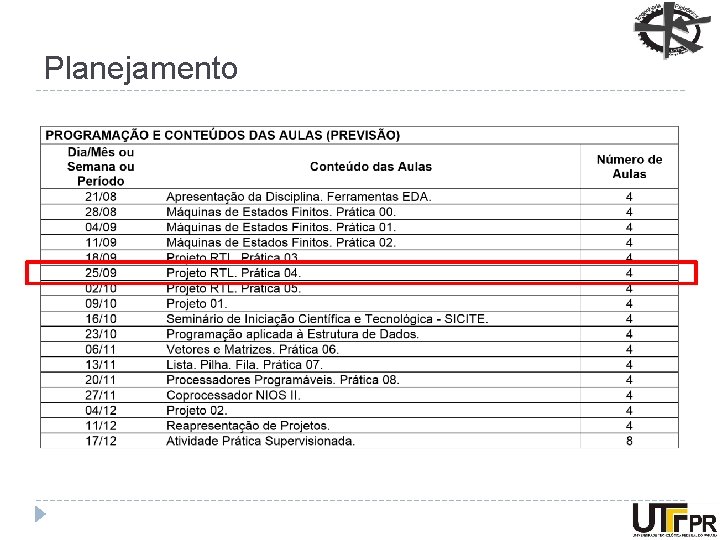

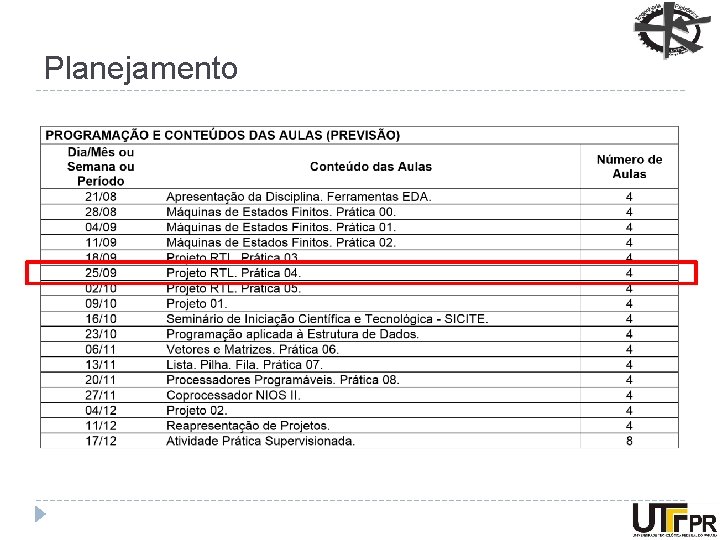

Planejamento

Agenda �Planejamento �Introdução �Projeto Lógico Combinacional �Projeto Lógico Sequencial �Projeto RTL

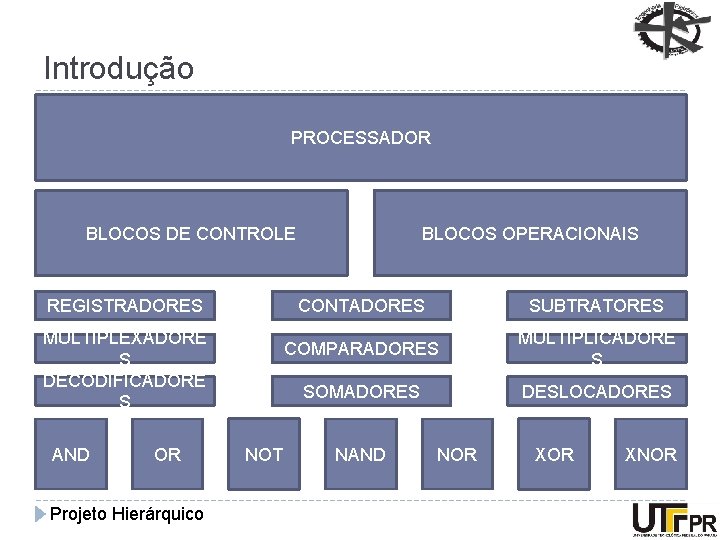

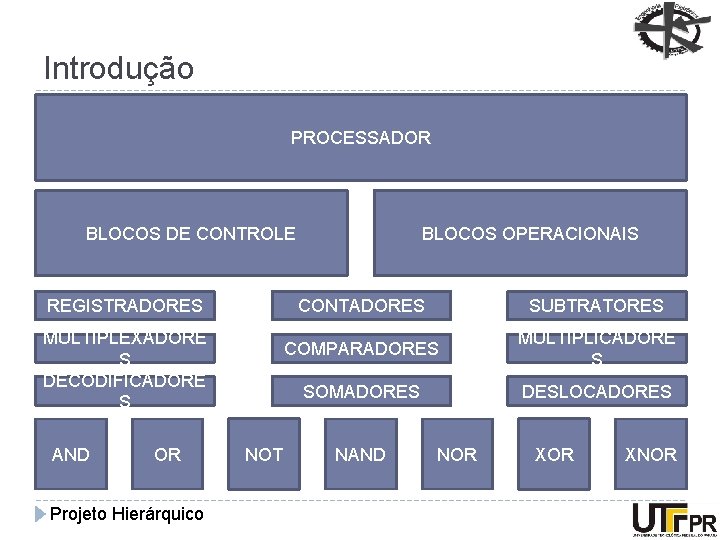

Introdução PROCESSADOR BLOCOS DE CONTROLE REGISTRADORES MULTIPLEXADORE S DECODIFICADORE S AND OR Projeto Hierárquico NOT BLOCOS OPERACIONAIS CONTADORES SUBTRATORES COMPARADORES MULTIPLICADORE S SOMADORES DESLOCADORES NAND NOR XNOR

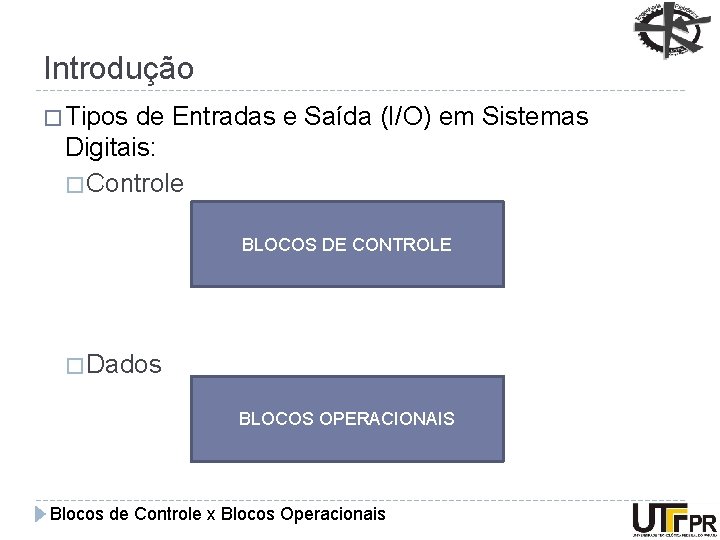

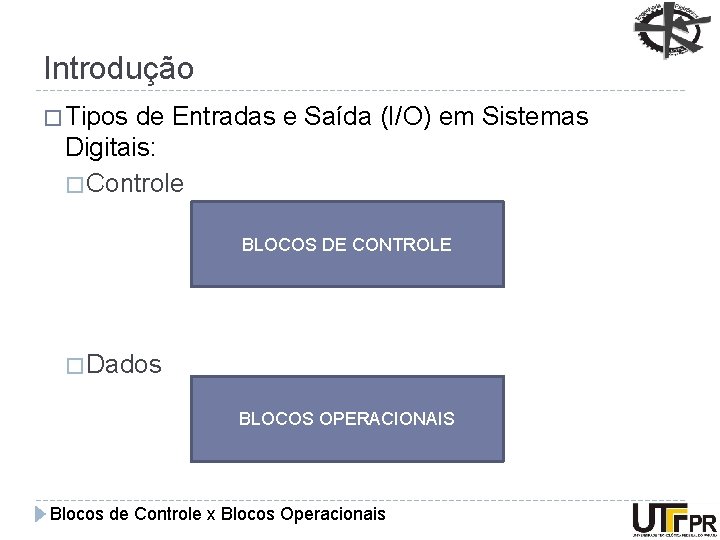

Introdução � Tipos de Entradas e Saída (I/O) em Sistemas Digitais: � Controle BLOCOS DE CONTROLE � Dados BLOCOS OPERACIONAIS Blocos de Controle x Blocos Operacionais

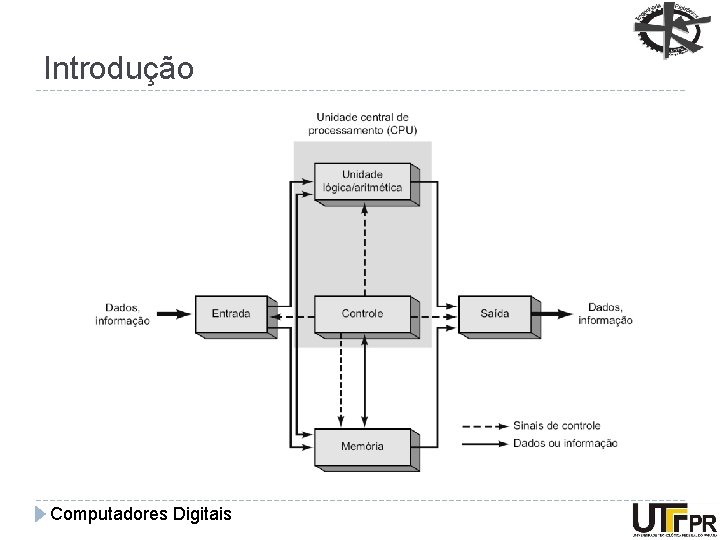

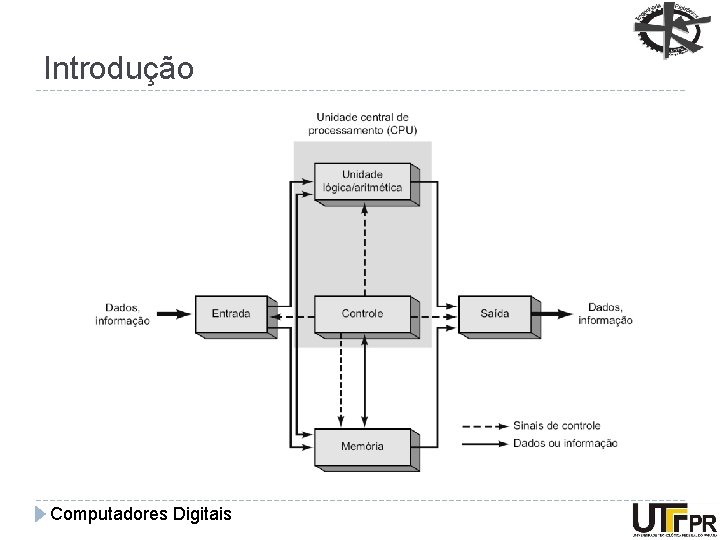

Introdução Computadores Digitais

Introdução PROJETO RTL PROJETO LÓGICO COMBINACIONAL Metodologias de Projeto PROJETO LÓGICO SEQUENCIAL

Agenda �Planejamento �Introdução �Projeto Lógico Combinacional �Projeto Lógico Sequencial �Projeto RTL

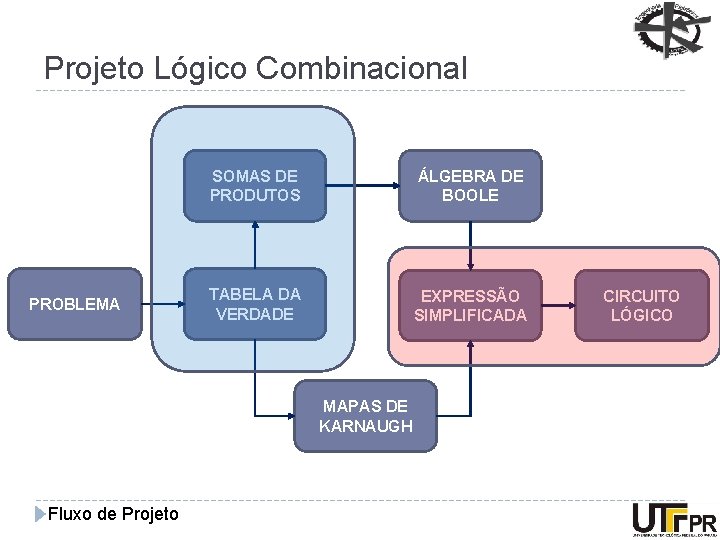

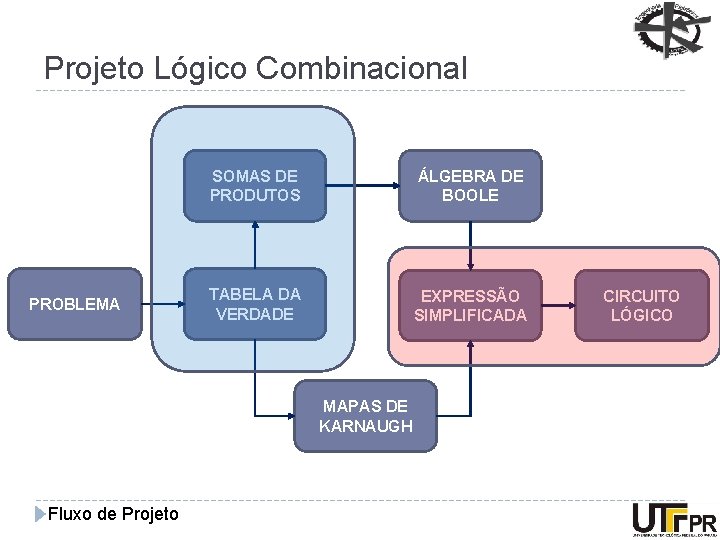

Projeto Lógico Combinacional PROBLEMA SOMAS DE PRODUTOS ÁLGEBRA DE BOOLE TABELA DA VERDADE EXPRESSÃO SIMPLIFICADA MAPAS DE KARNAUGH Fluxo de Projeto CIRCUITO LÓGICO

Agenda �Planejamento �Introdução �Projeto Lógico Combinacional �Projeto Lógico Sequencial �Projeto RTL

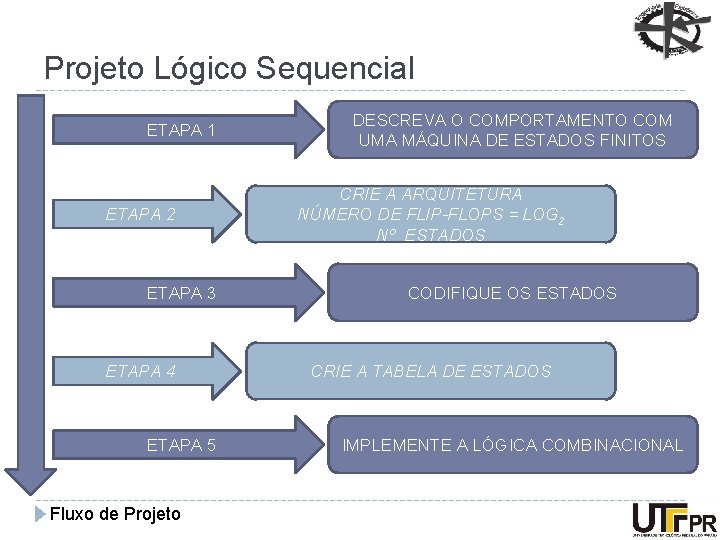

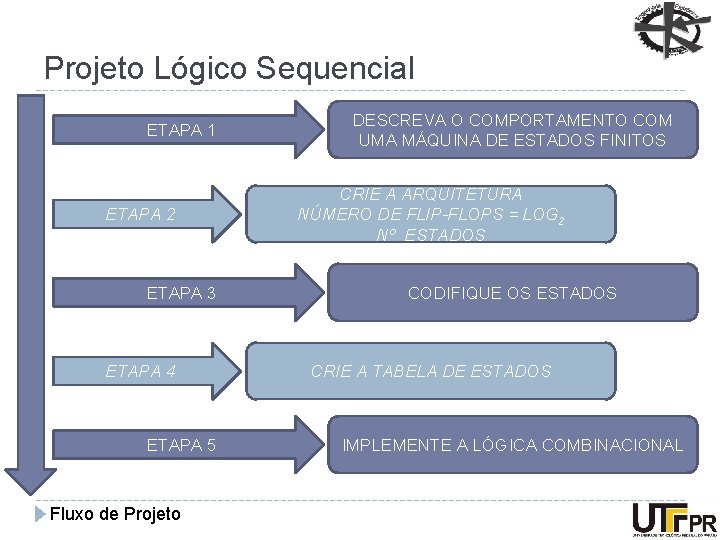

Projeto Lógico Sequencial ETAPA 1 ETAPA 2 ETAPA 3 ETAPA 4 ETAPA 5 Fluxo de Projeto DESCREVA O COMPORTAMENTO COM UMA MÁQUINA DE ESTADOS FINITOS CRIE A ARQUITETURA NÚMERO DE FLIP-FLOPS = LOG 2 Nº_ESTADOS CODIFIQUE OS ESTADOS CRIE A TABELA DE ESTADOS IMPLEMENTE A LÓGICA COMBINACIONAL

Agenda �Planejamento �Introdução �Projeto Lógico Combinacional �Projeto Lógico Sequencial �Projeto RTL

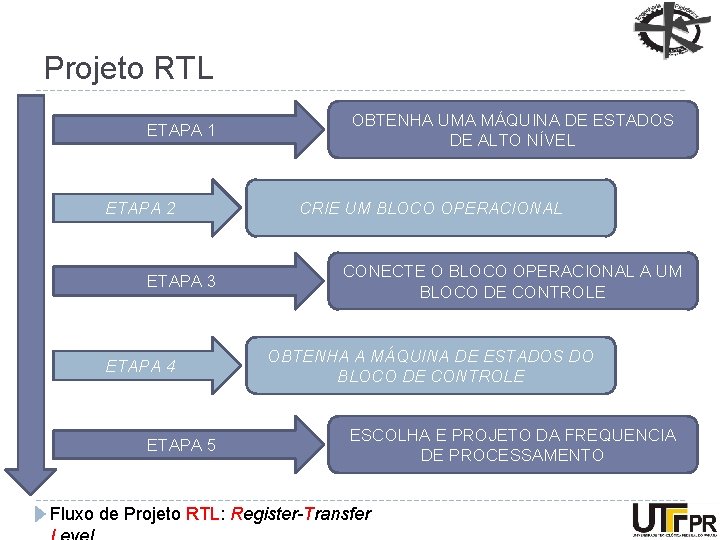

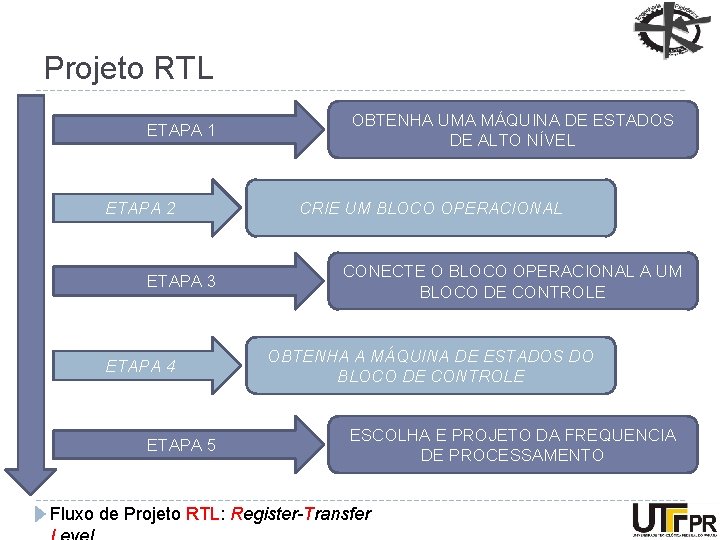

Projeto RTL ETAPA 1 ETAPA 2 ETAPA 3 ETAPA 4 ETAPA 5 OBTENHA UMA MÁQUINA DE ESTADOS DE ALTO NÍVEL CRIE UM BLOCO OPERACIONAL CONECTE O BLOCO OPERACIONAL A UM BLOCO DE CONTROLE OBTENHA A MÁQUINA DE ESTADOS DO BLOCO DE CONTROLE ESCOLHA E PROJETO DA FREQUENCIA DE PROCESSAMENTO Fluxo de Projeto RTL: Register-Transfer

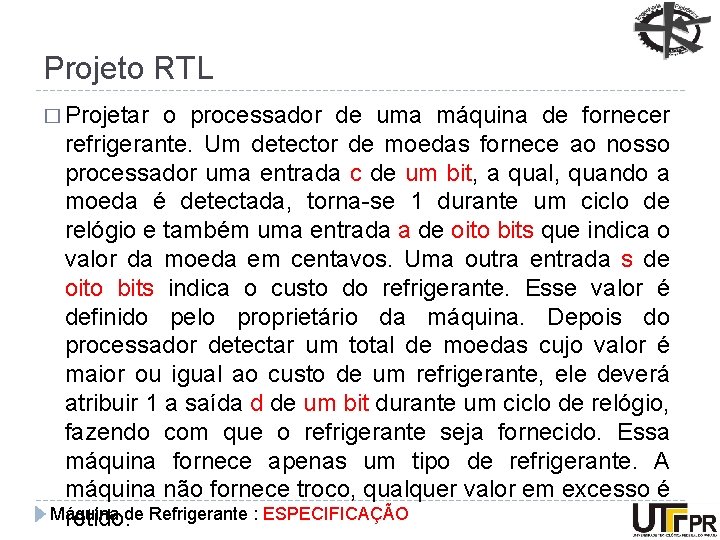

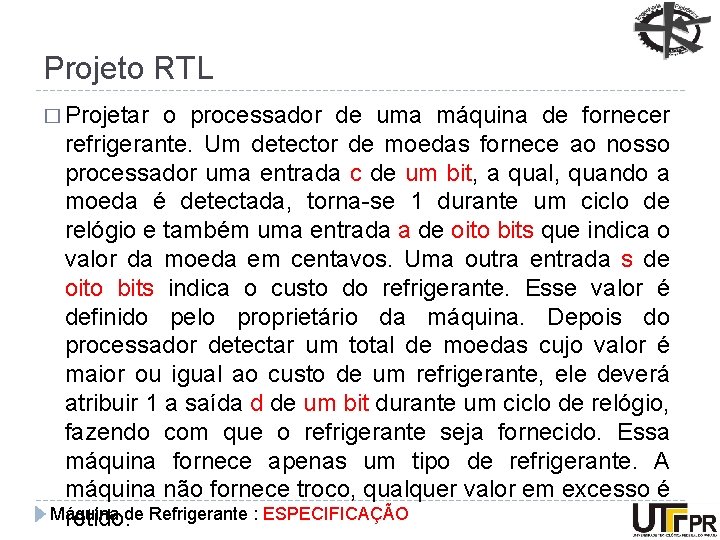

Projeto RTL � Projetar o processador de uma máquina de fornecer refrigerante. Um detector de moedas fornece ao nosso processador uma entrada c de um bit, a qual, quando a moeda é detectada, torna-se 1 durante um ciclo de relógio e também uma entrada a de oito bits que indica o valor da moeda em centavos. Uma outra entrada s de oito bits indica o custo do refrigerante. Esse valor é definido pelo proprietário da máquina. Depois do processador detectar um total de moedas cujo valor é maior ou igual ao custo de um refrigerante, ele deverá atribuir 1 a saída d de um bit durante um ciclo de relógio, fazendo com que o refrigerante seja fornecido. Essa máquina fornece apenas um tipo de refrigerante. A máquina não fornece troco, qualquer valor em excesso é Máquina retido. de Refrigerante : ESPECIFICAÇÃO

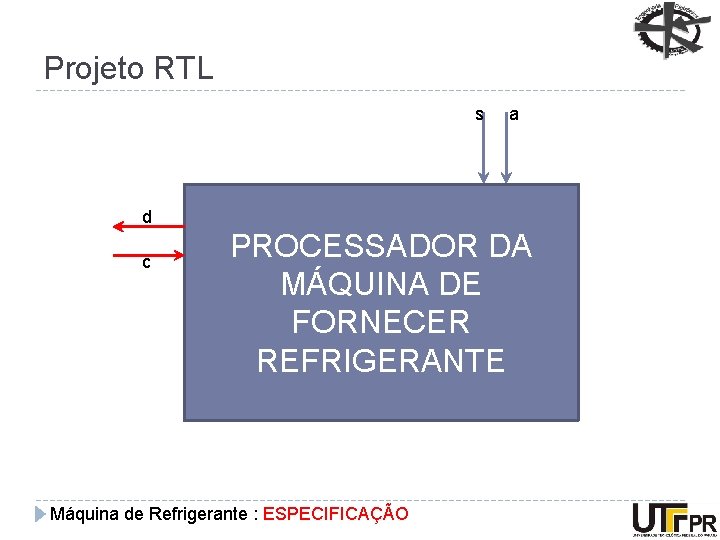

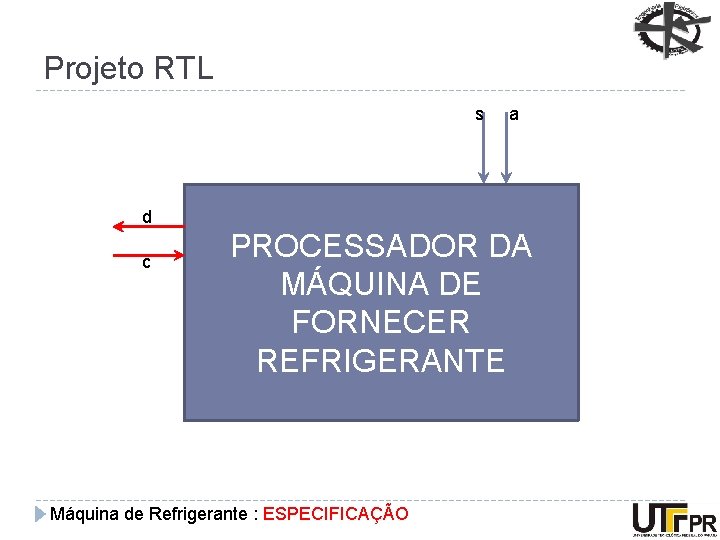

Projeto RTL s a d c PROCESSADOR DA MÁQUINA DE FORNECER REFRIGERANTE Máquina de Refrigerante : ESPECIFICAÇÃO

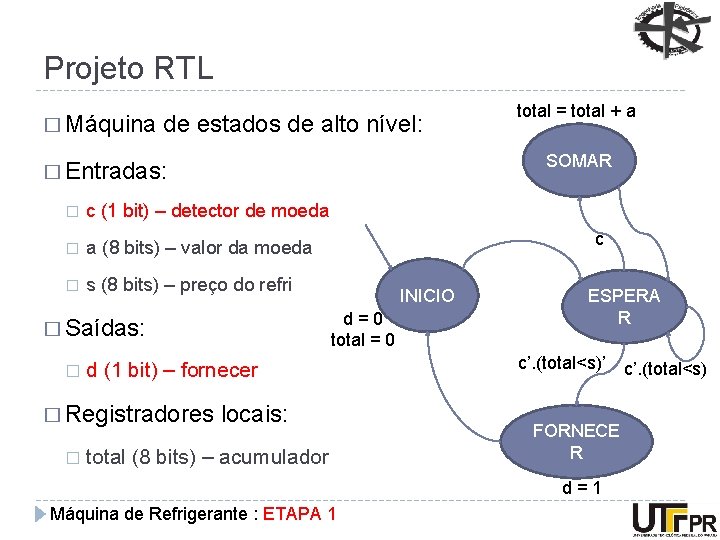

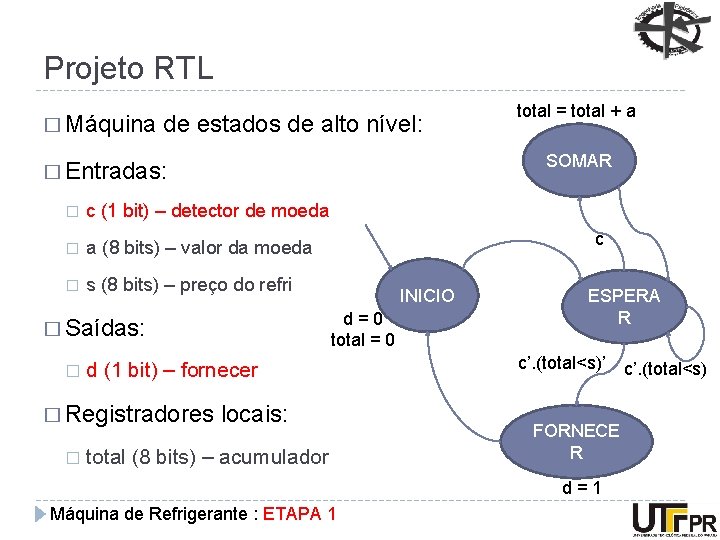

Projeto RTL � Máquina de estados de alto nível: SOMAR � Entradas: � c (1 bit) – detector de moeda � a (8 bits) – valor da moeda � s (8 bits) – preço do refri INICIO d (1 bit) – fornecer � Registradores � c d=0 total = 0 � Saídas: � total = total + a locais: total (8 bits) – acumulador ESPERA R c’. (total<s)’ c’. (total<s) FORNECE R d=1 Máquina de Refrigerante : ETAPA 1

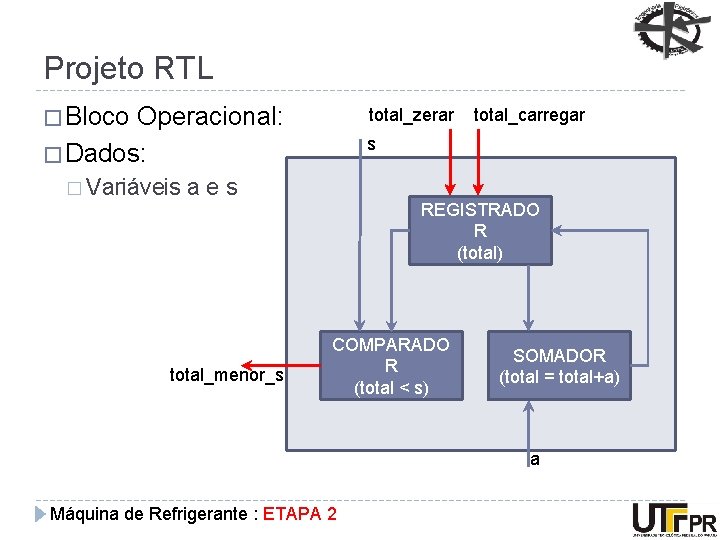

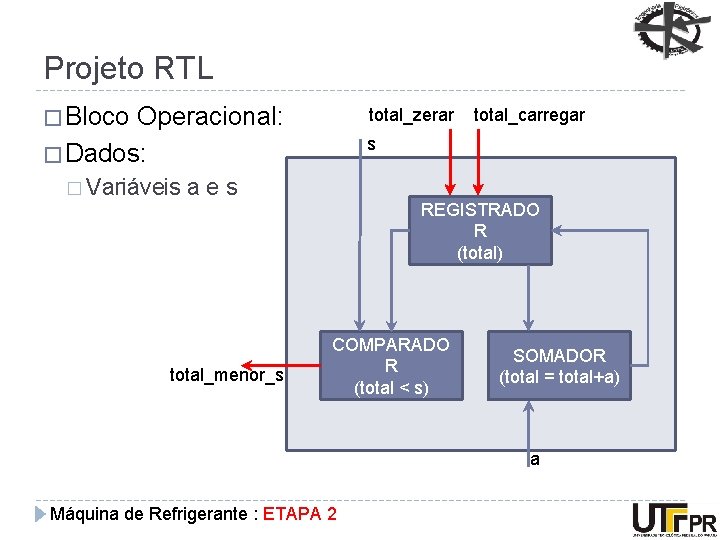

Projeto RTL � Bloco Operacional: � Dados: � Variáveis total_zerar s aes total_menor_s total_carregar REGISTRADO R (total) COMPARADO R (total < s) SOMADOR (total = total+a) a Máquina de Refrigerante : ETAPA 2

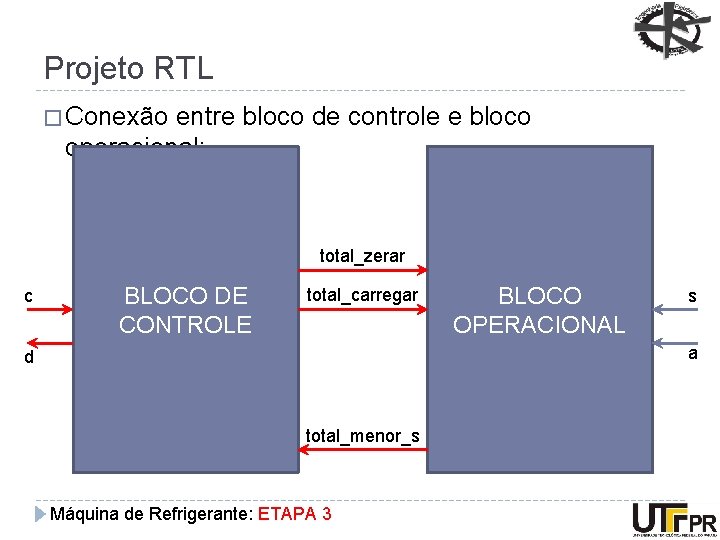

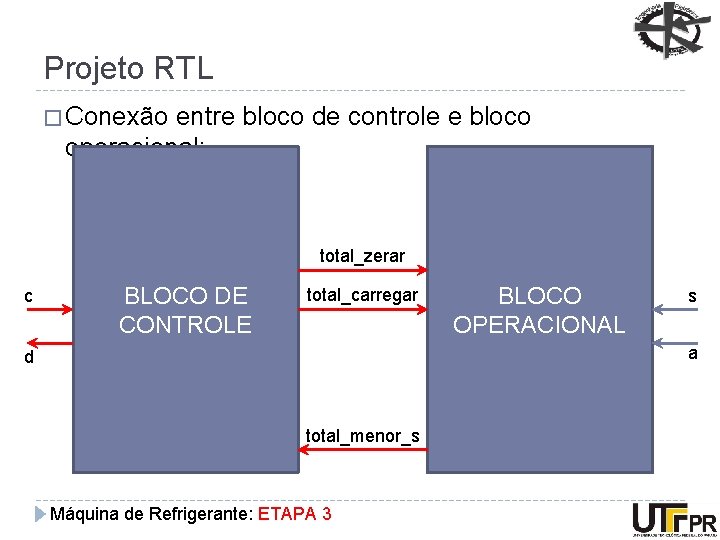

Projeto RTL � Conexão entre bloco de controle e bloco operacional: total_zerar c BLOCO DE CONTROLE total_carregar BLOCO OPERACIONAL s a d total_menor_s Máquina de Refrigerante: ETAPA 3

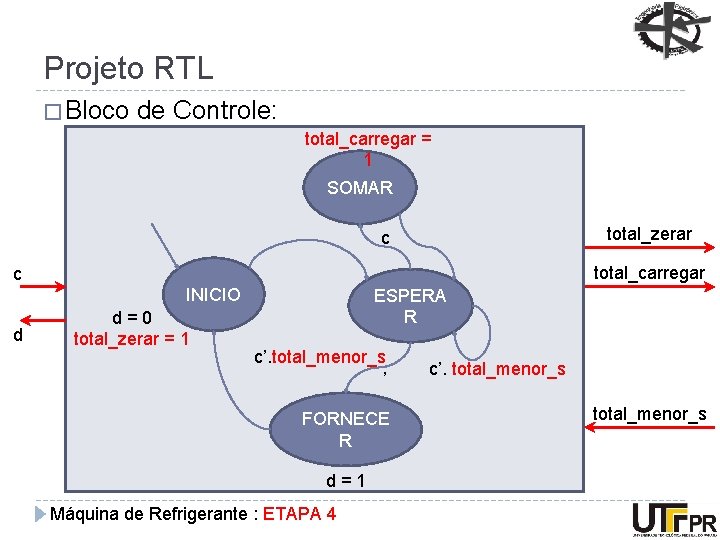

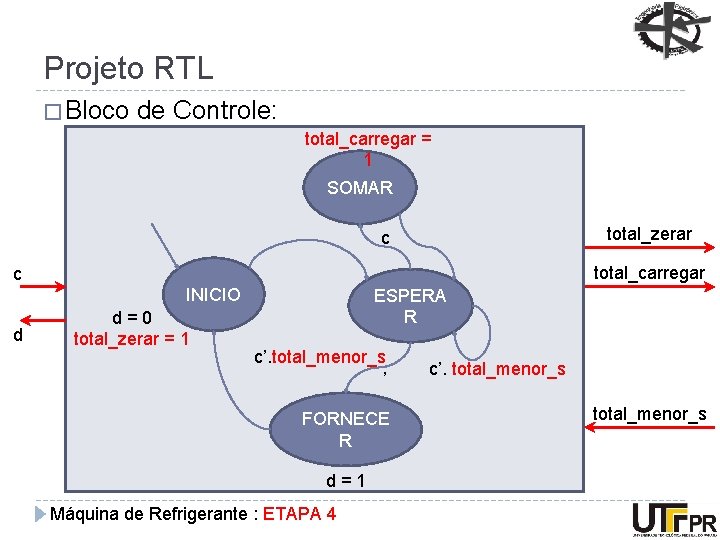

Projeto RTL � Bloco de Controle: total_carregar = 1 SOMAR total_zerar c total_carregar c INICIO d d=0 total_zerar = 1 ESPERA R c’. total_menor_s ’ FORNECE R d=1 Máquina de Refrigerante : ETAPA 4 c’. total_menor_s

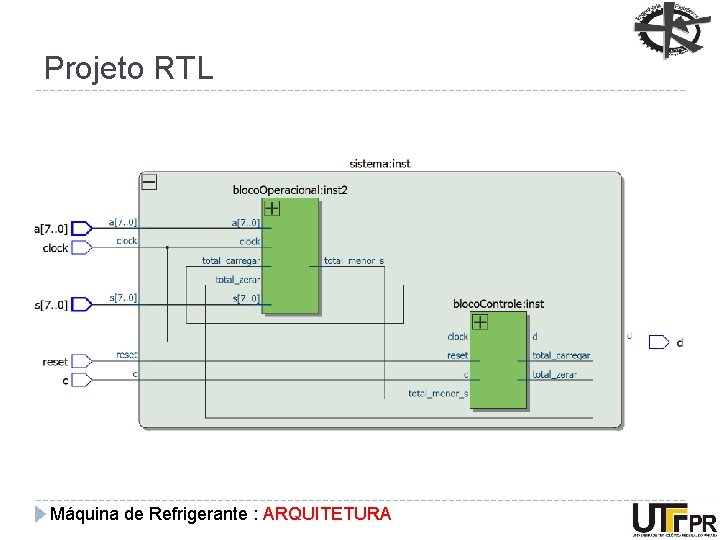

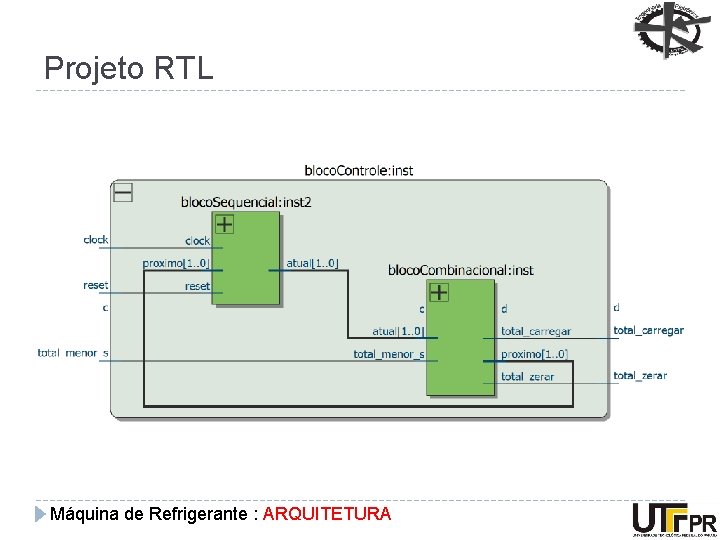

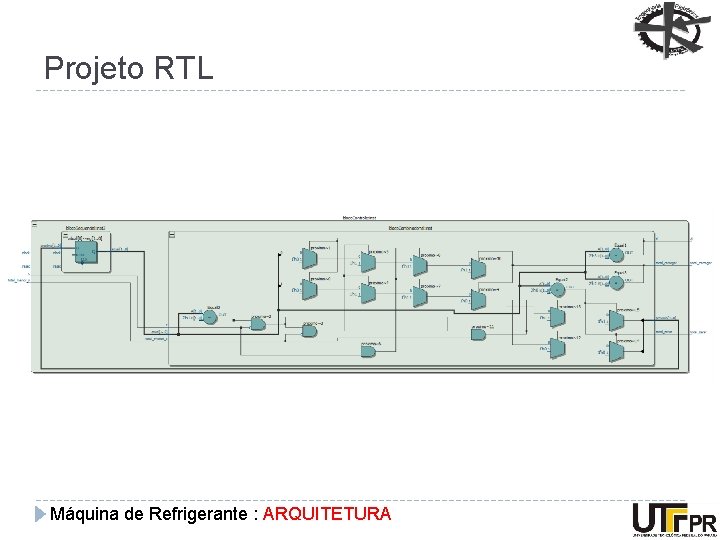

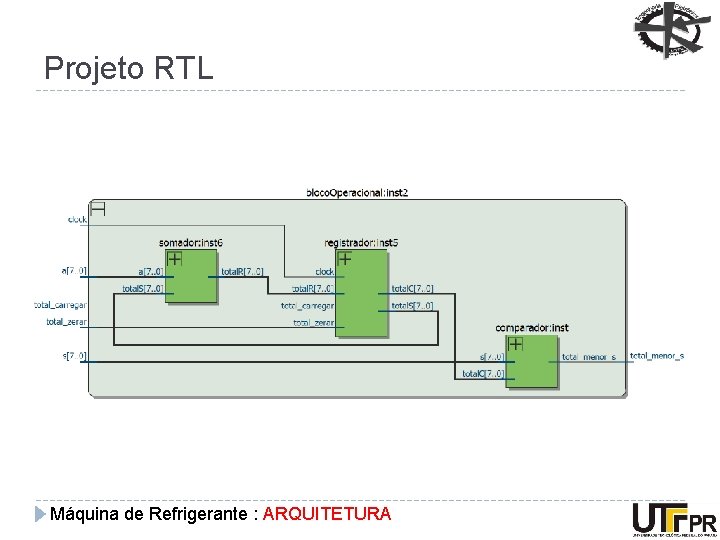

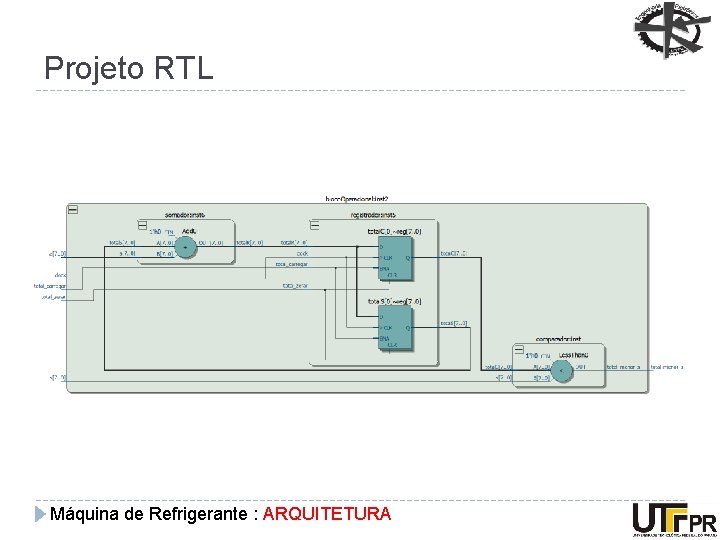

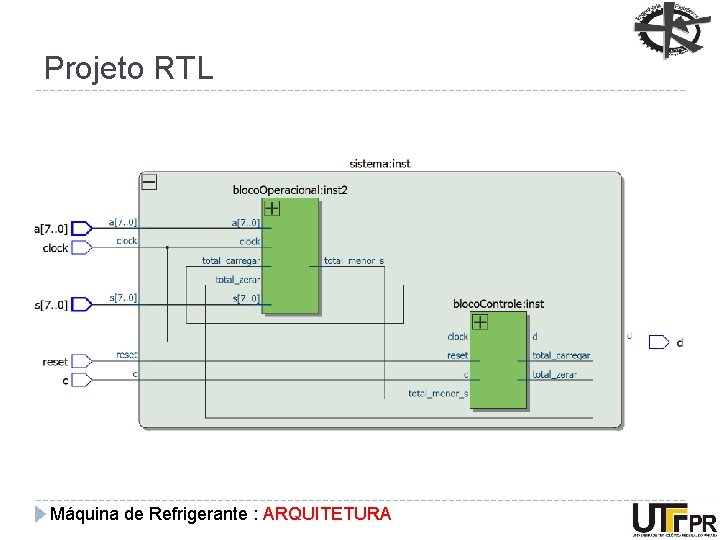

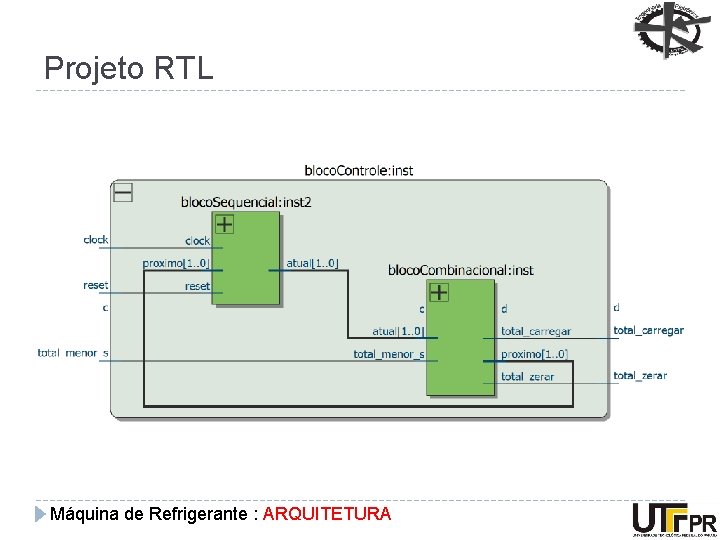

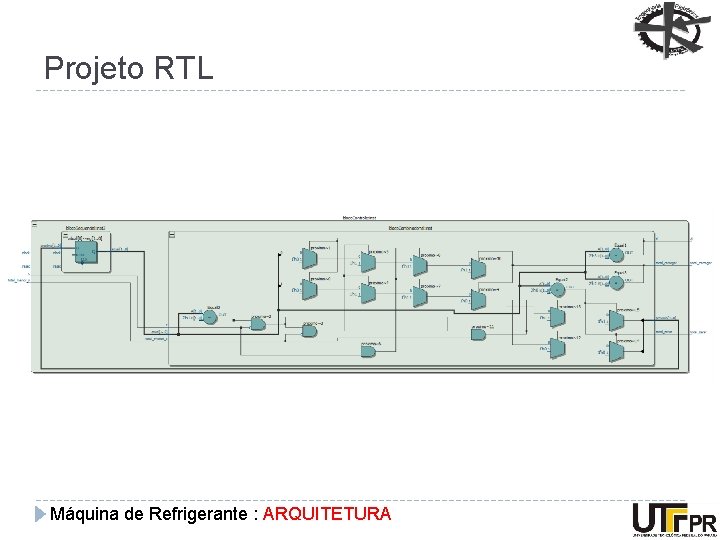

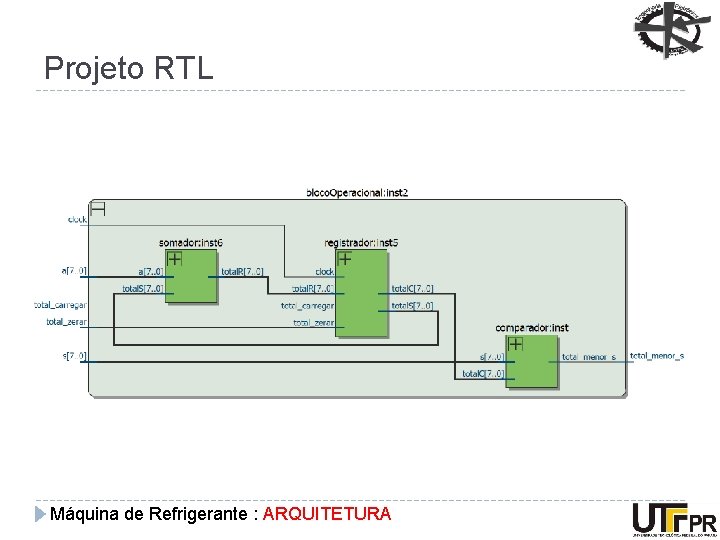

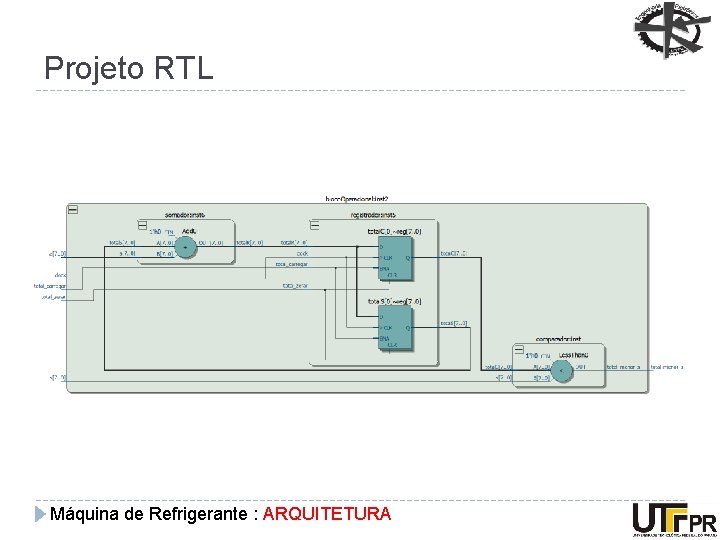

Projeto RTL Máquina de Refrigerante : ARQUITETURA

Projeto RTL Máquina de Refrigerante : ARQUITETURA

Projeto RTL Máquina de Refrigerante : ARQUITETURA

Projeto RTL Máquina de Refrigerante : ARQUITETURA

Projeto RTL Máquina de Refrigerante : ARQUITETURA

Projeto RTL � Exemplo extraído e adaptado: � VAHID, Frank. Sistemas digitais: projeto, otimização e HDLS. Porto Alegre: Artmed, 2008. 560 p. ISBN-13: 9788577801909. Máquina de Refrigerante : REFERENCIA

Lógica Programável e VHDL Prof. Marcio Cunha Aula 05 – Projeto RTL