Les oprateurs combinatoires Des circuits lmentaires L additionneur

Les opérateurs combinatoires Des circuits élémentaires L ’additionneur 1 bit L ’additionneur 4 bits Calculs des temps de propagation

Objectifs Nous verrons comment réaliser la synthèse d ’une fonction logique à partir de circuits élémentaires. Nous étudierons différentes réalisations de l ’additionneur et discuterons du temps de calcul.

Exemple de synthèse f = ab/+ac/ +a/bc On veut réaliser un circuit logique réalisant la fonction précédente.

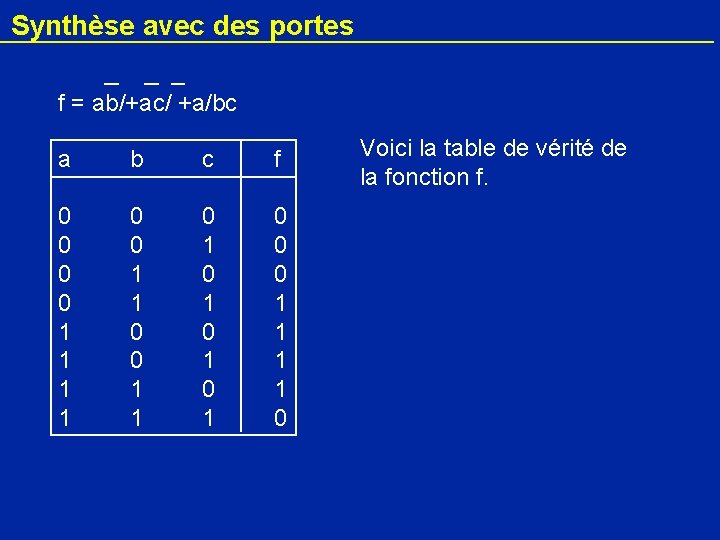

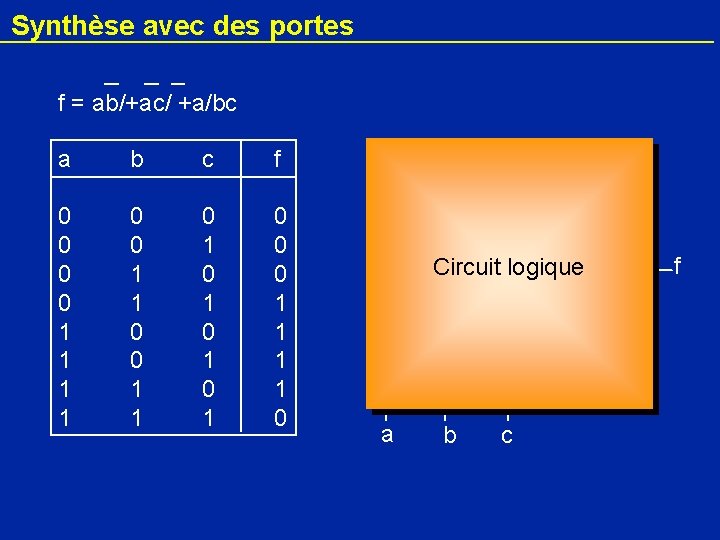

Synthèse avec des portes f = ab/+ac/ +a/bc a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 Voici la table de vérité de la fonction f.

Synthèse avec des portes f = ab/+ac/ +a/bc a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 Circuit logique a b c f

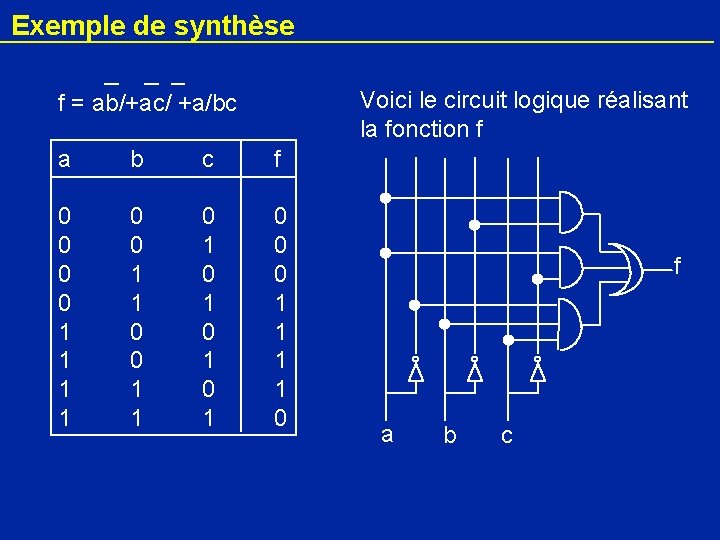

Exemple de synthèse f = ab/+ac/ +a/bc Voici le circuit logique réalisant la fonction f a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 f a b c

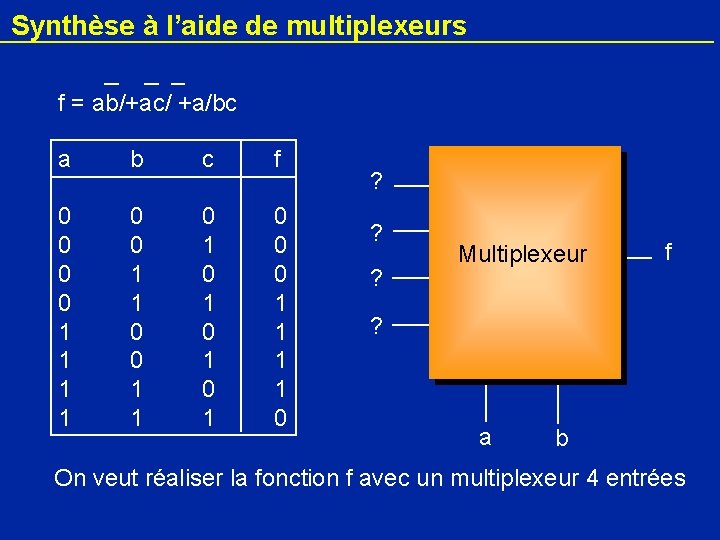

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 ? ? ? Multiplexeur f ? a b On veut réaliser la fonction f avec un multiplexeur 4 entrées

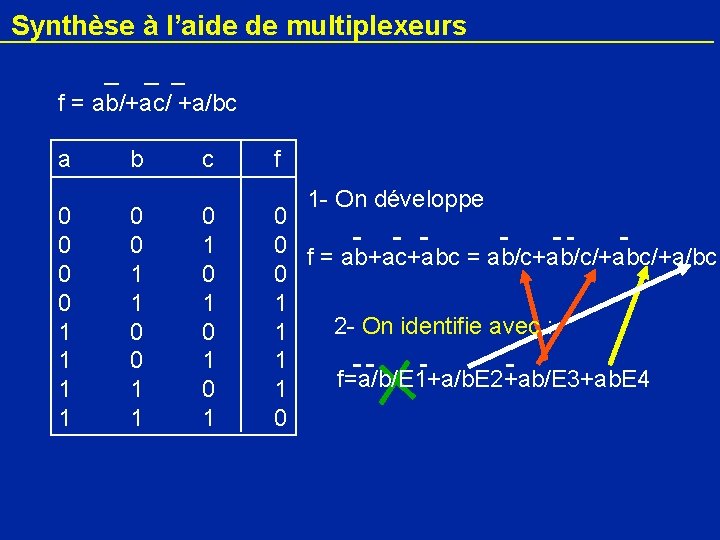

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc Première méthode a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 ? ? ? Multiplexeur f ? a b D ’après l ’équation de la sortie : f=a/b/E 1+a/b. E 2+ab/E 3+ab. E 4

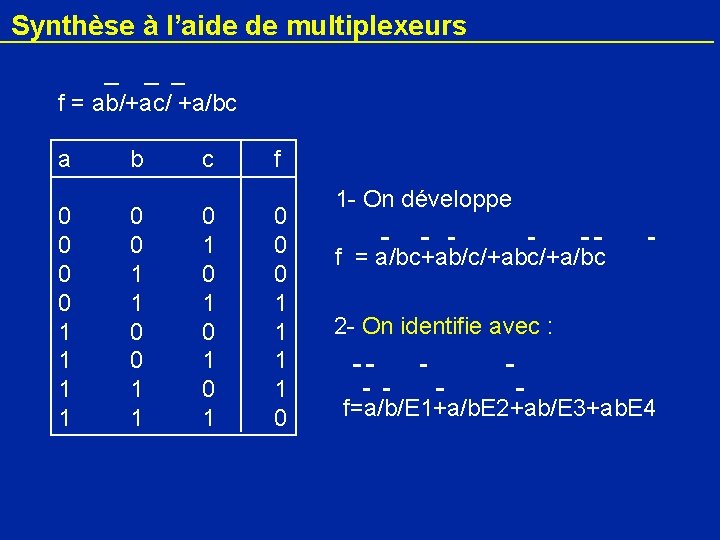

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a 0 0 1 1 b 0 0 1 1 c 0 1 0 1 f 0 0 0 1 1 0 1 - On développe f = a/bc+ab/c/+abc/+a/bc 2 - On identifie avec : f=a/b/E 1+a/b. E 2+ab/E 3+ab. E 4

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a 0 0 1 1 b 0 0 1 1 c f 0 1 0 1 1 - On développe 0 0 f = ab+ac+abc = ab/c+ab/c/+abc/+a/bc 0 1 2 - On identifie avec : 1 f=a/b/E 1+a/b. E 2+ab/E 3+ab. E 4 1 0

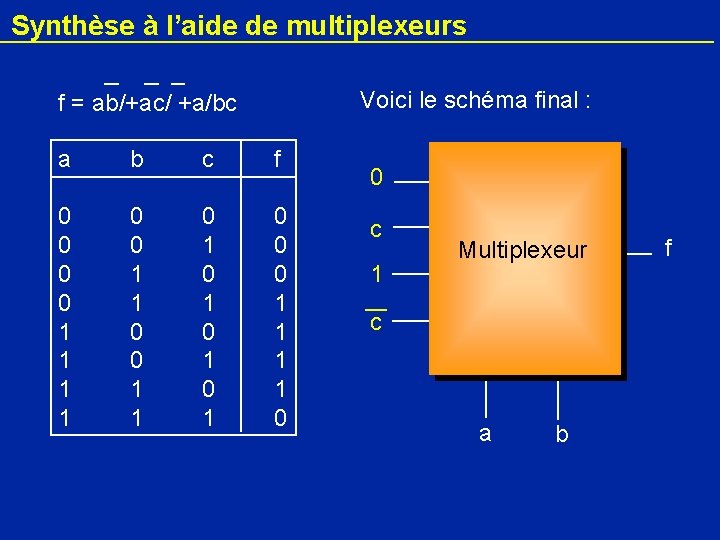

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc Voici le schéma final : a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 0 c 1 Multiplexeur c a b f

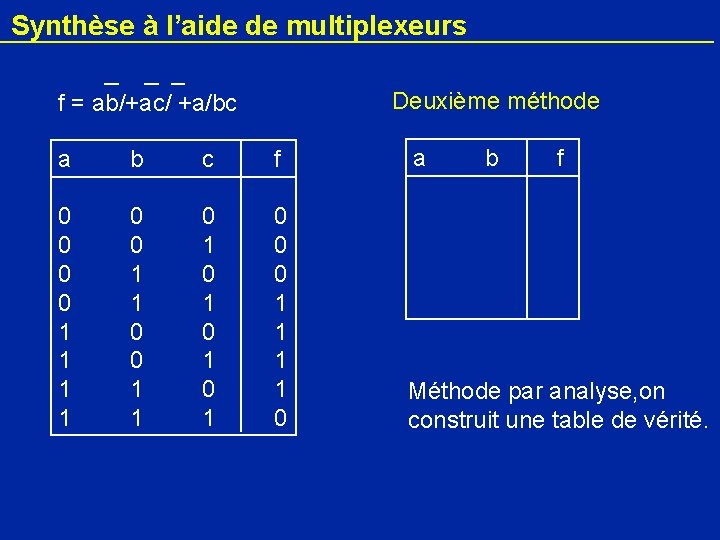

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 Il existe une autre méthode, la méthode par analyse.

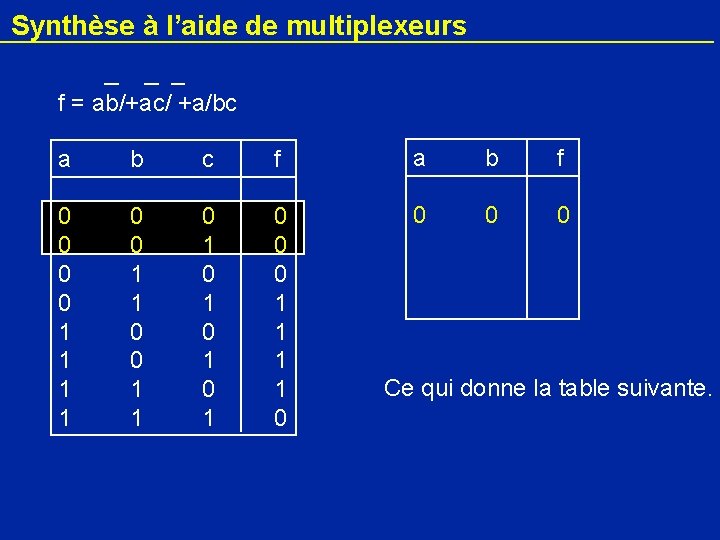

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc Deuxième méthode a b c f a b f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 Méthode par analyse, on construit une table de vérité.

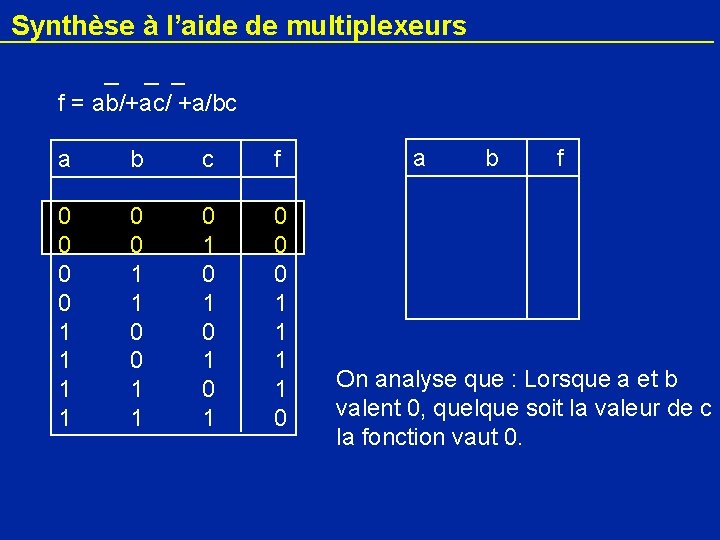

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 a b f On analyse que : Lorsque a et b valent 0, quelque soit la valeur de c la fonction vaut 0.

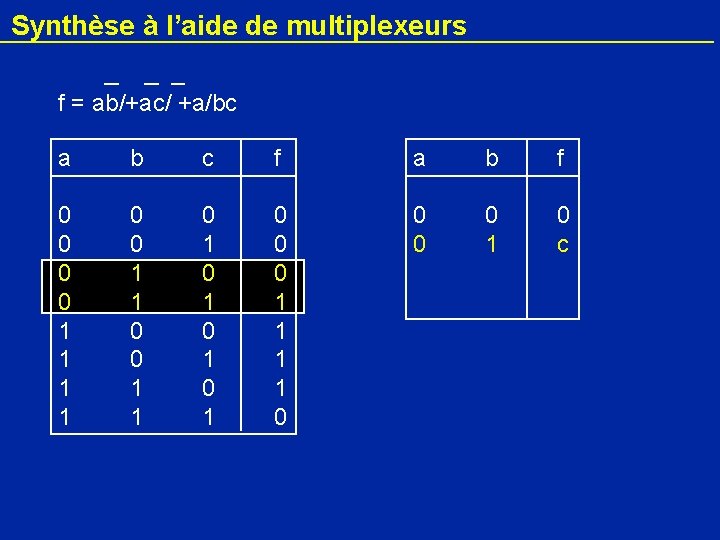

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f a b f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 0 Ce qui donne la table suivante.

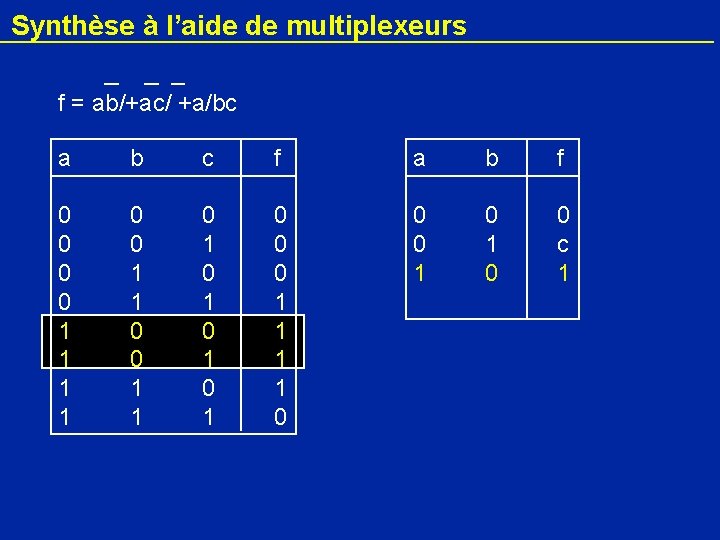

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f a b f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 0 1 0 c

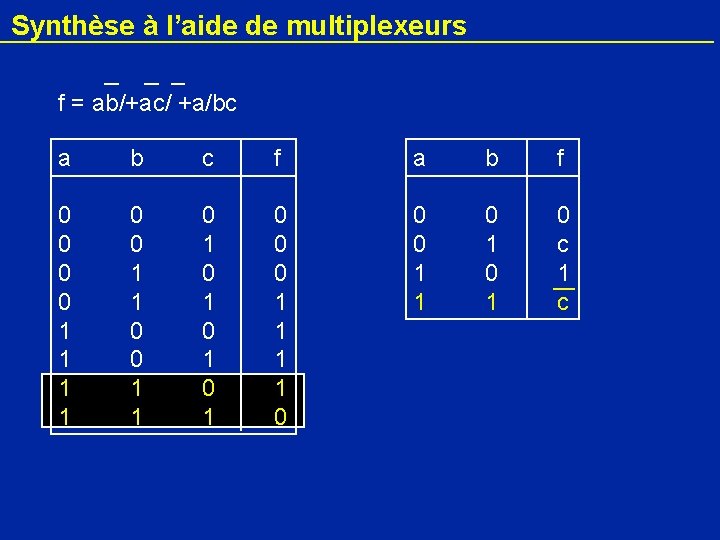

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f a b f 0 0 1 1 0 1 0 1 0 0 0 1 0 0 c 1

Synthèse à l’aide de multiplexeurs f = ab/+ac/ +a/bc a b c f a b f 0 0 1 1 0 1 0 1 0 0 0 1 1 0 1 0 c 1 c

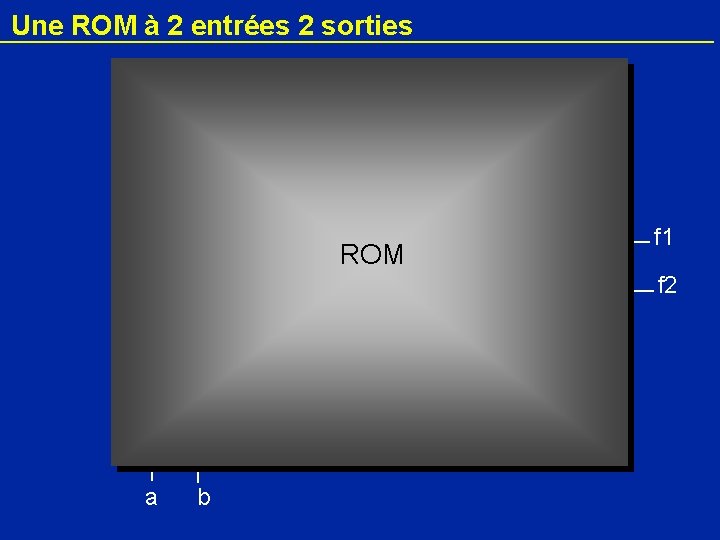

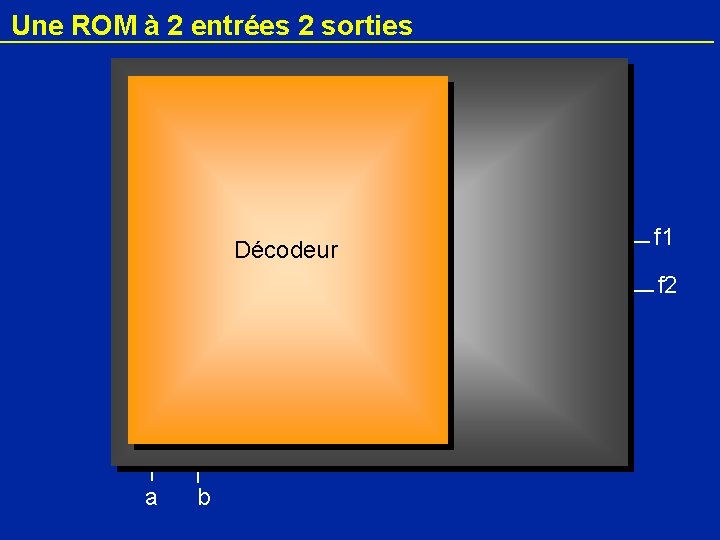

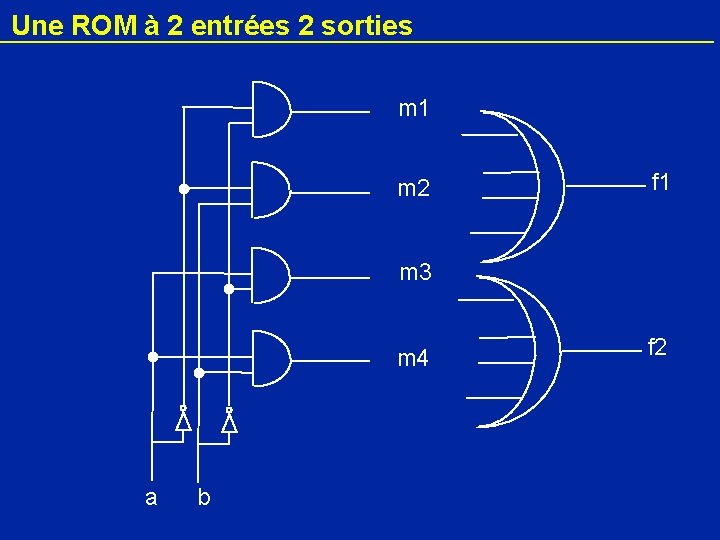

La structure ROM Une ROM (Mémoire à lecture seulement) est un opérateur combinatoire. Le nombre de bits en sortie correspond au nombre de fonctions logiques différentes implantées. Le nombre de bits d’adresse correspond au nombre de variables des fonctions logiques. La structure de la ROM est composée de deux parties : - un décodeur (générateur complet de mintermes), - un OU+ logique des mintermes pour lesquels la fonction prend la valeur 1.

Une ROM à 2 entrées 2 sorties ROM f 1 f 2 a b

Une ROM à 2 entrées 2 sorties Décodeur f 1 f 2 a b

Une ROM à 2 entrées 2 sorties m 1 m 2 Décodeur m 3 m 4 a b OU f 1 f 2

Une ROM à 2 entrées 2 sorties m 1 m 2 f 1 m 3 m 4 a b f 2

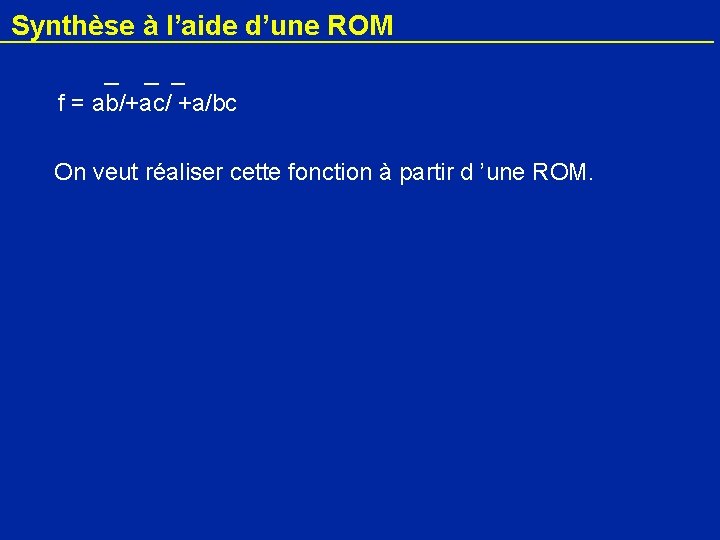

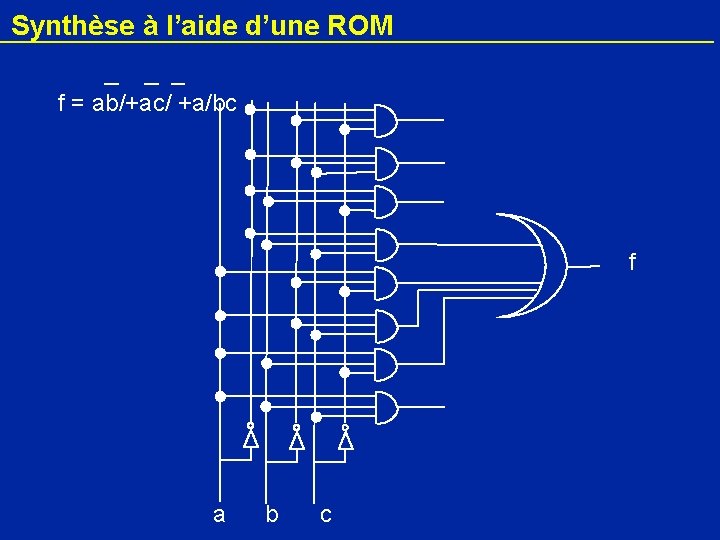

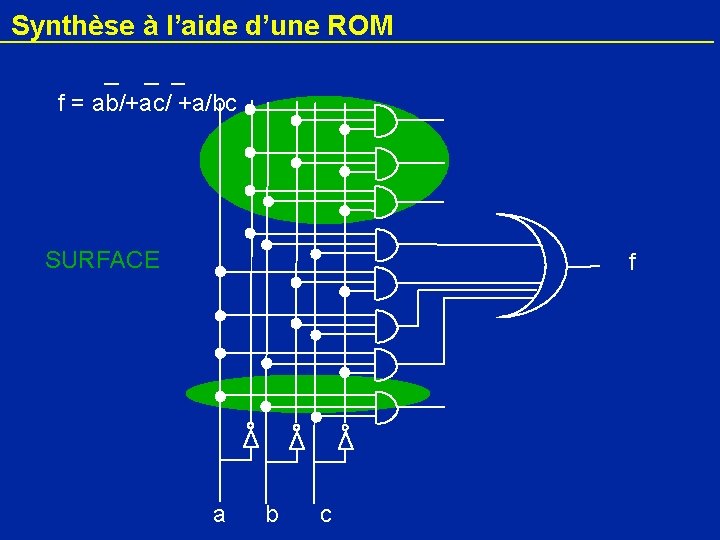

Synthèse à l’aide d’une ROM f = ab/+ac/ +a/bc On veut réaliser cette fonction à partir d ’une ROM.

Synthèse à l’aide d’une ROM f = ab/+ac/ +a/bc f a b c

Synthèse à l’aide d’une ROM f = ab/+ac/ +a/bc SURFACE f a b c

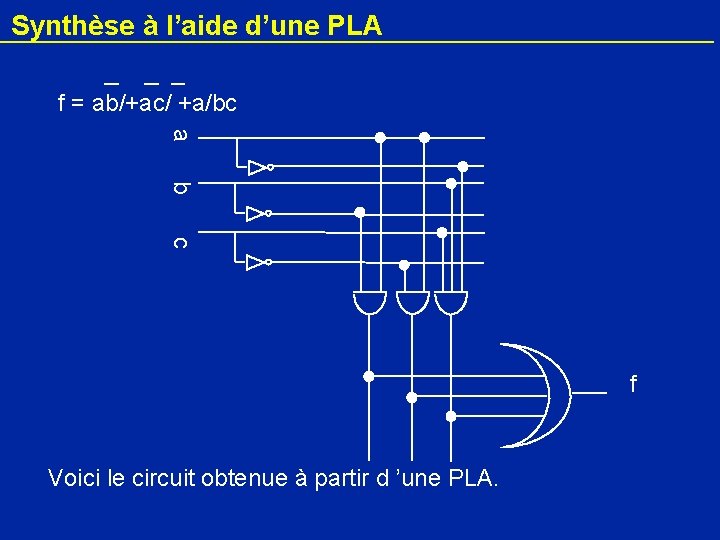

La structure PLA Une PLA est un opérateur combinatoire. Le nombre de bits en sortie correspond au nombre de fonctions logiques différentes implantées. Le nombre de bits d’adresse correspond au nombre de variables des fonctions logiques. La structure d’une PLA est composée de deux parties : - Le demi-PLA ET : générateur partiel de mintermes - Le demi-PLA OU : réalise le OU logique des mintermes pour lesquels la fonction a pour valeur 1.

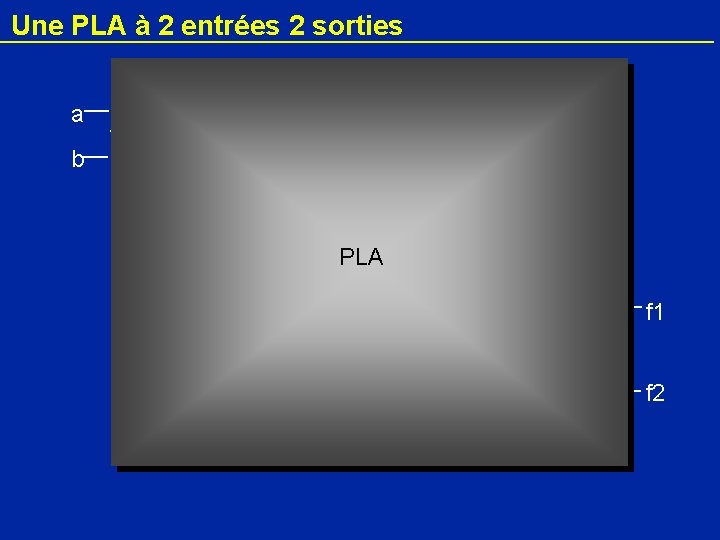

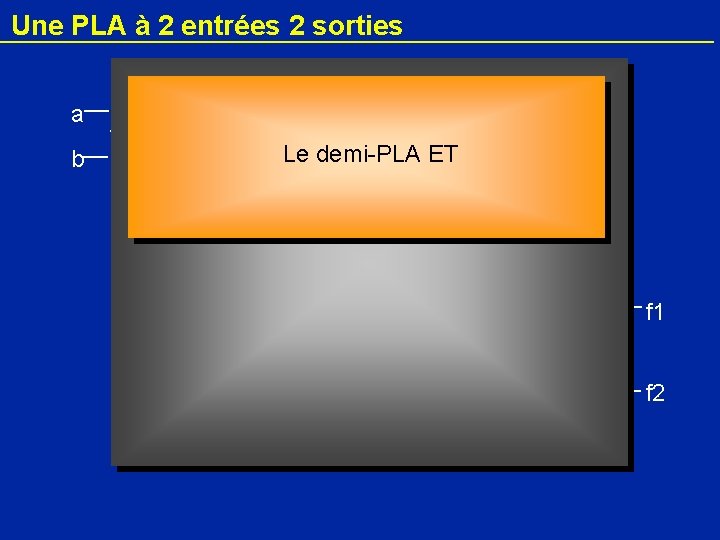

Une PLA à 2 entrées 2 sorties a b m 1 m 2 m 3 m 4 PLA f 1 f 2

Une PLA à 2 entrées 2 sorties a b Le demi-PLA ET f 1 f 2

Une PLA à 2 entrées 2 sorties a b Le demi-PLA ET f 1 Le demi-PLA OU f 2

Synthèse à l’aide d’une PLA f = ab/+ac/ +a/bc a b c f Voici le circuit obtenue à partir d ’une PLA.

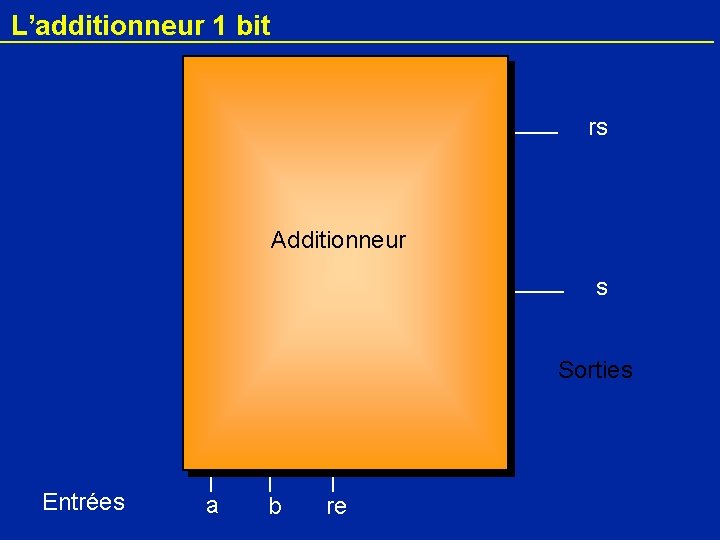

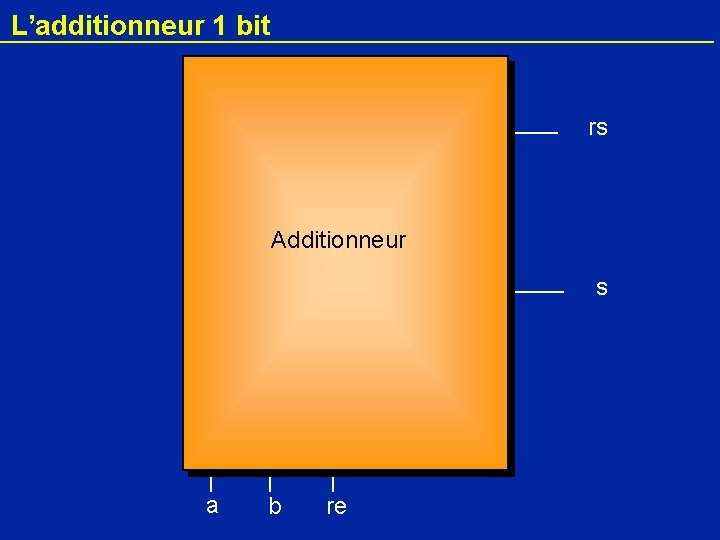

L’additionneur 1 bit rs Additionneur s Sorties Entrées a b re

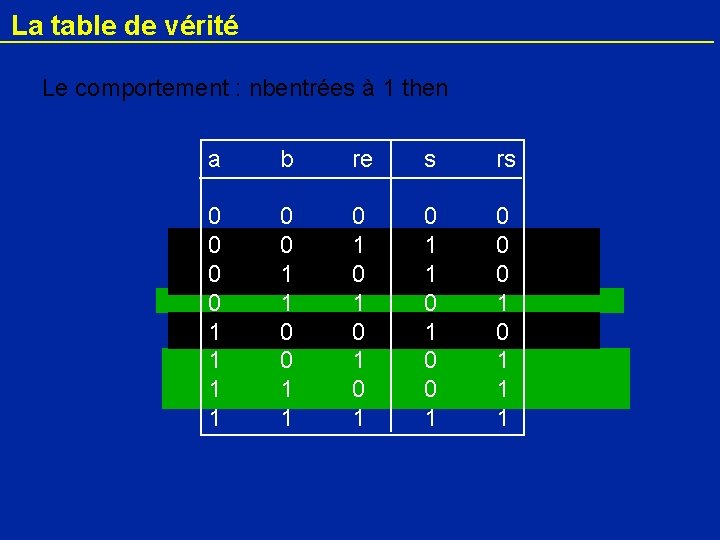

La table de vérité Le comportement : nbentrées à 1 then a b re s rs 0 0 1 1 0 1 0 1 0 1 1 0 0 0 1 1 1

L’additionneur 1 bit rs Additionneur s a b re

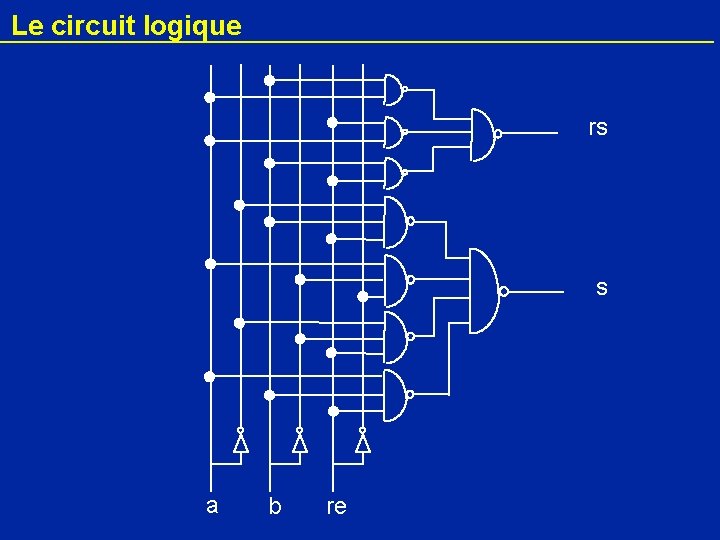

Le circuit logique rs s a b re

Objectifs o Le temps de calcul d ’un circuit est défini par le plus long chemin entre les entrées et les sorties. Nous étudions et analysons différentes architectures de l ’additionneur qui permettent d ’atteindre des performances de plus en plus élevées.

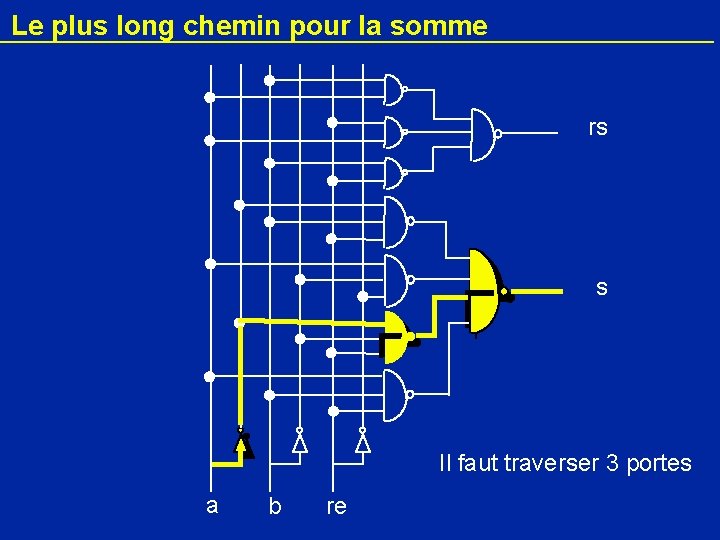

Le plus long chemin pour la somme rs s Il faut traverser 3 portes a b re

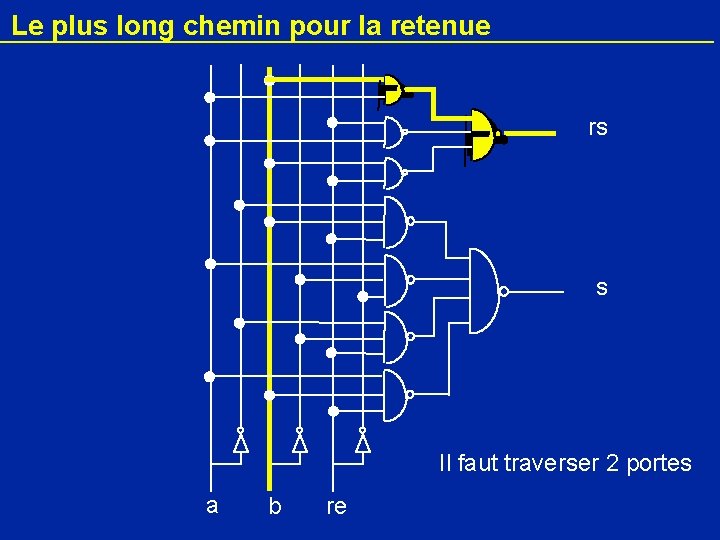

Le plus long chemin pour la retenue rs s Il faut traverser 2 portes a b re

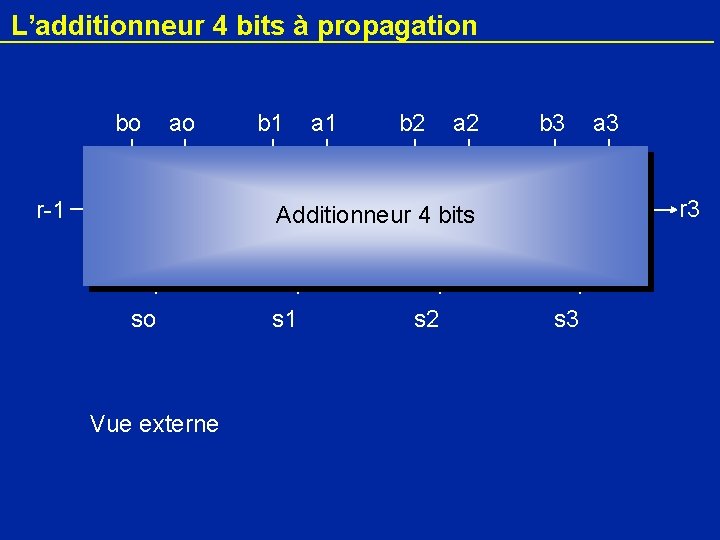

L’additionneur 4 bits à propagation bo ao b 1 b 2 a 2 r 1 r 0 r-1 a 1 b 3 a 3 r 2 1 Bit r-1 1 Bit Additionneur 4 bits 1 Bit so s 1 s 3 Vue externe s 2 r 3

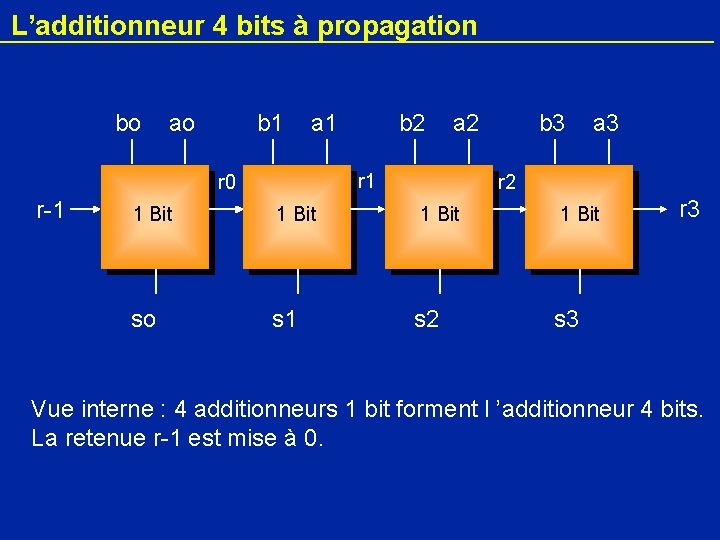

L’additionneur 4 bits à propagation bo ao b 1 a 2 r 1 r 0 r-1 b 2 b 3 a 3 r 2 1 Bit r-1 1 Bit so s 1 s 2 s 3 r 3 Vue interne : 4 additionneurs 1 bit forment l ’additionneur 4 bits. La retenue r-1 est mise à 0.

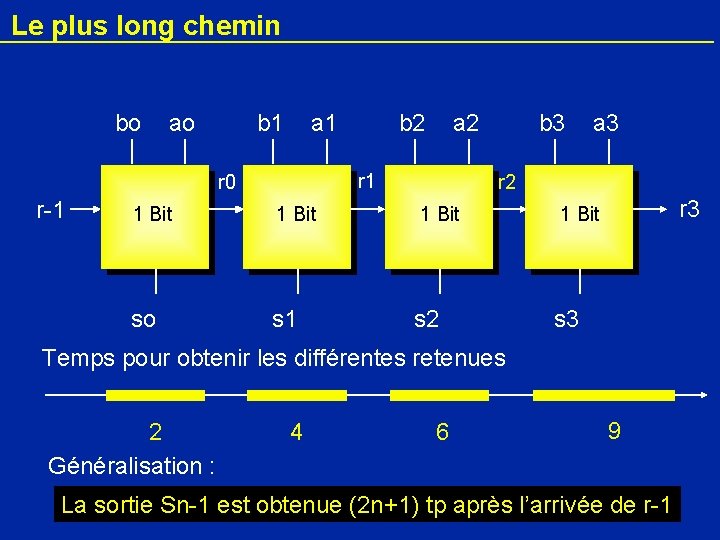

Le plus long chemin bo ao b 1 a 2 r 1 r 0 r-1 b 2 b 3 a 3 r 2 1 Bit r-1 1 Bit so s 1 s 2 s 3 r 3 Temps pour obtenir les différentes retenues 2 Généralisation : 4 6 9 La sortie Sn-1 est obtenue (2 n+1) tp après l’arrivée de r-1

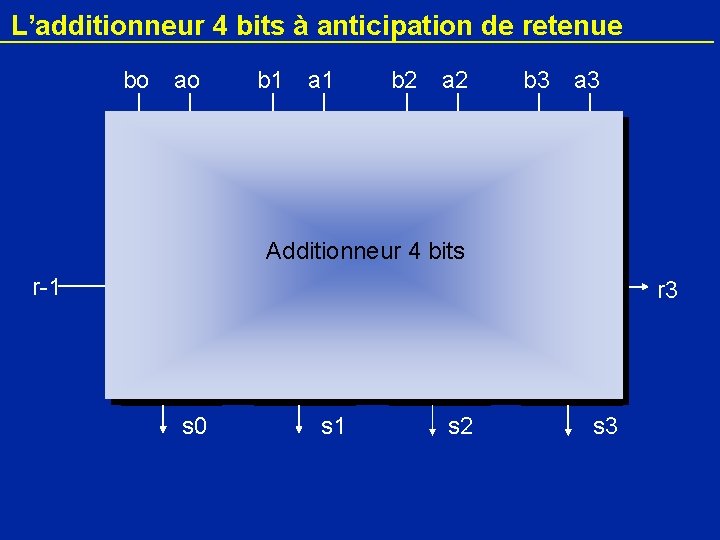

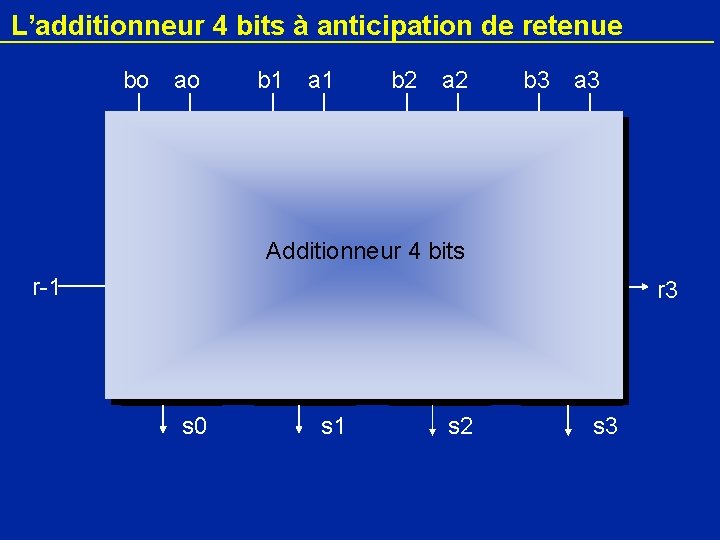

L’additionneur 4 bits à anticipation de retenue bo ao b 1 a 1 b 2 a 2 b 3 a 3 r-1 Go P 0 r-1 G 1 P 1 G 2 P 2 Additionneur 4 bits G 3 P 3 r 3 Circuit anticipation r-1 s 0 r 0 s 1 r 1 s 2 r 2 s 3

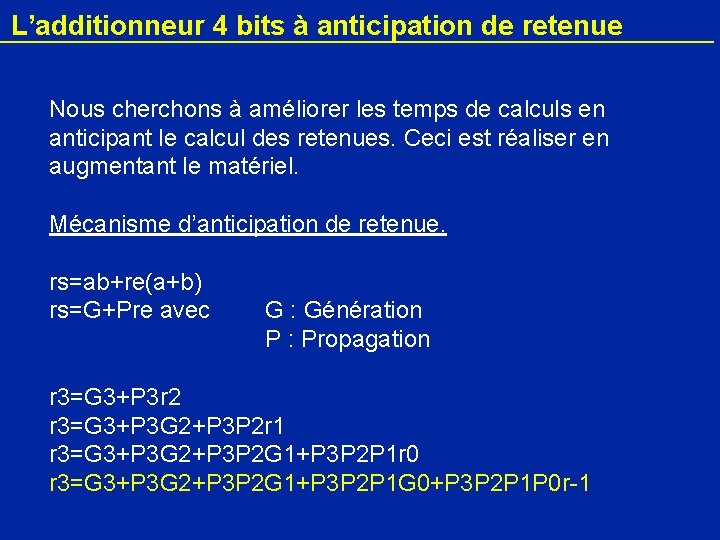

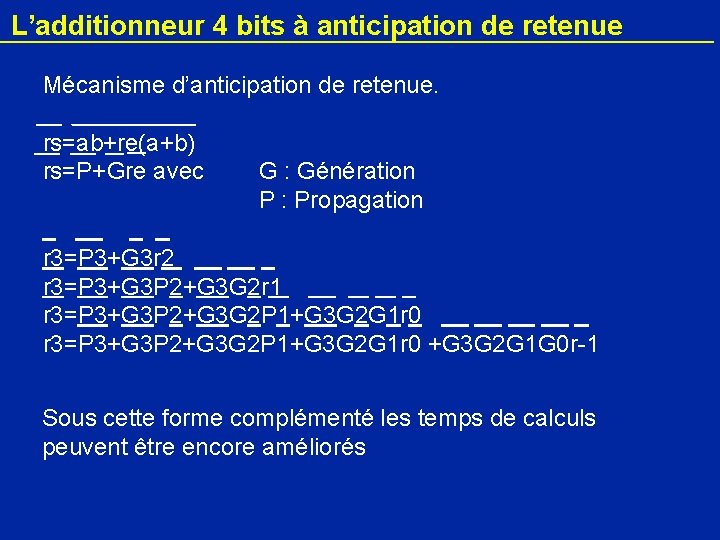

L’additionneur 4 bits à anticipation de retenue Nous cherchons à améliorer les temps de calculs en anticipant le calcul des retenues. Ceci est réaliser en augmentant le matériel. Mécanisme d’anticipation de retenue. rs=ab+re(a+b) rs=G+Pre avec G : Génération P : Propagation r 3=G 3+P 3 r 2 r 3=G 3+P 3 G 2+P 3 P 2 r 1 r 3=G 3+P 3 G 2+P 3 P 2 G 1+P 3 P 2 P 1 r 0 r 3=G 3+P 3 G 2+P 3 P 2 G 1+P 3 P 2 P 1 G 0+P 3 P 2 P 1 P 0 r-1

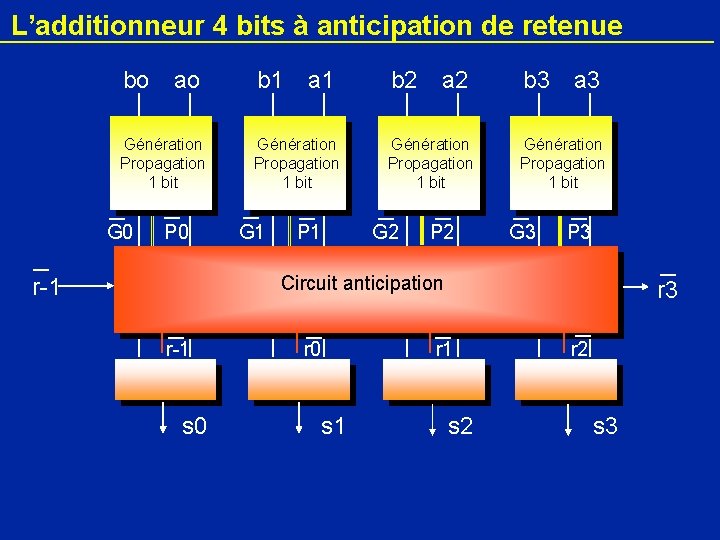

L’additionneur 4 bits à anticipation de retenue bo ao b 1 a 1 b 2 a 2 b 3 a 3 r-1 Go P 0 r-1 G 1 P 1 G 2 P 2 Additionneur 4 bits G 3 P 3 r 3 Circuit anticipation r-1 s 0 r 0 s 1 r 1 s 2 r 2 s 3

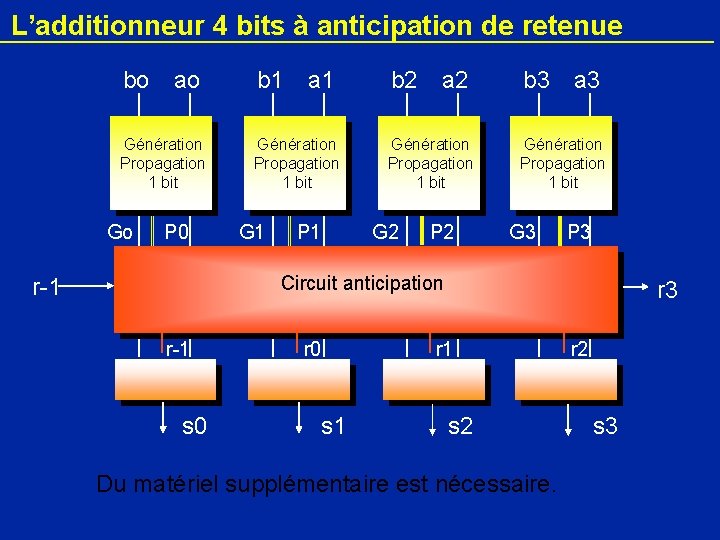

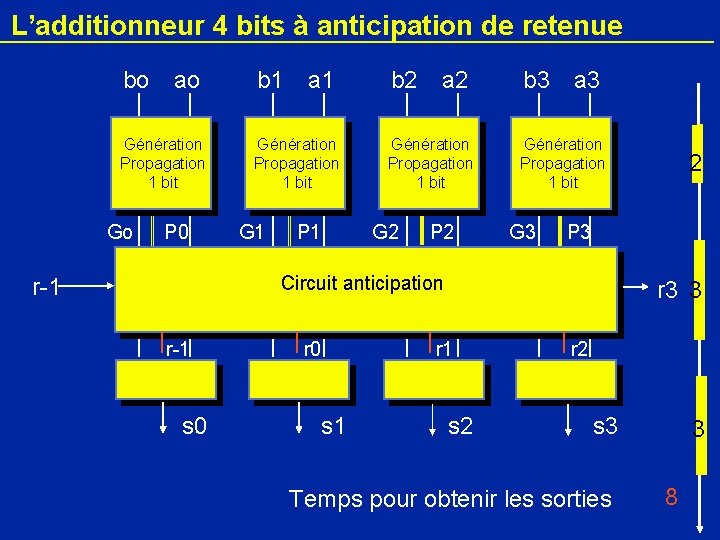

L’additionneur 4 bits à anticipation de retenue bo ao Génération r-1 Propagation 1 bit Go P 0 b 1 a 1 Génération Propagation 1 bit G 1 P 1 b 2 a 2 Génération Propagation 1 bit G 2 P 2 b 3 a 3 Génération Propagation 1 bit G 3 P 3 Circuit anticipation r-1 s 0 r 0 s 1 r 3 r 1 s 2 Du matériel supplémentaire est nécessaire. r 2 s 3

L’additionneur 4 bits à anticipation de retenue bo ao Génération r-1 Propagation 1 bit Go P 0 b 1 a 1 Génération Propagation 1 bit G 1 P 1 b 2 a 2 Génération Propagation 1 bit G 2 P 2 b 3 a 3 Génération Propagation 1 bit G 3 P 3 Circuit anticipation r-1 s 0 r 0 s 1 2 r 3 3 r 1 s 2 r 2 s 3 Temps pour obtenir les sorties 3 8

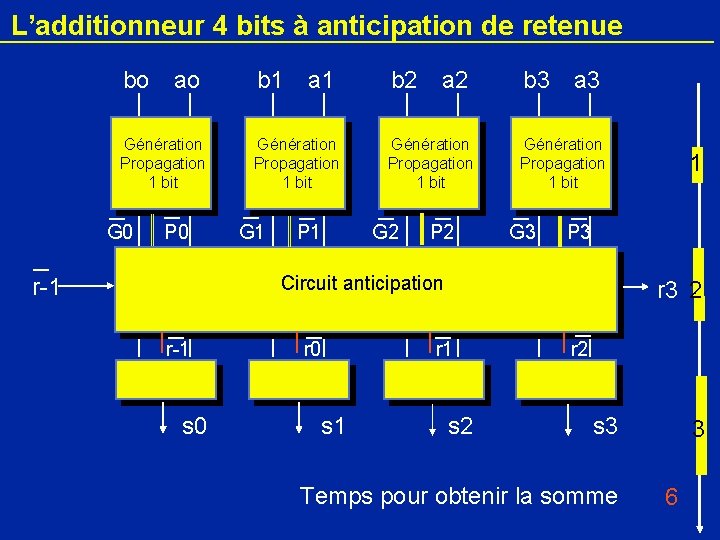

L’additionneur 4 bits à anticipation de retenue Mécanisme d’anticipation de retenue. rs=ab+re(a+b) rs=P+Gre avec G : Génération P : Propagation r 3=P 3+G 3 r 2 r 3=P 3+G 3 P 2+G 3 G 2 r 1 r 3=P 3+G 3 P 2+G 3 G 2 P 1+G 3 G 2 G 1 r 0 +G 3 G 2 G 1 G 0 r-1 Sous cette forme complémenté les temps de calculs peuvent être encore améliorés

L’additionneur 4 bits à anticipation de retenue bo ao Génération r-1 Propagation 1 bit G 0 P 0 b 1 a 1 Génération Propagation 1 bit G 1 P 1 b 2 a 2 Génération Propagation 1 bit G 2 P 2 b 3 a 3 Génération Propagation 1 bit G 3 P 3 Circuit anticipation r-1 s 0 r 0 s 1 r 3 r 1 s 2 r 2 s 3

L’additionneur 4 bits à anticipation de retenue bo ao Génération r-1 Propagation 1 bit G 0 P 0 b 1 a 1 Génération Propagation 1 bit G 1 P 1 b 2 a 2 Génération Propagation 1 bit G 2 P 2 b 3 a 3 Génération Propagation 1 bit G 3 P 3 Circuit anticipation r-1 s 0 r 0 s 1 1 r 3 2 r 1 s 2 r 2 s 3 Temps pour obtenir la somme 3 6

- Slides: 49