Les nouveaux bus de donnes H Le Provost

Les nouveaux bus de données H. Le Provost (SEDI) Journée Electronique du DAPNIA, 10 Novembre 2006

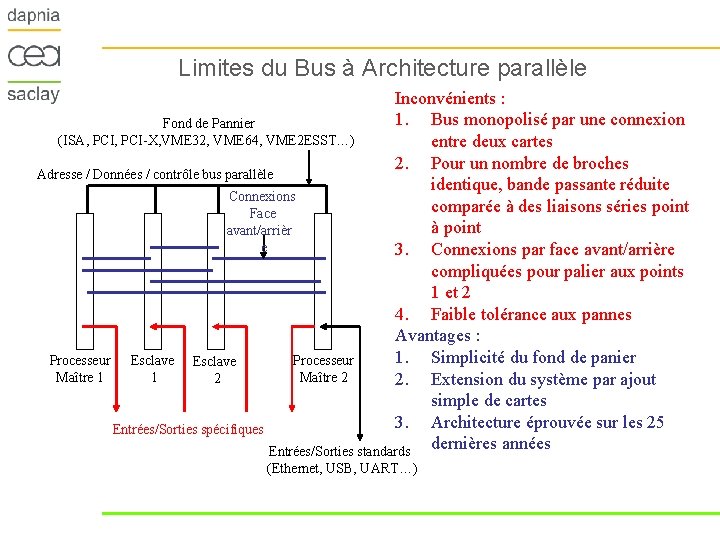

Limites du Bus à Architecture parallèle Inconvénients : 1. Bus monopolisé par une connexion Fond de Pannier (ISA, PCI-X, VME 32, VME 64, VME 2 ESST…) entre deux cartes 2. Pour un nombre de broches Adresse / Données / contrôle bus parallèle identique, bande passante réduite Connexions comparée à des liaisons séries point Face à point avant/arrièr e 3. Connexions par face avant/arrière compliquées pour palier aux points 1 et 2 4. Faible tolérance aux pannes Avantages : 1. Simplicité du fond de panier Processeur Esclave Processeur Maître 1 1 Maître 2 2 2. Extension du système par ajout simple de cartes 3. Architecture éprouvée sur les 25 Entrées/Sorties spécifiques dernières années Entrées/Sorties standards (Ethernet, USB, UART…)

Évolution des Bus d’acquisition de données ISA, Industry Standard Architecture (PC) PCI, Peripheral Component Interconnect (PC) Accelerated Graphic Port (PC) AGP, VME, Versa Module Eurocard Débit Max. * PCI-E 1. 1 (2 x 8 GO/s) * PCI-X 2. 0 (4, 3 GO/s) * AGP 8 x (2, 1 * PCI-XGO/s) 1. 0 (1 GO/s) * PCI 2. 1 (528 MO/s) * VME 2 ESST (320 MO/s) * PCI 1. 0 (132 MO/s) * VME 64 (80 MO/s) * VME 32 (40 MO/s) * ISA (16, 7 MO/s) * ISA (4, 8 MO/s) 1981 1982 1984 1992 1994 1995 1998 1999 2002 2003 Année

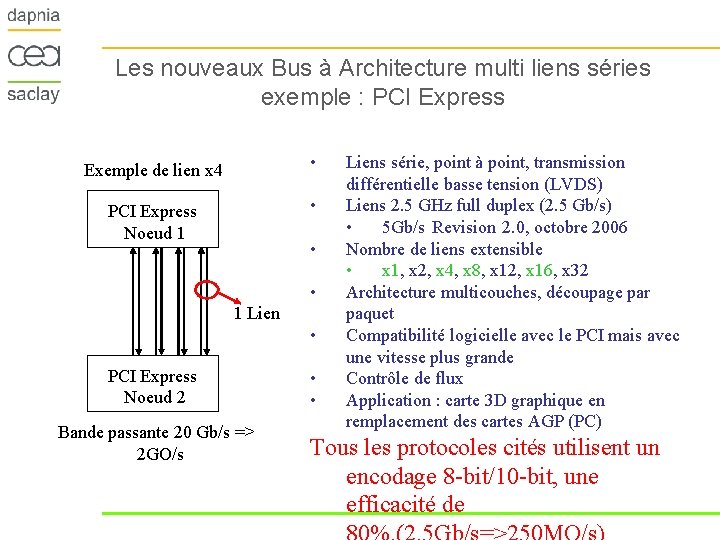

Les nouveaux Bus à Architecture multi liens séries exemple : PCI Express Exemple de lien x 4 • PCI Express Noeud 1 • • • 1 Lien • PCI Express Noeud 2 Bande passante 20 Gb/s => 2 GO/s • • Liens série, point à point, transmission différentielle basse tension (LVDS) Liens 2. 5 GHz full duplex (2. 5 Gb/s) • 5 Gb/s Revision 2. 0, octobre 2006 Nombre de liens extensible • x 1, x 2, x 4, x 8, x 12, x 16, x 32 Architecture multicouches, découpage par paquet Compatibilité logicielle avec le PCI mais avec une vitesse plus grande Contrôle de flux Application : carte 3 D graphique en remplacement des cartes AGP (PC) Tous les protocoles cités utilisent un encodage 8 -bit/10 -bit, une efficacité de

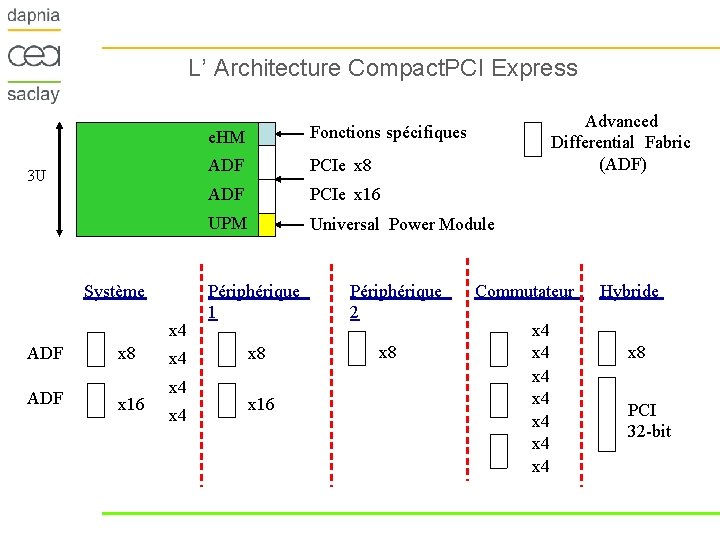

L’ Architecture Compact. PCI Express 3 U Système x 4 ADF x 8 x 16 x 4 x 4 Advanced Differential Fabric (ADF) e. HM Fonctions spécifiques ADF PCIe x 8 ADF PCIe x 16 UPM Universal Power Module Périphérique 1 x 8 x 16 Périphérique 2 x 8 Commutateur x 4 x 4 Hybride x 8 PCI 32 -bit

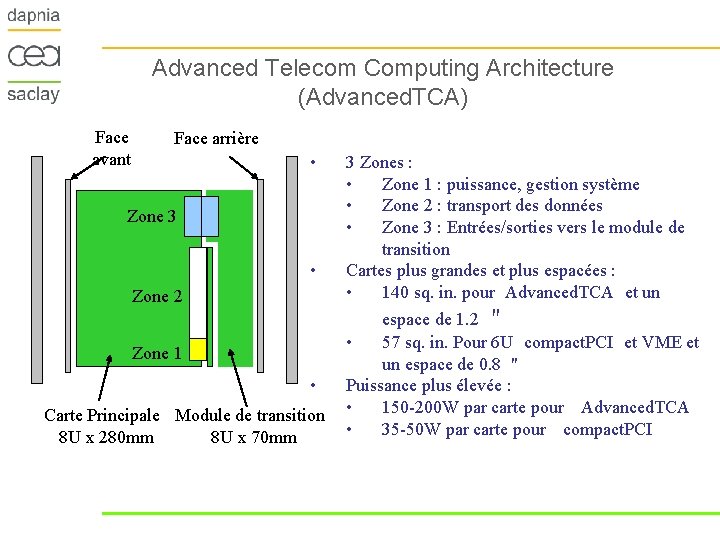

Advanced Telecom Computing Architecture (Advanced. TCA) Face avant Face arrière • Zone 3 • Zone 2 Zone 1 • Carte Principale Module de transition 8 U x 280 mm 8 U x 70 mm 3 Zones : • Zone 1 : puissance, gestion système • Zone 2 : transport des données • Zone 3 : Entrées/sorties vers le module de transition Cartes plus grandes et plus espacées : • 140 sq. in. pour Advanced. TCA et un espace de 1. 2 " • 57 sq. in. Pour 6 U compact. PCI et VME et un espace de 0. 8 " Puissance plus élevée : • 150 -200 W par carte pour Advanced. TCA • 35 -50 W par carte pour compact. PCI

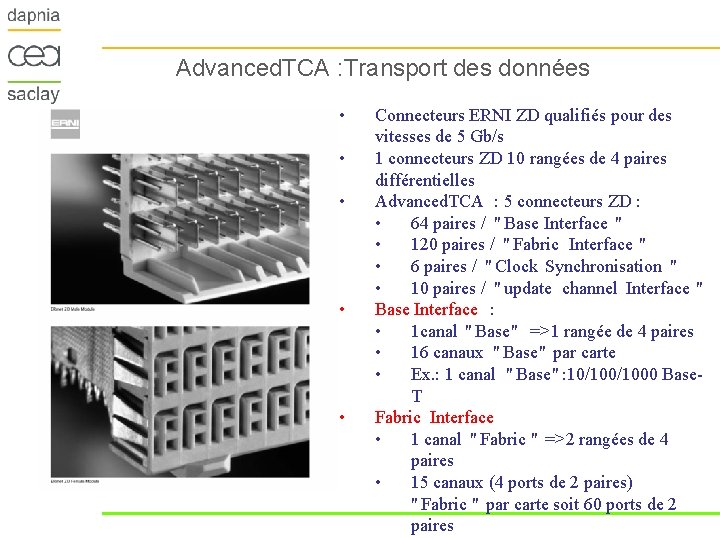

Advanced. TCA : Transport des données • • • Connecteurs ERNI ZD qualifiés pour des vitesses de 5 Gb/s 1 connecteurs ZD 10 rangées de 4 paires différentielles Advanced. TCA : 5 connecteurs ZD : • 64 paires / " Base Interface " • 120 paires / " Fabric Interface " • 6 paires / " Clock Synchronisation " • 10 paires / " update channel Interface " Base Interface : • 1 canal " Base" =>1 rangée de 4 paires • 16 canaux " Base" par carte • Ex. : 1 canal " Base" : 10/1000 Base. T Fabric Interface • 1 canal " Fabric " =>2 rangées de 4 paires • 15 canaux (4 ports de 2 paires) " Fabric " par carte soit 60 ports de 2 paires

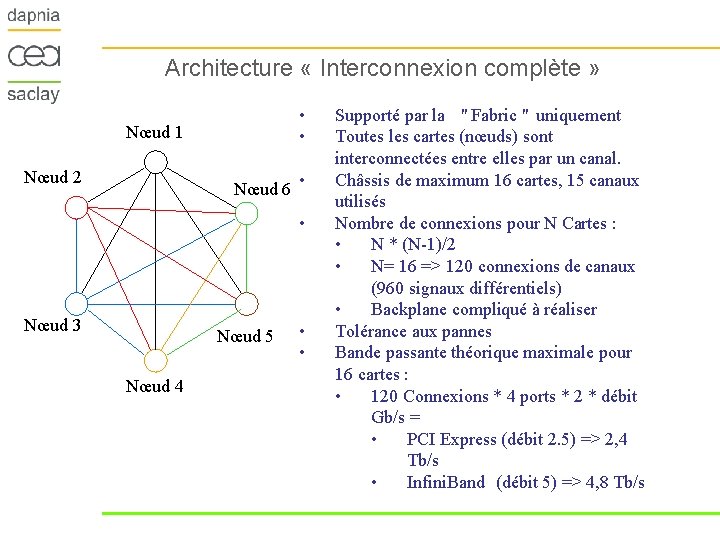

Architecture « Interconnexion complète » • • Nœud 1 Nœud 2 Nœud 6 • • Nœud 3 Nœud 5 Nœud 4 • • Supporté par la " Fabric " uniquement Toutes les cartes (nœuds) sont interconnectées entre elles par un canal. Châssis de maximum 16 cartes, 15 canaux utilisés Nombre de connexions pour N Cartes : • N * (N-1)/2 • N= 16 => 120 connexions de canaux (960 signaux différentiels) • Backplane compliqué à réaliser Tolérance aux pannes Bande passante théorique maximale pour 16 cartes : • 120 Connexions * 4 ports * 2 * débit Gb/s = • PCI Express (débit 2. 5) => 2, 4 Tb/s • Infini. Band (débit 5) => 4, 8 Tb/s

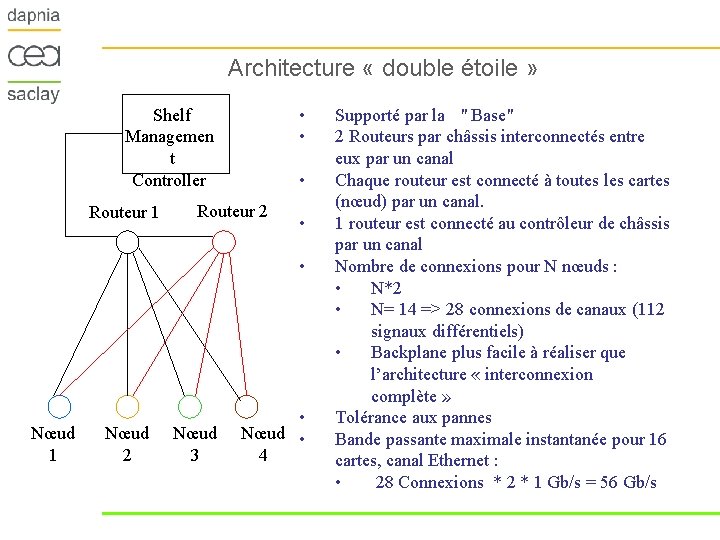

Architecture « double étoile » • • Shelf Managemen t Controller Routeur 1 • Routeur 2 • • Nœud 1 Nœud 2 Nœud 3 • Nœud • 4 Supporté par la " Base" 2 Routeurs par châssis interconnectés entre eux par un canal Chaque routeur est connecté à toutes les cartes (nœud) par un canal. 1 routeur est connecté au contrôleur de châssis par un canal Nombre de connexions pour N nœuds : • N*2 • N= 14 => 28 connexions de canaux (112 signaux différentiels) • Backplane plus facile à réaliser que l’architecture « interconnexion complète » Tolérance aux pannes Bande passante maximale instantanée pour 16 cartes, canal Ethernet : • 28 Connexions * 2 * 1 Gb/s = 56 Gb/s

Advanced. TCA : évolution Norme Advanced. TCA PICMG 3. 0 (Rev 2. 0 Mars 2005) indépendante du type de “Fabric“ : – – – PICMG PICMG 3. 1 3. 2 3. 3 3. 4 3. 5 : : : Ethernet (Janvier 2003) Infini. Band (Janvier 2003) Star. Fabric (Mai 2003) PCIExpress (Mai 2003) Rapid. IO (Septembre 2005) Advanced. MC AMC. 0 (Mars 2005) cartes mezzanines Cartes, fonds de panier, châssis disponibles sur le marché

Conclusion Nouveaux bus : agrégat de liaisons point à point haut-débit VMEbus Switched Serial (VXS) ~ Advanced. TCA mais moins performant Très haute bande passante Fiabilité Fonds de panier dédiés avec des emplacements pour nœuds de commutation, nœuds simples

- Slides: 11