Les FPGAs Emmanuel Boutillon Cours ralis partir de

Les FPGAs Emmanuel Boutillon Cours réalisé à partir de : Nathalie Julien, cours IUP EEA 1999. Jean-Luc Danger, ENST Paris Cours de l’ISEP disponible sur le WEB Pierre Bomel -1 - Emmanuel Boutillon

PLAN Comment et pourquoi faire de la logique programmable ? Les technologies de personnalisation PAL, EPLD et FPGA Spécificité du développement des CLPs Situation présente et évolution. -2 - Emmanuel Boutillon

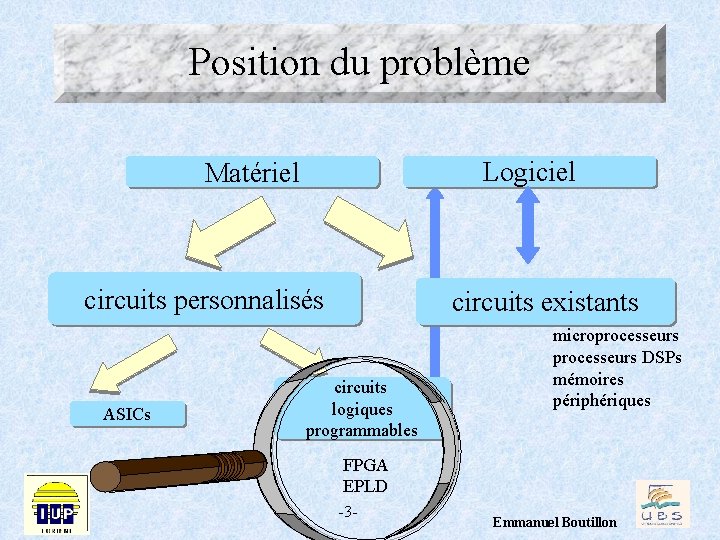

Position du problème Logiciel Matériel circuits personnalisés ASICs circuits existants circuits logiques programmables microprocesseurs DSPs mémoires périphériques FPGA EPLD -3 - Emmanuel Boutillon

Position du problème L’intérêt des CLP se justifie (depuis 30 ans) par : Le coûts très important des ASICs Le temps de développement d ’un ASIC Les performances faibles du logiciel La non flexibilité des solutions ASIC « Démocratisation » des FPGA -4 - Emmanuel Boutillon

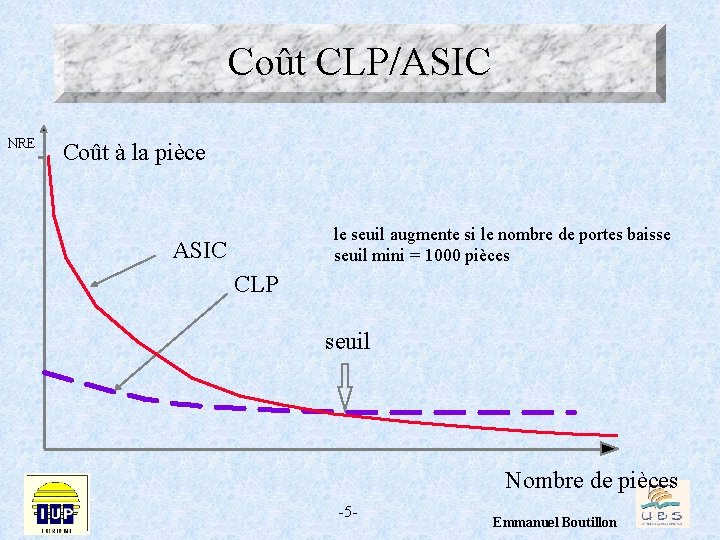

Coût CLP/ASIC NRE Coût à la pièce le seuil augmente si le nombre de portes baisse seuil mini = 1000 pièces ASIC CLP seuil Nombre de pièces -5 - Emmanuel Boutillon

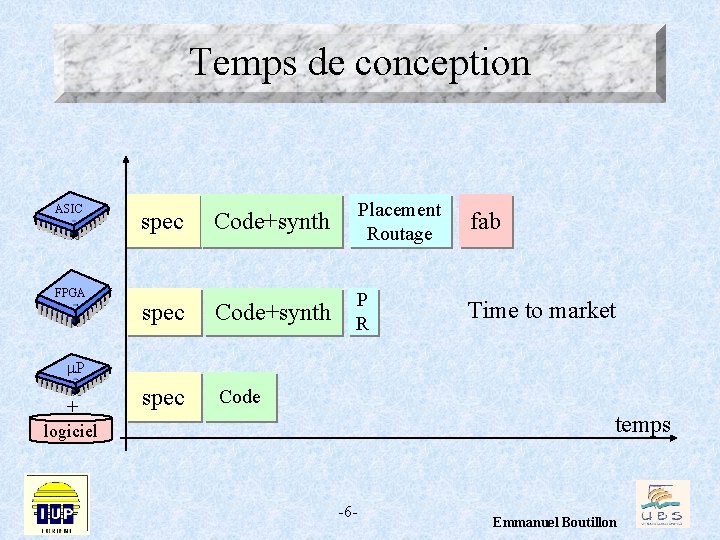

Temps de conception ASIC FPGA spec Code+synth Placement Routage spec Code+synth P R spec Code fab Time to market m. P + temps logiciel -6 - Emmanuel Boutillon

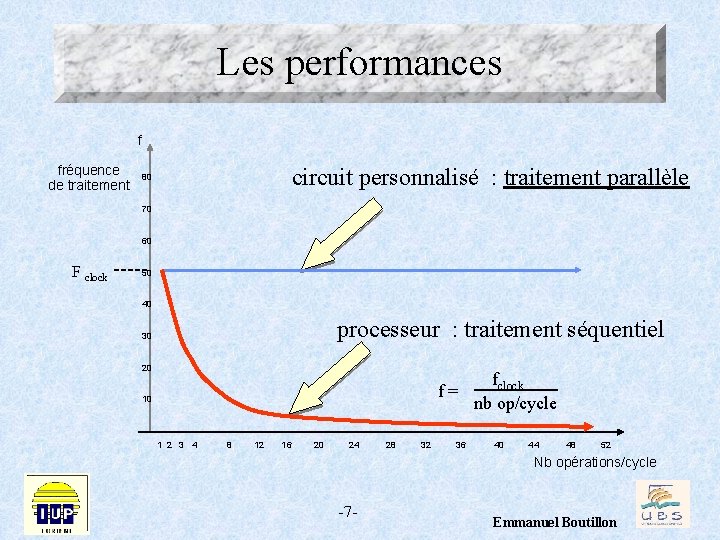

Les performances f fréquence de traitement 80 circuit personnalisé : traitement parallèle 70 60 F clock 50 40 30 processeur : traitement séquentiel 20 f = 10 fclock nb op/cycle 1 2 3 4 8 12 16 20 24 28 32 36 40 44 48 52 Nb opérations/cycle -7 - Emmanuel Boutillon

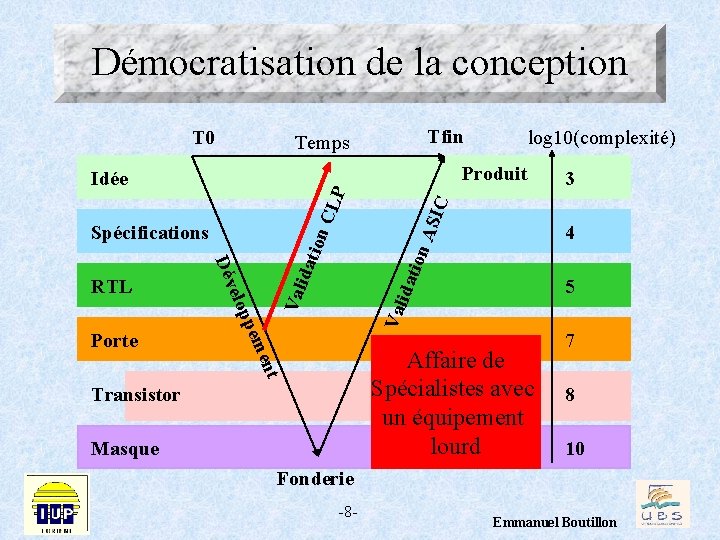

Démocratisation de la conception T 0 3 C P ASI CL 4 idat 5 Val pem elop Dév idat ion Spécifications Porte log 10(complexité) Produit Idée RTL Tfin Temps ent Affaire de Spécialistes avec un équipement lourd Transistor Masque 7 8 10 Fonderie -8 - Emmanuel Boutillon

Intérêts propres aux CLPs l prototypage conception rapide de démonstrateurs ï autonomie (pas de fondeur) ï l Reprogrammation ï maintenance in situ -9 - Emmanuel Boutillon

Comment faire des CLP ? Un circuit classique contient : - des portes logiques ; - des connections entre les portes logiques ; - des éléments de mémorisation (registre et/ou mémoire) ; - des entrées-sorties. - une (ou des) horloges - une structure hiérarchique Le CLP doit donc avoir les mêmes fonctionnalités, avec la notion de « programmabilité » . -10 - Emmanuel Boutillon

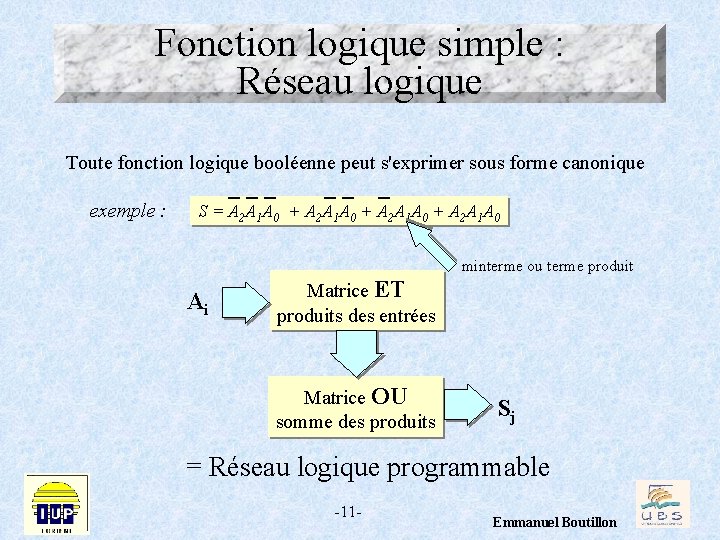

Fonction logique simple : Réseau logique Toute fonction logique booléenne peut s'exprimer sous forme canonique exemple : S = A 2 A 1 A 0 + A 2 A 1 A 0 minterme ou terme produit Ai Matrice ET produits des entrées Matrice OU somme des produits Sj = Réseau logique programmable -11 - Emmanuel Boutillon

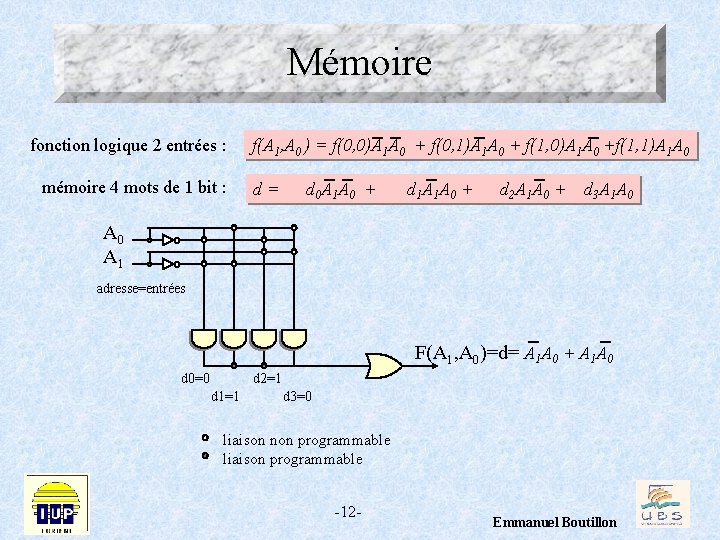

Mémoire fonction logique 2 entrées : mémoire 4 mots de 1 bit : f(A 1, A 0 ) = f(0, 0)A 1 A 0 + f(0, 1)A 1 A 0 + f(1, 0)A 1 A 0 +f(1, 1)A 1 A 0 d= d 0 A 1 A 0 + d 2 A 1 A 0 + d 3 A 1 A 0 A 1 adresse=entrées F(A 1, A 0)=d= A 1 A 0 + A 1 A 0 d 0=0 d 2=1 d 1=1 d 3=0 liaison non programmable liaison programmable -12 - Emmanuel Boutillon

Mémoire mémoire 16 mots de 2 bits => 2 fonctions logiques de 4 entrées A 0 A 1 A 2 A 3 matrice ET figée adresse=entrées matrice S 0 OU S 1 programmable liaison non programmable liaison programmable -13 - Emmanuel Boutillon

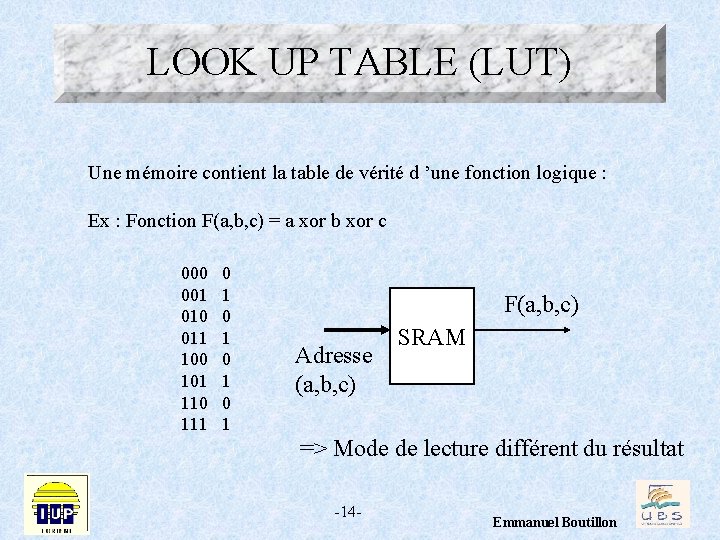

LOOK UP TABLE (LUT) Une mémoire contient la table de vérité d ’une fonction logique : Ex : Fonction F(a, b, c) = a xor b xor c 000 0 001 1 010 0 011 1 100 0 101 1 110 0 111 1 F(a, b, c) Adresse (a, b, c) SRAM => Mode de lecture différent du résultat -14 - Emmanuel Boutillon

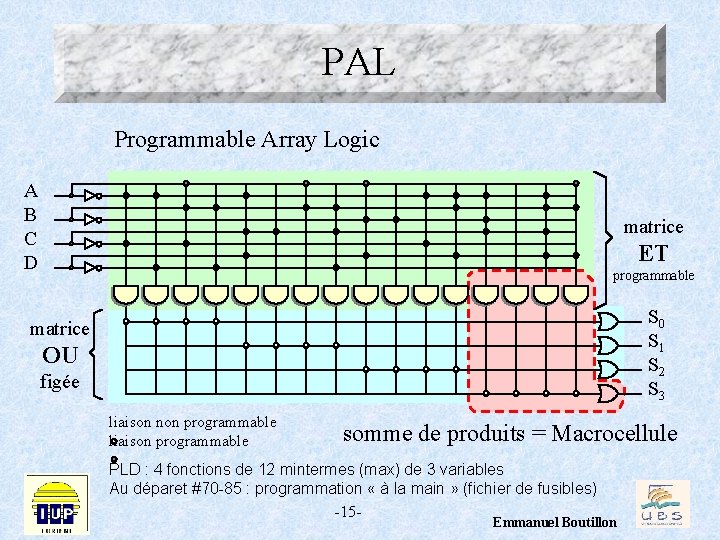

PAL Programmable Array Logic A B C D matrice ET programmable S 0 S 1 S 2 S 3 matrice OU figée liaison non programmable liaison programmable somme de produits = Macrocellule PLD : 4 fonctions de 12 mintermes (max) de 3 variables Au déparet #70 -85 : programmation « à la main » (fichier de fusibles) -15 - Emmanuel Boutillon

cellule logique à MUX l utilisée pour la technologie ANTIFUSIBLE équivaut à une LUT cablée e 0 e 1 e 2 e 3 mux sortie a b sortie = abe 0 ou abe 1 ou abe 2 ou abe 3 intérêt : surface réduite cellule grain fin -16 - Emmanuel Boutillon

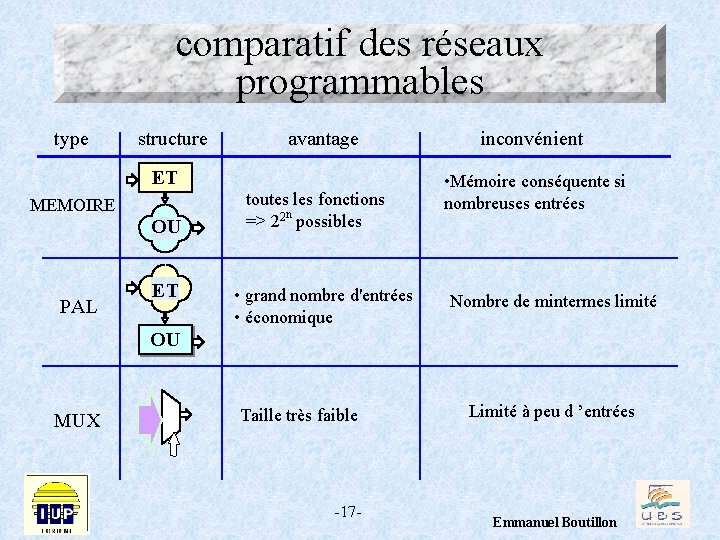

comparatif des réseaux programmables type structure avantage ET MEMOIRE PAL OU ET toutes les fonctions => 22 n possibles • grand nombre d'entrées • économique inconvénient • Mémoire conséquente si nombreuses entrées Nombre de mintermes limité OU MUX Taille très faible -17 - Limité à peu d ’entrées Emmanuel Boutillon

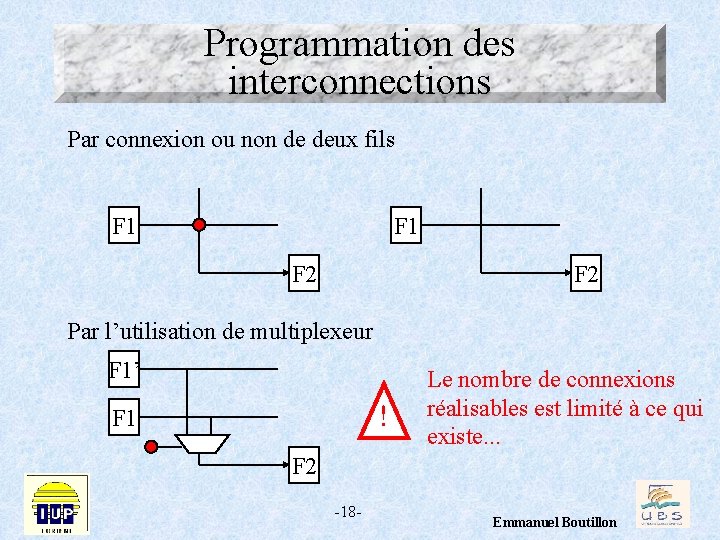

Programmation des interconnections Par connexion ou non de deux fils F 1 F 2 Par l’utilisation de multiplexeur F 1’ ! F 1 Le nombre de connexions réalisables est limité à ce qui existe. . . F 2 -18 - Emmanuel Boutillon

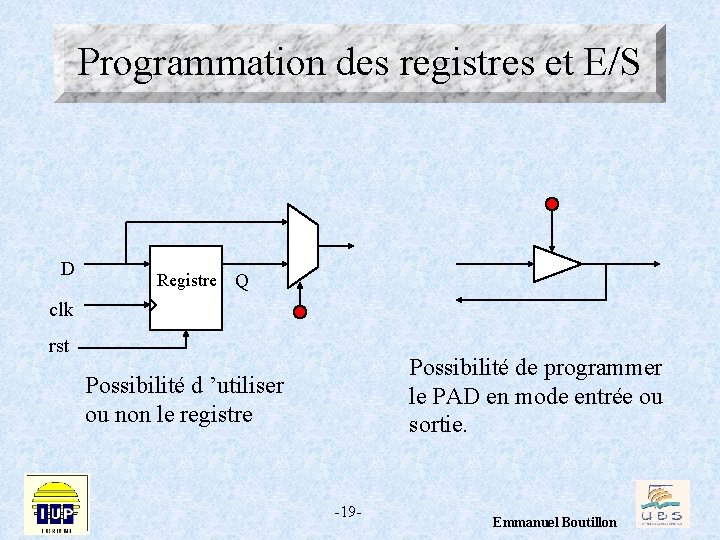

Programmation des registres et E/S D Registre Q clk rst Possibilité de programmer le PAD en mode entrée ou sortie. Possibilité d ’utiliser ou non le registre -19 - Emmanuel Boutillon

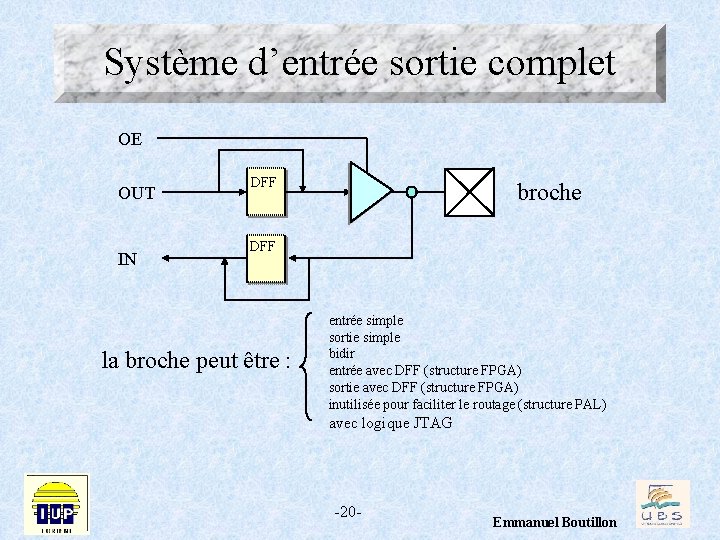

Système d’entrée sortie complet OE OUT IN DFF broche DFF la broche peut être : entrée simple sortie simple bidir entrée avec DFF (structure FPGA) sortie avec DFF (structure FPGA) inutilisée pour faciliter le routage (structure PAL) avec logique JTAG -20 - Emmanuel Boutillon

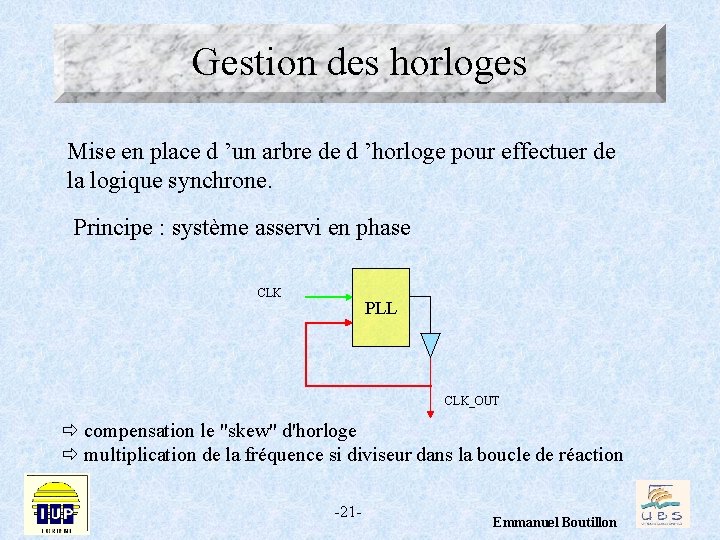

Gestion des horloges Mise en place d ’un arbre de d ’horloge pour effectuer de la logique synchrone. Principe : système asservi en phase CLK PLL CLK_OUT ð compensation le "skew" d'horloge ð multiplication de la fréquence si diviseur dans la boucle de réaction -21 - Emmanuel Boutillon

Gestion de la complexité Pour les CLP complexes, il est possible de définir des niveaux de hiérarchie du matériel. => Au niveau des interconnections => Au niveau du regroupement de fonctions logiques Il est aussi possible de diviser le circuit en fonctionnalités différentes : => Zone de mémoire RAM => Zone de CLP => Zone spécialisée -22 - Emmanuel Boutillon

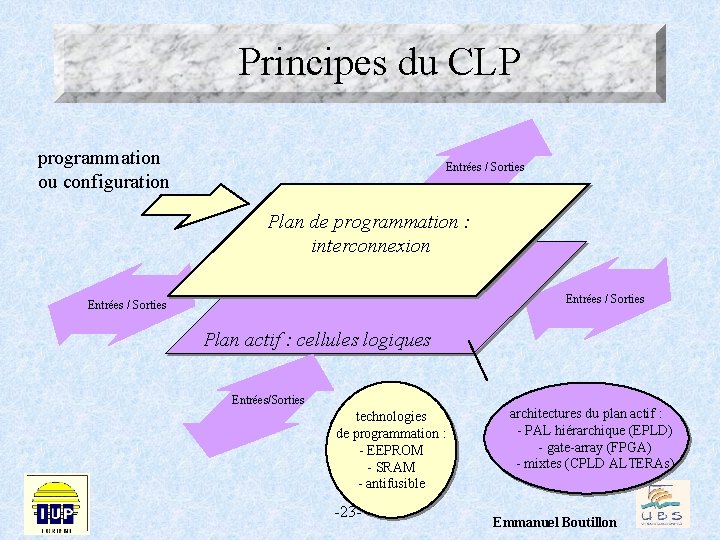

Principes du CLP programmation ou configuration Entrées / Sorties Plan de programmation : interconnexion Entrées / Sorties Plan actif : cellules logiques Entrées/Sorties technologies de programmation : - EEPROM - SRAM - antifusible -23 - architectures du plan actif : - PAL hiérarchique (EPLD) - gate-array (FPGA) - mixtes (CPLD ALTERAs) Emmanuel Boutillon

PLAN Comment et pourquoi faire de la logique programmable ? Les technologies de personnalisation PAL, EPLD et FPGA Spécificité du développement des CLPs Situation présente et évolution. -24 - Emmanuel Boutillon

Les composants logiques programmables : Les technologies de personnalisation Le circuit est personnalisé par création/destruction de connections sur la structure prédéfinie. ï Fusibles ï Anti-fusibles ï UV PROM (obsolète) EEPROM ï SRAM ï Métalisation ï Comparaison des différents techniques. -25 - Emmanuel Boutillon

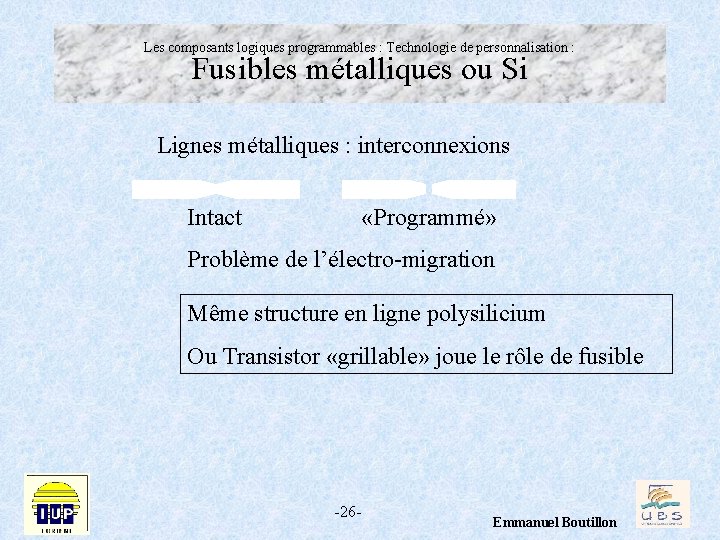

Les composants logiques programmables : Technologie de personnalisation : Fusibles métalliques ou Si Lignes métalliques : interconnexions Intact «Programmé» Problème de l’électro-migration Même structure en ligne polysilicium Ou Transistor «grillable» joue le rôle de fusible -26 - Emmanuel Boutillon

Les composants logiques programmables : Technologie de personnalisation : Antifusibles -27 - Emmanuel Boutillon

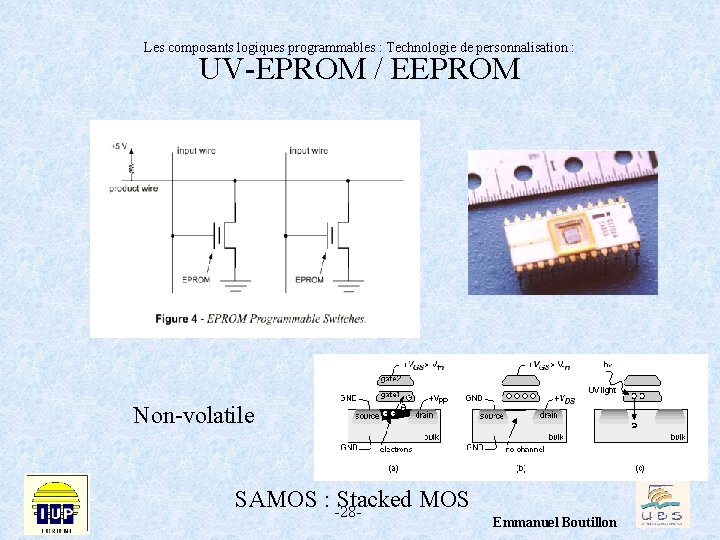

Les composants logiques programmables : Technologie de personnalisation : UV-EPROM / EEPROM Non-volatile SAMOS : Stacked MOS -28 - Emmanuel Boutillon

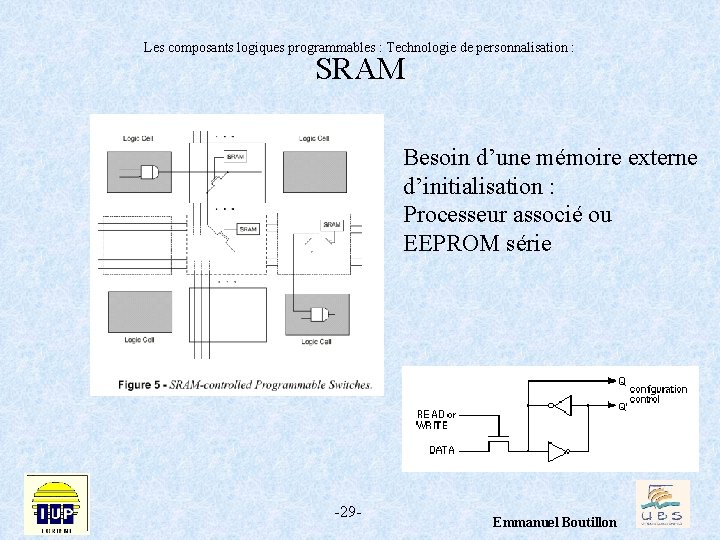

Les composants logiques programmables : Technologie de personnalisation : SRAM Besoin d’une mémoire externe d’initialisation : Processeur associé ou EEPROM série -29 - Emmanuel Boutillon

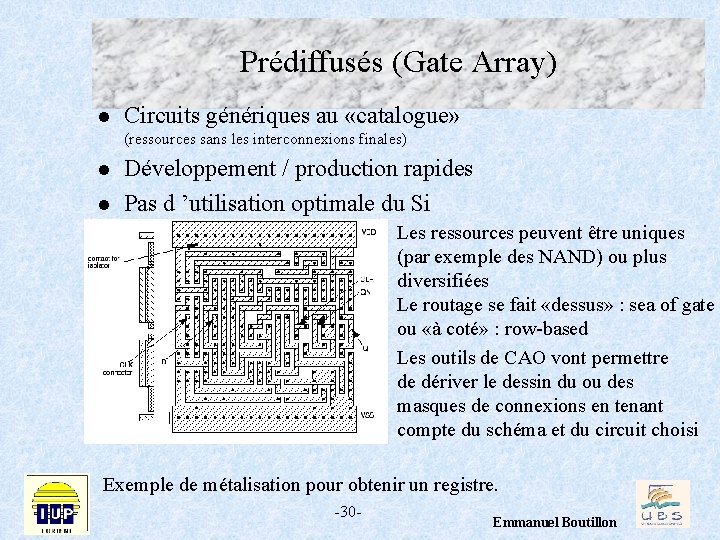

Prédiffusés (Gate Array) l Circuits génériques au «catalogue» (ressources sans les interconnexions finales) l l Développement / production rapides Pas d ’utilisation optimale du Si Les ressources peuvent être uniques (par exemple des NAND) ou plus diversifiées Le routage se fait «dessus» : sea of gate ou «à coté» : row-based Les outils de CAO vont permettre de dériver le dessin du ou des masques de connexions en tenant compte du schéma et du circuit choisi Exemple de métalisation pour obtenir un registre. -30 - Emmanuel Boutillon

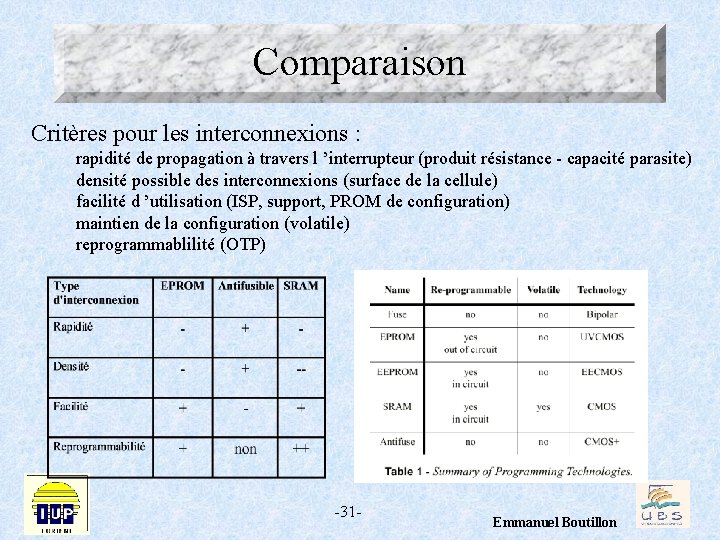

Comparaison Critères pour les interconnexions : rapidité de propagation à travers l ’interrupteur (produit résistance - capacité parasite) densité possible des interconnexions (surface de la cellule) facilité d ’utilisation (ISP, support, PROM de configuration) maintien de la configuration (volatile) reprogrammablilité (OTP) -31 - Emmanuel Boutillon

PLAN Comment et pourquoi faire de la logique programmable ? Les technologies de personnalisation PAL, EPLD et FPGA Spécificité du développement des CLPs Situation présente et évolution. -32 - Emmanuel Boutillon

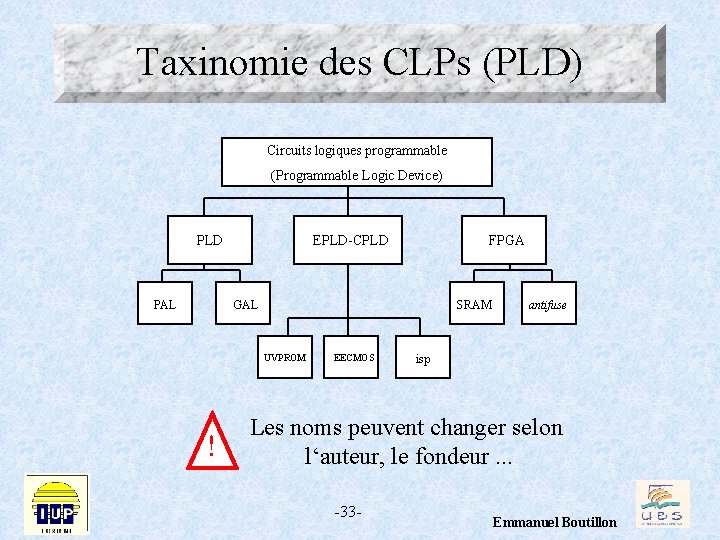

Taxinomie des CLPs (PLD) Circuits logiques programmable (Programmable Logic Device) PLD PAL EPLD-CPLD FPGA GAL SRAM UVPROM ! EECMOS antifuse isp Les noms peuvent changer selon l‘auteur, le fondeur. . . -33 - Emmanuel Boutillon

Vocabulaire (1) a. PAL, GAL ( Programmable Array Logic, Généric Array Logic). b. EPLD-CPLD (Erasable PLD ou Complex PLD) Les EPLD sont programmables électriquement et effaçables aux UV ; Les EEPLD sont effaçables électriquement Principe similaire aux PAL mais avec interconnexions réalisées en techno UVPROM On trouve également les p. LSI et isp. LSI (in situ programmable) c. FPGA (Field Programmable Gate Array) C ’est un ensemble de blocs logiques élémentaires que l ’utilisateur peut interconnecter pour réaliser les fonctions logiques de son choix La densité des portes est importante et sans cesse en évolution FPGA à SRAM ou LCA Logic Cell Array (1985 par Xilinx) FPGA à antifusibles (1990 Actel) non effaçables -34 - Emmanuel Boutillon

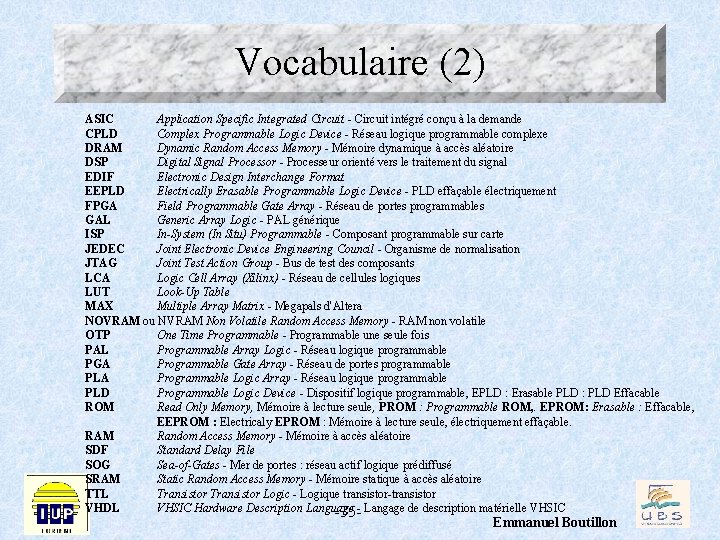

Vocabulaire (2) ASIC Application Specific Integrated Circuit - Circuit intégré conçu à la demande CPLD Complex Programmable Logic Device - Réseau logique programmable complexe DRAM Dynamic Random Access Memory - Mémoire dynamique à accès aléatoire DSP Digital Signal Processor - Processeur orienté vers le traitement du signal EDIF Electronic Design Interchange Format EEPLD Electrically Erasable Programmable Logic Device - PLD effaçable électriquement FPGA Field Programmable Gate Array - Réseau de portes programmables GAL Generic Array Logic - PAL générique ISP In-System (In Situ) Programmable - Composant programmable sur carte JEDEC Joint Electronic Device Engineering Council - Organisme de normalisation JTAG Joint Test Action Group - Bus de test des composants LCA Logic Cell Array (Xilinx) - Réseau de cellules logiques LUT Look-Up Table MAX Multiple Array Matrix - Megapals d'Altera NOVRAM ou NVRAM Non Volatile Random Access Memory - RAM non volatile OTP One Time Programmable - Programmable une seule fois PAL Programmable Array Logic - Réseau logique programmable PGA Programmable Gate Array - Réseau de portes programmable PLA Programmable Logic Array - Réseau logique programmable PLD Programmable Logic Device - Dispositif logique programmable, EPLD : Erasable PLD : PLD Effacable ROM Read Only Memory, Mémoire à lecture seule, PROM : Programmable ROM, . EPROM: Erasable : Effacable, EEPROM : Electricaly EPROM : Mémoire à lecture seule, électriquement effaçable. RAM Random Access Memory - Mémoire à accès aléatoire SDF Standard Delay File SOG Sea-of-Gates - Mer de portes : réseau actif logique prédiffusé SRAM Static Random Access Memory - Mémoire statique à accès aléatoire TTL Transistor Logic - Logique transistor-transistor VHDL VHSIC Hardware Description Language - Langage de description matérielle VHSIC -35 - Emmanuel Boutillon

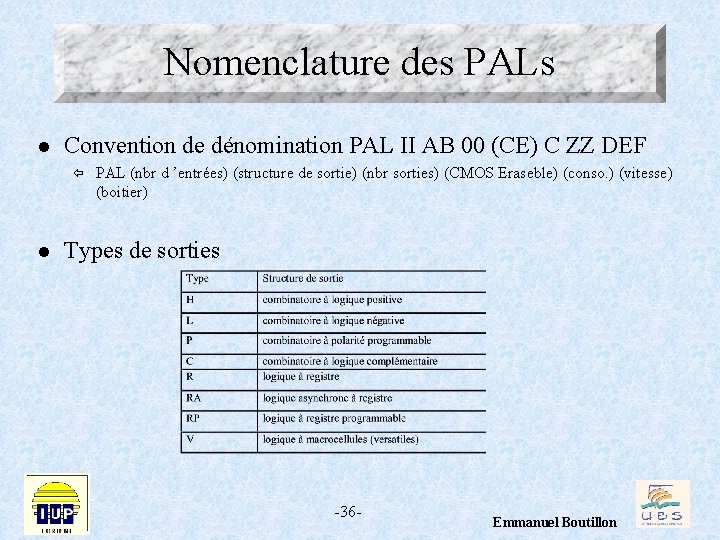

Nomenclature des PALs l Convention de dénomination PAL II AB 00 (CE) C ZZ DEF ï l PAL (nbr d ’entrées) (structure de sortie) (nbr sorties) (CMOS Eraseble) (conso. ) (vitesse) (boitier) Types de sorties -36 - Emmanuel Boutillon

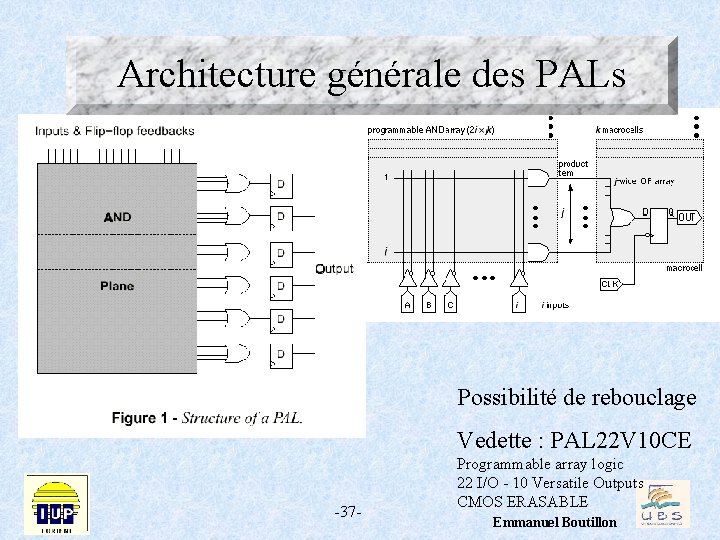

Principe des PAL Architecture générale des PALs Possibilité de rebouclage Vedette : PAL 22 V 10 CE -37 - Programmable array logic 22 I/O - 10 Versatile Outputs CMOS ERASABLE Emmanuel Boutillon

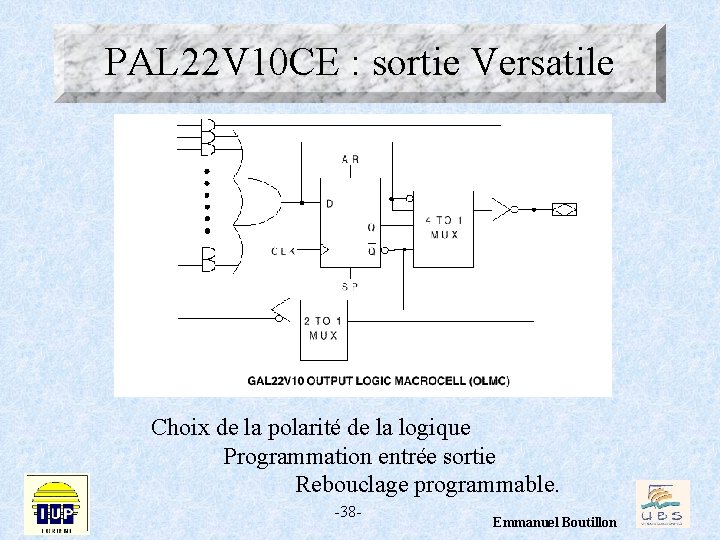

PAL 22 V 10 CE : sortie Versatile Choix de la polarité de la logique Programmation entrée sortie Rebouclage programmable. -38 - Emmanuel Boutillon

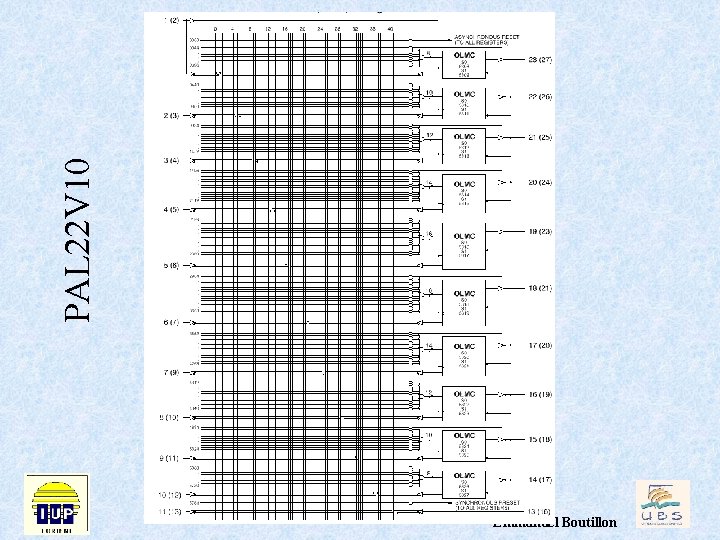

PAL 22 V 10 -39 - Emmanuel Boutillon

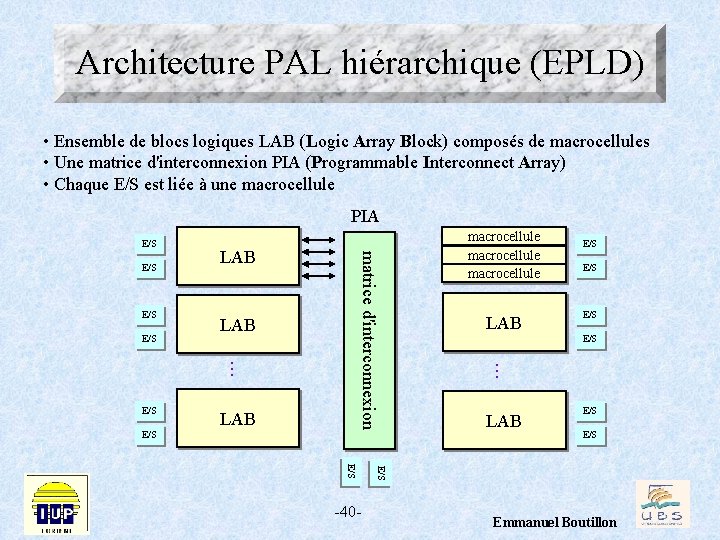

Architecture PAL hiérarchique (EPLD) • Ensemble de blocs logiques LAB (Logic Array Block) composés de macrocellules • Une matrice d'interconnexion PIA (Programmable Interconnect Array) • Chaque E/S est liée à une macrocellule PIA E/S LAB. . . E/S LAB E/S E/S -40 - . . . LAB matrice d'interconnexion E/S macrocellule . . . E/S Emmanuel Boutillon

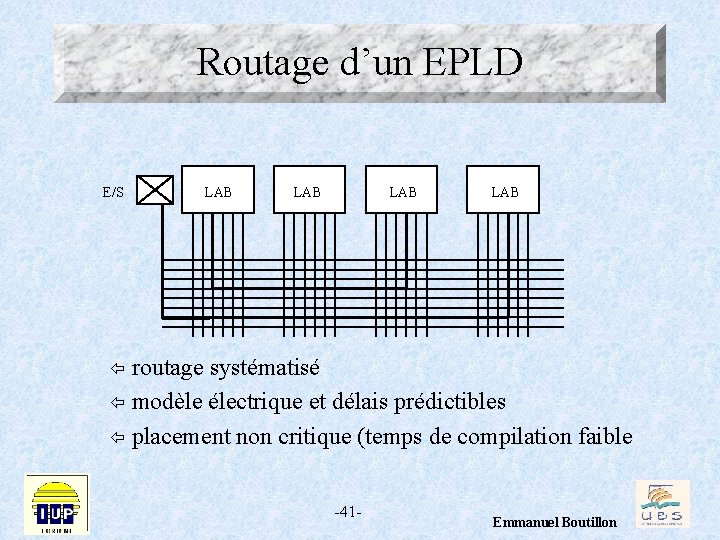

Routage d’un EPLD E/S LAB LAB routage systématisé ï modèle électrique et délais prédictibles ï placement non critique (temps de compilation faible ï -41 - Emmanuel Boutillon

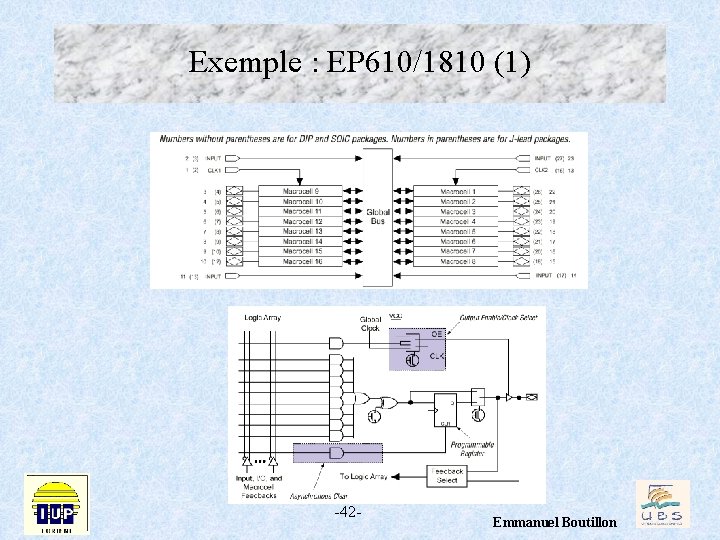

Exemple : EP 610/1810 (1) -42 - Emmanuel Boutillon

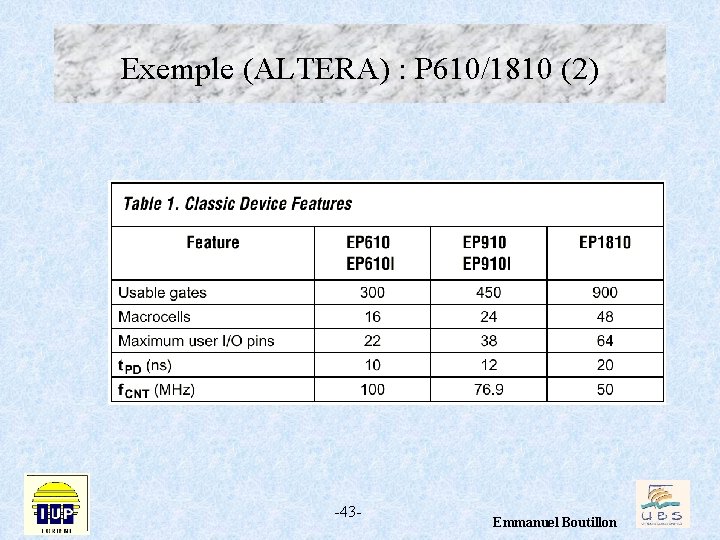

Exemple (ALTERA) : P 610/1810 (2) -43 - Emmanuel Boutillon

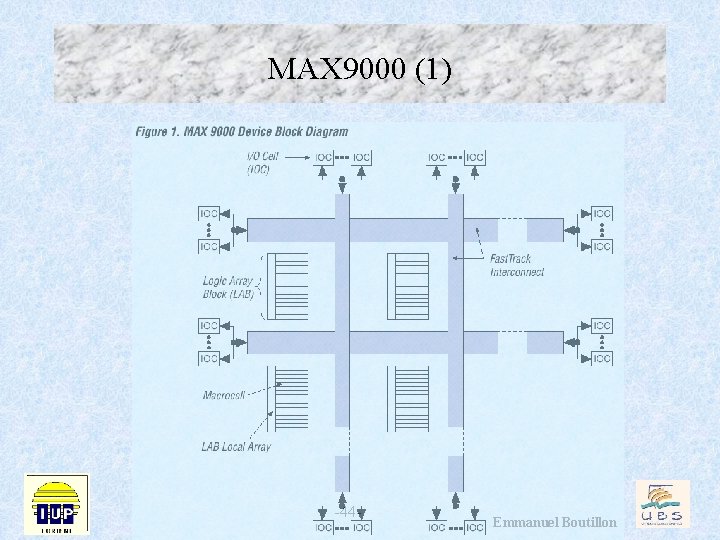

MAX 9000 (1) -44 - Emmanuel Boutillon

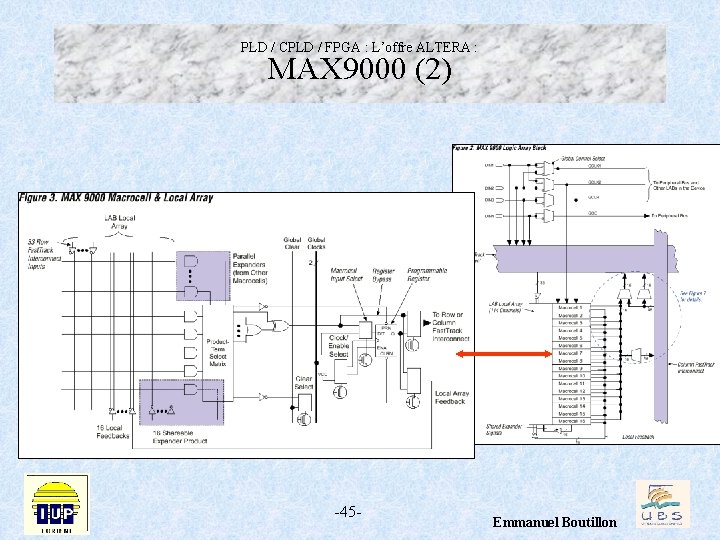

PLD / CPLD / FPGA : L’offre ALTERA : MAX 9000 (2) -45 - Emmanuel Boutillon

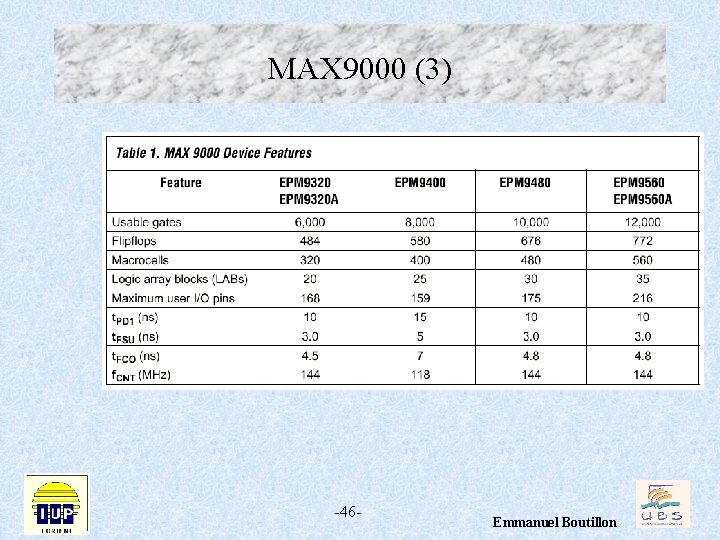

MAX 9000 (3) -46 - Emmanuel Boutillon

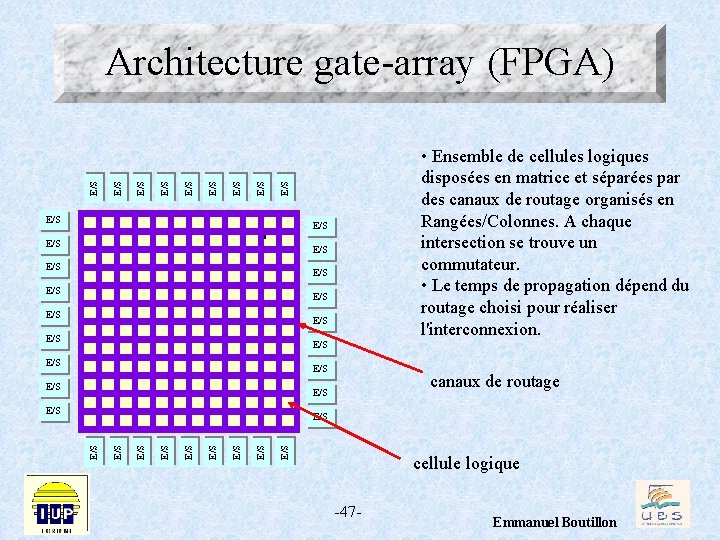

• Ensemble de cellules logiques disposées en matrice et séparées par des canaux de routage organisés en Rangées/Colonnes. A chaque intersection se trouve un commutateur. • Le temps de propagation dépend du routage choisi pour réaliser l'interconnexion. E/S E/S E/S Architecture gate-array (FPGA) E/S E/S E/S E/S canaux de routage E/S E/S E/S cellule logique -47 - Emmanuel Boutillon

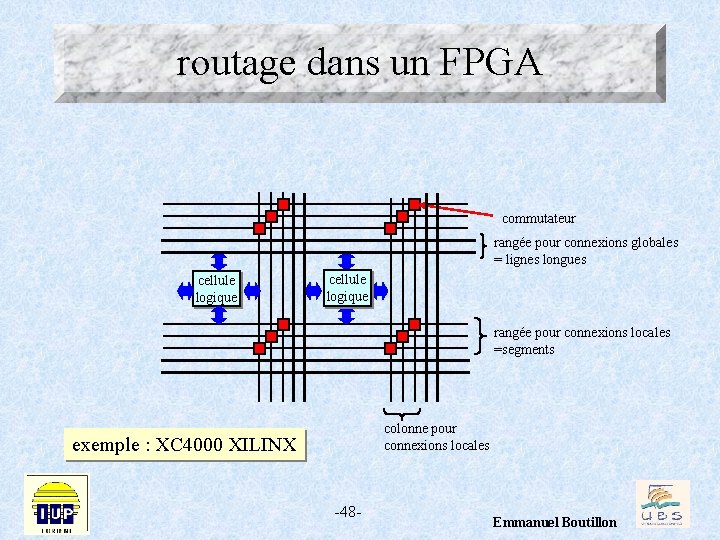

routage dans un FPGA commutateur rangée pour connexions globales = lignes longues cellule logique rangée pour connexions locales =segments colonne pour connexions locales exemple : XC 4000 XILINX -48 - Emmanuel Boutillon

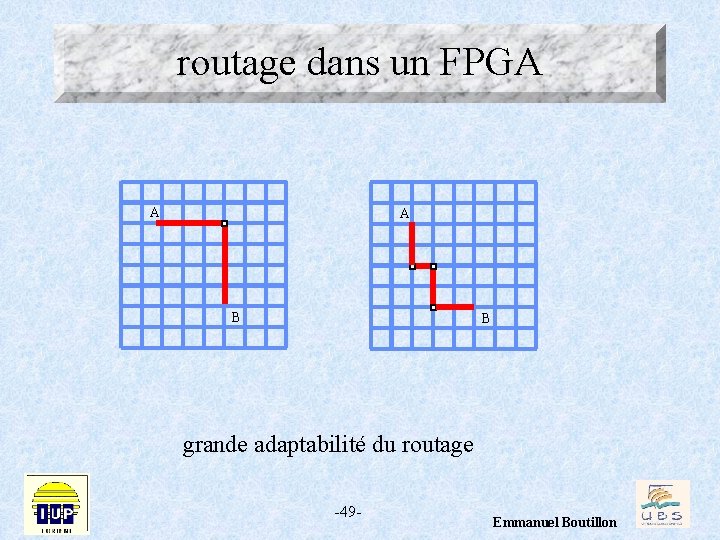

routage dans un FPGA A A B B grande adaptabilité du routage -49 - Emmanuel Boutillon

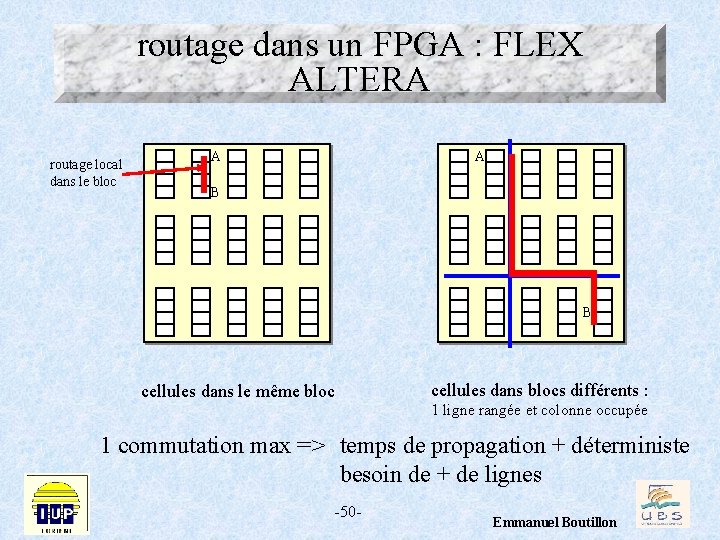

routage dans un FPGA : FLEX ALTERA routage local dans le bloc AA A A B B cellules dans le même bloc cellules dans blocs différents : 1 ligne rangée et colonne occupée 1 commutation max => temps de propagation + déterministe besoin de + de lignes -50 - Emmanuel Boutillon

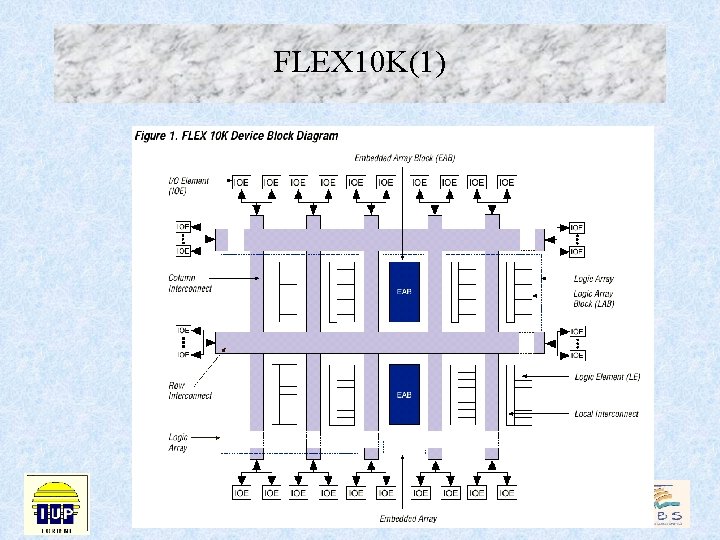

FLEX 10 K(1) -51 - Emmanuel Boutillon

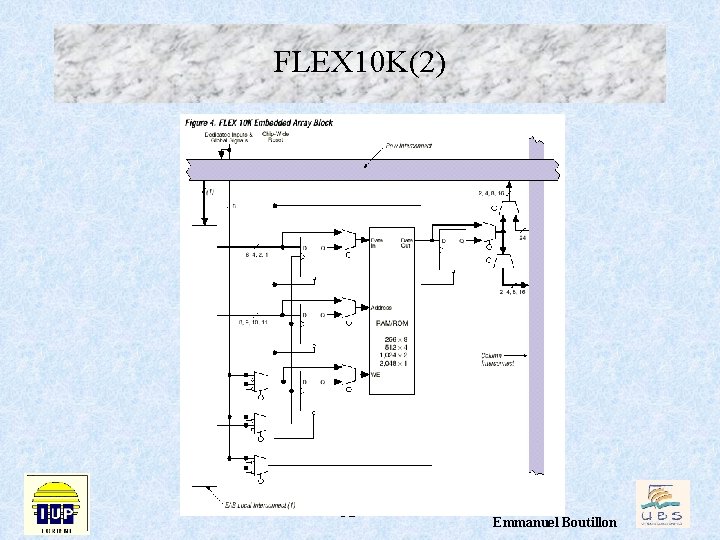

FLEX 10 K(2) -52 - Emmanuel Boutillon

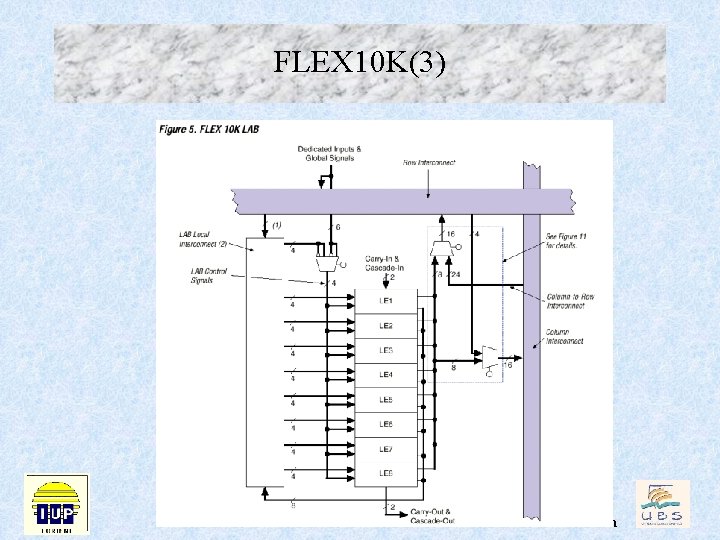

FLEX 10 K(3) -53 - Emmanuel Boutillon

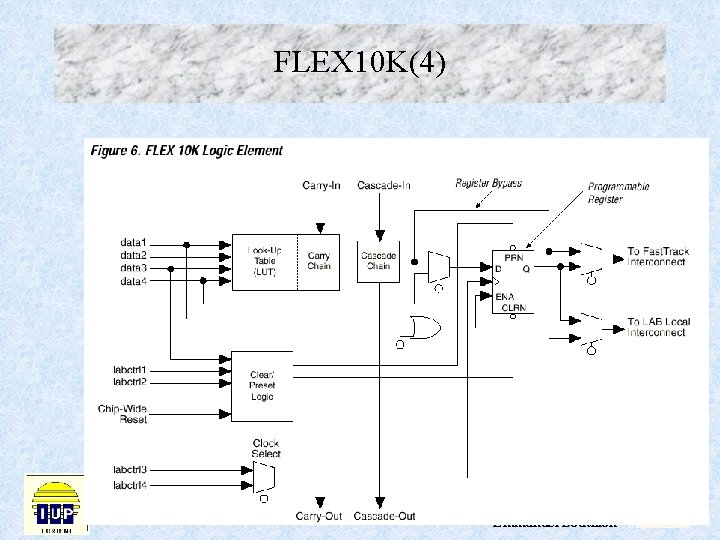

FLEX 10 K(4) -54 - Emmanuel Boutillon

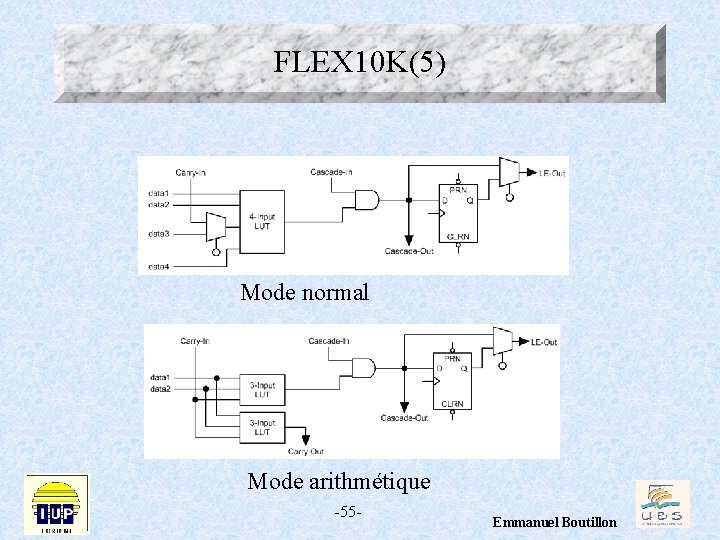

FLEX 10 K(5) Mode normal Mode arithmétique -55 - Emmanuel Boutillon

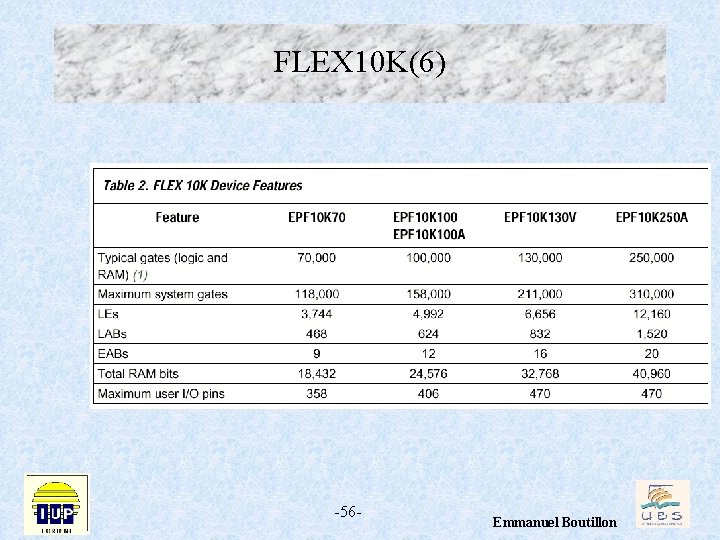

FLEX 10 K(6) -56 - Emmanuel Boutillon

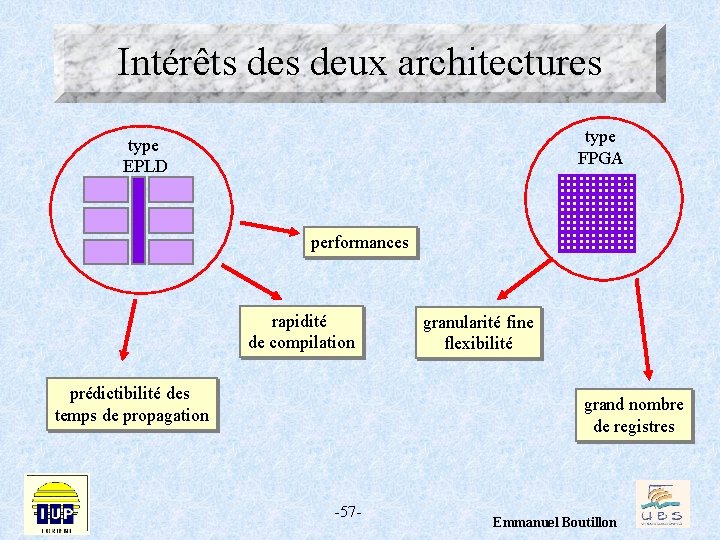

Intérêts deux architectures type FPGA type EPLD performances rapidité de compilation prédictibilité des temps de propagation granularité fine flexibilité grand nombre de registres -57 - Emmanuel Boutillon

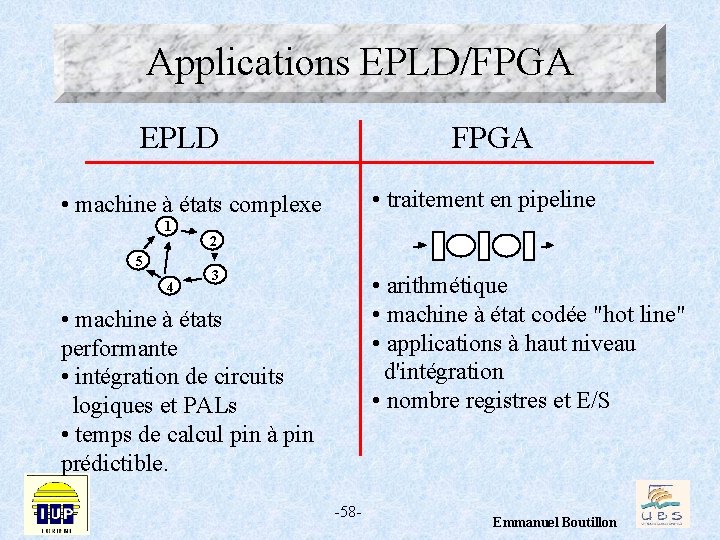

Applications EPLD/FPGA EPLD FPGA • traitement en pipeline • machine à états complexe 1 5 2 3 • arithmétique • machine à état codée "hot line" • applications à haut niveau d'intégration • nombre registres et E/S • machine à états performante • intégration de circuits logiques et PALs • temps de calcul pin à pin prédictible. 4 -58 - Emmanuel Boutillon

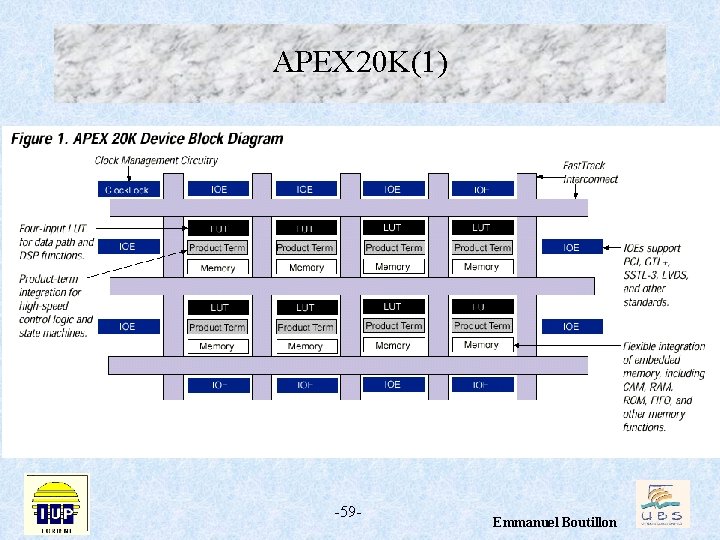

APEX 20 K(1) -59 - Emmanuel Boutillon

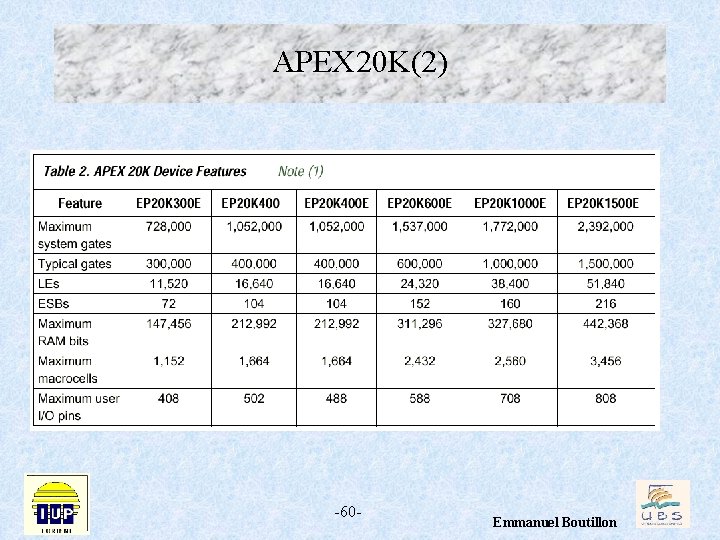

APEX 20 K(2) -60 - Emmanuel Boutillon

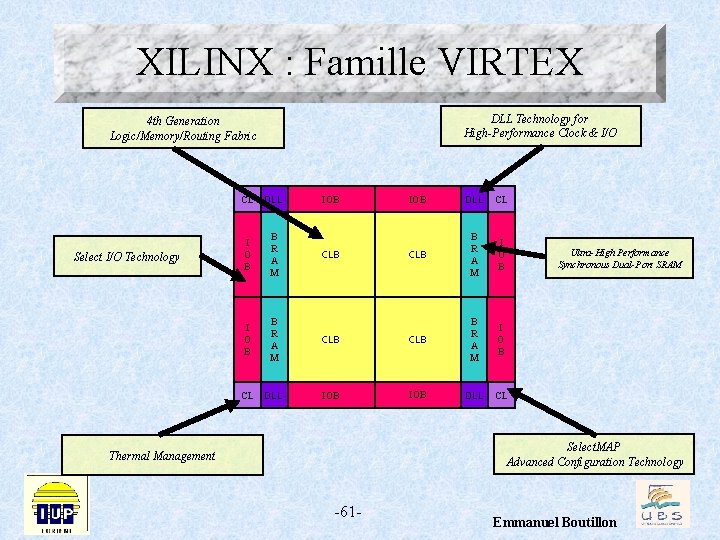

XILINX : Famille VIRTEX DLL Technology for High-Performance Clock & I/O 4 th Generation Logic/Memory/Routing Fabric Select I/O Technology CL DLL I O B B R A M CL DLL IOB DLL CL CLB B R A M I O B IOB DLL CL CLB Ultra-High Performance Synchronous Dual-Port SRAM Select. MAP Advanced Configuration Technology Thermal Management -61 - Emmanuel Boutillon

PLAN Comment et pourquoi faire de la logique programmable ? Les technologies de personnalisation PAL, EPLD et FPGA Comment choisir un FPGA Situation présente et évolution. -62 - Emmanuel Boutillon

Comment choisir un FPGA ? Caractéristiques techniques du FPGA - Performances (complexité, vitesse, conso. ) - Nombre E/S et interface - Tension d’alimentation - Boitié Qualité des softs associés au FPGA (CAO et IP) Technique de programmation (Field/In. Situ) Technique de debug et de test Critères économiques - prix, disponibilité - pérennité et flexibilité de la famille. -63 - Emmanuel Boutillon

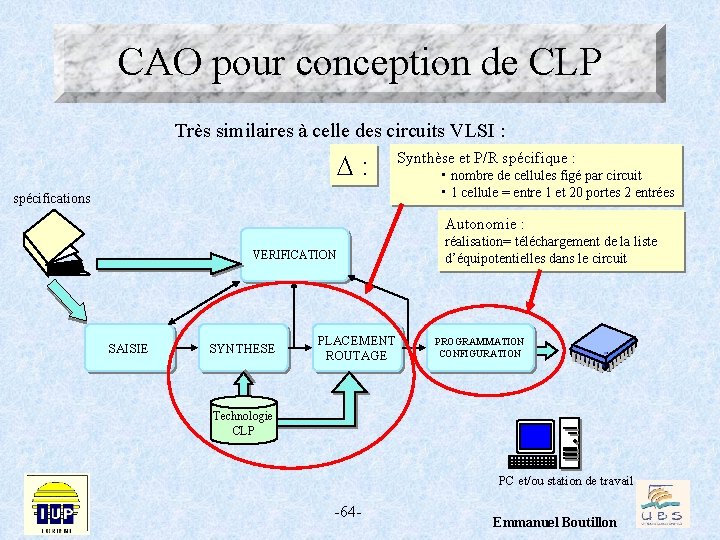

CAO pour conception de CLP Très similaires à celle des circuits VLSI : D : spécifications Synthèse et P/R spécifique : • nombre de cellules figé par circuit • 1 cellule = entre 1 et 20 portes 2 entrées Autonomie : VERIFICATION SAISIE SYNTHESE PLACEMENT ROUTAGE réalisation= téléchargement de la liste d’équipotentielles dans le circuit PROGRAMMATION CONFIGURATION Technologie CLP PC et/ou station de travail -64 - Emmanuel Boutillon

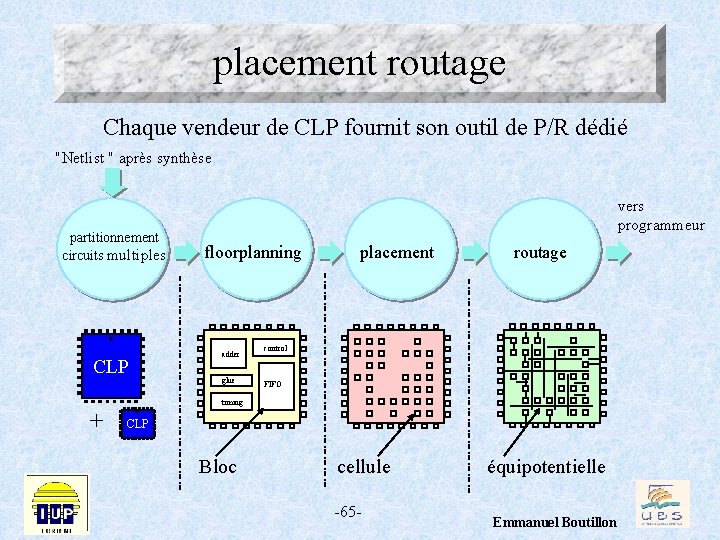

placement routage Chaque vendeur de CLP fournit son outil de P/R dédié "Netlist " après synthèse partitionnement circuits multiples CLP vers programmeur floorplanning adder glue placement routage control FIFO timing + CLP Bloc cellule -65 - équipotentielle Emmanuel Boutillon

Importance de la qualité des softs Les FPGAs deviennent très complexes et très flexibles. => L’optimisation du P/R devient très complexe => Logiciels performants Hors les logiciels de CAO pour les CLPs manquent de maturités : => très lents (24 h pour un placement routage) => peu stables (machine à rebouter) => peu efficaces et non déterministes : a) temps de propagation trop long b) en échec (pas de solution trouvée). =>il faut alors guider « à la main » le placement -66 - Emmanuel Boutillon

Synthèse sur FPGA Pour optimiser la synthèse, il faut la guider : => Directive global de compilation : Effort d ’optimisation, critères de synthèse (Vitesse vs Surface, Fan out) => Directive locale de compilation dans le texte -- « mot clef » « directive compilation » => Directive hiérarchique de compilation tel bloc, telle méthode (insertion libre de registres, méthode A). => Utilisation d ’opérateurs « optimisés par le fondeur » appels de macro-blocs additionneurs, multiplieurs, . . . paramétrables PROBLEME : Le code VHDL devient spécifique au FPGA -67 - Emmanuel Boutillon

Placement sur FPGA Problème NP-complet qui conditionne : - la possibilité de trouver une solution de routage - le chemin critique Solution : - Indiquer « à la main » le placement des blocs dans le floor plan. - Placement routage incrémental Assignation manuelle ou automatique des PAD E/S sur les entrées/sorties du composant VHDL. -68 - Emmanuel Boutillon

Intellectual Property (IP) La qualité d ’une CLPs dépend aussi des IPs disponibles pour accélérer la conception (de même que la qualité d’un système d ’exploitation dépend des logiciels existant). l l Les structures matérielles deviennent du consommable Achat ou location d ’un design paramétrable Licence ou royalties Développement et échange d’IP grâce aux langages standards -69 - Emmanuel Boutillon

IP Mega. Store: Search Engine www. altera. com/IPmegastore -70 - Emmanuel Boutillon

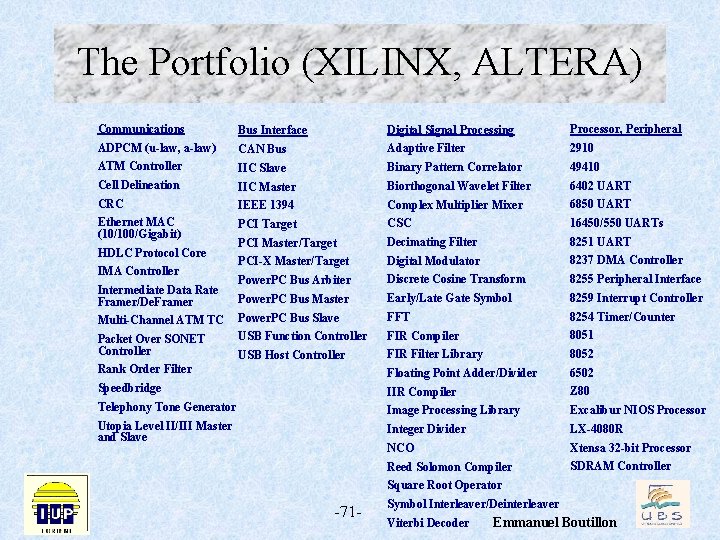

The Portfolio (XILINX, ALTERA) Communications Bus Interface Digital Signal Processing Processor, Peripheral ADPCM (u-law, a-law) CAN Bus Adaptive Filter 2910 ATM Controller IIC Slave Binary Pattern Correlator 49410 Cell Delineation IIC Master Biorthogonal Wavelet Filter 6402 UART CRC IEEE 1394 Complex Multiplier Mixer 6850 UART Ethernet MAC (10/100/Gigabit) PCI Target CSC 16450/550 UARTs PCI Master/Target Decimating Filter 8251 UART PCI-X Master/Target Digital Modulator 8237 DMA Controller Power. PC Bus Arbiter Discrete Cosine Transform 8255 Peripheral Interface Power. PC Bus Master Early/Late Gate Symbol 8259 Interrupt Controller Multi-Channel ATM TC Power. PC Bus Slave FFT 8254 Timer/Counter Packet Over SONET Controller USB Function Controller FIR Compiler 8051 USB Host Controller FIR Filter Library 8052 Rank Order Filter Floating Point Adder/Divider 6502 Speedbridge IIR Compiler Z 80 Telephony Tone Generator Image Processing Library Excalibur NIOS Processor Utopia Level II/III Master and Slave Integer Divider LX-4080 R NCO Xtensa 32 -bit Processor Reed Solomon Compiler SDRAM Controller HDLC Protocol Core IMA Controller Intermediate Data Rate Framer/De. Framer Square Root Operator -71 - Symbol Interleaver/Deinterleaver Viterbi Decoder Emmanuel Boutillon

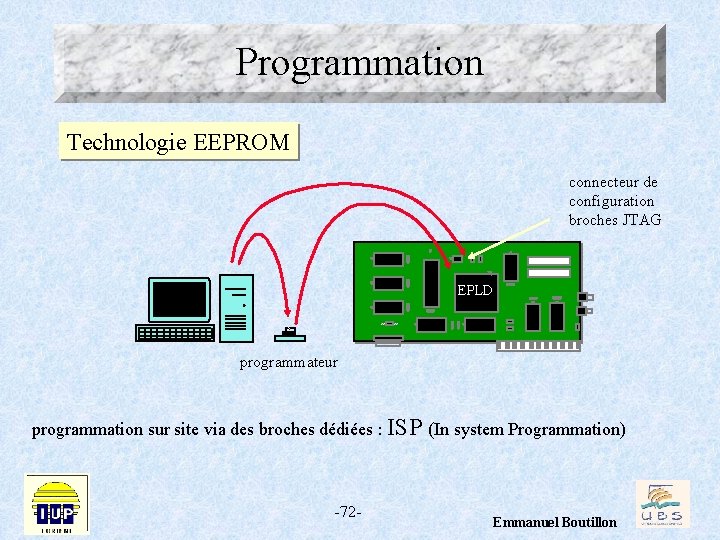

Programmation Technologie EEPROM connecteur de configuration broches JTAG EPLD programmateur programmation sur site via des broches dédiées : ISP (In system Programmation) -72 - Emmanuel Boutillon

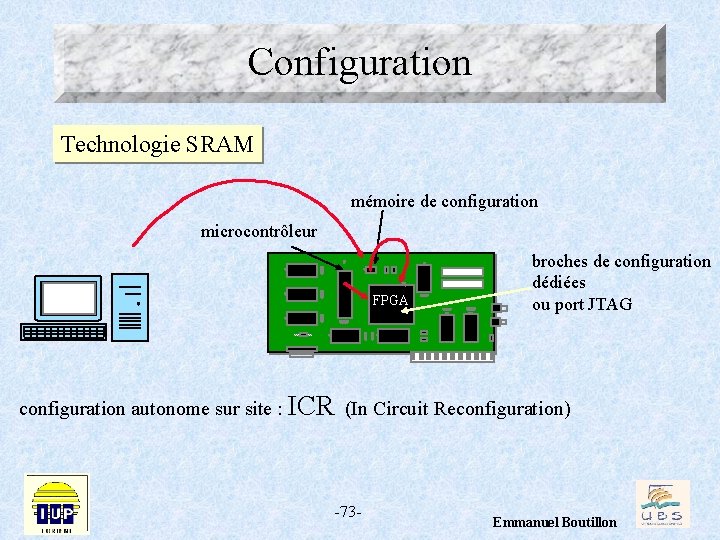

Configuration Technologie SRAM mémoire de configuration microcontrôleur FPGA CLP broches de configuration dédiées ou port JTAG configuration autonome sur site : ICR (In Circuit Reconfiguration) -73 - Emmanuel Boutillon

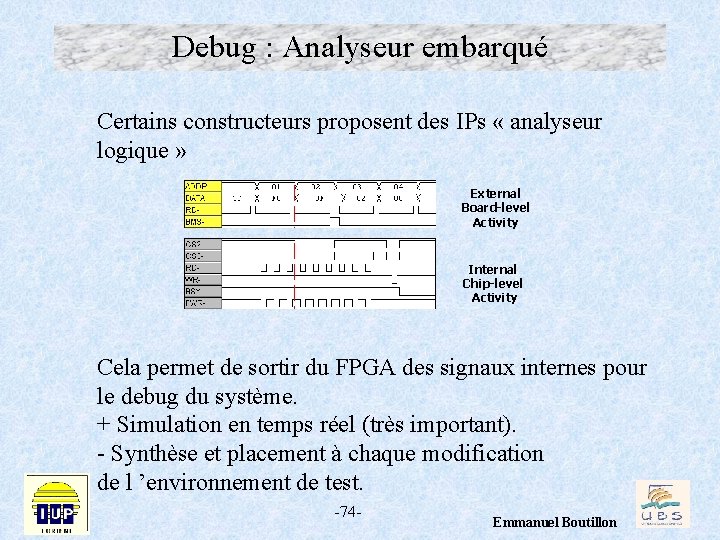

Debug : Analyseur embarqué Certains constructeurs proposent des IPs « analyseur logique » External Board-level Activity Internal Chip-level Activity Cela permet de sortir du FPGA des signaux internes pour le debug du système. + Simulation en temps réel (très important). - Synthèse et placement à chaque modification de l ’environnement de test. -74 - Emmanuel Boutillon

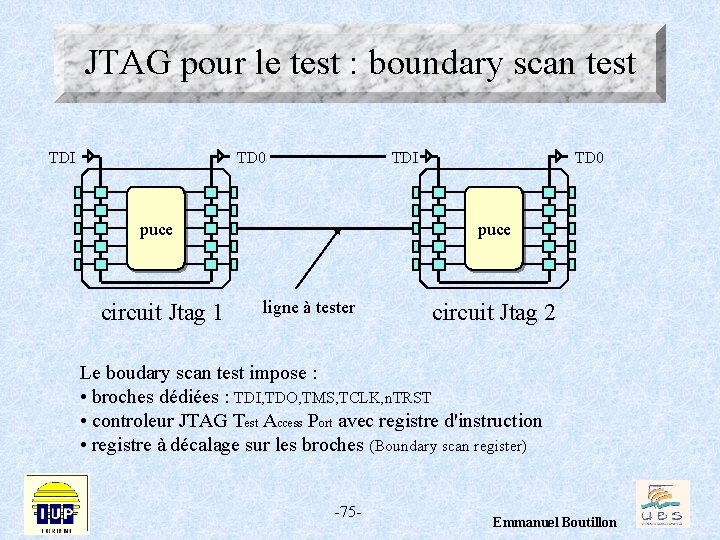

JTAG pour le test : boundary scan test TDI TD 0 TDI puce circuit Jtag 1 TD 0 puce ligne à tester circuit Jtag 2 Le boudary scan test impose : • broches dédiées : TDI, TDO, TMS, TCLK, n. TRST • controleur JTAG Test Access Port avec registre d'instruction • registre à décalage sur les broches (Boundary scan register) -75 - Emmanuel Boutillon

Critère économique Coût du composant : évidemment. . . Coût du développement : dépend de la culture de l’entreprise => Savoir faire => Réutilisation de code déjà existant => Existence ou non des logiciels de CAO (conditionne aussi le temps de développement) Coût de maintenance : => extension de la famille FPGA : nouvelle génération de produit -76 - Emmanuel Boutillon

PLAN Comment et pourquoi faire de la logique programmable ? Les technologies de personnalisation PAL, EPLD et FPGA Comment choisir un FPGA Situation présente et évolution. -77 - Emmanuel Boutillon

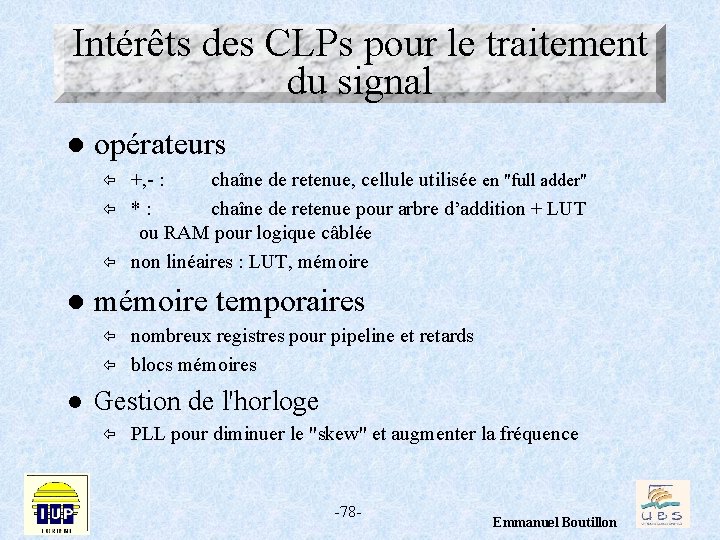

Intérêts des CLPs pour le traitement du signal l opérateurs ï ï ï l mémoire temporaires ï ï l +, - : chaîne de retenue, cellule utilisée en "full adder" * : chaîne de retenue pour arbre d’addition + LUT ou RAM pour logique câblée non linéaires : LUT, mémoire nombreux registres pour pipeline et retards blocs mémoires Gestion de l'horloge ï PLL pour diminuer le "skew" et augmenter la fréquence -78 - Emmanuel Boutillon

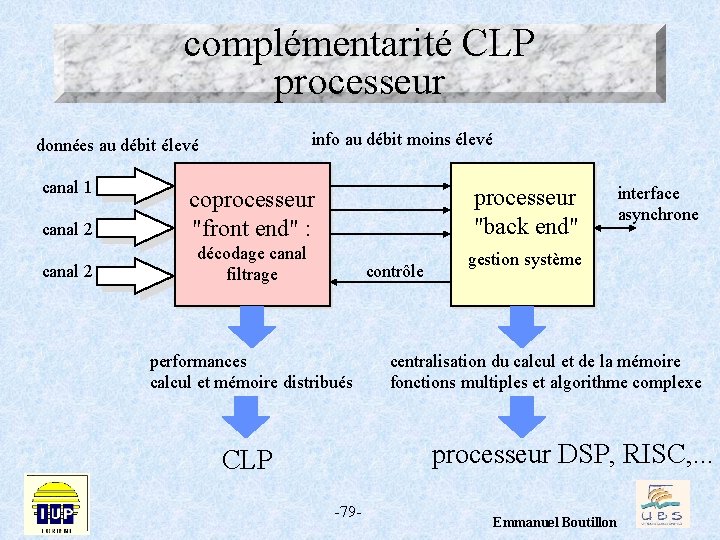

complémentarité CLP processeur info au débit moins élevé données au débit élevé canal 1 canal 2 coprocesseur "front end" : canal 2 décodage canal filtrage processeur "back end" contrôle performances calcul et mémoire distribués interface asynchrone gestion système centralisation du calcul et de la mémoire fonctions multiples et algorithme complexe processeur DSP, RISC, . . . CLP -79 - Emmanuel Boutillon

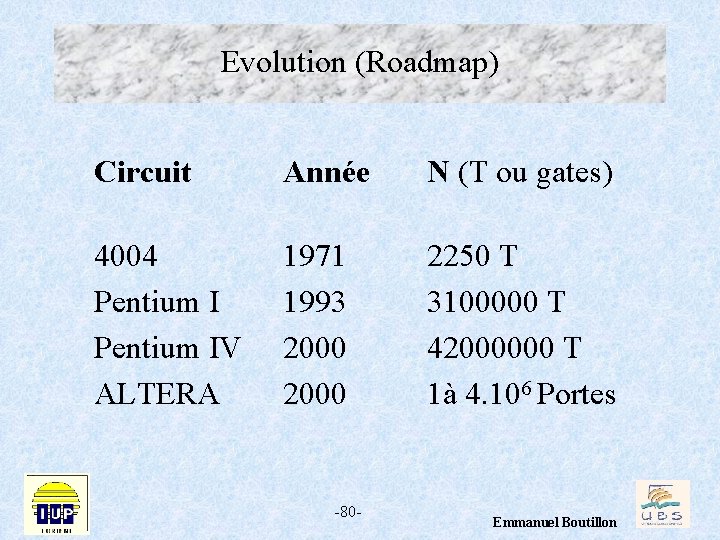

Evolution (Roadmap) Circuit Année N (T ou gates) 4004 Pentium IV ALTERA 1971 1993 2000 2250 T 3100000 T 42000000 T 1à 4. 106 Portes -80 - Emmanuel Boutillon

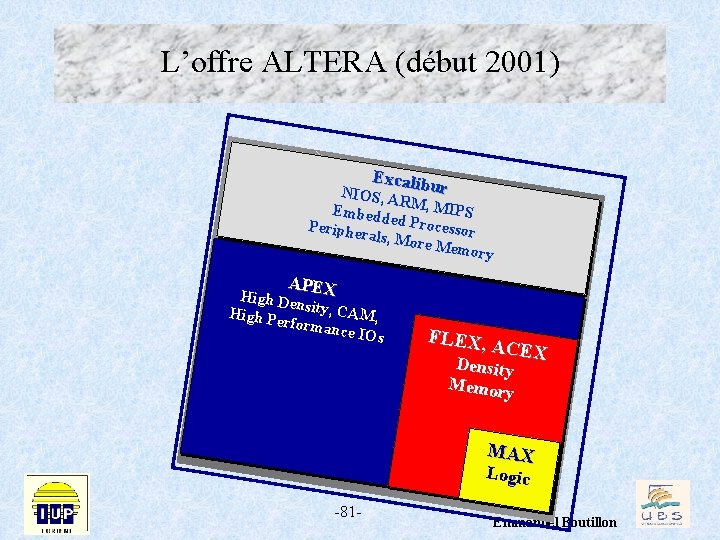

L’offre ALTERA (début 2001) Excalib ur NIOS , AR Embedd M, MIPS ed Pro Periphe rals, Mo cessor re Mem ory APE ALTERA Device. FLEDX, ACEX ensit High De EX n High Pe sity, CAM, rforman ce IOs y Memory MAX Logic -81 - Emmanuel Boutillon

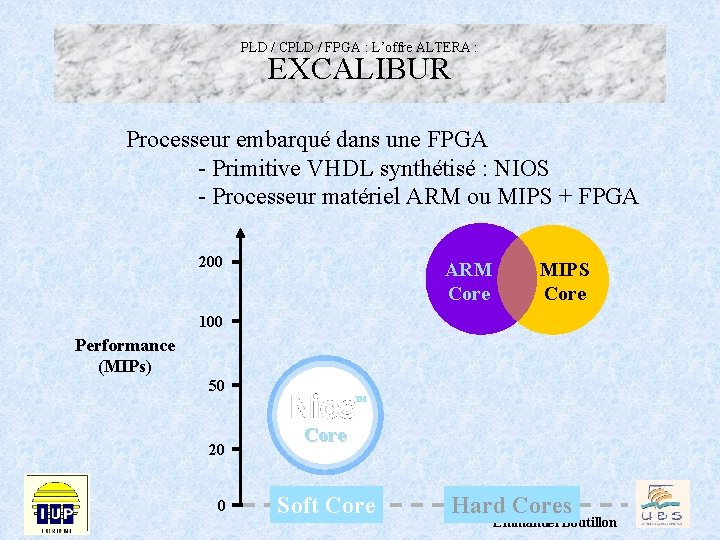

PLD / CPLD / FPGA : L’offre ALTERA : EXCALIBUR Processeur embarqué dans une FPGA - Primitive VHDL synthétisé : NIOS - Processeur matériel ARM ou MIPS + FPGA 200 ARM Core MIPS Core 100 Performance (MIPs) 50 TM 20 0 Core Soft Core -82 - Hard Cores Emmanuel Boutillon

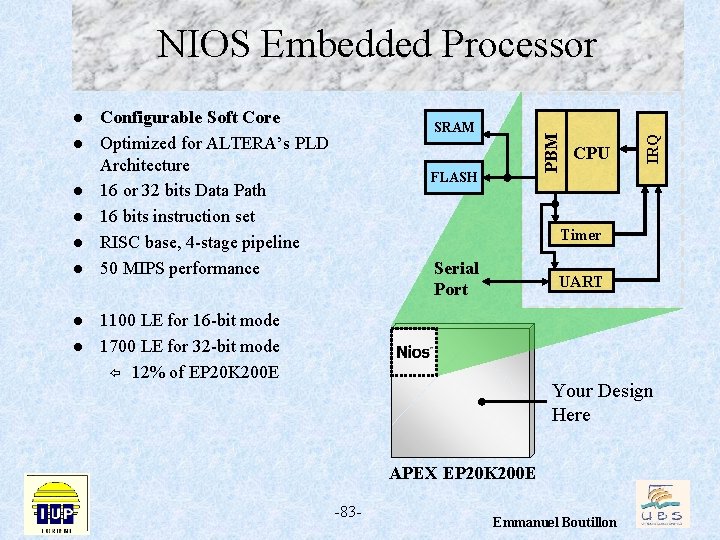

l l l l Configurable Soft Core Optimized for ALTERA’s PLD Architecture 16 or 32 bits Data Path 16 bits instruction set RISC base, 4 -stage pipeline 50 MIPS performance SRAM PBM l FLASH CPU IRQ NIOS Embedded Processor Timer Serial Port UART 1100 LE for 16 -bit mode 1700 LE for 32 -bit mode ï 12% of EP 20 K 200 E Your Design Here APEX EP 20 K 200 E -83 - Emmanuel Boutillon

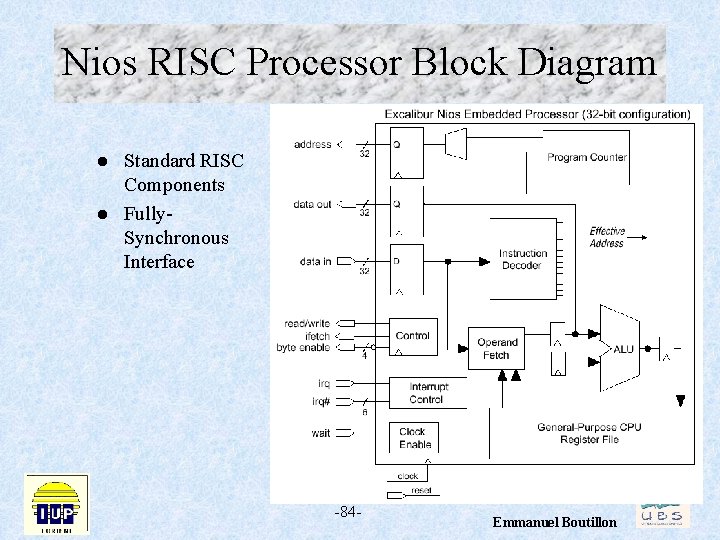

Nios RISC Processor Block Diagram l l Standard RISC Components Fully. Synchronous Interface -84 - Emmanuel Boutillon

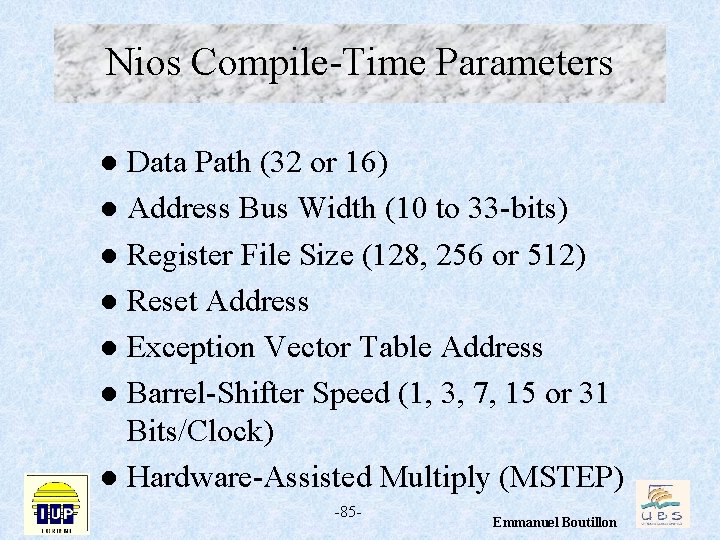

Nios Compile-Time Parameters Data Path (32 or 16) l Address Bus Width (10 to 33 -bits) l Register File Size (128, 256 or 512) l Reset Address l Exception Vector Table Address l Barrel-Shifter Speed (1, 3, 7, 15 or 31 Bits/Clock) l Hardware-Assisted Multiply (MSTEP) l -85 - Emmanuel Boutillon

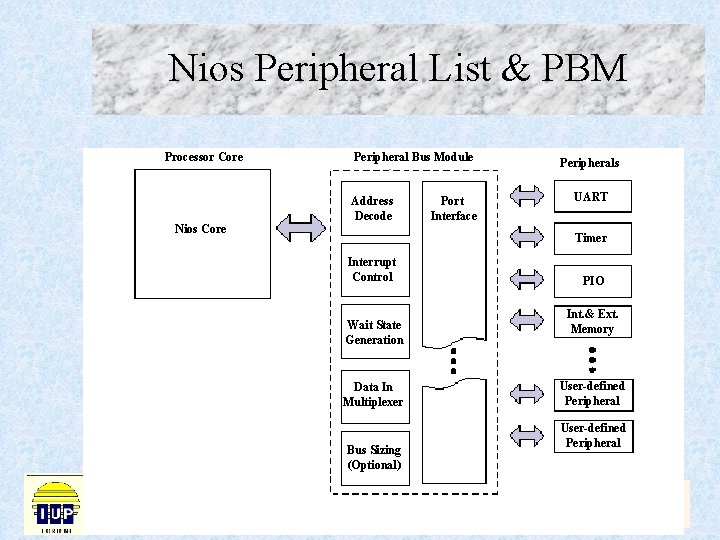

Nios Peripheral List & PBM Processor Core Nios Core Peripheral Bus Module Address Decode Port Interface Peripherals UART Timer Interrupt Control Wait State Generation Data In Multiplexer Bus Sizing (Optional) -86 - PIO Int. & Ext. Memory User-defined Peripheral Emmanuel Boutillon

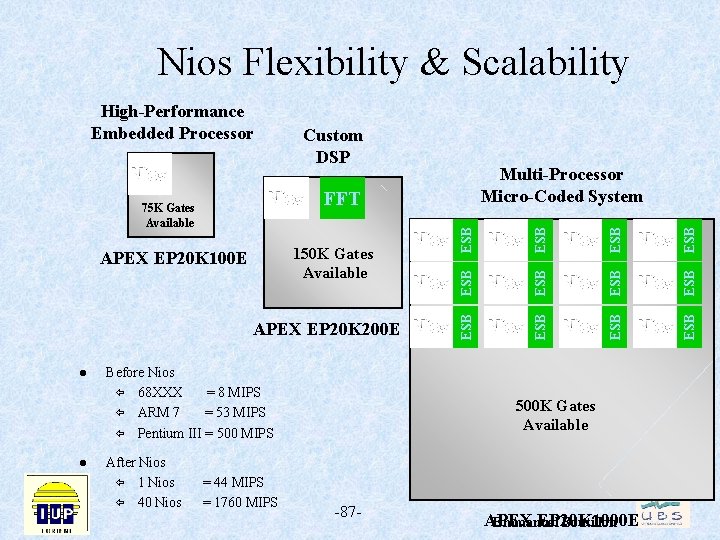

Nios Flexibility & Scalability Custom DSP l Before Nios ï 68 XXX = 8 MIPS ï ARM 7 = 53 MIPS ï Pentium III = 500 MIPS After Nios ï 1 Nios = 44 MIPS ï 40 Nios = 1760 MIPS 500 K Gates Available -87 - ESB ESB ESB APEX EP 20 K 200 E ESB 150 K Gates Available APEX EP 20 K 100 E ESB FFT 75 K Gates Available l Multi-Processor Micro-Coded System ESB High-Performance Embedded Processor APEX EP 20 K 1000 E Emmanuel Boutillon

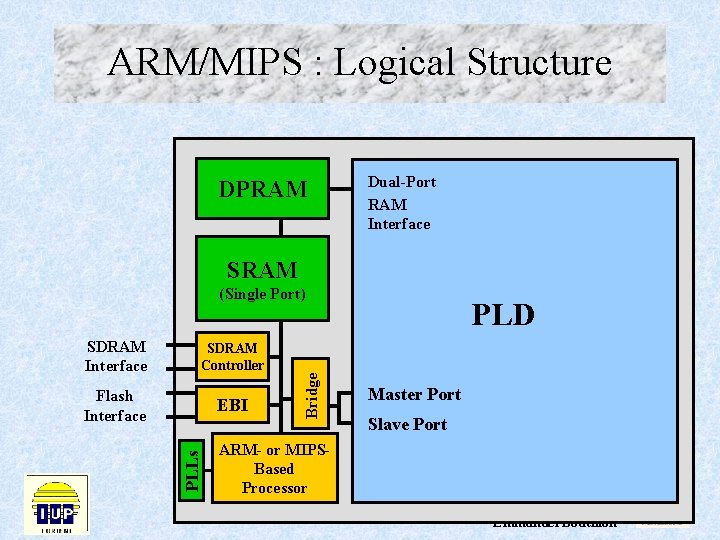

ARM/MIPS : Logical Structure Dual-Port RAM Interface DPRAM SRAM (Single Port) Flash Interface EBI Bridge SDRAM Controller PLLs SDRAM Interface PLD Master Port Slave Port ARM- or MIPSBased Processor -88 - Emmanuel Boutillon

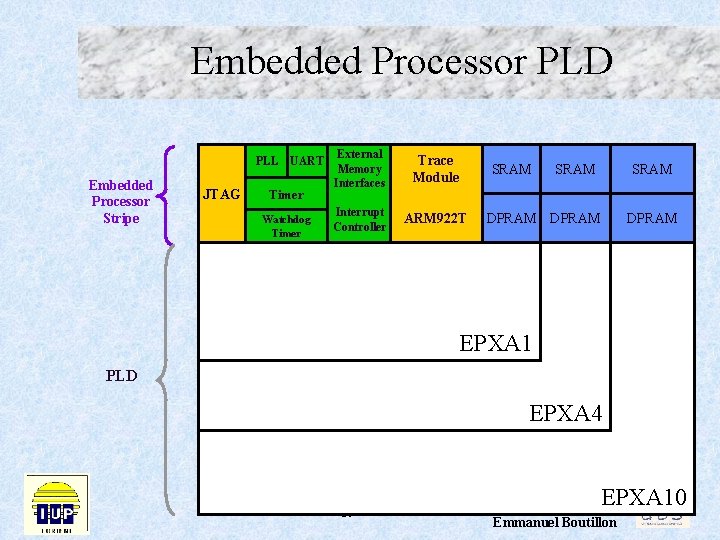

Embedded Processor PLD PLL UART Embedded Processor Stripe JTAG Timer Watchdog Timer External Memory Interfaces Trace Module SRAM Interrupt Controller ARM 922 T DPRAM EPXA 1 PLD EPXA 4 -89 - EPXA 10 Emmanuel Boutillon

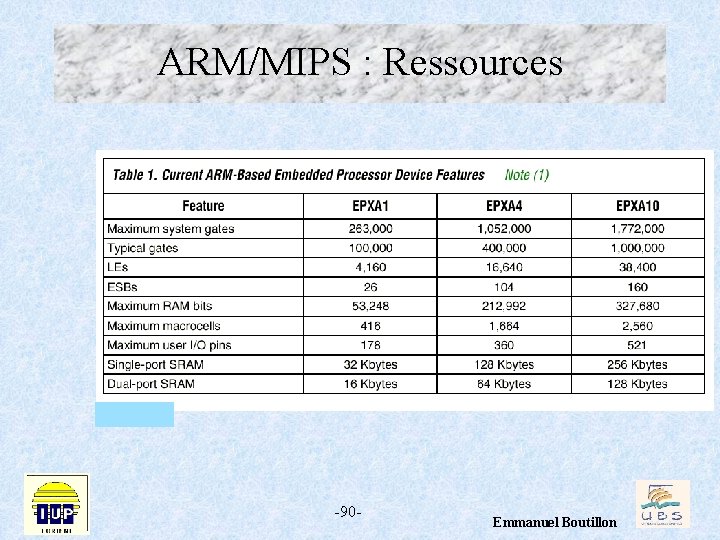

ARM/MIPS : Ressources -90 - Emmanuel Boutillon

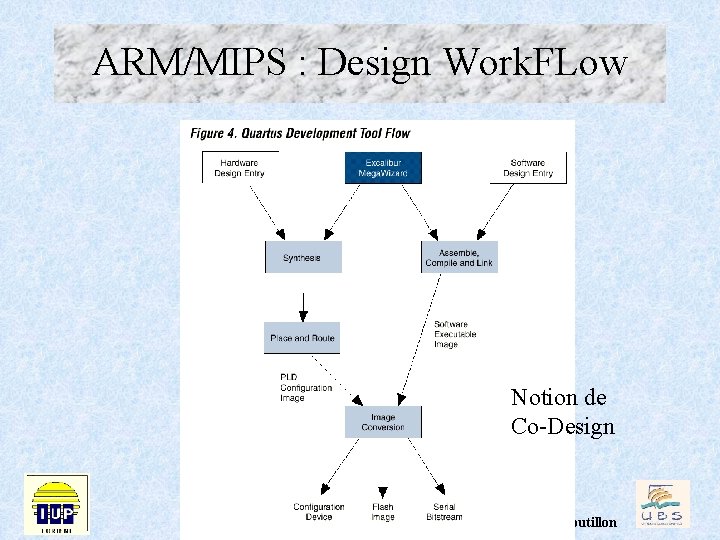

ARM/MIPS : Design Work. FLow Notion de Co-Design -91 - Emmanuel Boutillon

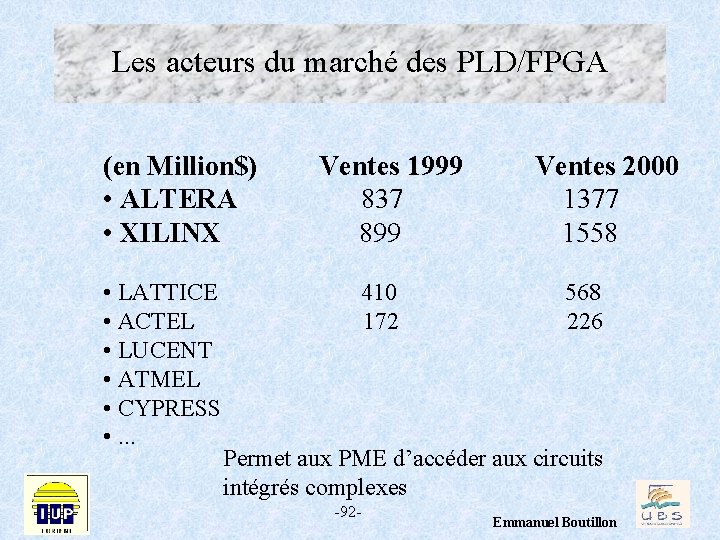

Les acteurs du marché des PLD/FPGA (en Million$) • ALTERA • XILINX Ventes 1999 Ventes 2000 837 1377 899 1558 • LATTICE 410 568 • ACTEL 172 226 • LUCENT • ATMEL • CYPRESS • . . . Permet aux PME d’accéder aux circuits intégrés complexes -92 - Emmanuel Boutillon

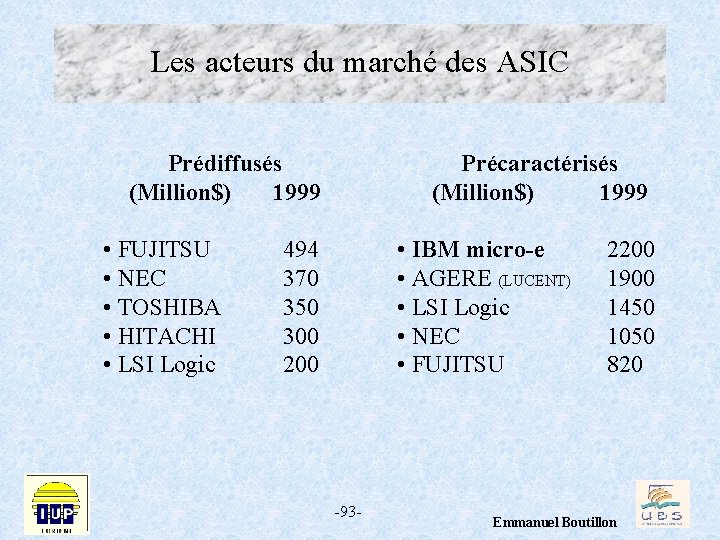

Les acteurs du marché des ASIC Prédiffusés (Million$) 1999 • FUJITSU • NEC • TOSHIBA • HITACHI • LSI Logic Précaractérisés (Million$) 1999 • IBM micro-e 2200 • AGERE (LUCENT) 1900 • LSI Logic 1450 • NEC 1050 • FUJITSU 820 494 370 350 300 200 -93 - Emmanuel Boutillon

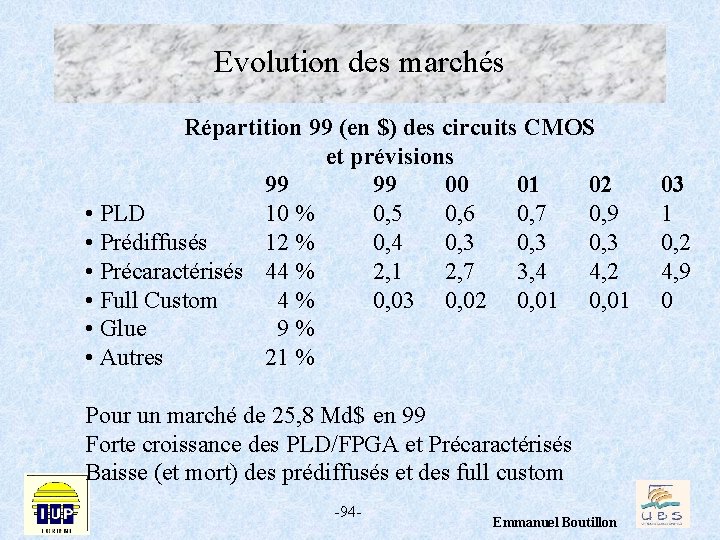

Evolution des marchés Répartition 99 (en $) des circuits CMOS et prévisions 99 99 00 01 02 • PLD 10 % 0, 5 0, 6 0, 7 0, 9 • Prédiffusés 12 % 0, 4 0, 3 • Précaractérisés 44 % 2, 1 2, 7 3, 4 4, 2 • Full Custom 4 % 0, 03 0, 02 0, 01 • Glue 9 % • Autres 21 % Pour un marché de 25, 8 Md$ en 99 Forte croissance des PLD/FPGA et Précaractérisés Baisse (et mort) des prédiffusés et des full custom -94 - Emmanuel Boutillon 03 1 0, 2 4, 9 0

Le futur (1) FPGA avec Processeur … ou Processeur avec zone de FPGA ? FPGA reconfigurable dynamiquement : - de façon déterministe (filtre A puis B sur image). - de façon dynamique en fonction des données… => Problèmes de recherche qui débutent. - software radio : la configuration est télé-chargée , - partitionnement logiciel-matériel - prouver que cela marche. . . -95 - Emmanuel Boutillon

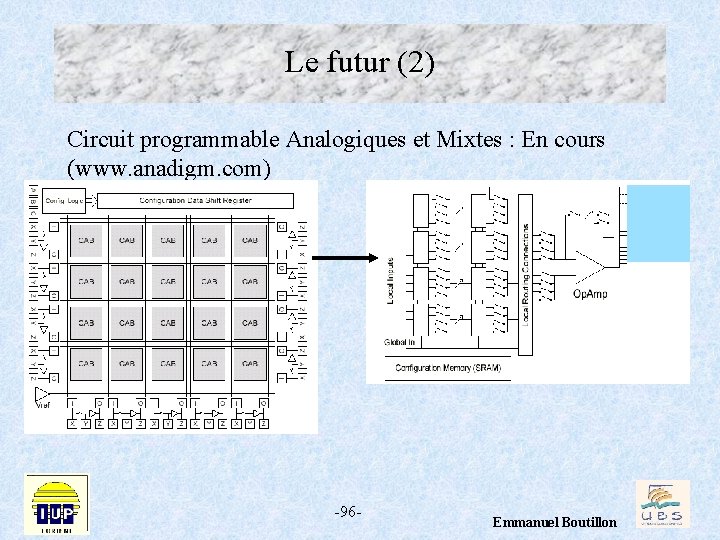

Le futur (2) Circuit programmable Analogiques et Mixtes : En cours (www. anadigm. com) -96 - Emmanuel Boutillon

- Slides: 96