Les FPGA Field Programmable Gate Array Circuit intgr

Les FPGA « Field Programmable Gate Array » - Circuit intégré contenant un très grand nombre de portes logiques organisées en blocs logiques configurables et interconnectables « Programmer » un fpga = Configurer et interconnecter des blocs logiques = « Câblage » sur silicium

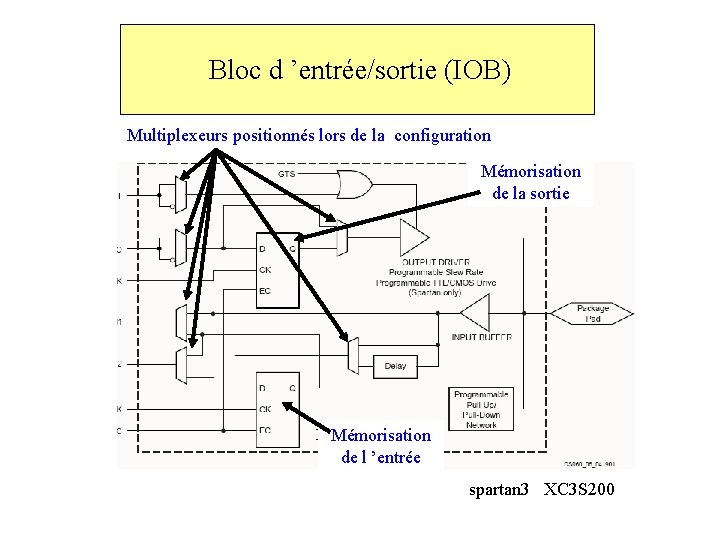

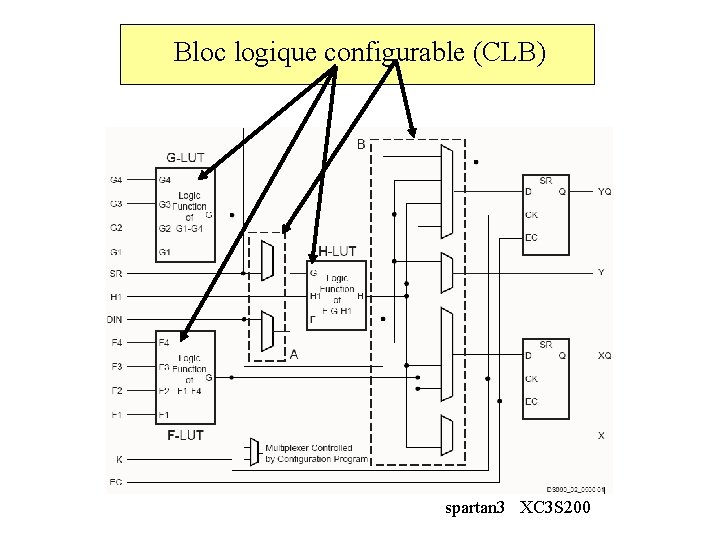

Architecture des FPGA – Blocs d ’entrées/sorties « IOB » configurables • Entrée, sortie ou les deux, mémorisation dans une bascule D • niveaux logiques LVTTL, LVCMOS, … 3. 3 V, 2. 5 V, … • pull-up ou pull-down interne sur les entrées – Blocs logiques « CLB » configurables • Blocs combinatoires 4 entrées une sortie (en général) • Bascules D pour la mémorisation – Lignes d ’interconnexions « PSM » configurables • lignes courtes • lignes longues – Options : multiplicateurs , sram, etc…

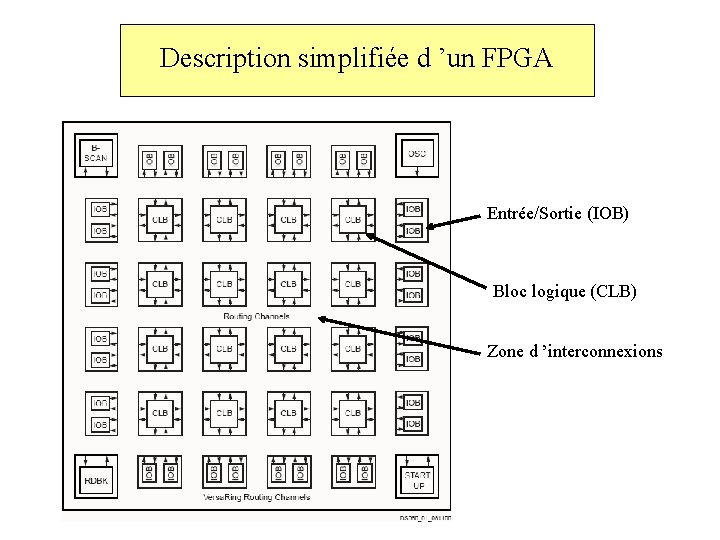

Description simplifiée d ’un FPGA Entrée/Sortie (IOB) Bloc logique (CLB) Zone d ’interconnexions

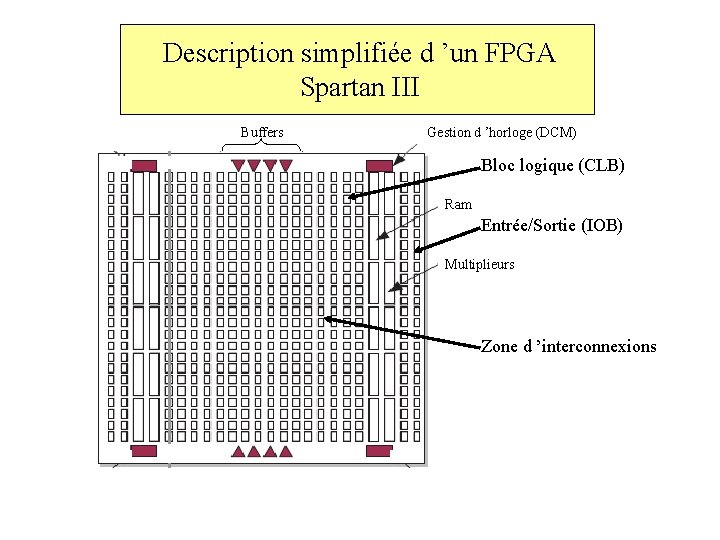

Description simplifiée d ’un FPGA Spartan III Buffers Gestion d ’horloge (DCM) Bloc logique (CLB) Ram Entrée/Sortie (IOB) Multiplieurs Zone d ’interconnexions

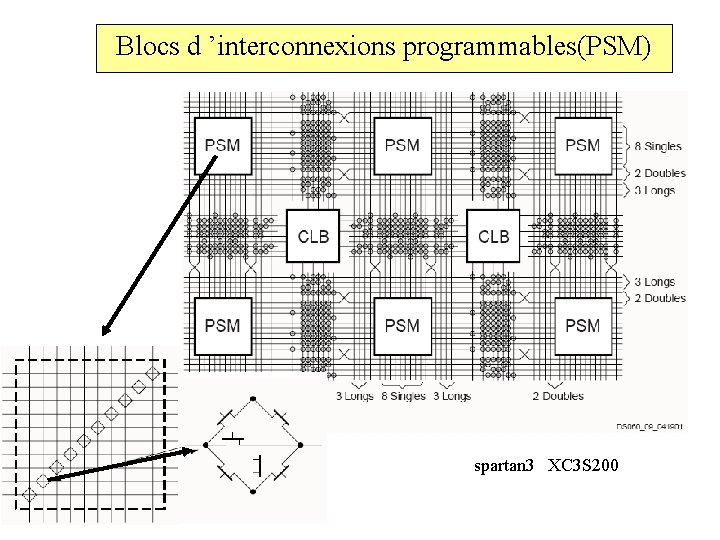

Blocs d ’interconnexions programmables(PSM) spartan 3 XC 3 S 200

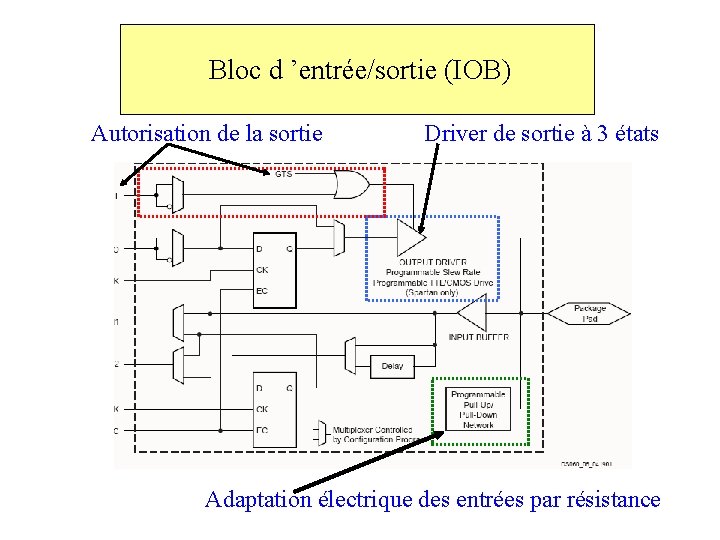

Bloc d ’entrée/sortie (IOB) Multiplexeurs positionnés lors de la configuration Mémorisation de la sortie Mémorisation de l ’entrée spartan 3 XC 3 S 200

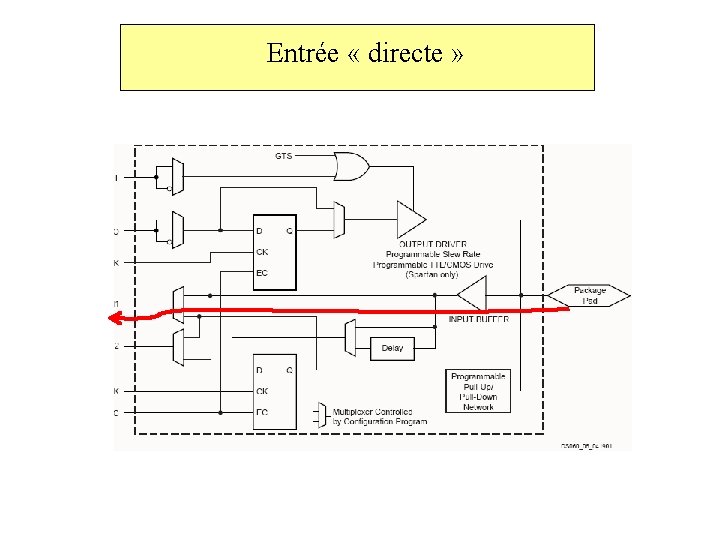

Entrée « directe »

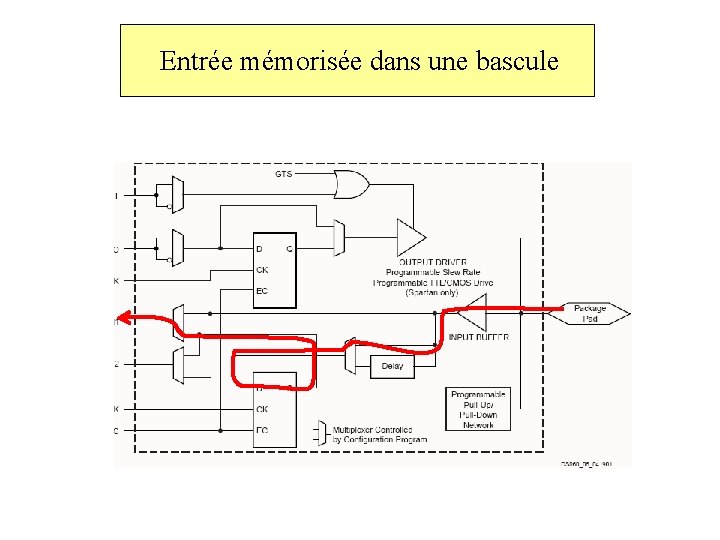

Entrée mémorisée dans une bascule

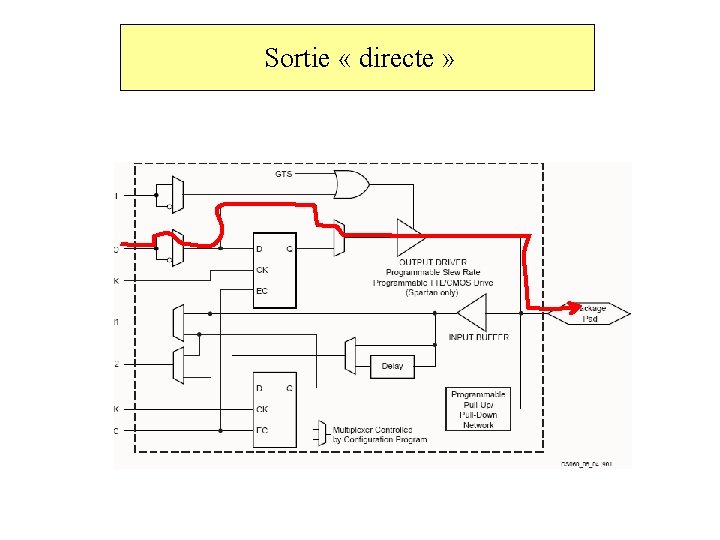

Sortie « directe »

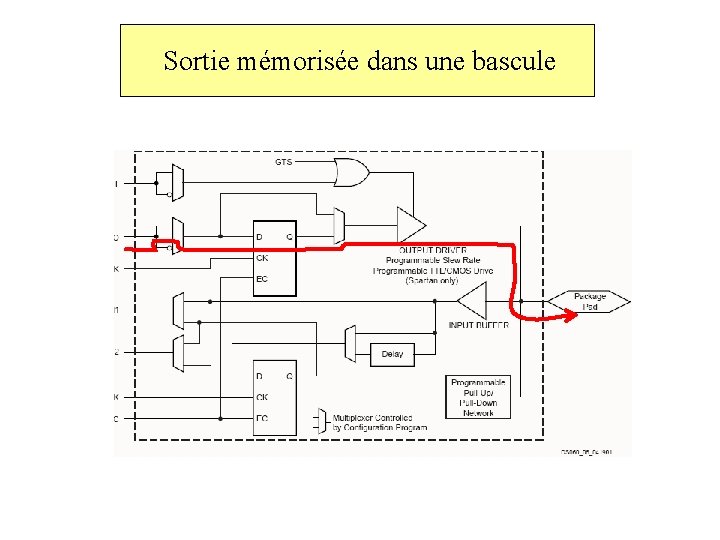

Sortie mémorisée dans une bascule

Bloc d ’entrée/sortie (IOB) Autorisation de la sortie Driver de sortie à 3 états Adaptation électrique des entrées par résistance

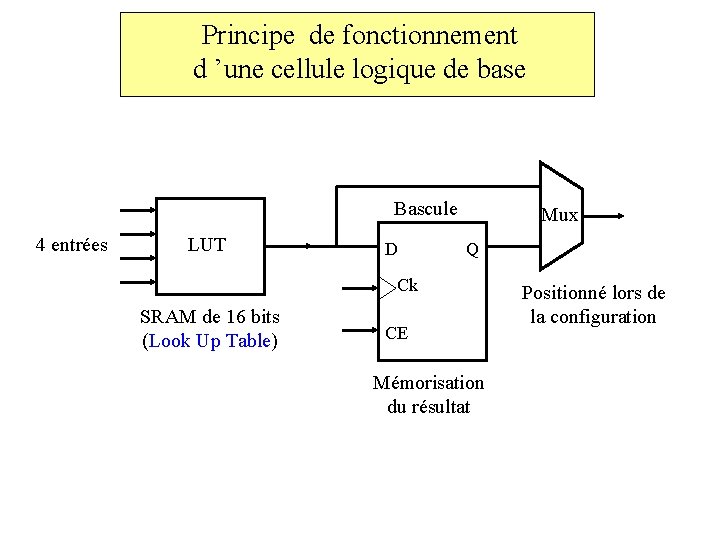

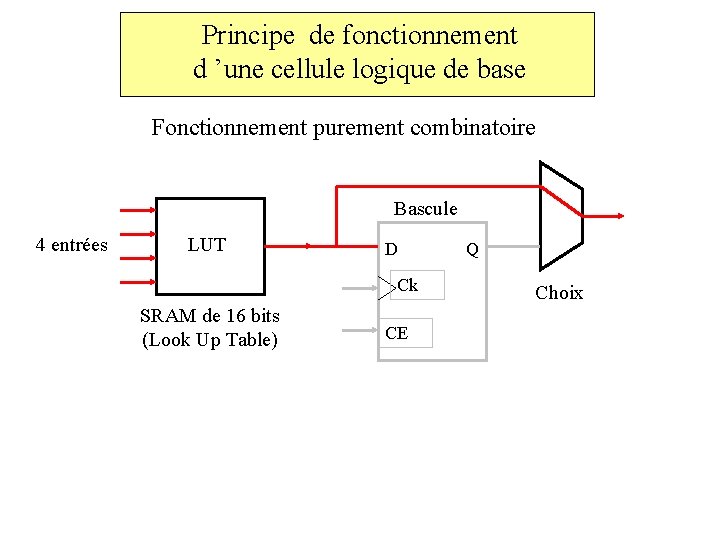

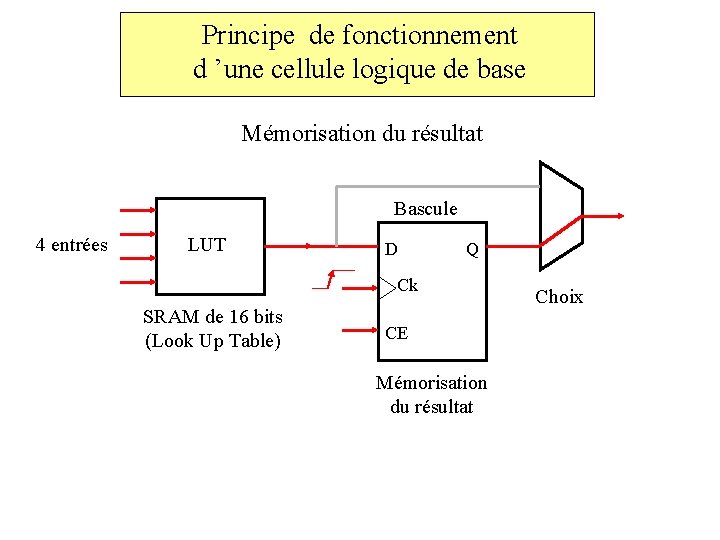

Principe de fonctionnement d ’une cellule logique de base Bascule 4 entrées LUT D Q Ck SRAM de 16 bits (Look Up Table) Mux CE Mémorisation du résultat Positionné lors de la configuration

Principe de fonctionnement d ’une cellule logique de base Fonctionnement purement combinatoire Bascule 4 entrées LUT D Q Ck SRAM de 16 bits (Look Up Table) CE Choix

Principe de fonctionnement d ’une cellule logique de base Mémorisation du résultat Bascule 4 entrées LUT D Q Ck SRAM de 16 bits (Look Up Table) CE Mémorisation du résultat Choix

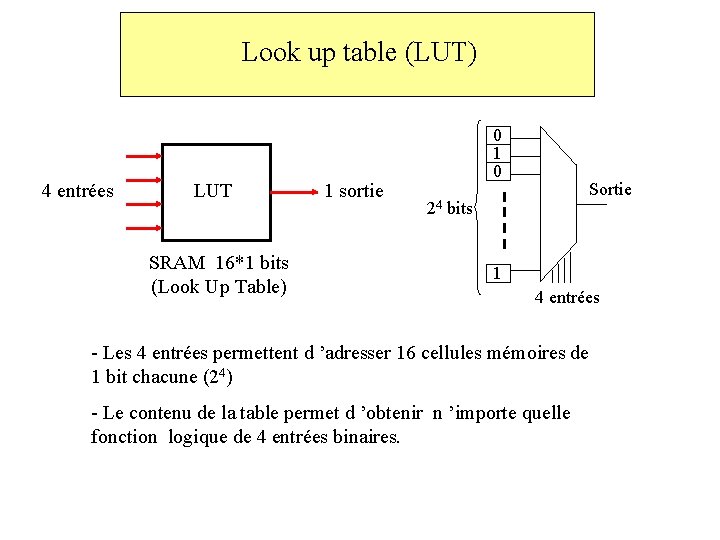

Look up table (LUT) 4 entrées LUT SRAM 16*1 bits (Look Up Table) 1 sortie 0 1 0 Sortie 24 bits 1 4 entrées - Les 4 entrées permettent d ’adresser 16 cellules mémoires de 1 bit chacune (24) - Le contenu de la table permet d ’obtenir n ’importe quelle fonction logique de 4 entrées binaires.

Bloc logique configurable (CLB) spartan 3 XC 3 S 200

Horloges • Des entrées spécialisées sont prévues pour recevoir les signaux d'horloge et les distribuer à l'intérieur du circuit • les DCM (Digital Clock Managers) sont des blocs internes pour la gestion du signal d'horloge: • Ils génèrent d'autres fréquences d'horloge et des déphasages à partir du signal d ’horloge externe, en éliminant le « jitter » • Les DCM sont basés sur des PLL (phase-locked loops)

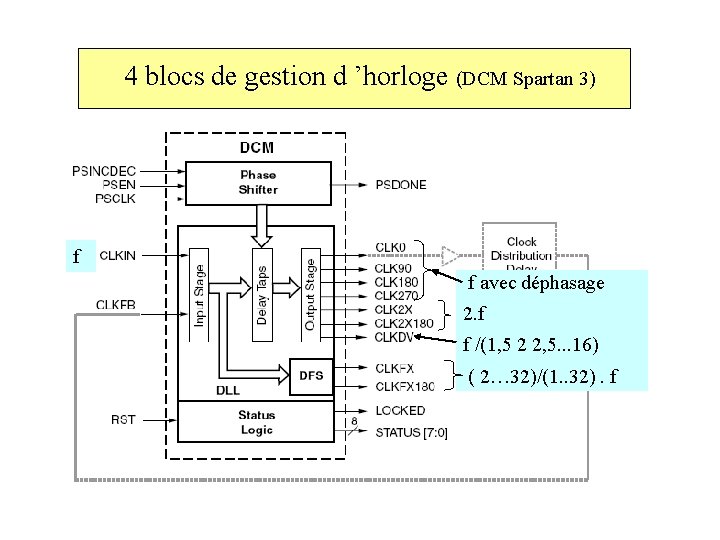

4 blocs de gestion d ’horloge (DCM Spartan 3) f f avec déphasage 2. f f /(1, 5 2 2, 5. . . 16) ( 2… 32)/(1. . 32). f

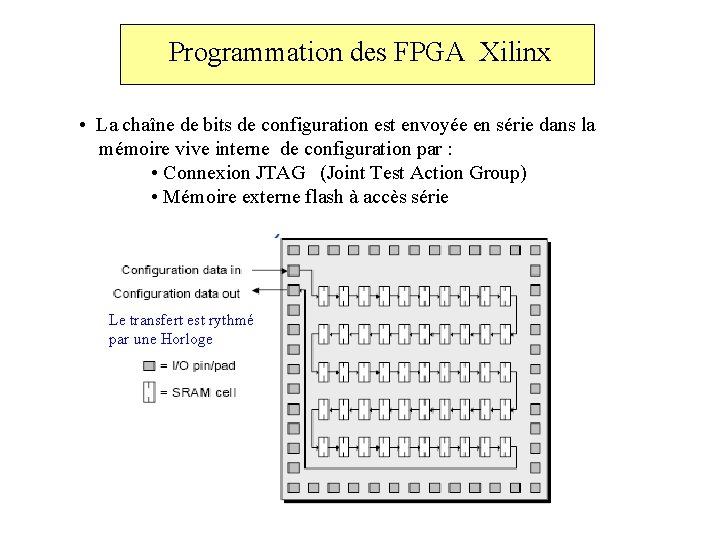

Programmation des FPGA Xilinx • La chaîne de bits de configuration est envoyée en série dans la mémoire vive interne de configuration par : • Connexion JTAG (Joint Test Action Group) • Mémoire externe flash à accès série Le transfert est rythmé par une Horloge

Outils logiciels génériques • Synario, Synopsis, Mentor, View. Logic, ASYL, CADENCE, , … Avantages: – un seul apprentissage pour tous les composants – permet une conception détachée du composant cible… Inconvénients : – toujours un peu en retard sur les derniers composants sortis – plus chers – Le P/R constructeur est nécessaire

Outils logiciels spécifiques • Ne permettent que le développement des composants du constructeurs • Ex : Actel Logiciel Designer, Altera Max. Plus. II, AMD Mach XL, Lattice Isp. Design. EXPERT, Xilinx ISE… • Avantages : – ils optimisent au mieux la synthèse pour le composant ciblé – toujours à jour sur le dernier composant • Inconvénients : – ils nécessitent un apprentissage à refaire si on souhaite changer de constructeur

Projet FPGA Conception « Top-Down » • Décomposer le circuit principal en blocs fonctionnels simples interconnectés. Un bloc fonctionnel complexe peut, à son tour, être décomposé en éléments plus simples…etc. . . Réalisation « Bottom-up » • Mettre au point chacun des blocs fonctionnels séparément • Regrouper les blocs et tester le fonctionnement global

Les interfaces de saisie • Schéma électronique: On place et on relie des composants Le fichier HDL est créé automatiquement • Saisie en mode texte en VHDL ( Verilog, Abel…) Description structurelle Description comportementale Génération du composant pour la saisie schématique • Autre : Saisie graphique de diagramme d ’états

La synthèse logique • Traduit en «blocs logiques élémentaires interconnectés » les fichiers du projet. • L ’utilisateur peut agir sur la façon dont la synthèse s ’effectue. Par exemple : Codage « one-hot » ou binaire pour les machines séquentielles. . . • Le résultat de la synthèse peut être affiché sous forme : - classique ne tenant pas compte de l ’architecture du FPGA - ou de schémas adapté à l ’architecture du FPGA

La simulation fonctionnelle • Simule le fonctionnement du circuit avant son implantation • Utile pour détecter des erreurs de conception • Ne tient pas compte des contraintes et aléa de fonctionnement liées au composant ciblé: • fréquences maximales d ’horloge • possibilités de routage • ressources insuffisantes • temps de transfert réel dans les circuits logiques • …etc. . .

Le placement - routage • Implante le circuit dans le composant cible • Affecte les pattes d ’entrées/sorties • Mode d ’optimisation (en surface ou en vitesse) • Génère le fichier de configuration à télécharger dans la cible • Produit un rapport avec les ressources utilisées et les temps de propagation de broche à broche.

La simulation « post-routage » • La simulation tient compte de l ’implantation dans le composant. • Elle permet de vérifier si le circuit répond au cahier des charges

Chargement dans la cible • Directement par l ’interface JTAG dans la mémoire SRAM de configuration • Indirectement : • Le fichier est tout d ’abord stocké dans une mémoire flash à accès série externe (ou interne). • A la mise sous tension du FPGA il y a recopie de la mémoire flash vers la SRAM de configuration

Tests sur la cible • On effectue des tests avec des signaux réels sur la cible pour valider le circuit créé. • L ’interface JTAG est utile pour sonder l ’état logique des broches du circuit en fonctionnement

Les TP sur FPGA Spartan 3 xc 3 s 200 • Prise en main de outils Xilinx : • en VHDL (TP 1) • en mode schéma (TP 2) • Utilisation de « cœurs configurables » (core IP) et des bibliothèques de symboles (TP 3) • Mise en évidence des performances d ’une architecture distribuée (parallèle) avec la réalisation d ’un filtre passe-bande numérique (TP 4) • Mise en place d’un cœur microprocesseur (TP 5)

Les documents utiles • Description de la carte de développement UG 130. pdf • Manuel de référence VHDL (synopsys) VHDLman. pdf • Tutorial rapide (Xilinx) qst. pdf • Tutorial complet (Xilinx) ise 8. 2 tut. pdf • Datasheet du spartan 3 (Xilinx) ds 099. pdf • Documentation des librairies (Xilinx) s 3 esc. pdf et s 3 ehl. pdf

- Slides: 31