LEON 3 Products Advantages Solutions 2005 GEResearch LEON

- Slides: 12

LEON 3 Products · Advantages · Solutions © 2005 GE-Research LEON 3 V 0105 dsr With explicit permission of Gaisler Research

COMPANY INFORMATION Gaisler Research • Located in Gothenburg, Sweden • Private Company • Management team with 40 years combined experience in the space sector: – Per Danielsson: CEO – Jiri Gaisler: Founder and CTO – Sandi Habinc: System Design • Design engineers with expertise within electronics, ASIC and software design • Complete design facilities in-house for ASIC and FPGA design LEON 3 V 0105 dsr 2

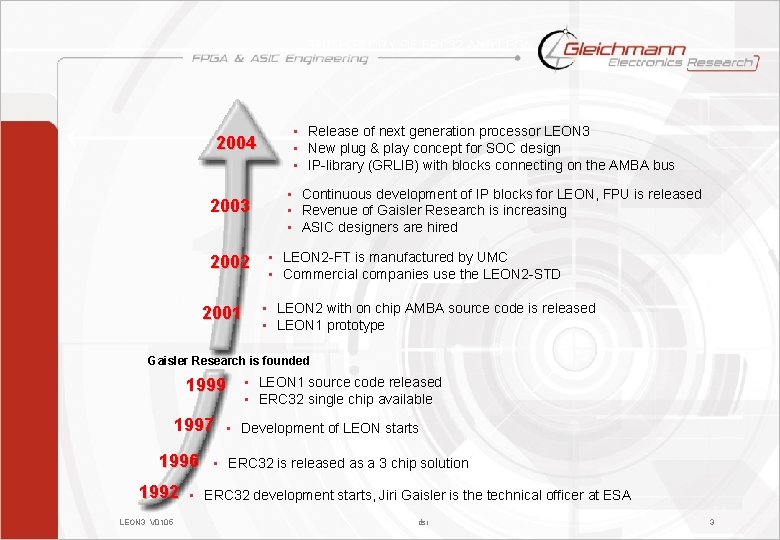

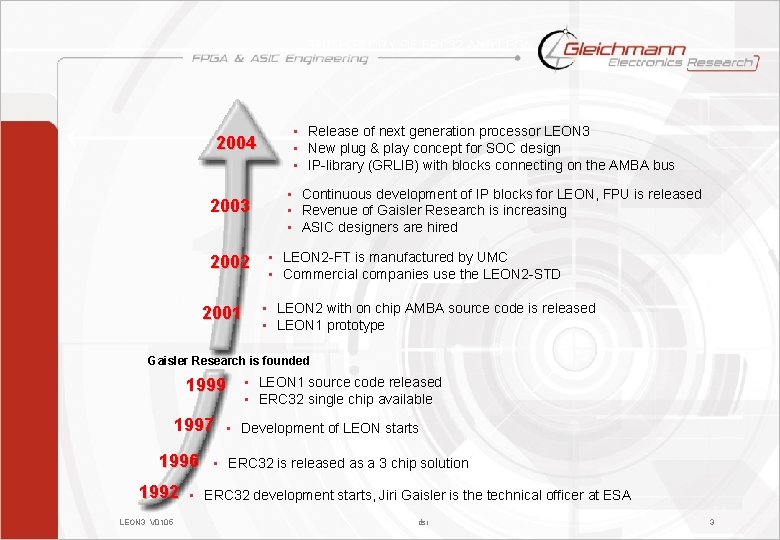

THE HISTORY OF ERC 32 AND LEON • Release of next generation processor LEON 3 • New plug & play concept for SOC design • IP-library (GRLIB) with blocks connecting on the AMBA bus 2004 • Continuous development of IP blocks for LEON, FPU is released • Revenue of Gaisler Research is increasing • ASIC designers are hired 2003 2002 • LEON 2 -FT is manufactured by UMC • Commercial companies use the LEON 2 -STD • LEON 2 with on chip AMBA source code is released • LEON 1 prototype 2001 Gaisler Research is founded 1999 • LEON 1 source code released • ERC 32 single chip available 1997 • 1996 • 1992 • LEON 3 V 0105 Development of LEON starts ERC 32 is released as a 3 chip solution ERC 32 development starts, Jiri Gaisler is the technical officer at ESA dsr 3

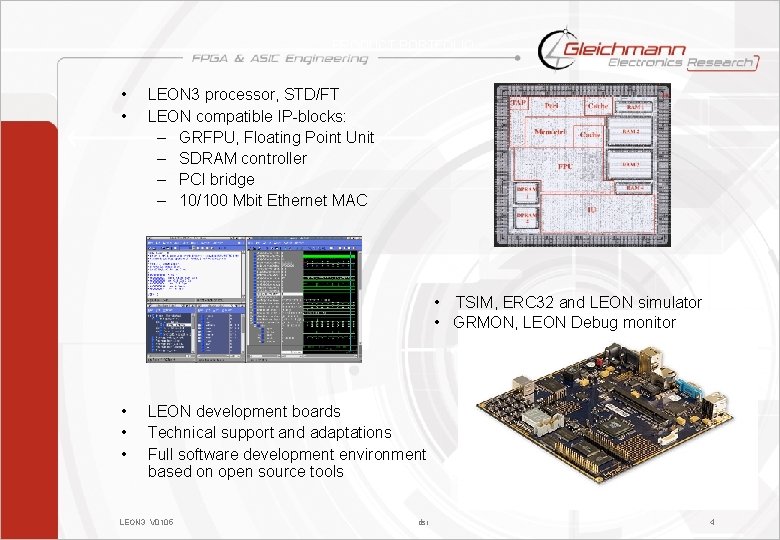

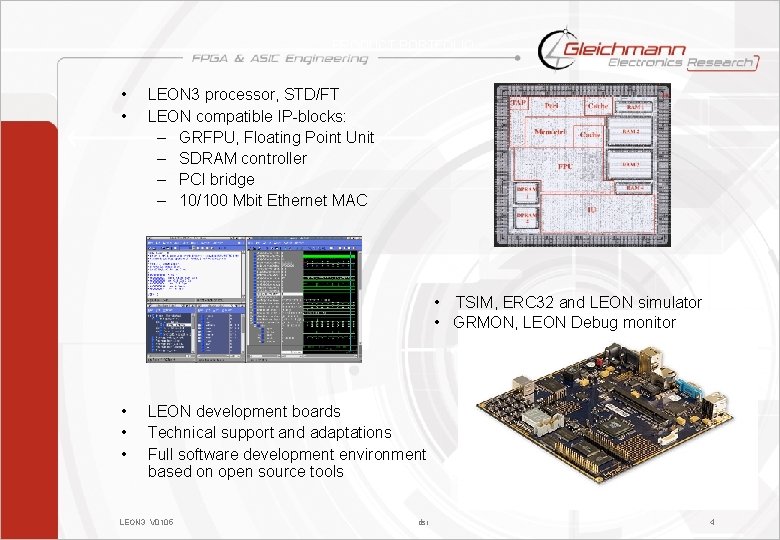

PRODUCT PORTFOLIO • • LEON 3 processor, STD/FT LEON compatible IP-blocks: – GRFPU, Floating Point Unit – SDRAM controller – PCI bridge – 10/100 Mbit Ethernet MAC • TSIM, ERC 32 and LEON simulator • GRMON, LEON Debug monitor • • • LEON development boards Technical support and adaptations Full software development environment based on open source tools LEON 3 V 0105 dsr 4

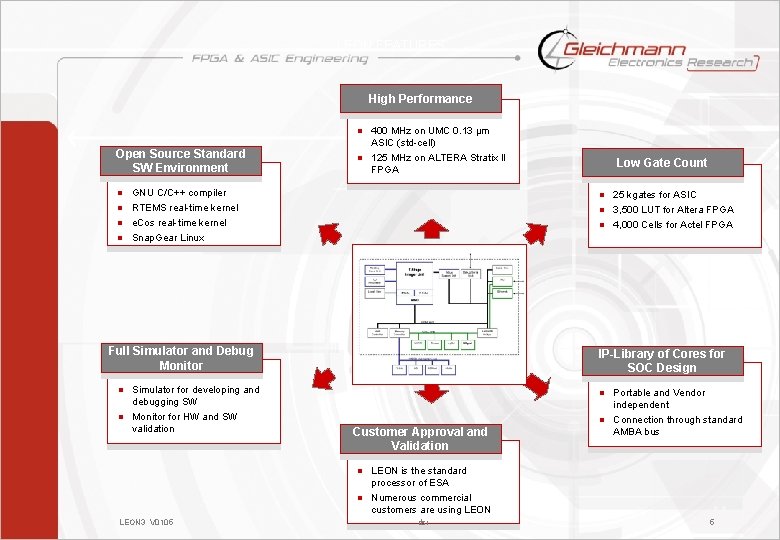

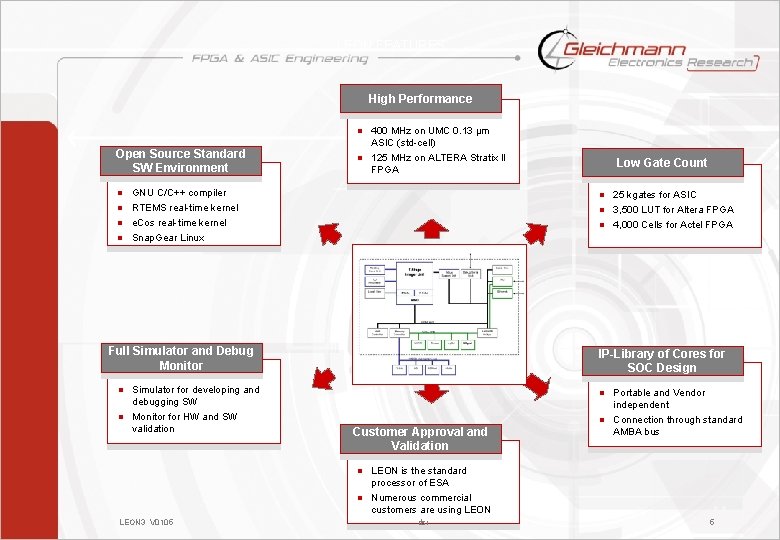

LEON FEATURES High Performance Open Source Standard SW Environment n 400 MHz on UMC 0. 13 µm ASIC (std-cell) n 125 MHz on ALTERA Stratix II FPGA Low Gate Count n Simple Integration GNU C/C++ compiler n n RTEMS real-time kernel n 25 kgates for ASIC 3, 500 LUT for Altera FPGA n e. Cos real-time kernel Snap. Gear Linux n 4, 000 Cells for Actel FPGA n Full Simulator and Debug Monitor n Simulator for developing and debugging SW n Monitor for HW and SW validation LEON 3 V 0105 IP-Library of Cores for SOC Design Customer Approval and Validation n LEON is the standard processor of ESA n Numerous commercial customers are using LEON dsr n Portable and Vendor independent n Connection through standard AMBA bus 5

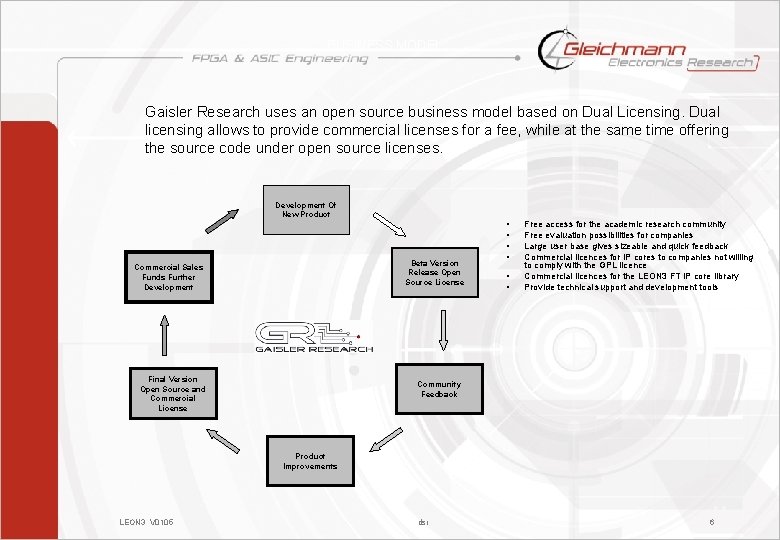

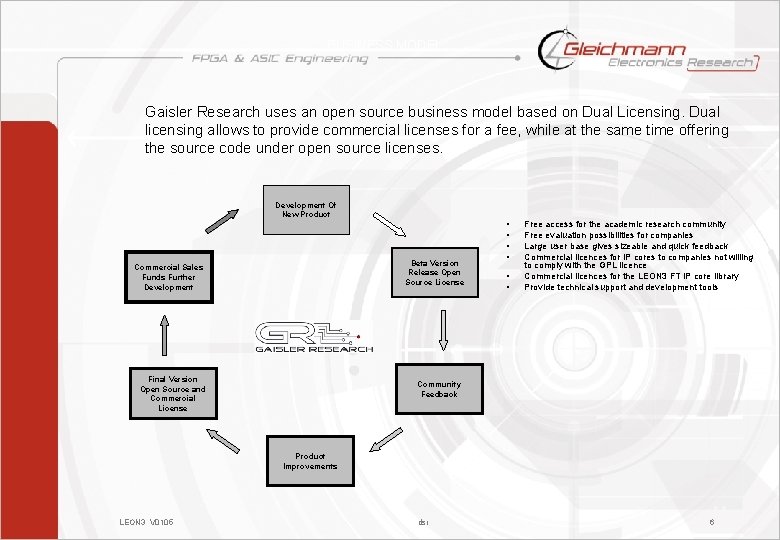

BUSINESS MODEL Gaisler Research uses an open source business model based on Dual Licensing. Dual licensing allows to provide commercial licenses for a fee, while at the same time offering the source code under open source licenses. Development Of New Product Beta Version Release Open Source License Commercial Sales Funds Further Development Final Version Open Source and Commercial License • • • Free access for the academic research community Free evaluation possibilities for companies Large user base gives sizeable and quick feedback Commercial licences for IP cores to companies not willing to comply with the GPL licence Commercial licences for the LEON 3 FT IP core library Provide technical support and development tools Community Feedback Product Improvements LEON 3 V 0105 dsr 6

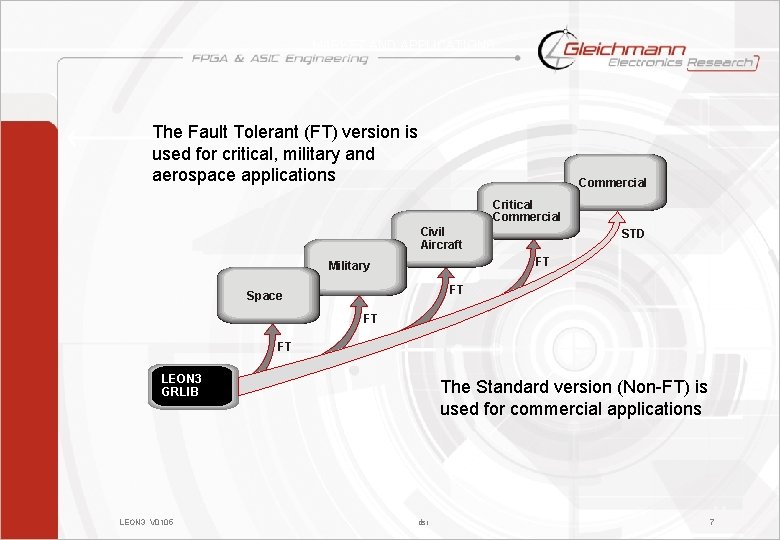

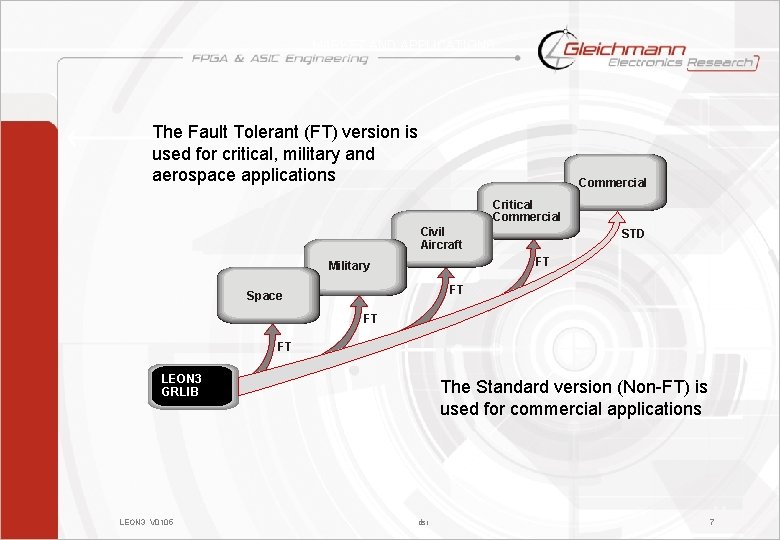

MARKET AND APPLICATIONS The Fault Tolerant (FT) version is used for critical, military and aerospace applications Commercial Critical Commercial Civil Aircraft STD FT Military FT Space FT FT LEON 3 GRLIB LEON 3 V 0105 The Standard version (Non-FT) is used for commercial applications dsr 7

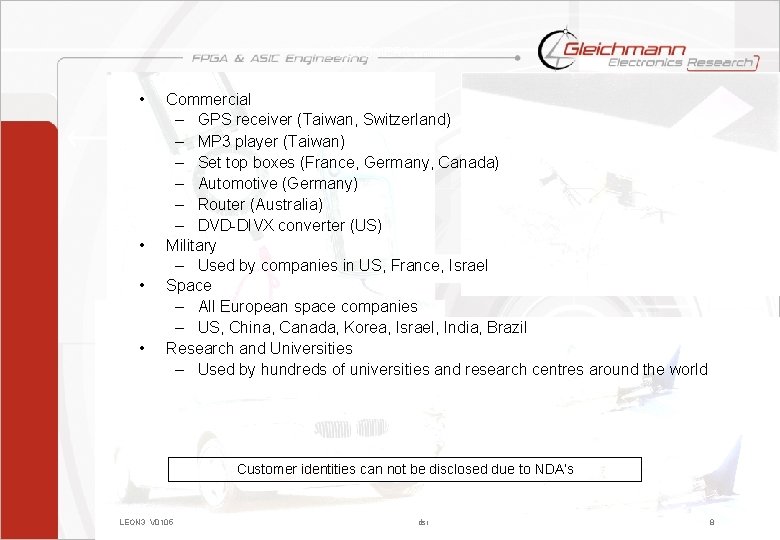

CUSTOMERS cont. INUED • • Commercial – GPS receiver (Taiwan, Switzerland) – MP 3 player (Taiwan) – Set top boxes (France, Germany, Canada) – Automotive (Germany) – Router (Australia) – DVD-DIVX converter (US) Military – Used by companies in US, France, Israel Space – All European space companies – US, China, Canada, Korea, Israel, India, Brazil Research and Universities – Used by hundreds of universities and research centres around the world Customer identities can not be disclosed due to NDA’s LEON 3 V 0105 dsr 8

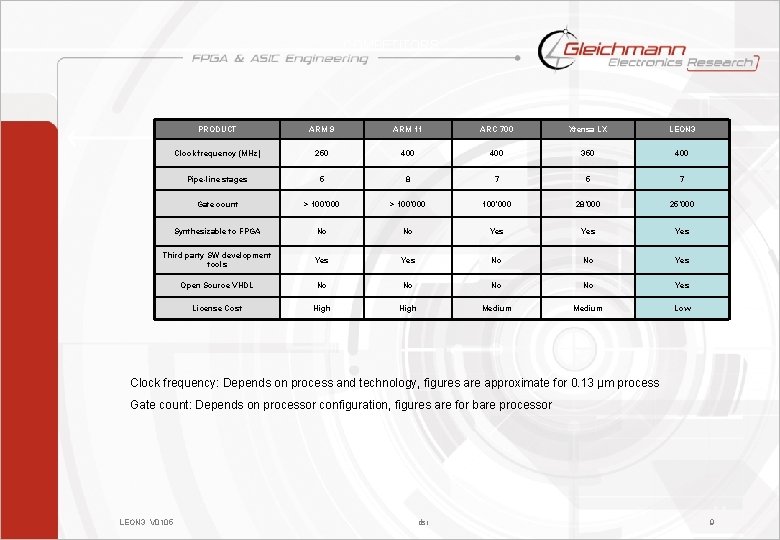

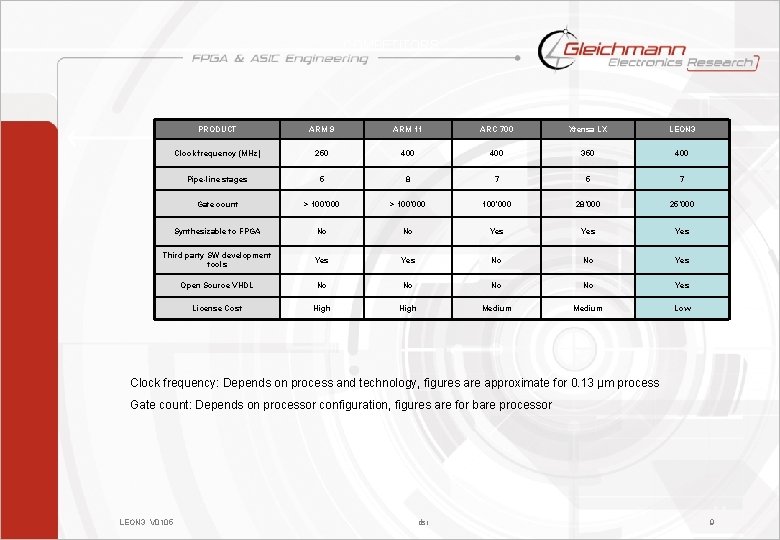

COMPETITORS PRODUCT ARM 9 ARM 11 ARC 700 Xtensa LX LEON 3 Clock frequency (MHz) 250 400 350 400 Pipe-line stages 5 8 7 5 7 Gate count > 100’ 000 28’ 000 25’ 000 Synthesizable to FPGA No No Yes Yes Third party SW development tools Yes No No Yes Open Source VHDL No No Yes License Cost High Medium Low Clock frequency: Depends on process and technology, figures are approximate for 0. 13 µm process Gate count: Depends on processor configuration, figures are for bare processor LEON 3 V 0105 dsr 9

Some advantages of LEON 3 (1) • Developed and validated for space use (FT-version) • High performance (400 MHz on 0. 13 µm process) • Optimized for embedded real time systems • IP library with co-processors and peripherals available • Plug&play capabilities for system on a chip design • Synthesizable, available in full VHDL source code • Tool and vendor independent LEON 3 V 0105 dsr 10

Some advantages of LEON 3 (2) • Standard CPU (SPARC 8), standard bus system (AMBA 2. 0) • Complete set of macros available (click & synthesize) • Large user community • Operating system LINUX and different RTOS available • Many years of experience guarantees a minimum number of bugs. • Every ARM user is a potential LEON client, specially for FPGA’s • … LEON 3 V 0105 dsr 11

Next steps at Gleichmann Research • Implementation of LEON 3 system on Hpe_mini LEC • Synthesis for high speed solution • Adaption of Snapgear Linux (with and without MMU • Evaluation of multiprocessor System • Adaptation and check of multi processor Linux • Implementation of different system solutions like PCIe, LCD controller, motor control … LEON 3 V 0105 dsr 12