Lecture Week 6 1 Computer Data Acquisition Systems

- Slides: 38

Lecture Week 6. 1 Computer Data Acquisition Systems Contents of this Lecture: § Outlines: Basics of computer data acquisition system. Lecturer: § Mohd Sofian Bin Mohammad Rosbi 2021/6/16 Lecture 14 1

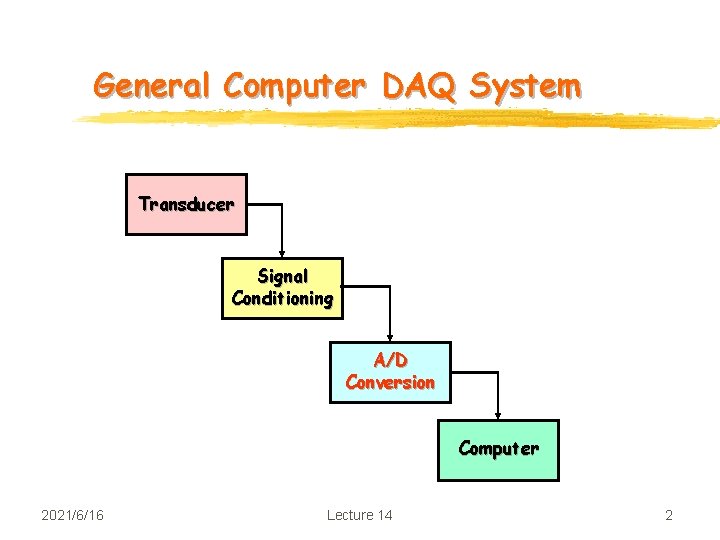

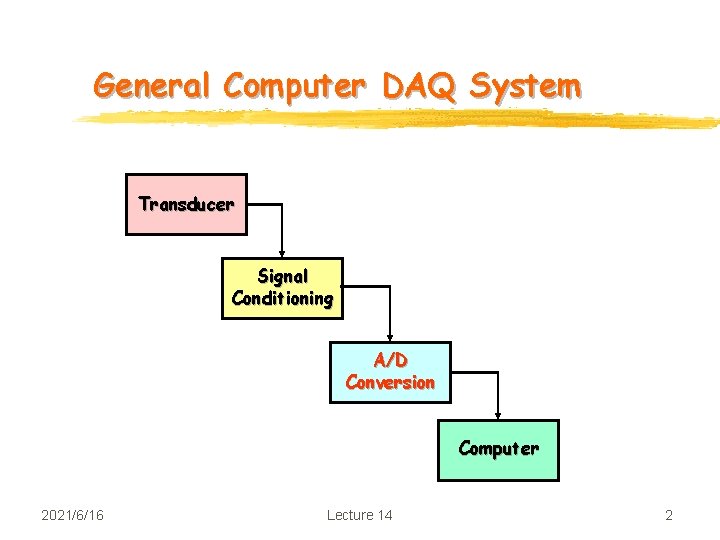

General Computer DAQ System Transducer Signal Conditioning A/D Conversion Computer 2021/6/16 Lecture 14 2

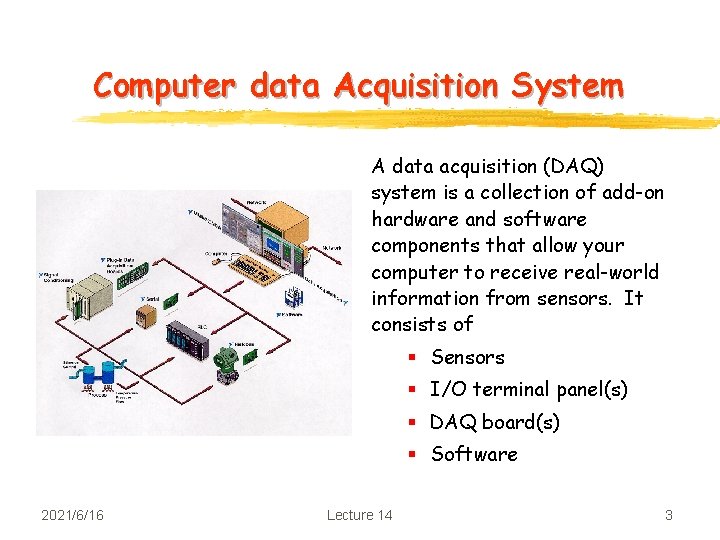

Computer data Acquisition System A data acquisition (DAQ) system is a collection of add-on hardware and software components that allow your computer to receive real-world information from sensors. It consists of § Sensors § I/O terminal panel(s) § DAQ board(s) § Software 2021/6/16 Lecture 14 3

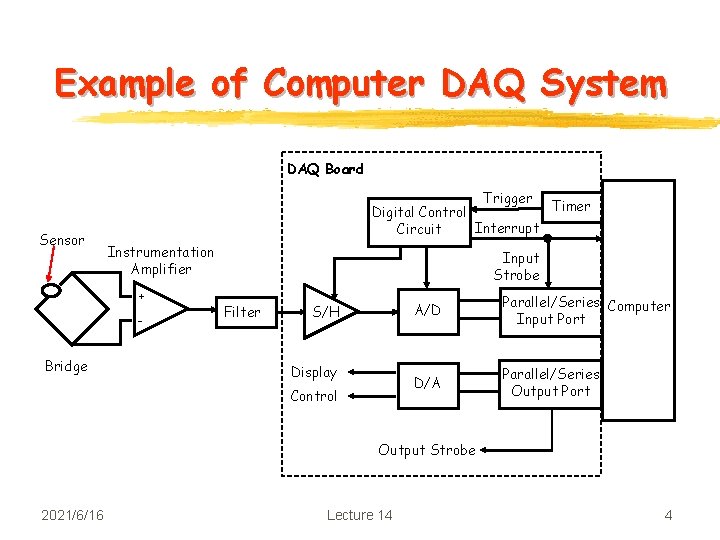

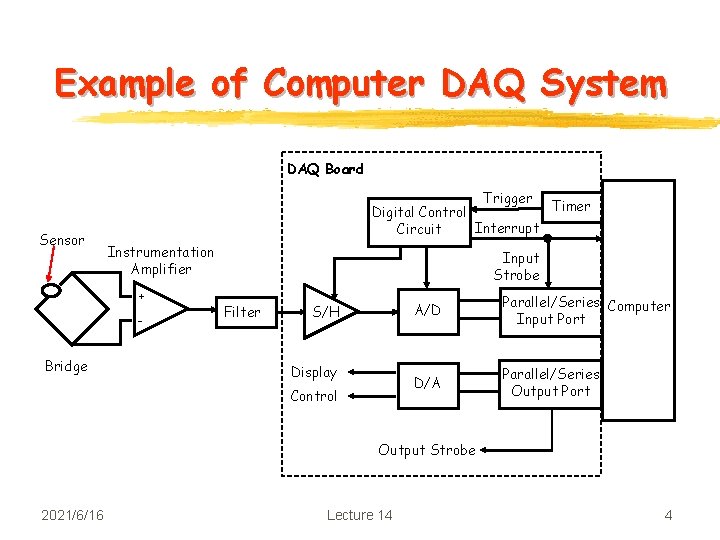

Example of Computer DAQ System DAQ Board Trigger Sensor Timer Digital Control Interrupt Circuit Instrumentation Amplifier + - Bridge Input Strobe Filter S/H Display Control A/D Parallel/Series Computer Input Port D/A Parallel/Series Output Port Output Strobe 2021/6/16 Lecture 14 4

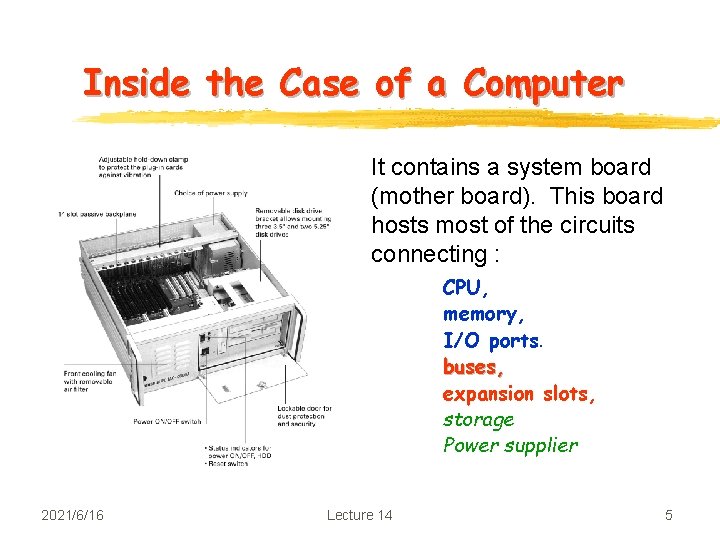

Inside the Case of a Computer It contains a system board (mother board). This board hosts most of the circuits connecting : CPU, memory, I/O ports. buses, expansion slots, storage Power supplier 2021/6/16 Lecture 14 5

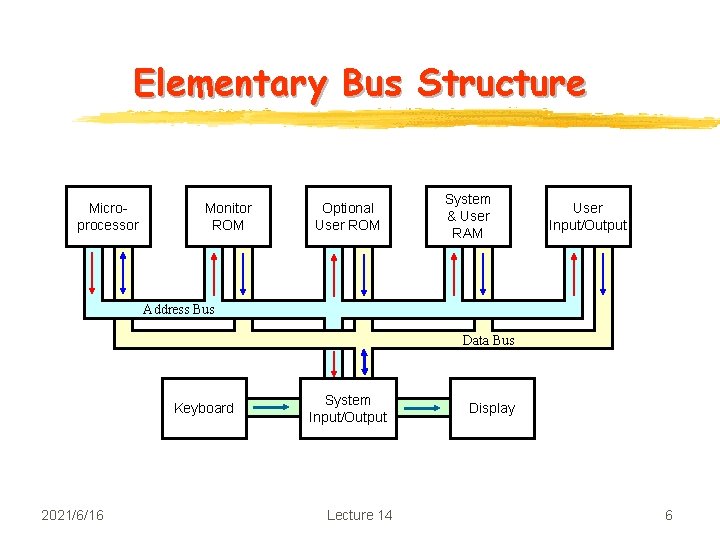

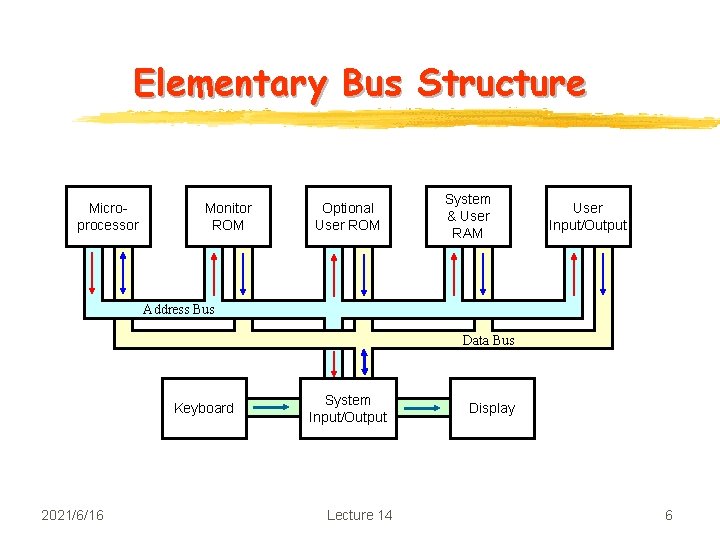

Elementary Bus Structure Microprocessor Monitor ROM Optional User ROM System & User RAM User Input/Output Address Bus Data Bus Keyboard 2021/6/16 System Input/Output Lecture 14 Display 6

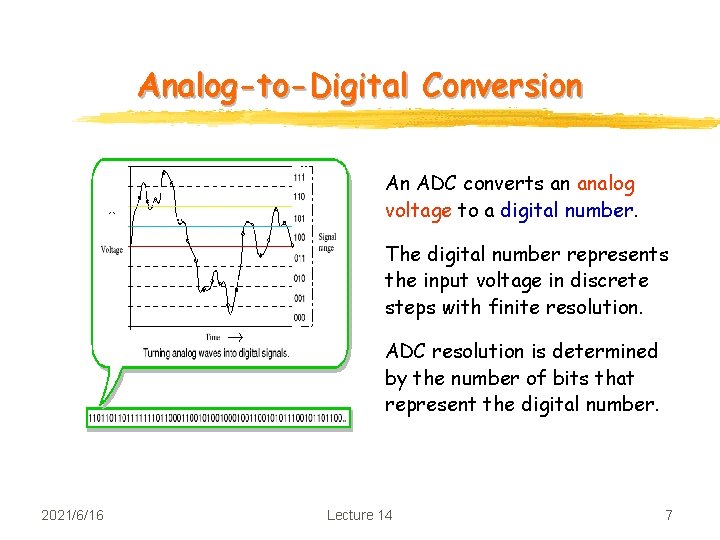

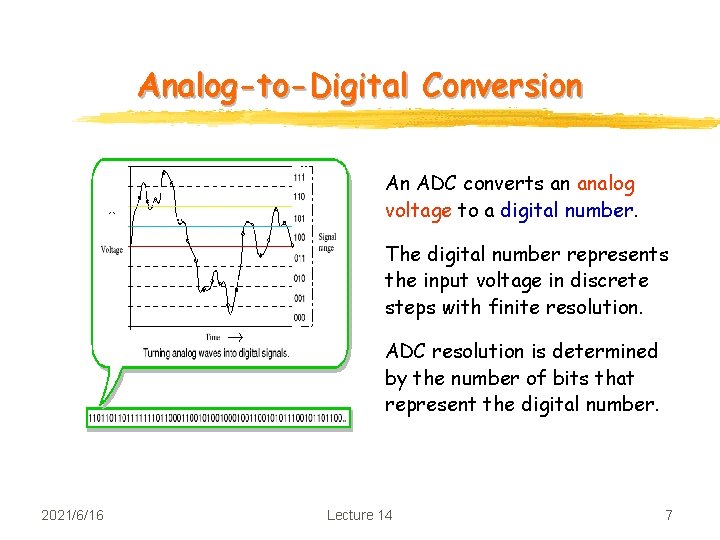

Analog-to-Digital Conversion An ADC converts an analog voltage to a digital number. The digital number represents the input voltage in discrete steps with finite resolution. ADC resolution is determined by the number of bits that represent the digital number. 2021/6/16 Lecture 14 7

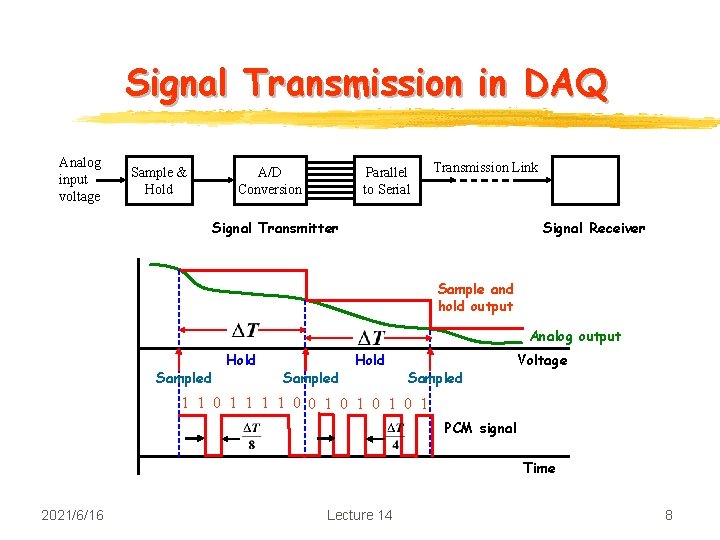

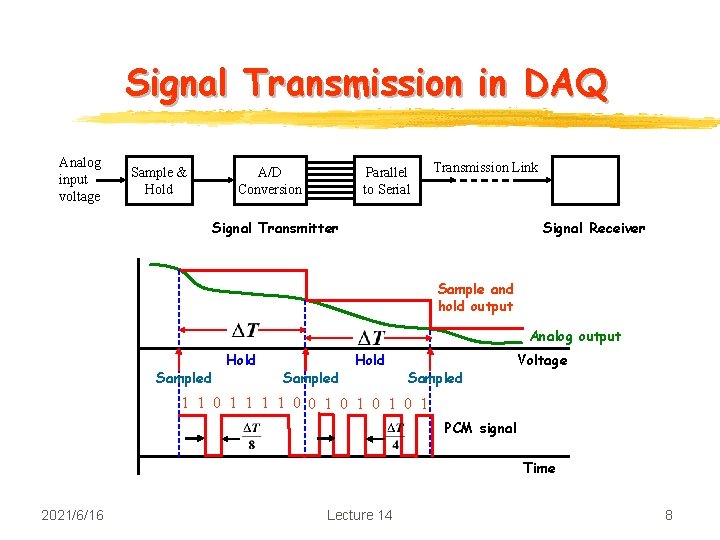

Signal Transmission in DAQ Analog input voltage Sample & Hold A/D Conversion Parallel to Serial Transmission Link Signal Transmitter Signal Receiver Sample and hold output Analog output Sampled Hold Sampled Voltage 1 1 0 0 1 0 1 PCM signal Time 2021/6/16 Lecture 14 8

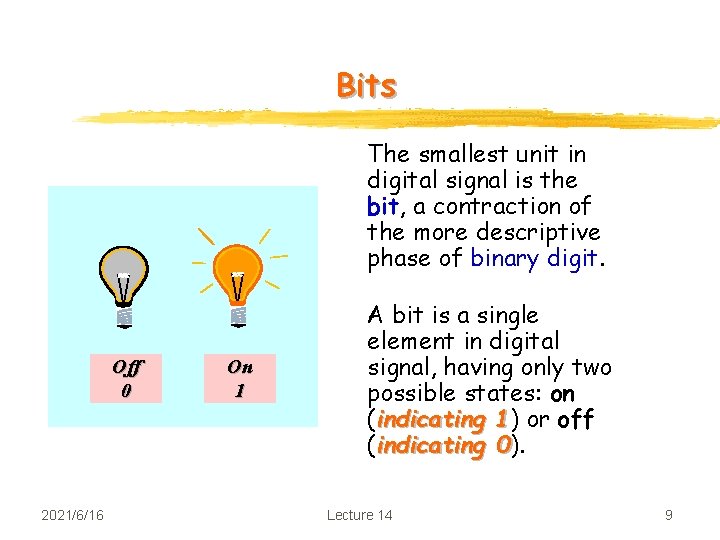

Bits The smallest unit in digital signal is the bit, a contraction of the more descriptive phase of binary digit. Off 0 2021/6/16 On 1 A bit is a single element in digital signal, having only two possible states: on (indicating 1) 1 or off (indicating 0). 0 Lecture 14 9

Bytes Bits are organized into larger units called bytes, the basic unit of information in a computer system. Off On Off Off On 0 0 1 A basic byte contains 8 bits. The total amount of information it can convey is 28 (=256) possible combinations. 2021/6/16 Lecture 14 10

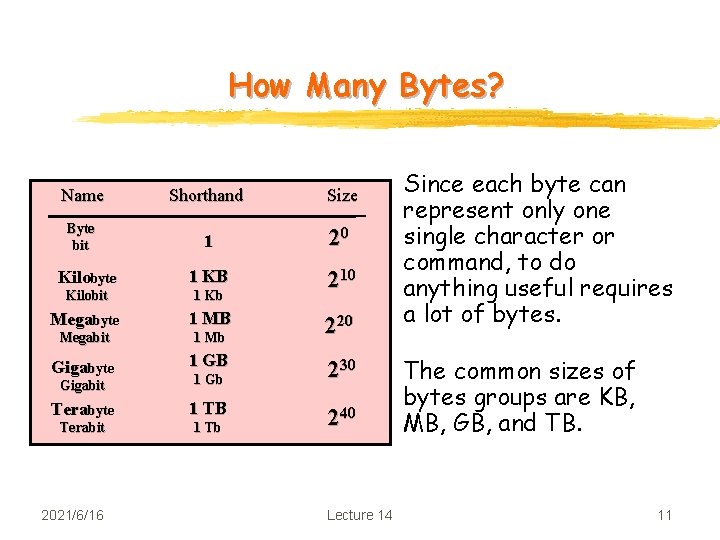

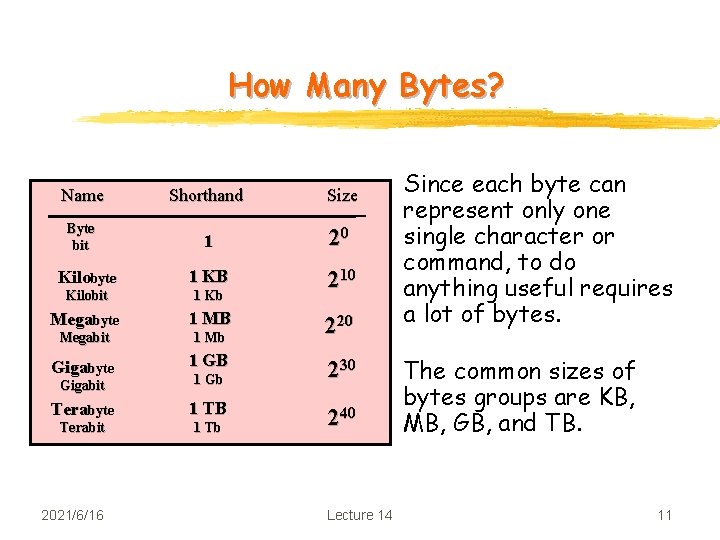

How Many Bytes? Name Shorthand Size Byte bit 1 20 Kilobyte 1 KB Kilobit 1 Kb 210 Megabyte 1 MB Megabit 1 Mb Gigabyte 1 GB Gigabit 1 Gb Terabyte 1 TB Terabit 1 Tb 2021/6/16 220 230 240 Lecture 14 Since each byte can represent only one single character or command, to do anything useful requires a lot of bytes. The common sizes of bytes groups are KB, MB, GB, and TB. 11

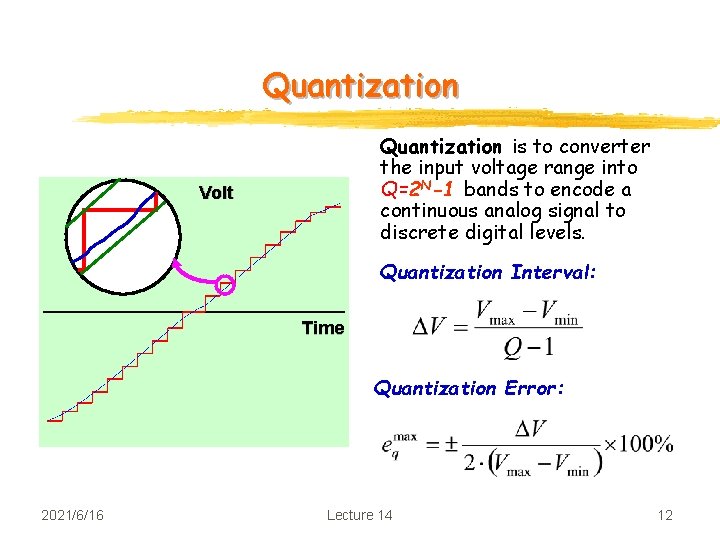

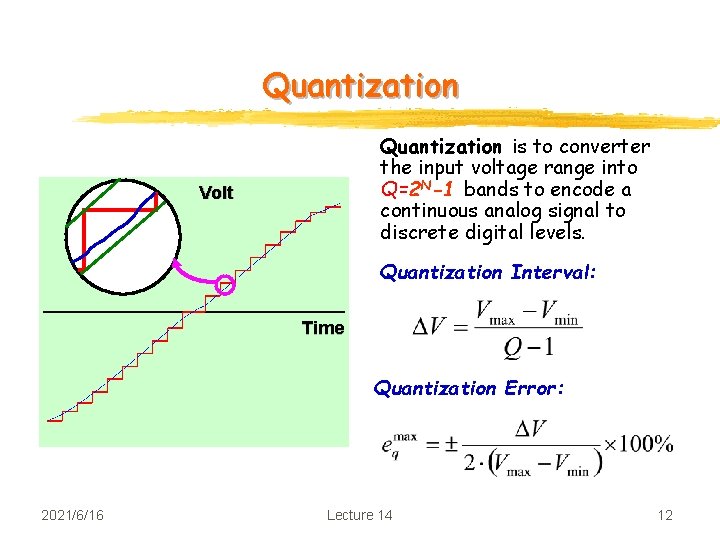

Quantization is to converter the input voltage range into Q=2 N-1 bands to encode a continuous analog signal to discrete digital levels. Volt Quantization Interval: Time Quantization Error: 2021/6/16 Lecture 14 12

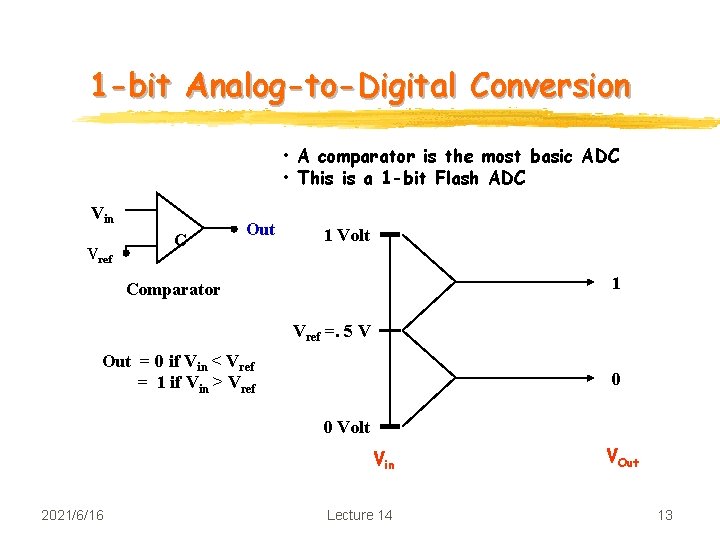

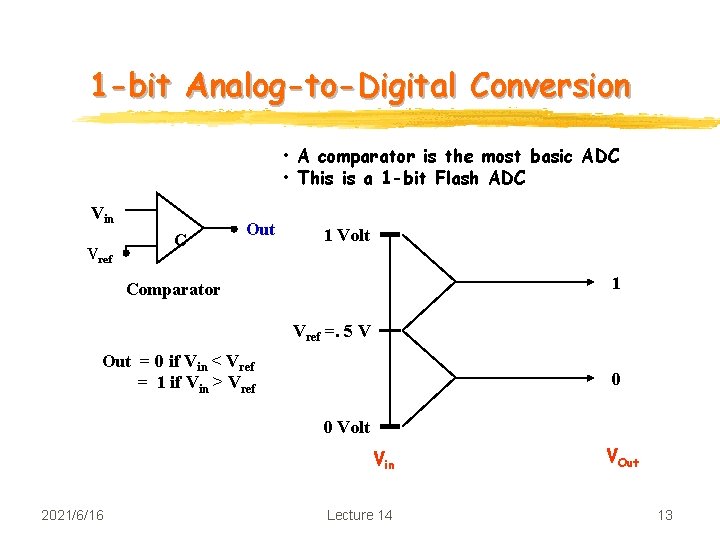

1 -bit Analog-to-Digital Conversion • A comparator is the most basic ADC • This is a 1 -bit Flash ADC Vin Vref C Out 1 Volt 1 Comparator Vref =. 5 V Out = 0 if Vin < Vref = 1 if Vin > Vref 0 0 Volt Vin 2021/6/16 Lecture 14 VOut 13

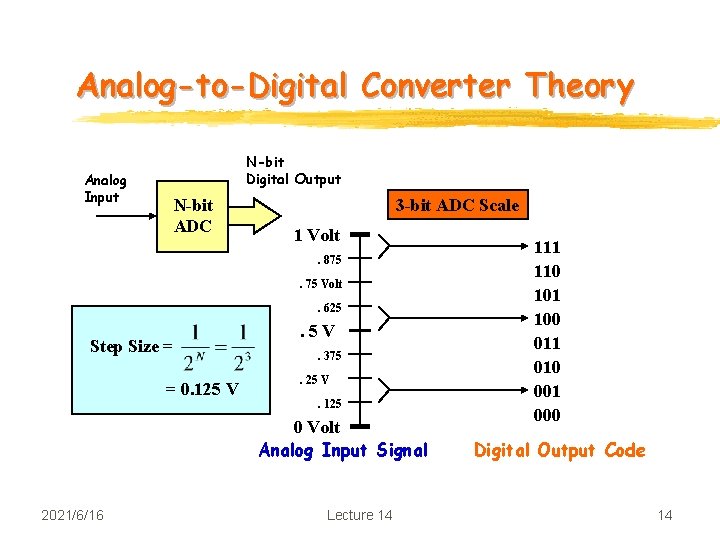

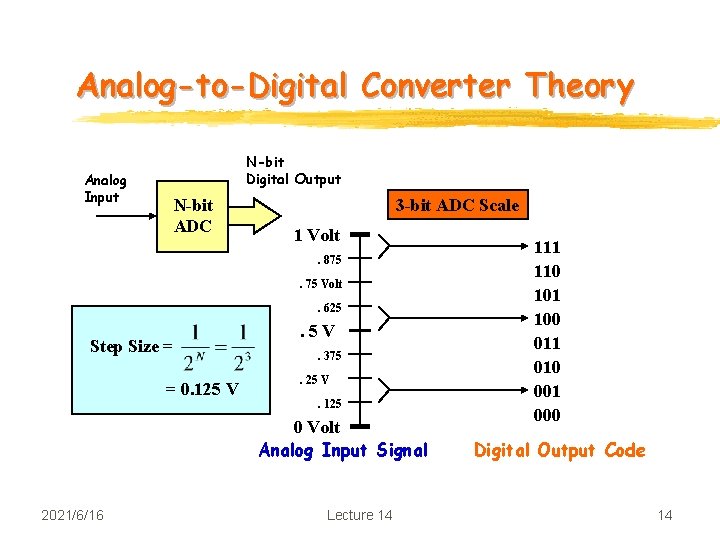

Analog-to-Digital Converter Theory Analog Input N-bit Digital Output N-bit ADC 3 -bit ADC Scale 1 Volt. 875. 75 Volt. 625 Step Size = = 0. 125 V . 5 V. 375. 25 V. 125 0 Volt Analog Input Signal 2021/6/16 Lecture 14 111 110 101 100 011 010 001 000 Digital Output Code 14

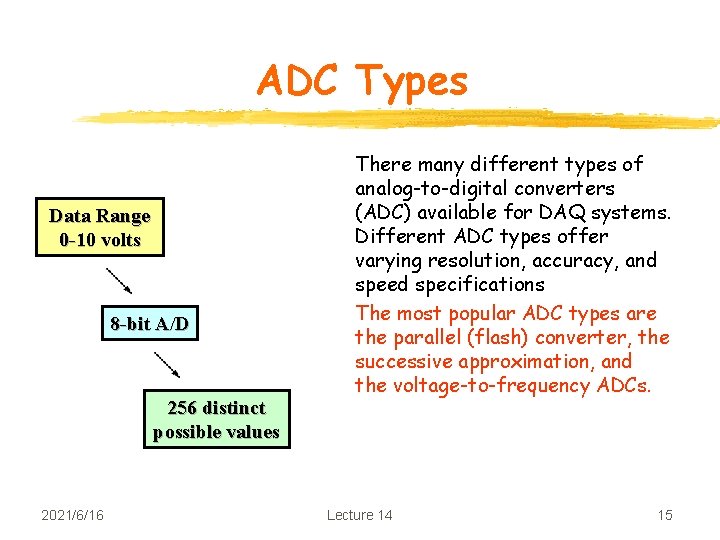

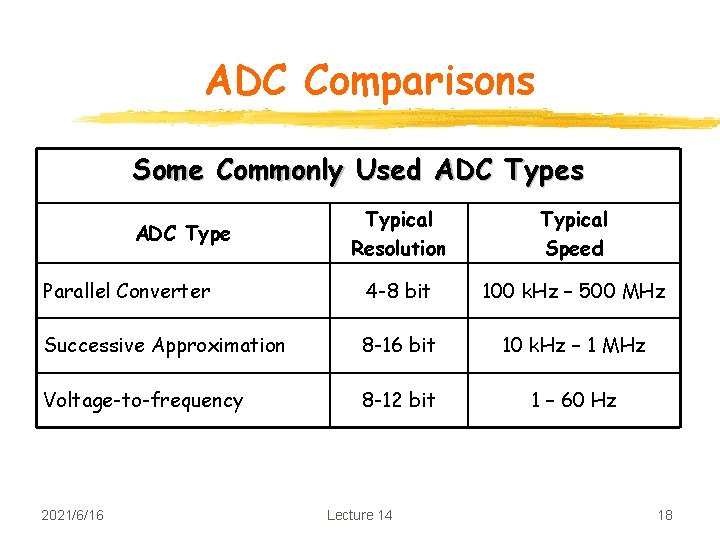

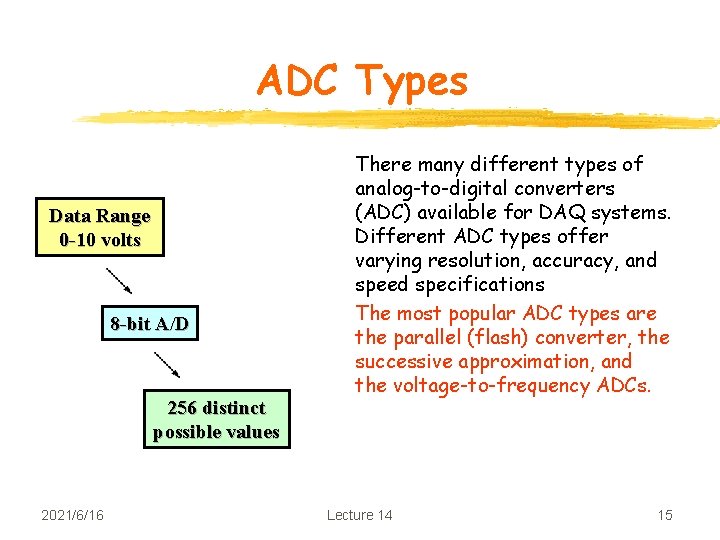

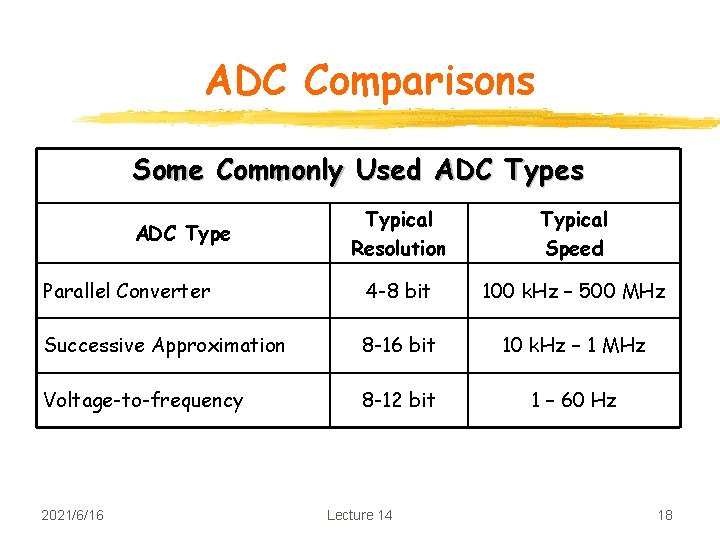

ADC Types Data Range 0 -10 volts 8 -bit A/D 256 distinct possible values 2021/6/16 There many different types of analog-to-digital converters (ADC) available for DAQ systems. Different ADC types offer varying resolution, accuracy, and speed specifications The most popular ADC types are the parallel (flash) converter, the successive approximation, and the voltage-to-frequency ADCs. Lecture 14 15

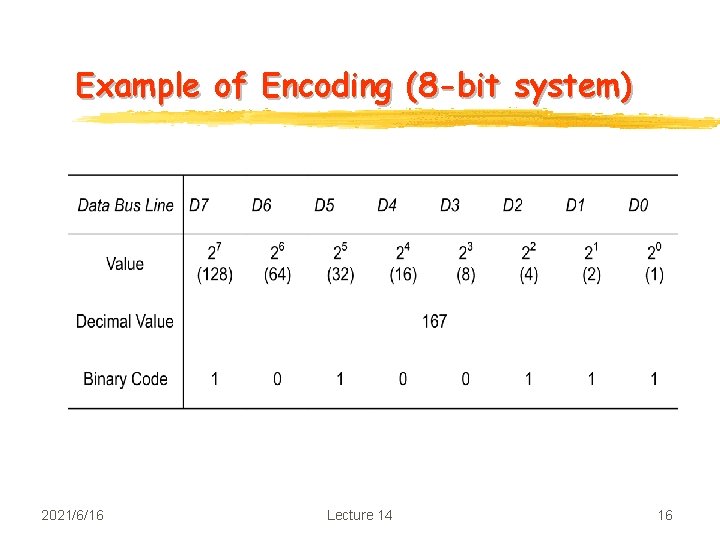

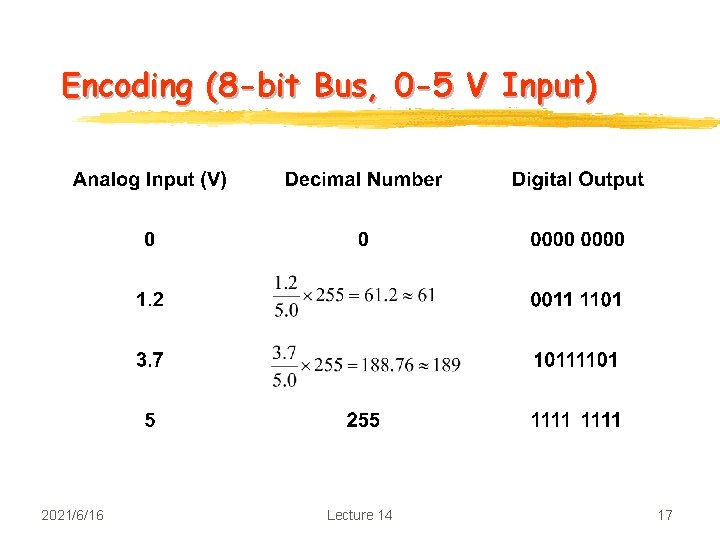

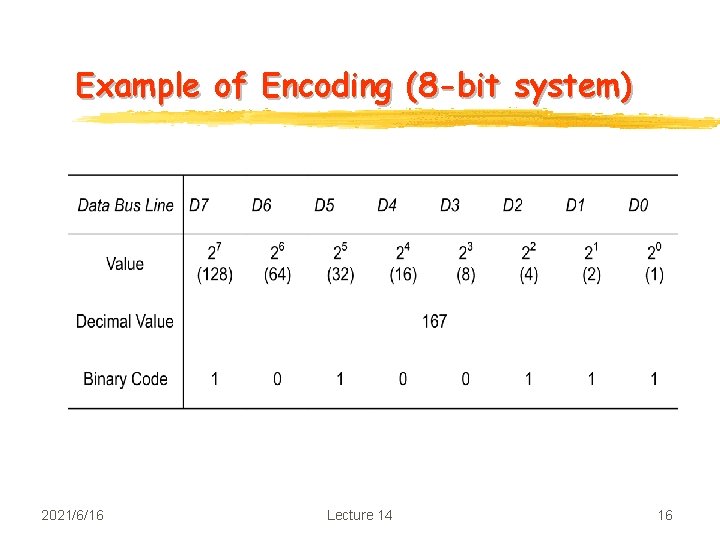

Example of Encoding (8 -bit system) 2021/6/16 Lecture 14 16

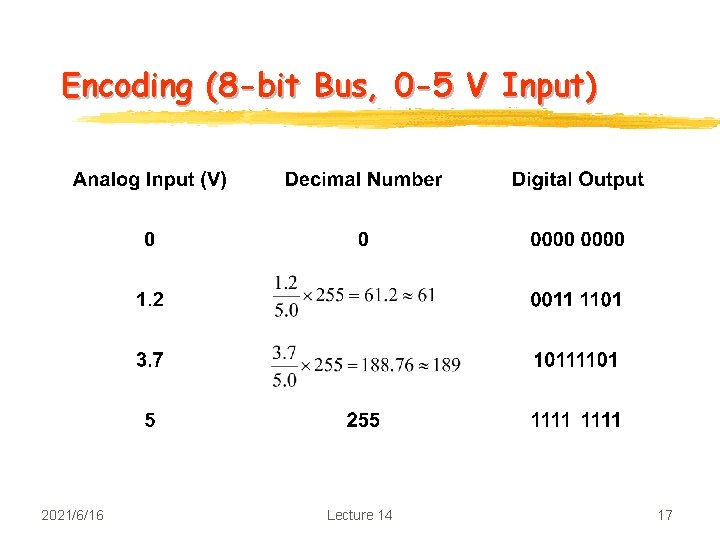

Encoding (8 -bit Bus, 0 -5 V Input) 2021/6/16 Lecture 14 17

ADC Comparisons Some Commonly Used ADC Types Typical Resolution Typical Speed Parallel Converter 4 -8 bit 100 k. Hz – 500 MHz Successive Approximation 8 -16 bit 10 k. Hz – 1 MHz Voltage-to-frequency 8 -12 bit 1 – 60 Hz ADC Type 2021/6/16 Lecture 14 18

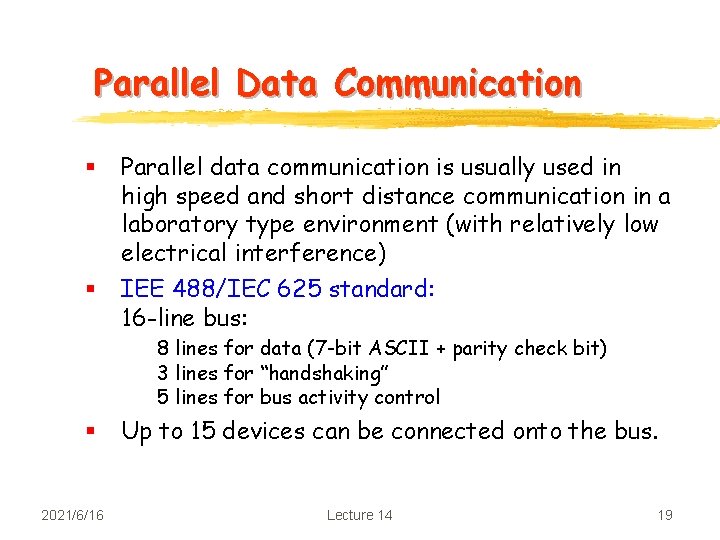

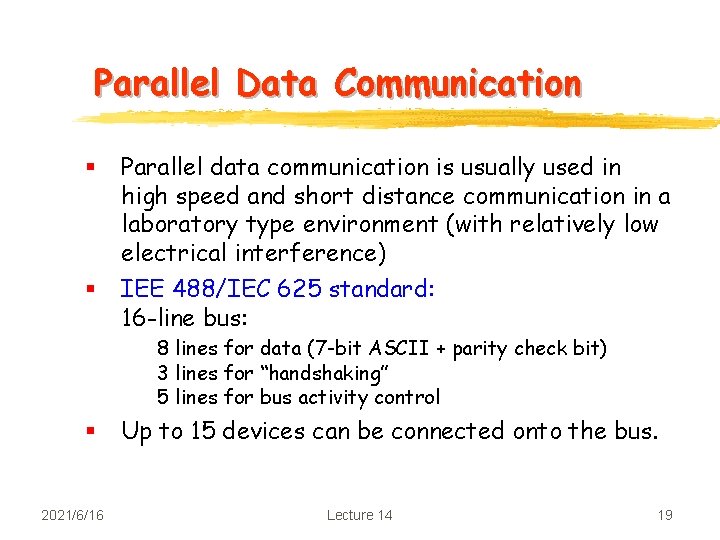

Parallel Data Communication § § Parallel data communication is usually used in high speed and short distance communication in a laboratory type environment (with relatively low electrical interference) IEE 488/IEC 625 standard: 16 -line bus: 8 lines for data (7 -bit ASCII + parity check bit) 3 lines for “handshaking” 5 lines for bus activity control § 2021/6/16 Up to 15 devices can be connected onto the bus. Lecture 14 19

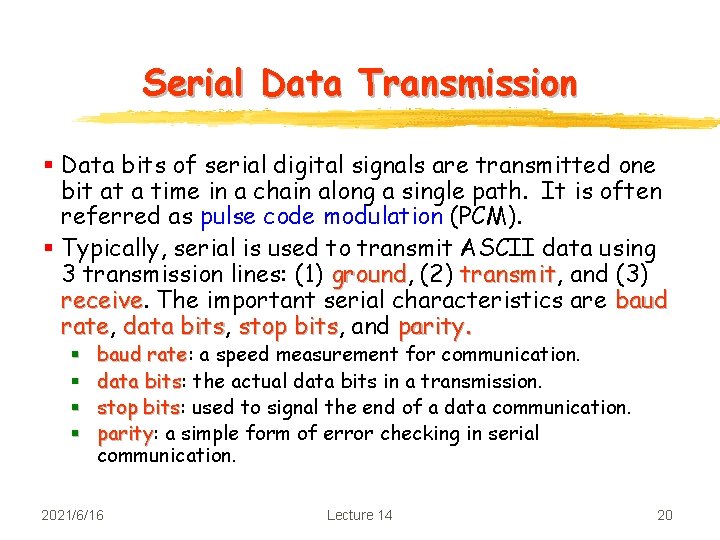

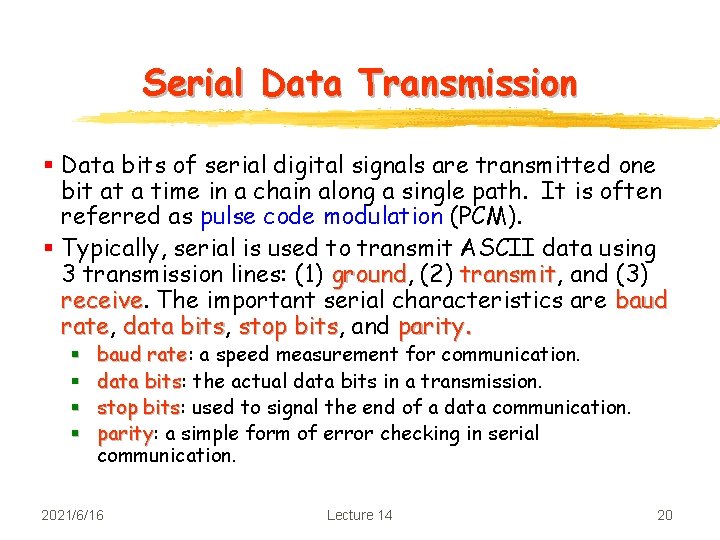

Serial Data Transmission § Data bits of serial digital signals are transmitted one bit at a time in a chain along a single path. It is often referred as pulse code modulation (PCM). § Typically, serial is used to transmit ASCII data using 3 transmission lines: (1) ground, ground (2) transmit, transmit and (3) receive The important serial characteristics are baud rate, rate data bits, bits stop bits, bits and parity. § § baud rate: rate a speed measurement for communication. data bits: bits the actual data bits in a transmission. stop bits: bits used to signal the end of a data communication. parity: parity a simple form of error checking in serial communication. 2021/6/16 Lecture 14 20

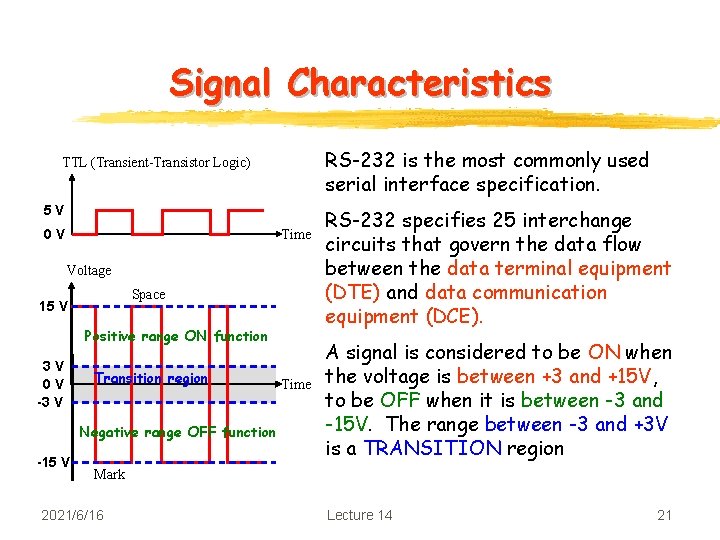

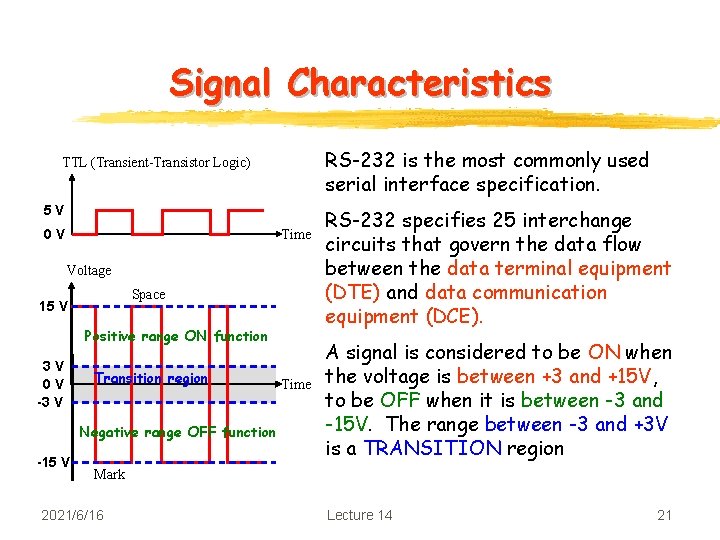

Signal Characteristics RS-232 is the most commonly used serial interface specification. TTL (Transient-Transistor Logic) 5 V 0 V Time Voltage Space 15 V Positive range ON function 3 V 0 V -3 V Transition region Negative range OFF function -15 V Time RS-232 specifies 25 interchange circuits that govern the data flow between the data terminal equipment (DTE) and data communication equipment (DCE). A signal is considered to be ON when the voltage is between +3 and +15 V, to be OFF when it is between -3 and -15 V. The range between -3 and +3 V is a TRANSITION region Mark 2021/6/16 Lecture 14 21

Baud Rate When we refer to the clock speed of serial transmission, we mean the baud rate. If the protocol calls for a 4800 baud rate, then the clock is running at 4800 Hz. It means that the serial port is sampling the data line at 4800 Hz. Common baud rates for telephone lines are 14, 400; 28, 800; and 33, 600. Baud rates greater than these are possible, but these rates reduce the distance by which devices can be separated. 2021/6/16 Lecture 14 22

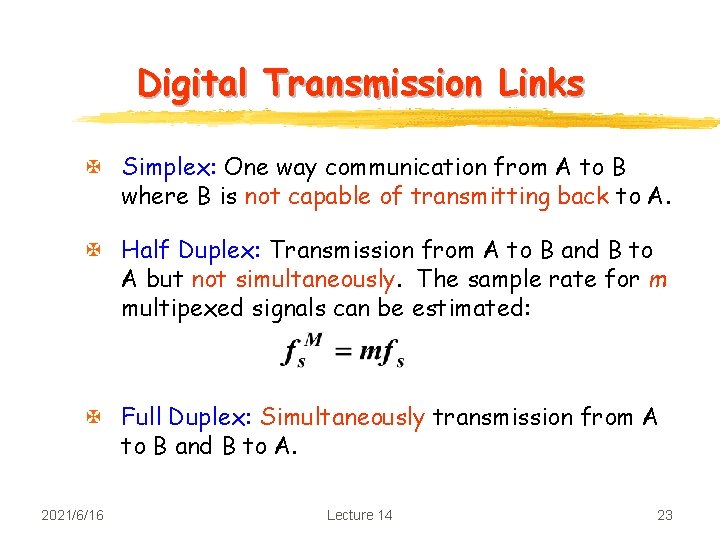

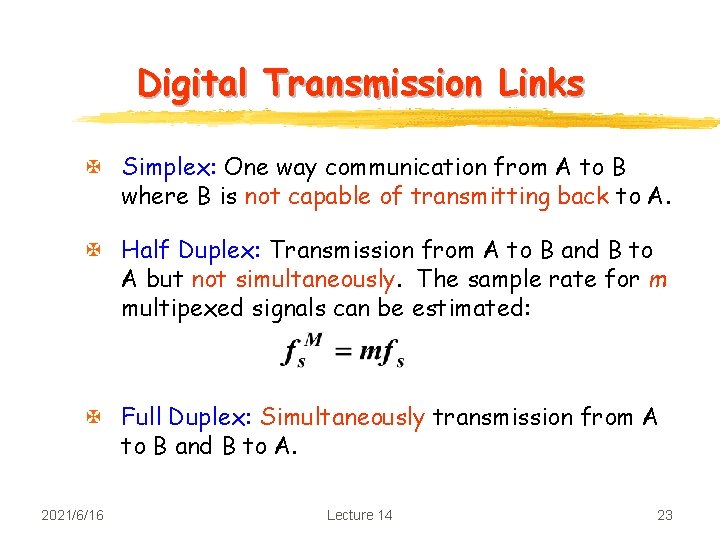

Digital Transmission Links X Simplex: One way communication from A to B where B is not capable of transmitting back to A. X Half Duplex: Transmission from A to B and B to A but not simultaneously. The sample rate for m multipexed signals can be estimated: X Full Duplex: Simultaneously transmission from A to B and B to A. 2021/6/16 Lecture 14 23

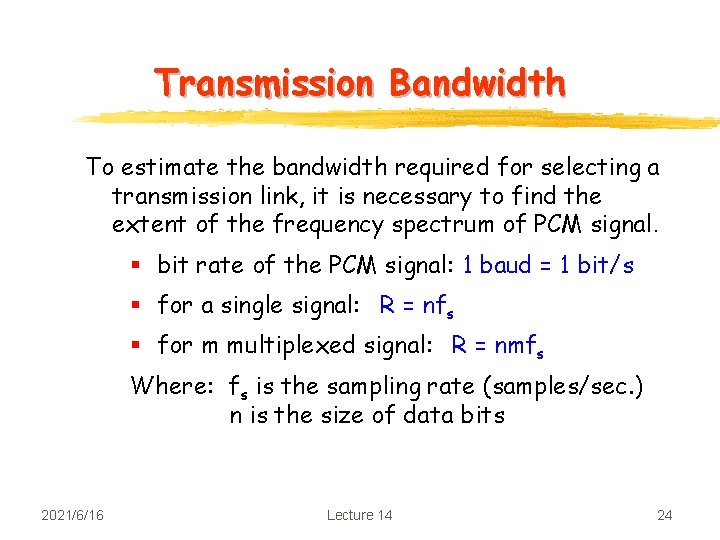

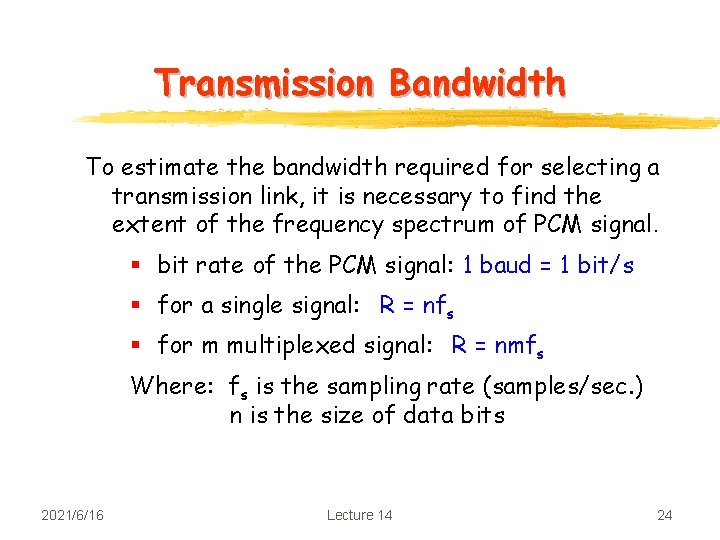

Transmission Bandwidth To estimate the bandwidth required for selecting a transmission link, it is necessary to find the extent of the frequency spectrum of PCM signal. § bit rate of the PCM signal: 1 baud = 1 bit/s § for a single signal: R = nfs § for m multiplexed signal: R = nmfs Where: fs is the sampling rate (samples/sec. ) n is the size of data bits 2021/6/16 Lecture 14 24

Transmission Bandwidth Calculation In a general case of a single signal, sampled at f. S, and encoded into an n-bit code, the minimum PCM bandwidth is determined by For m multiplexed signals, each sampled as f. S=1/ t, the time in the HOLD state is m/ t. This means that an n bits of information must be transmitted during time t /m, the corresponding PCM bandwidth in this case is 2021/6/16 Lecture 14 25

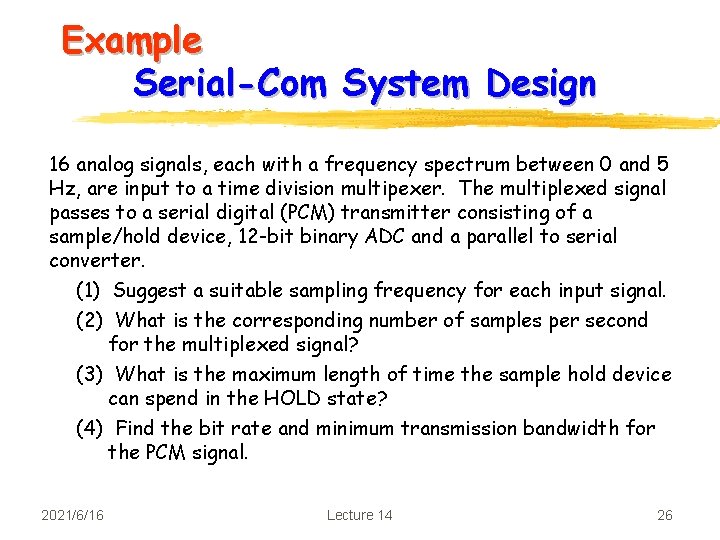

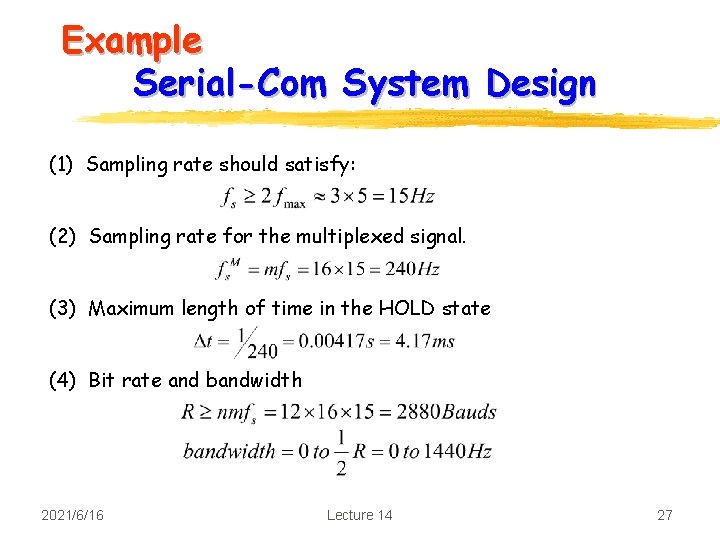

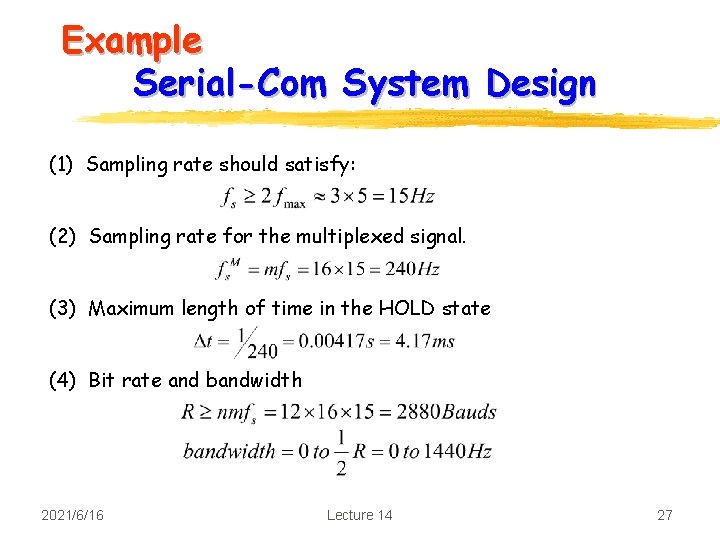

Example Serial-Com System Design 16 analog signals, each with a frequency spectrum between 0 and 5 Hz, are input to a time division multipexer. The multiplexed signal passes to a serial digital (PCM) transmitter consisting of a sample/hold device, 12 -bit binary ADC and a parallel to serial converter. (1) Suggest a suitable sampling frequency for each input signal. (2) What is the corresponding number of samples per second for the multiplexed signal? (3) What is the maximum length of time the sample hold device can spend in the HOLD state? (4) Find the bit rate and minimum transmission bandwidth for the PCM signal. 2021/6/16 Lecture 14 26

Example Serial-Com System Design (1) Sampling rate should satisfy: (2) Sampling rate for the multiplexed signal. (3) Maximum length of time in the HOLD state (4) Bit rate and bandwidth 2021/6/16 Lecture 14 27

Plug-In Data Acquisition Boards Plug in data acquisition board is a good solution for systems that don't need portability. Key Benefits § Lowest cost § Large selection to choose from § Established platform 2021/6/16 Lecture 14 28

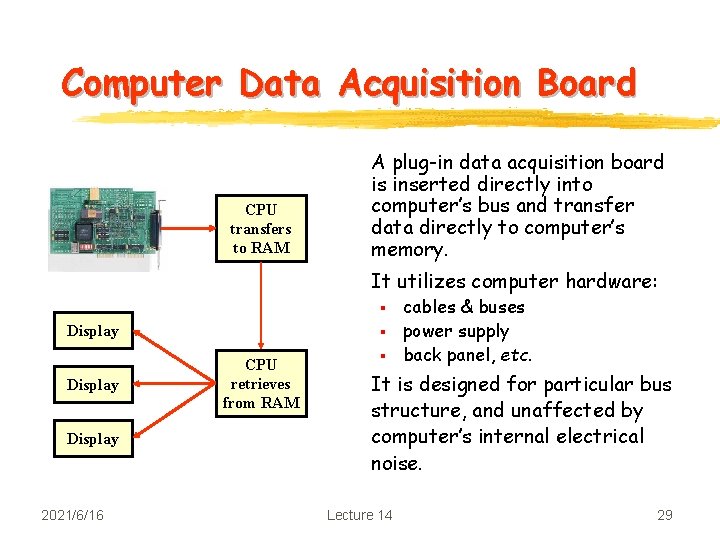

Computer Data Acquisition Board CPU transfers to RAM A plug-in data acquisition board is inserted directly into computer’s bus and transfer data directly to computer’s memory. It utilizes computer hardware: § Display 2021/6/16 § CPU retrieves from RAM § cables & buses power supply back panel, etc. It is designed for particular bus structure, and unaffected by computer’s internal electrical noise. Lecture 14 29

Bus Structures of Plug-in Board The are several types of local bus structures commonly used for plug-in boards : l l l l 2021/6/16 Lecture 14 AT NEC PC-9800 Parallel Port PCI PCMCIA PXI USB Others 30

DAS-8 Series The DAS-8 family is a series of 4 k. Hz analog and digital boards for IBM compatible computers. Major Models § DAS-8 base model, 8 -channel, 12 -bit § DAS-8/LT modified model for laptop § DAS-8 PGA programmable inputs, clock § DAS-8/AO include 2 analog output channels 2021/6/16 Lecture 14 31

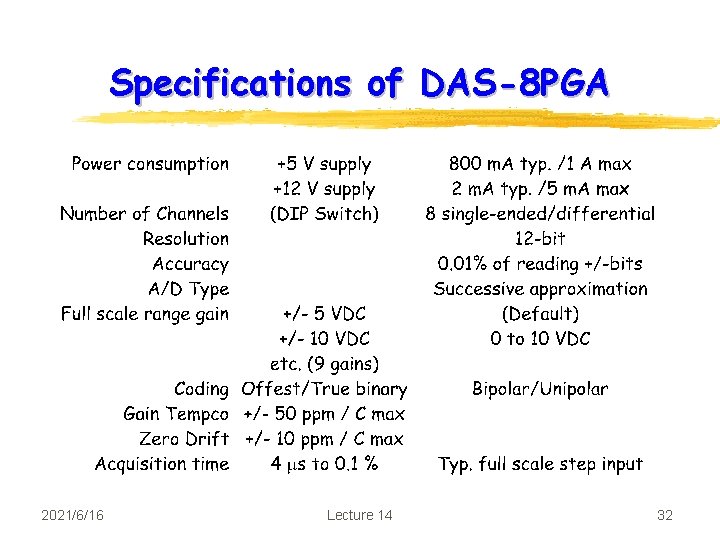

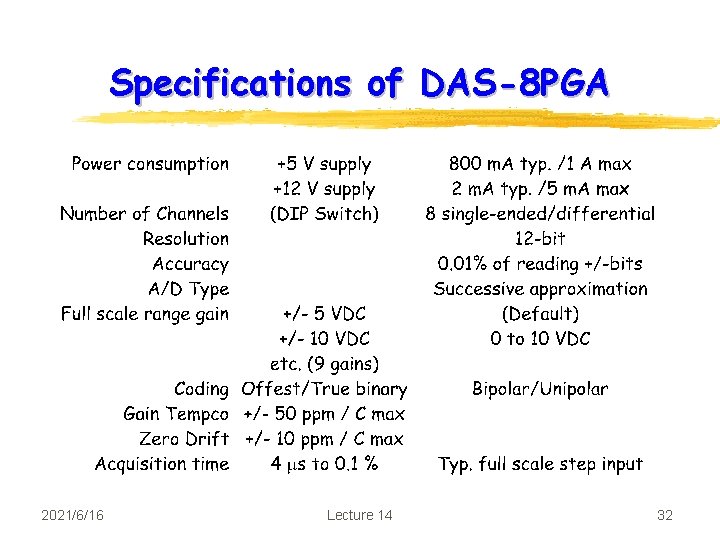

Specifications of DAS-8 PGA 2021/6/16 Lecture 14 32

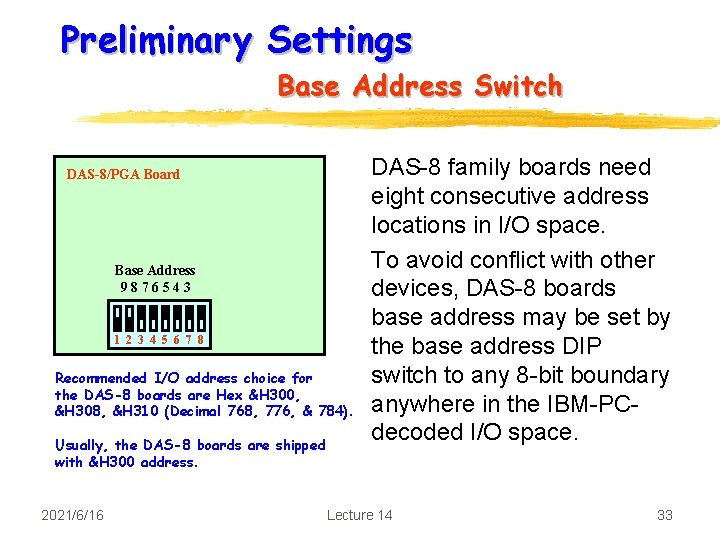

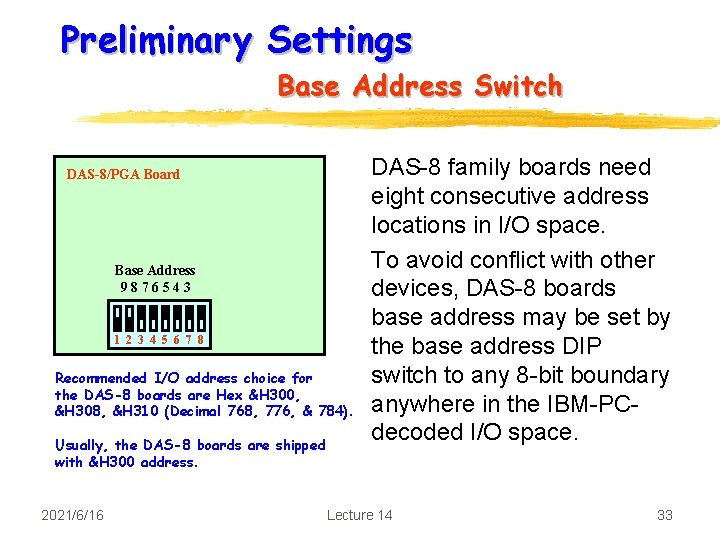

Preliminary Settings Base Address Switch DAS-8/PGA Board Base Address 9876543 1 2 3 4 5 6 7 8 Recommended I/O address choice for the DAS-8 boards are Hex &H 300, &H 308, &H 310 (Decimal 768, 776, & 784). Usually, the DAS-8 boards are shipped with &H 300 address. 2021/6/16 DAS-8 family boards need eight consecutive address locations in I/O space. To avoid conflict with other devices, DAS-8 boards base address may be set by the base address DIP switch to any 8 -bit boundary anywhere in the IBM-PCdecoded I/O space. Lecture 14 33

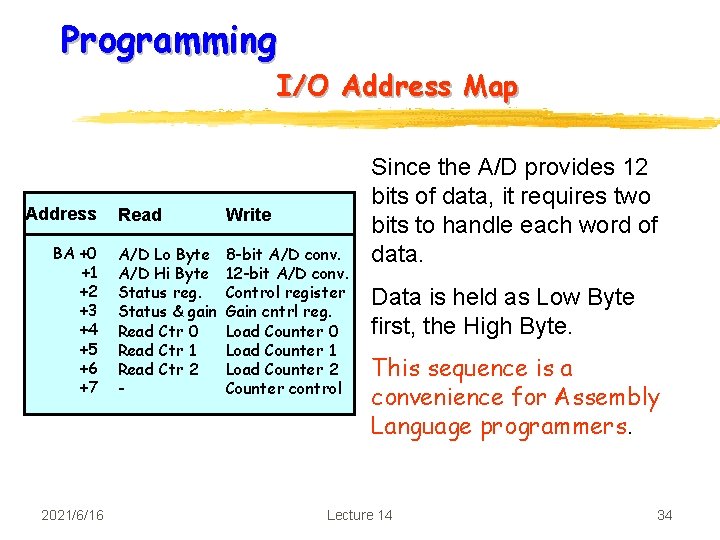

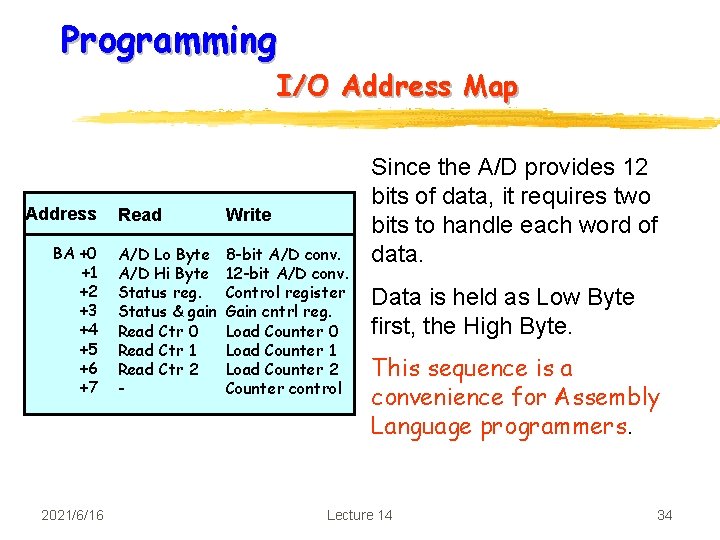

Programming I/O Address Map Address BA +0 +1 +2 +3 +4 +5 +6 +7 2021/6/16 Read Write A/D Lo Byte A/D Hi Byte Status reg. Status & gain Read Ctr 0 Read Ctr 1 Read Ctr 2 - 8 -bit A/D conv. 12 -bit A/D conv. Control register Gain cntrl reg. Load Counter 0 Load Counter 1 Load Counter 2 Counter control Since the A/D provides 12 bits of data, it requires two bits to handle each word of data. Data is held as Low Byte first, the High Byte. This sequence is a convenience for Assembly Language programmers. Lecture 14 34

Programming Driver Installation Example of syntax for device definition of a single board located at 300 (hex): DEVICE = DAS 8 DI. SYS/B: &h 300 A Device Interface Driver is required to pass the Base Address and corresponding Interrupt Level of a DAS-8 family board to a user program. Driver installs automatically at boot-up and can handle up to five boards in a computer system. 2021/6/16 Lecture 14 35

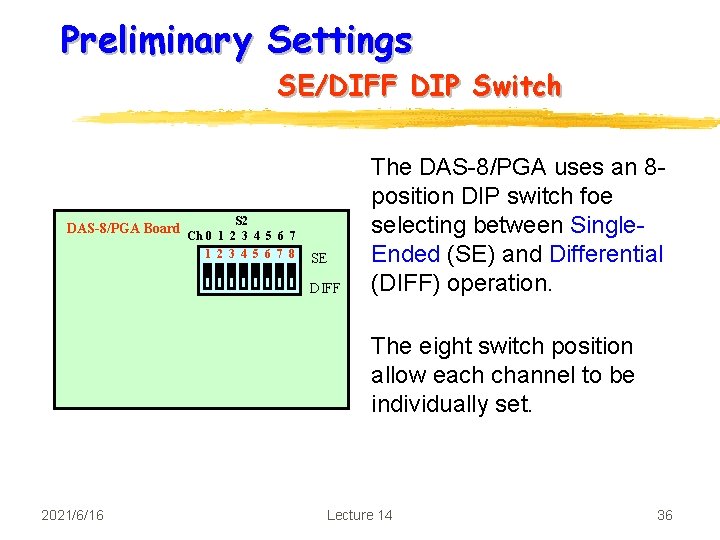

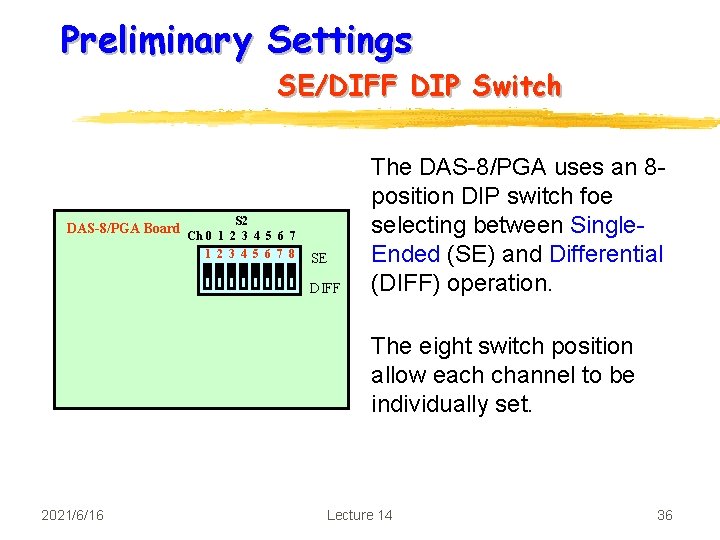

Preliminary Settings SE/DIFF DIP Switch S 2 DAS-8/PGA Board Ch 0 1 2 3 4 5 6 7 8 SE DIFF The DAS-8/PGA uses an 8 position DIP switch foe selecting between Single. Ended (SE) and Differential (DIFF) operation. The eight switch position allow each channel to be individually set. 2021/6/16 Lecture 14 36

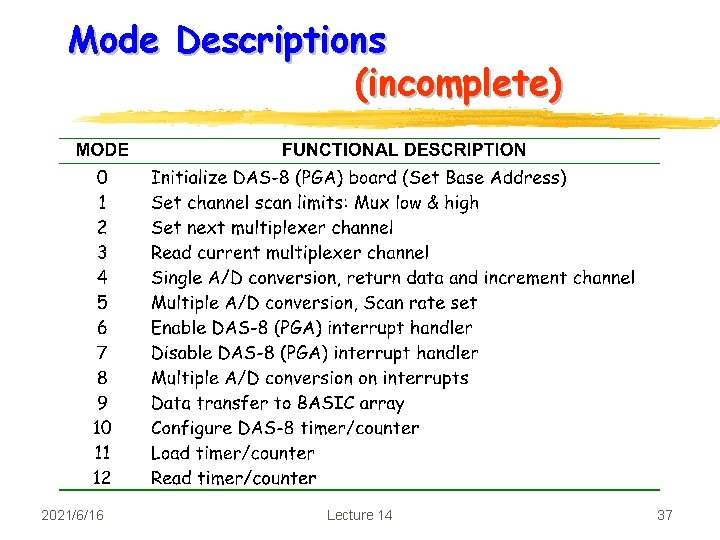

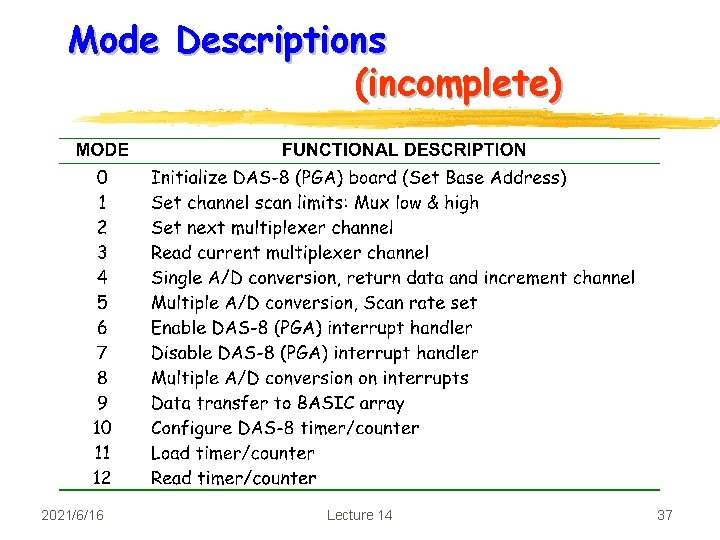

Mode Descriptions (incomplete) 2021/6/16 Lecture 14 37

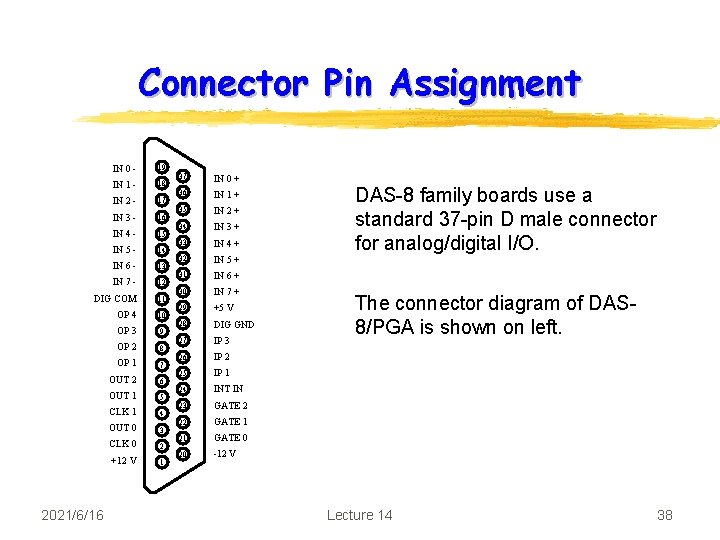

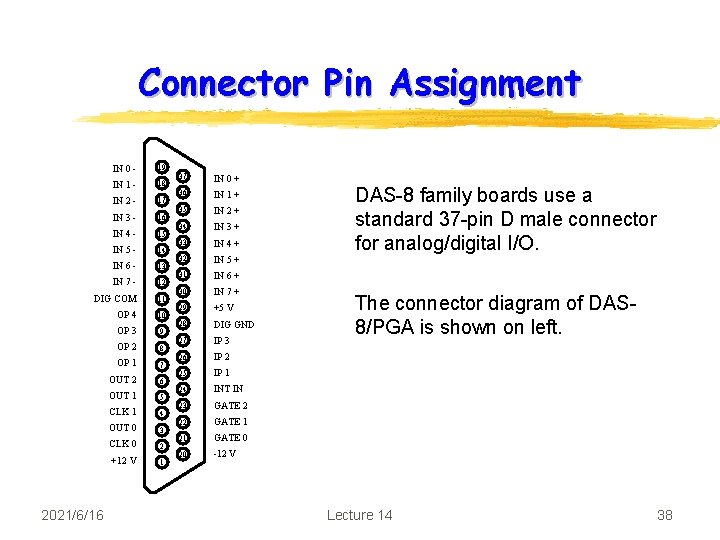

Connector Pin Assignment IN 0 - 19 IN 1 - 18 IN 2 - 17 IN 3 - 16 IN 4 - 15 IN 5 - 14 IN 6 - 13 IN 7 - 12 DIG COM 11 OP 4 10 OP 3 9 OP 2 8 OP 1 7 OUT 2 6 2021/6/16 OUT 1 5 CLK 1 4 OUT 0 3 CLK 0 2 +12 V 1 37 IN 0 + 36 IN 1 + 35 IN 2 + 34 IN 3 + 33 IN 4 + 32 IN 5 + 31 IN 6 + 30 IN 7 + 29 +5 V 28 DIG GND 27 IP 3 26 IP 2 25 IP 1 24 INT IN 23 GATE 2 22 GATE 1 21 GATE 0 20 -12 V DAS-8 family boards use a standard 37 -pin D male connector for analog/digital I/O. The connector diagram of DAS 8/PGA is shown on left. Lecture 14 38