Lecture 9 1 Building a FET Integrated Circuits

Lecture 9. 1 Building a FET

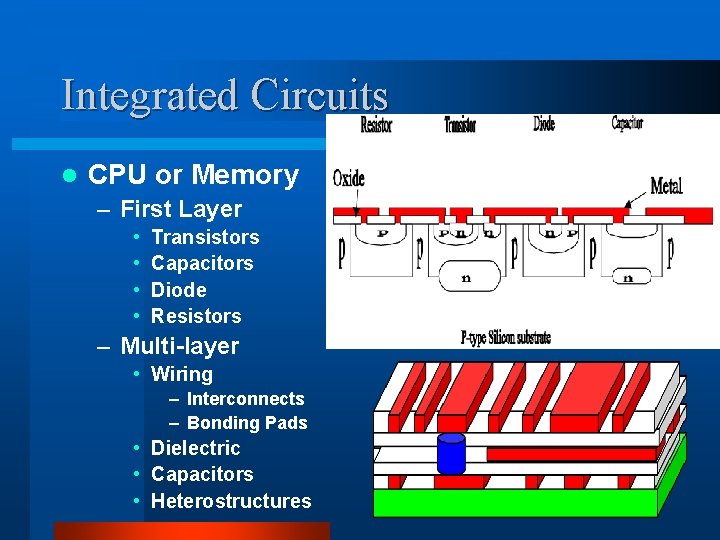

Integrated Circuits l CPU or Memory – First Layer • • Transistors Capacitors Diode Resistors – Multi-layer • Wiring – Interconnects – Bonding Pads • Dielectric • Capacitors • Heterostructures

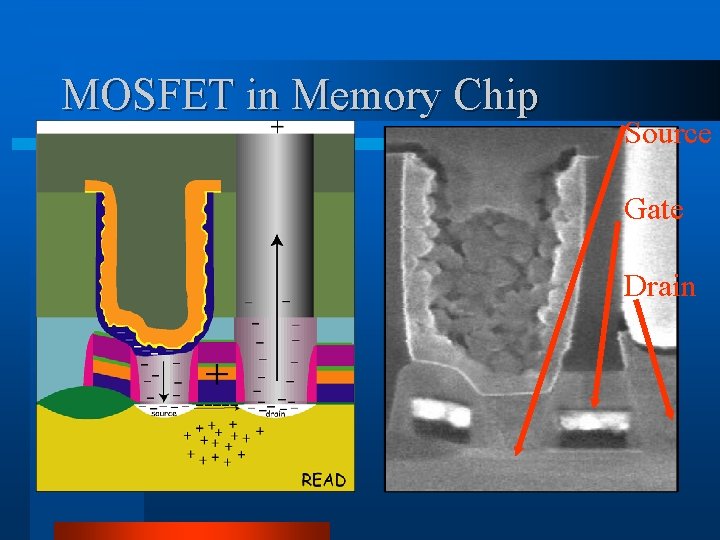

MOSFET in Memory Chip Source Gate Drain

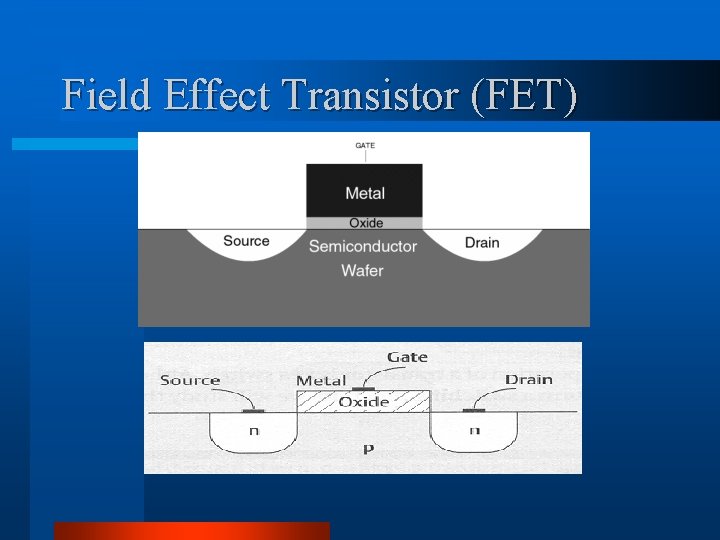

Field Effect Transistor (FET)

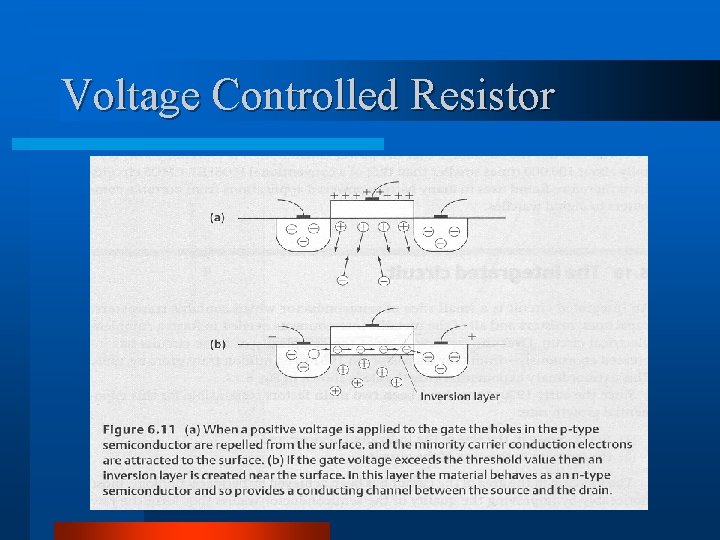

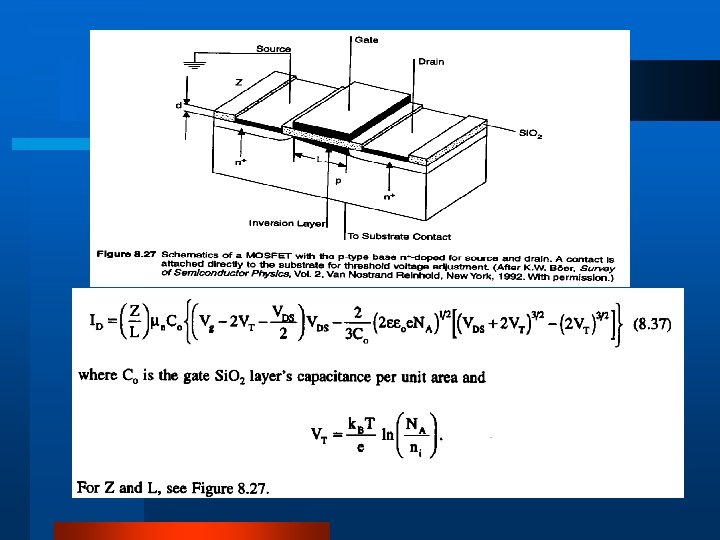

Voltage Controlled Resistor

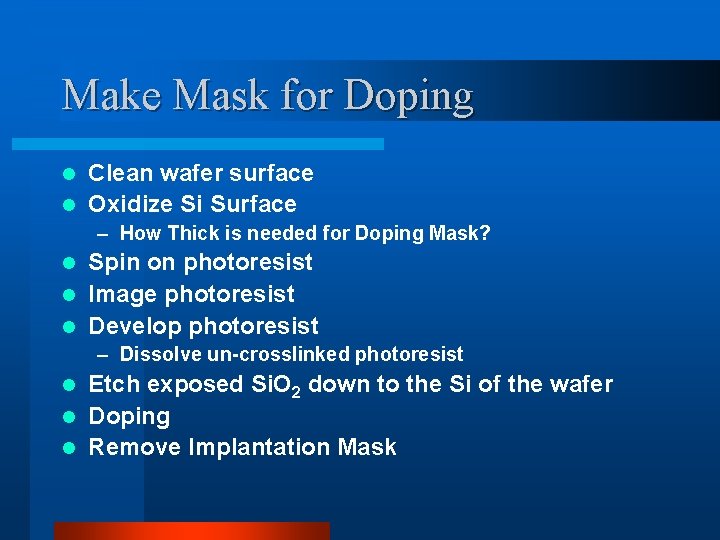

Make Mask for Doping Clean wafer surface l Oxidize Si Surface l – How Thick is needed for Doping Mask? Spin on photoresist l Image photoresist l Develop photoresist l – Dissolve un-crosslinked photoresist Etch exposed Si. O 2 down to the Si of the wafer l Doping l Remove Implantation Mask l

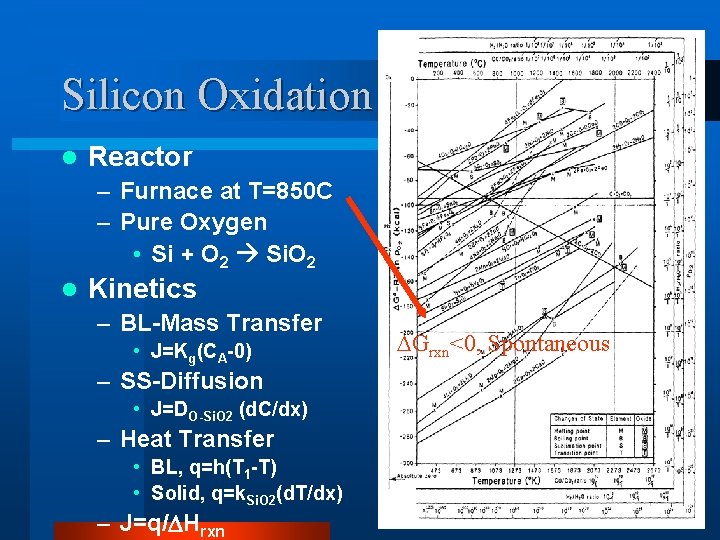

Silicon Oxidation l Reactor – Furnace at T=850 C – Pure Oxygen • Si + O 2 Si. O 2 l Kinetics – BL-Mass Transfer • J=Kg(CA-0) – SS-Diffusion • J=DO-Si. O 2 (d. C/dx) – Heat Transfer • BL, q=h(T 1 -T) • Solid, q=k. Si. O 2(d. T/dx) – J=q/ Hrxn Grxn<0, Spontaneous

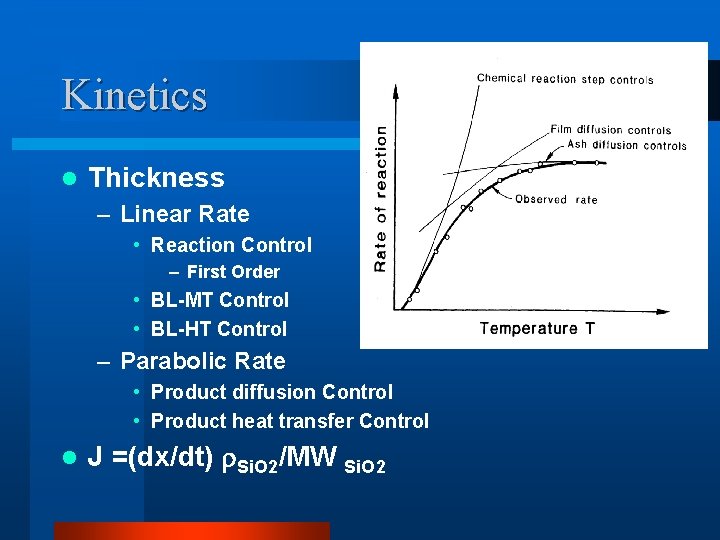

Kinetics l Thickness – Linear Rate • Reaction Control – First Order • BL-MT Control • BL-HT Control – Parabolic Rate • Product diffusion Control • Product heat transfer Control l J =(dx/dt) Si. O 2/MW Si. O 2

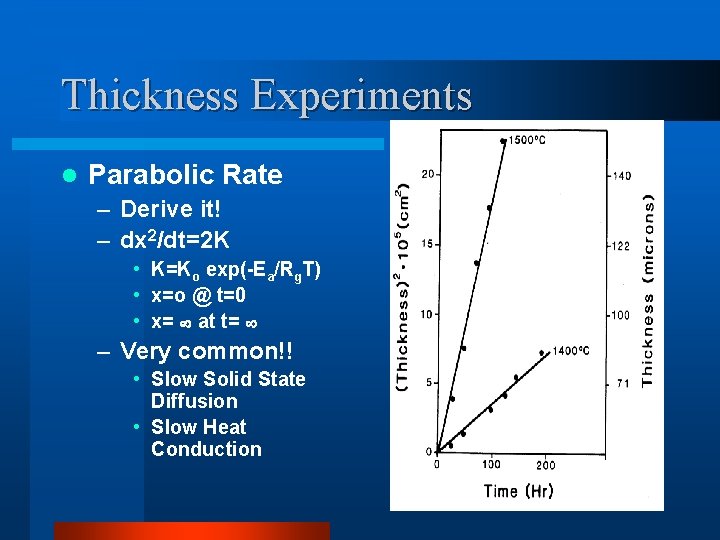

Thickness Experiments l Parabolic Rate – Derive it! – dx 2/dt=2 K • K=Ko exp(-Ea/Rg. T) • x=o @ t=0 • x= at t= – Very common!! • Slow Solid State Diffusion • Slow Heat Conduction

Mask Thickness l l l To effectively prevent ions penetrating in thick zone Relatively thick Oxide Protection layer Patterned Thinning (etching) of Oxide Protection layer over implantation zone Remove oxide layer with impurities inside

![Mask Thickness l Transmission through mask – T=1/2 erfc[(x-xave)/ 2 x] l To stop Mask Thickness l Transmission through mask – T=1/2 erfc[(x-xave)/ 2 x] l To stop](http://slidetodoc.com/presentation_image/d39e4e3076c831fd729521691cff6a24/image-12.jpg)

Mask Thickness l Transmission through mask – T=1/2 erfc[(x-xave)/ 2 x] l To stop 99. 99% of implanted materials, T=10 -4 l Solve for x, the thickness to stop 99. 99% of ions.

Si. O 2 Mask Thickness

Si 3 N 4 Mask Thickness

Photoresist Mask Thickness

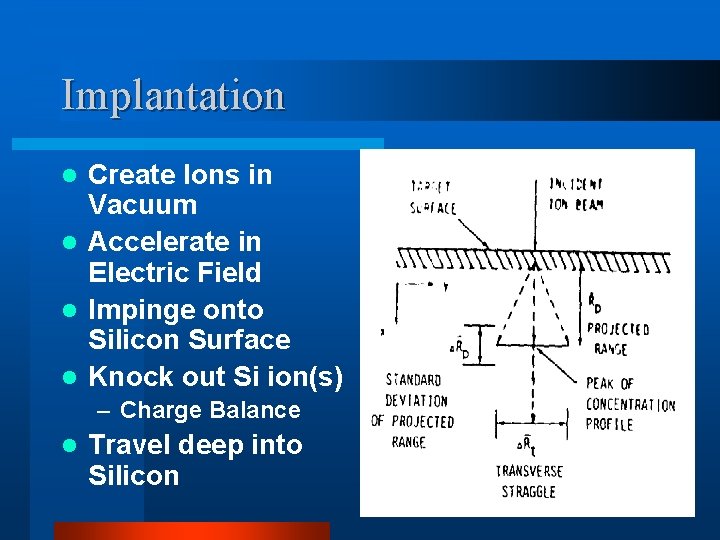

Implantation Create Ions in Vacuum l Accelerate in Electric Field l Impinge onto Silicon Surface l Knock out Si ion(s) l – Charge Balance l Travel deep into Silicon

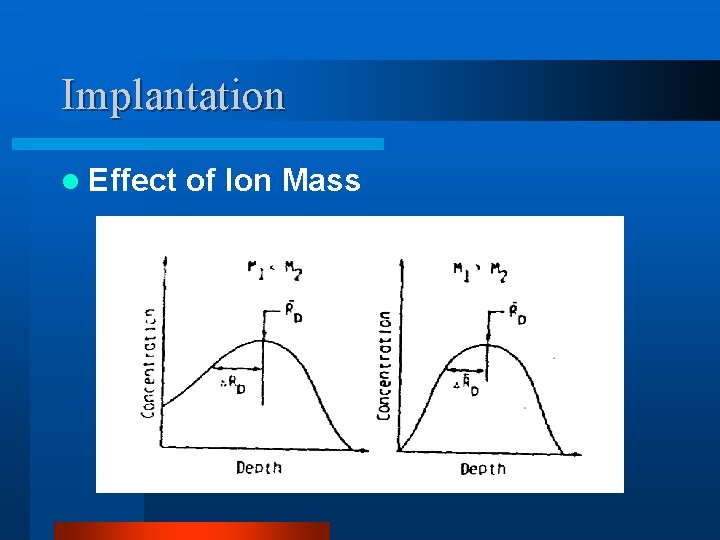

Implantation l Effect of Ion Mass

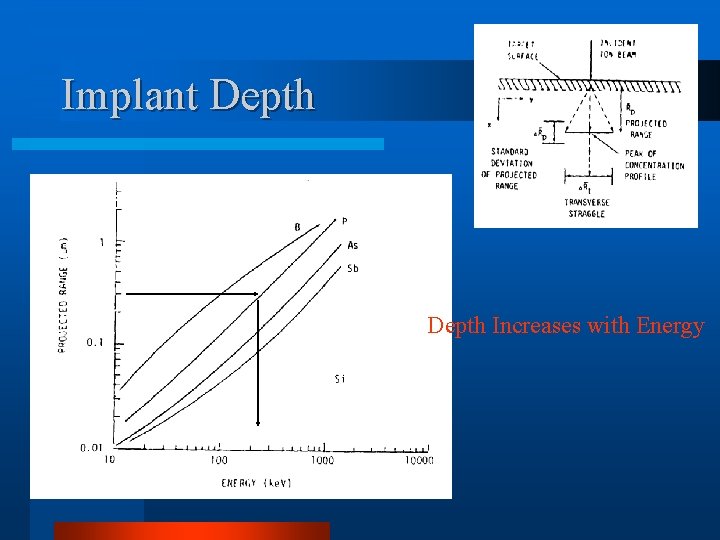

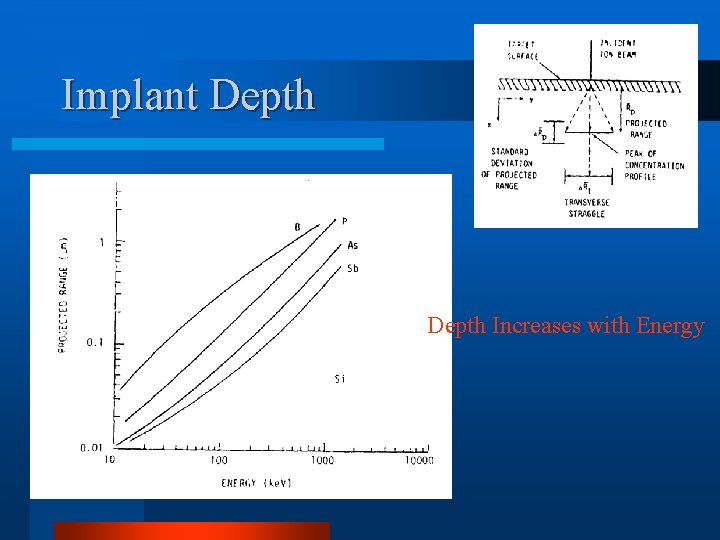

Implant Depth Increases with Energy

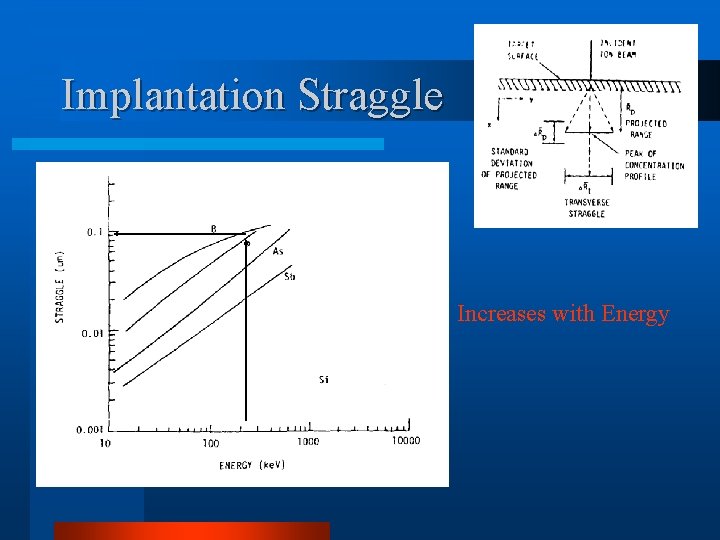

Implantation Straggle Increases with Energy

![Implantation Concentration Profile Probability Based l N(x)=Nmax exp[(x-xave)2/2 x 2] l Nmax=(Ndose/[ (2 ) Implantation Concentration Profile Probability Based l N(x)=Nmax exp[(x-xave)2/2 x 2] l Nmax=(Ndose/[ (2 )](http://slidetodoc.com/presentation_image/d39e4e3076c831fd729521691cff6a24/image-20.jpg)

Implantation Concentration Profile Probability Based l N(x)=Nmax exp[(x-xave)2/2 x 2] l Nmax=(Ndose/[ (2 ) x])~(0. 4 Ndose/ x) l Ndose=Qdose/e l Qdose= current applied/cm 2 l σx = projected straggle l

Remove Implantation Mask l Chemical Mechanical Polishing – Stop etch at the desired thickness of the Gate Oxide l Dry Etching

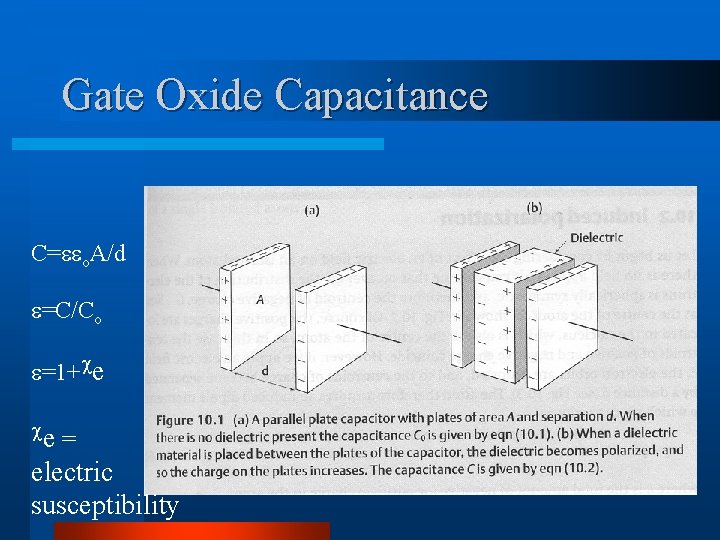

Gate Oxide l Capacitor connecting Gate to center of npn or pnp heterojunction l Capacitance – Area – Thickness – Dielectric constant of oxide

Gate Oxide Capacitance C= o. A/d =C/Co =1+ e e = electric susceptibility

Metalization l Transistor Contacts – Base – Emitter – Gate l Planarize/Polish layer to get Flat Surface for next lithography Step

Diffusion l Deposition of B or P on surface l Heat and Hold for period of time – Solid State Diffusion – d. C/dt=D d 2 C/dx 2 • C=Co at x=0 • C=0 at x= – C=Co(1 -erf[x/ (4 Dt)]) l Etch excess B or P from surface

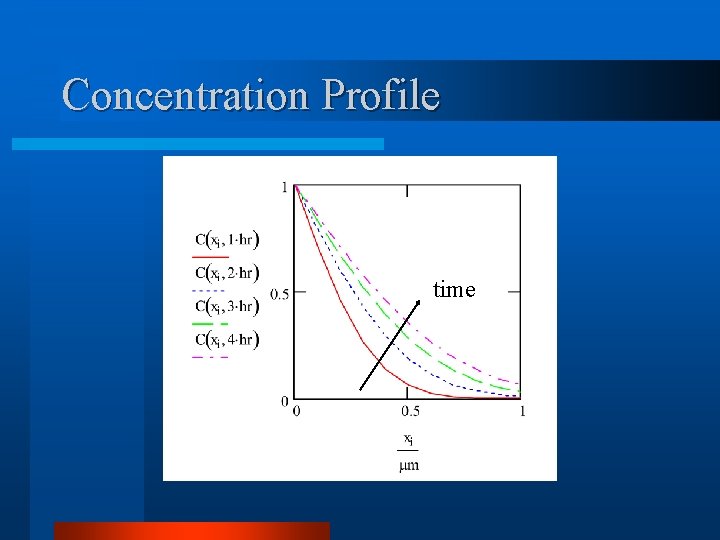

Concentration Profile time

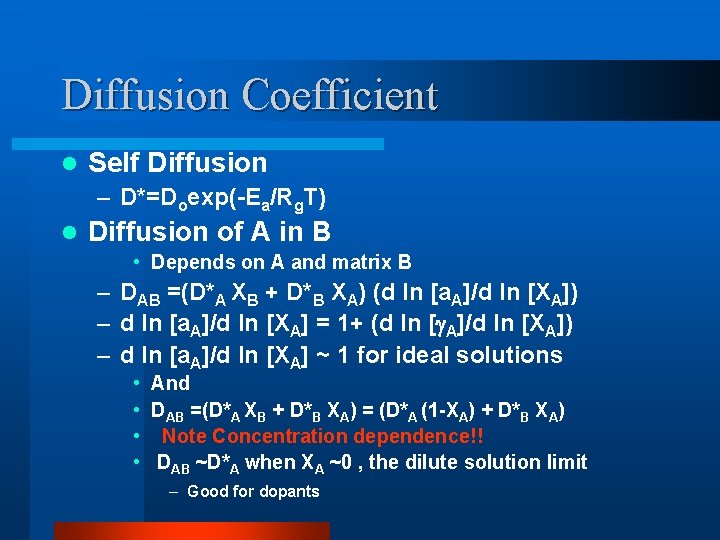

Diffusion Coefficient l Self Diffusion – D*=Doexp(-Ea/Rg. T) l Diffusion of A in B • Depends on A and matrix B – DAB =(D*A XB + D*B XA) (d ln [a. A]/d ln [XA]) – d ln [a. A]/d ln [XA] = 1+ (d ln [ A]/d ln [XA]) – d ln [a. A]/d ln [XA] ~ 1 for ideal solutions • And • DAB =(D*A XB + D*B XA) = (D*A (1 -XA) + D*B XA) • Note Concentration dependence!! • DAB ~D*A when XA ~0 , the dilute solution limit – Good for dopants

Implant Depth Increases with Energy

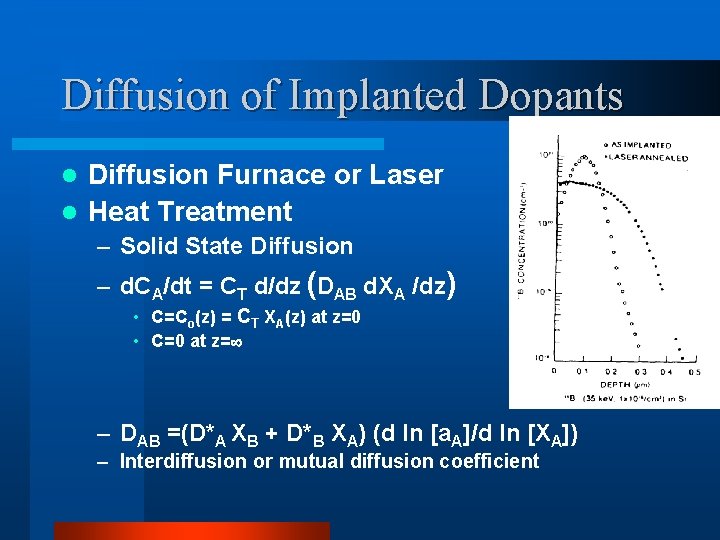

Diffusion of Implanted Dopants Diffusion Furnace or Laser l Heat Treatment l – Solid State Diffusion – d. CA/dt = CT d/dz (DAB d. XA /dz) • C=Co(z) = CT XA(z) at z=0 • C=0 at z= – DAB =(D*A XB + D*B XA) (d ln [a. A]/d ln [XA]) – Interdiffusion or mutual diffusion coefficient

- Slides: 30