Lecture 7 1 Device Physics Transistor Integrated Circuit

- Slides: 32

Lecture 7. 1 Device Physics – Transistor Integrated Circuit

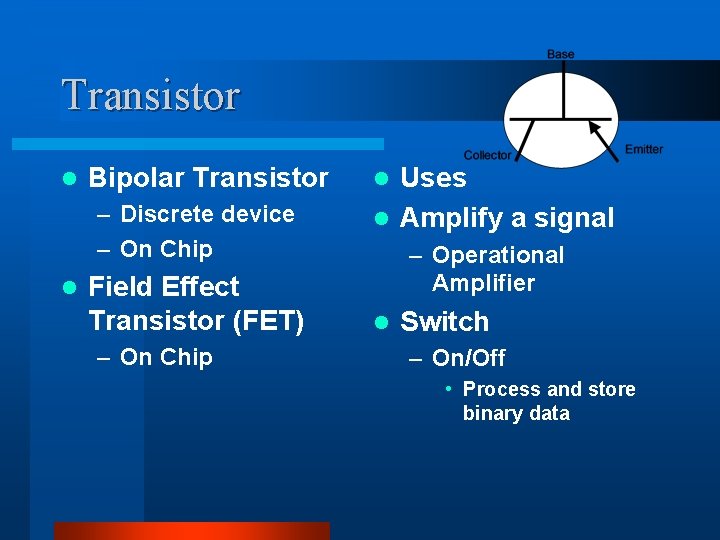

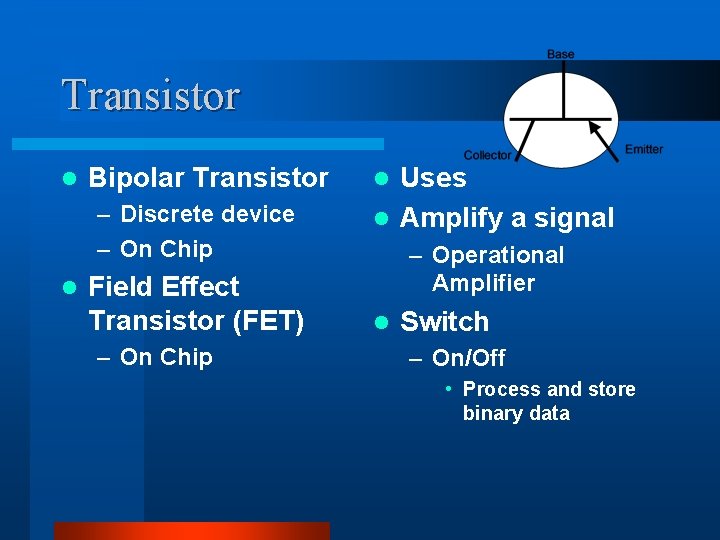

Transistor l Bipolar Transistor – Discrete device – On Chip l Field Effect Transistor (FET) – On Chip Uses l Amplify a signal l – Operational Amplifier l Switch – On/Off • Process and store binary data

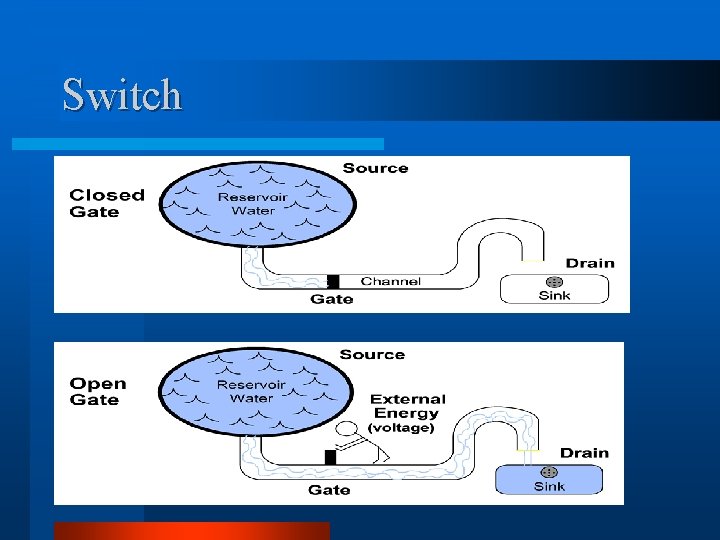

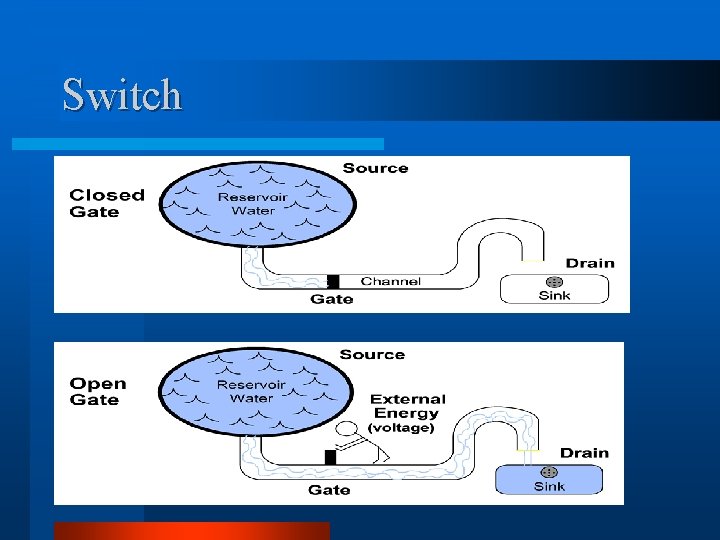

Switch

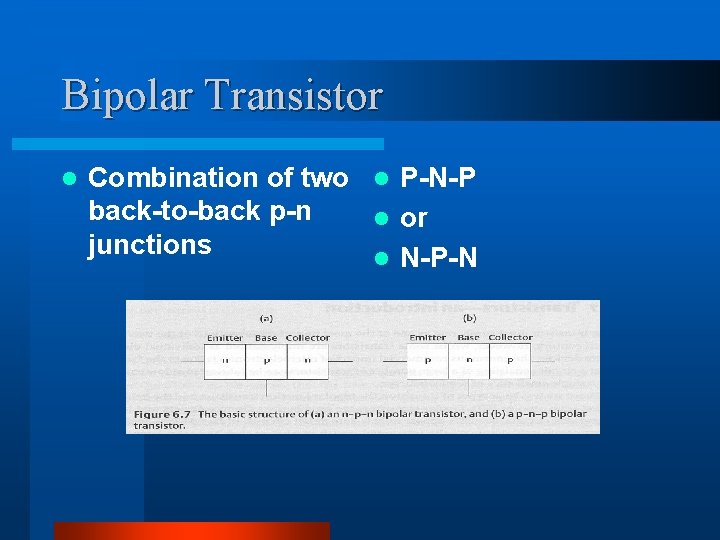

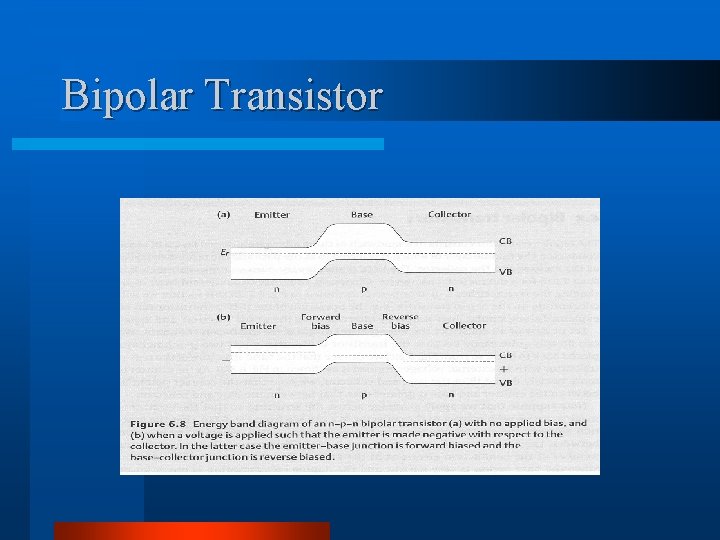

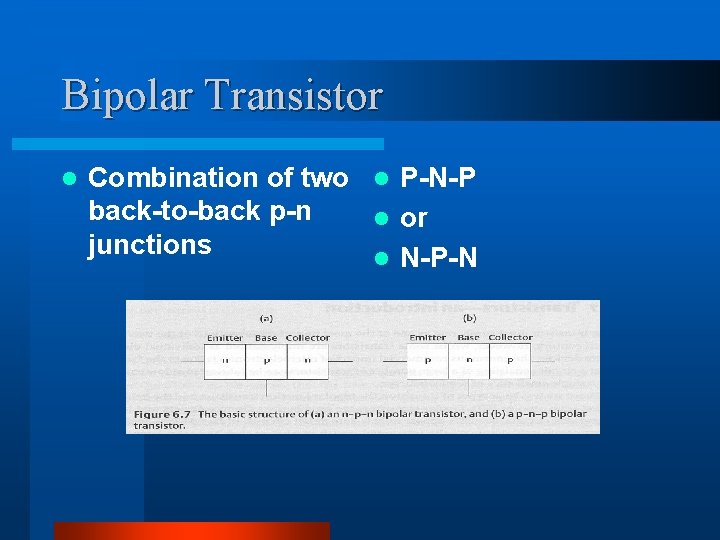

Bipolar Transistor l Combination of two l P-N-P back-to-back p-n l or junctions l N-P-N

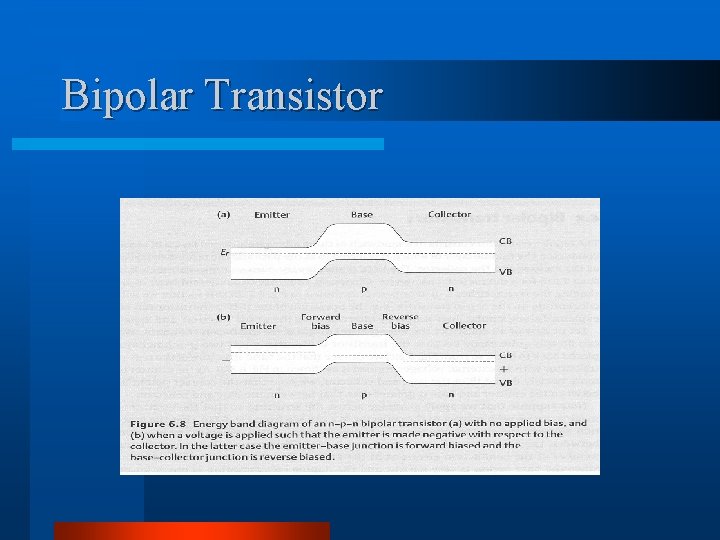

Bipolar Transistor

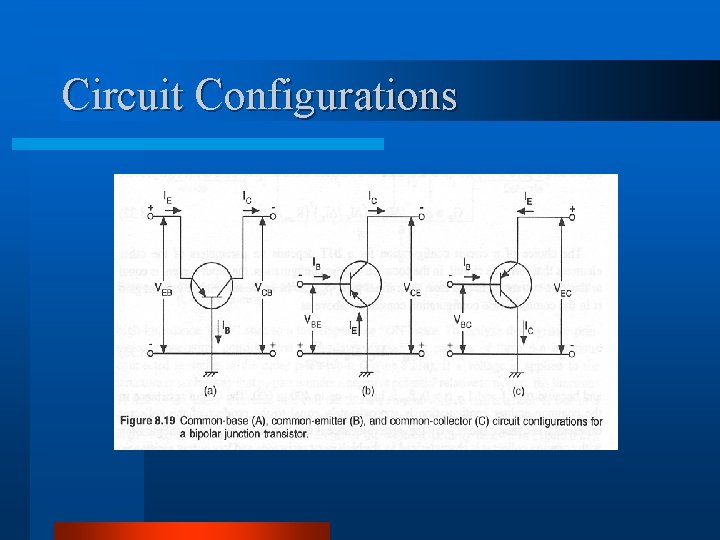

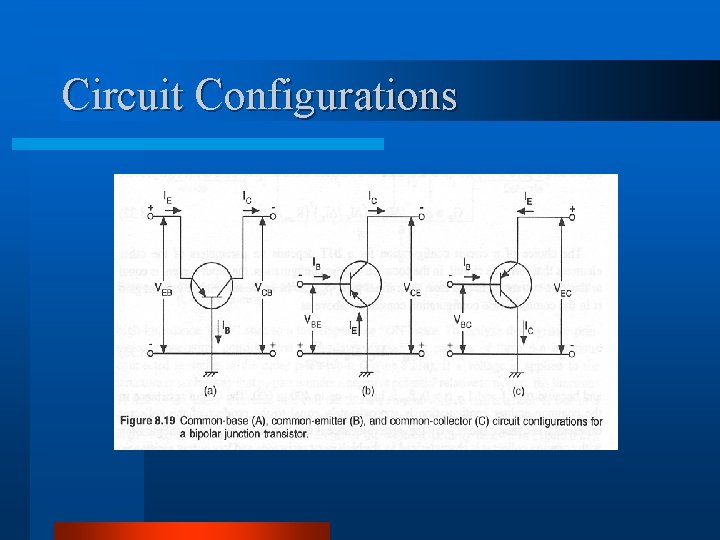

Circuit Configurations

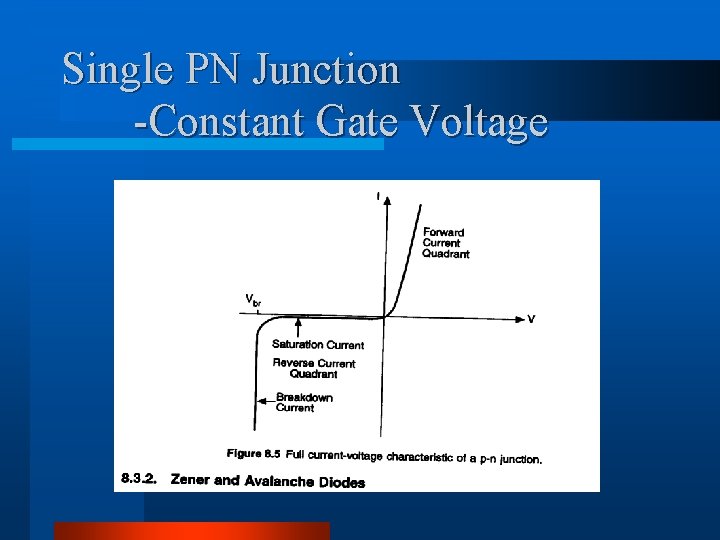

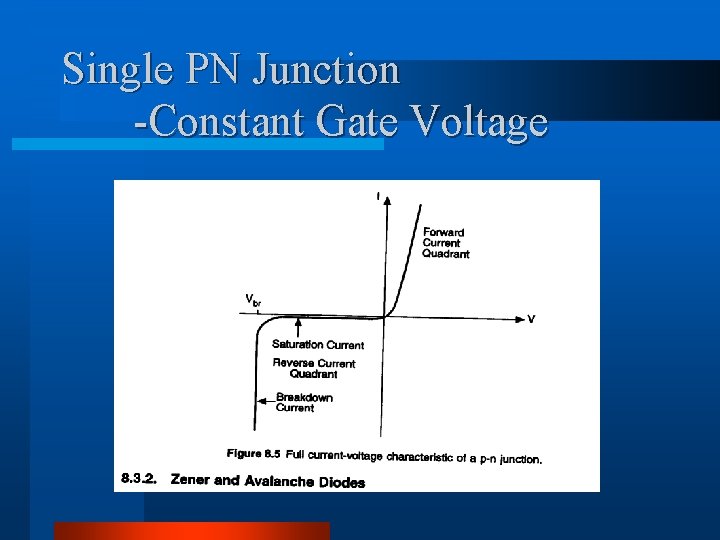

Single PN Junction -Constant Gate Voltage

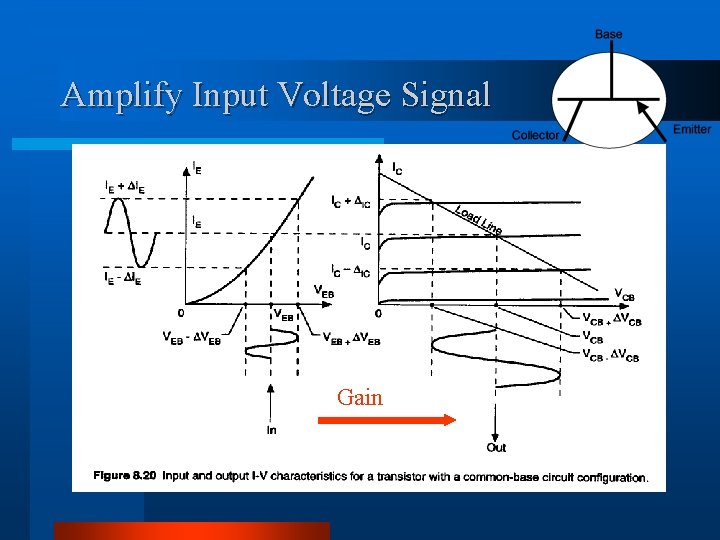

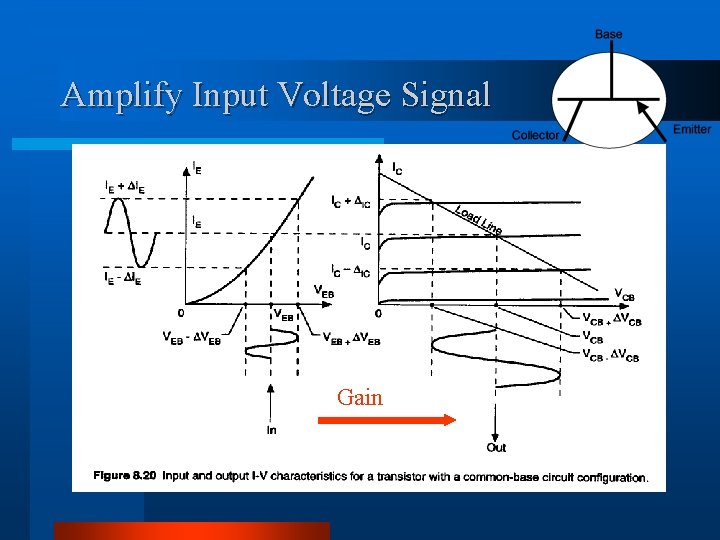

Amplify Input Voltage Signal Gain

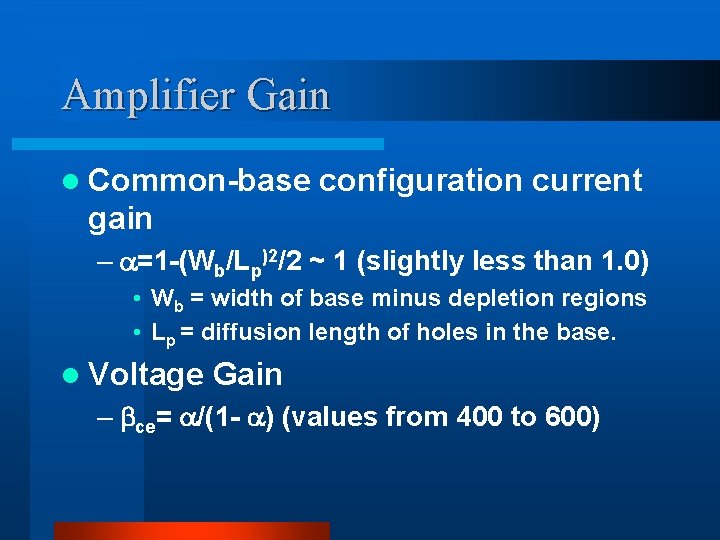

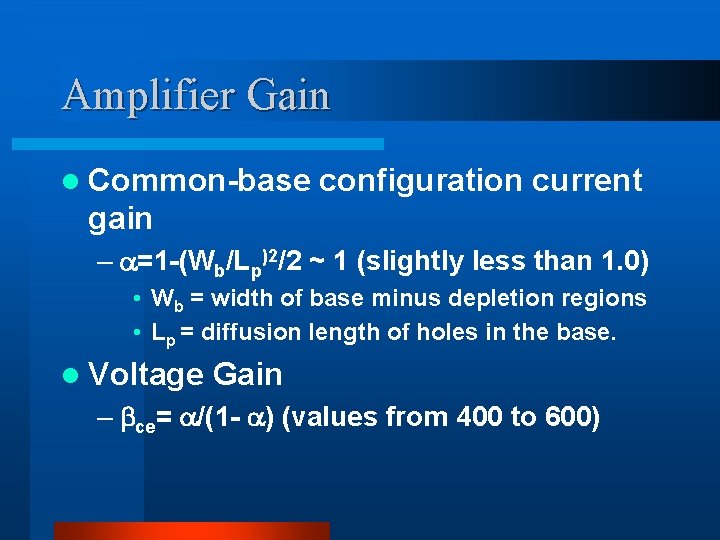

Amplifier Gain l Common-base configuration current gain – =1 -(Wb/Lp)2/2 ~ 1 (slightly less than 1. 0) • Wb = width of base minus depletion regions • Lp = diffusion length of holes in the base. l Voltage Gain – ce= /(1 - ) (values from 400 to 600)

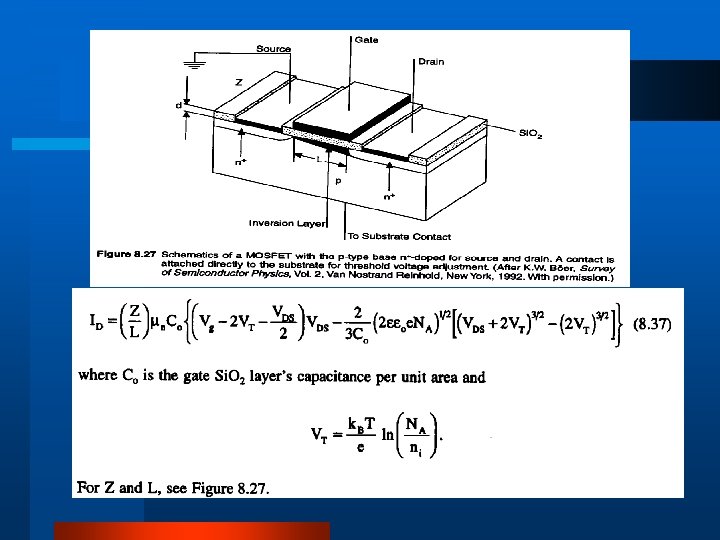

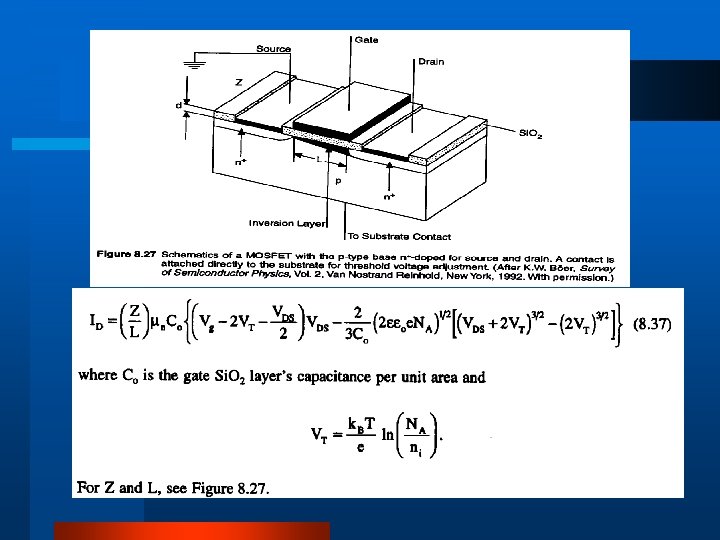

FET- (Field Effect Transistor) l MOSFET – Metal oxide semiconductor field effect transistor l l – Metal-insulatorsemiconductor FET l MOST – Metal-oxide semiconductor transistor IGFET – Insulated-gate FET l MISFET NMOS or PMOS l JFET – Junction FET

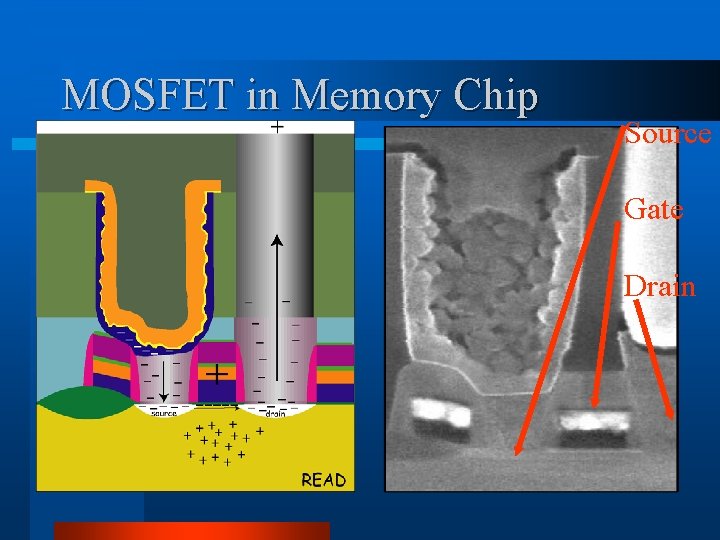

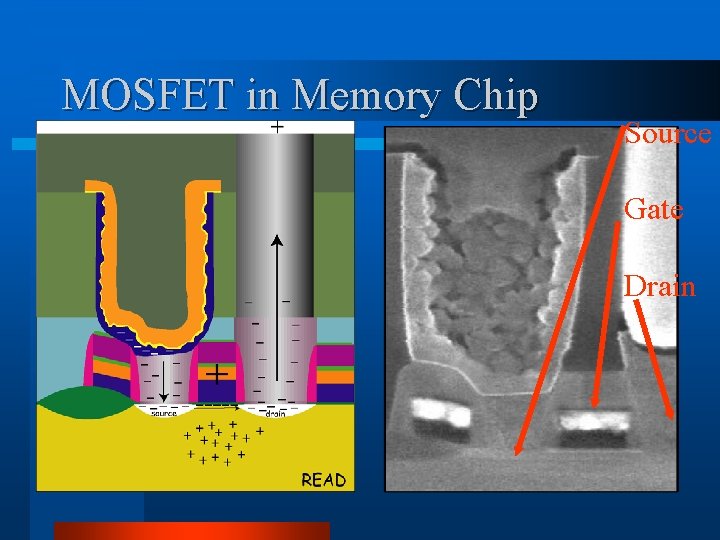

MOSFET in Memory Chip Source Gate Drain

Field Effect Transistor (FET)

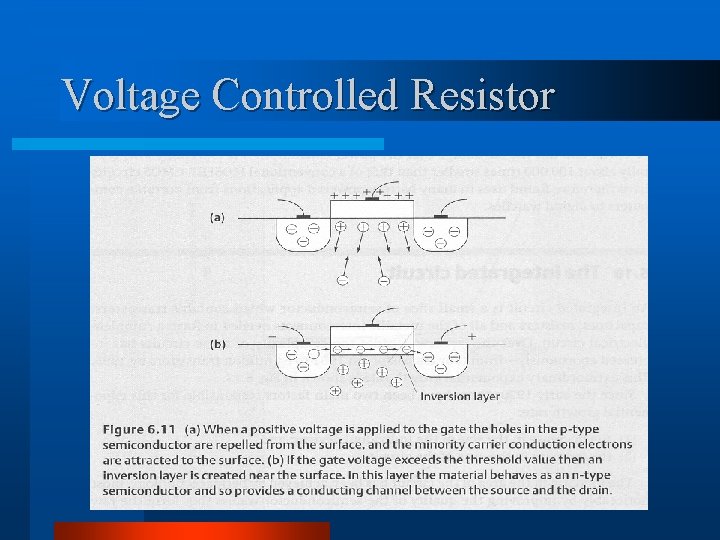

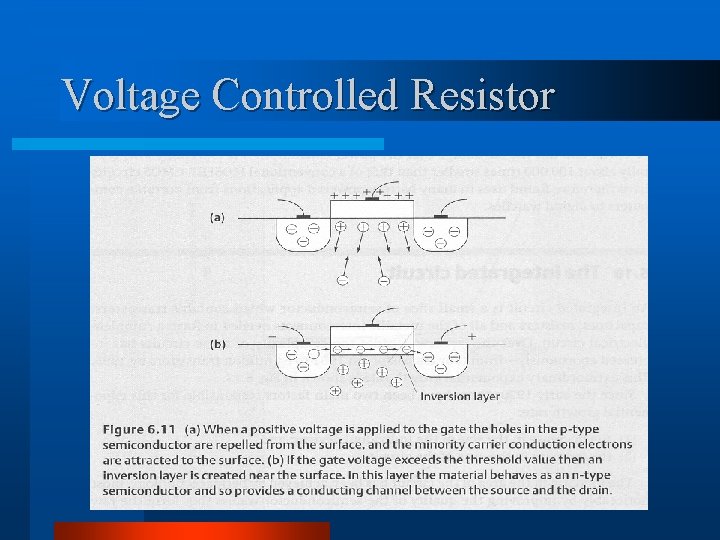

Voltage Controlled Resistor

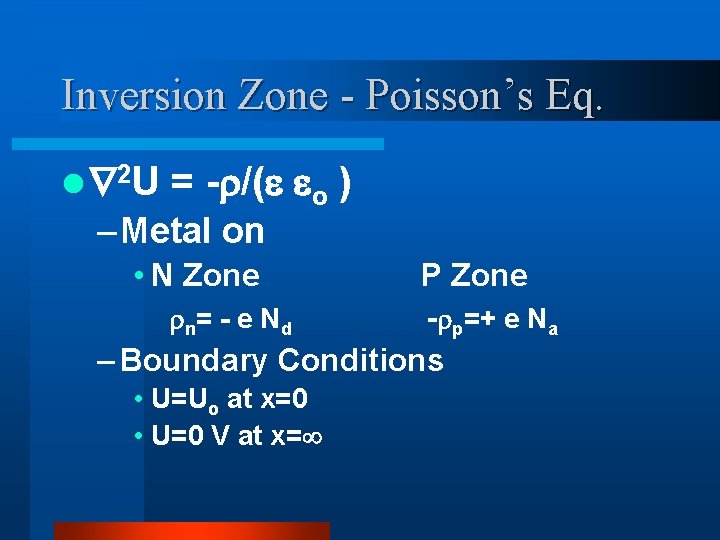

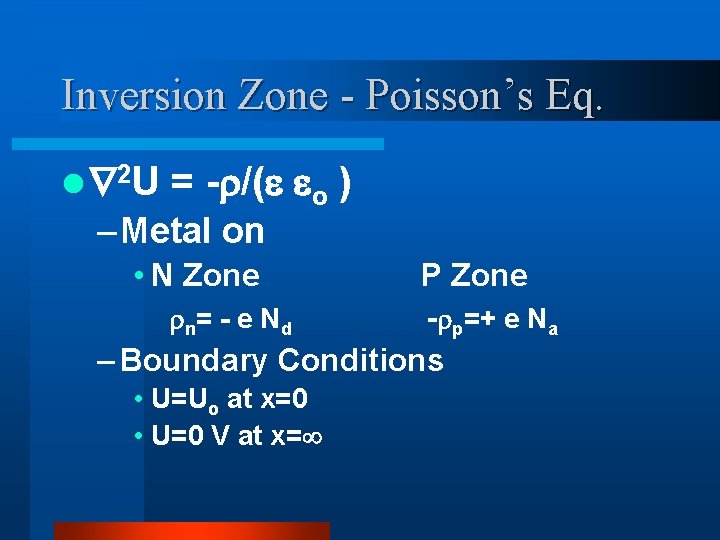

Inversion Zone - Poisson’s Eq. l 2 U = - /( o ) – Metal on • N Zone P Zone n = - e Nd - p=+ e Na – Boundary Conditions • U=Uo at x=0 • U=0 V at x=

Inversion Layer

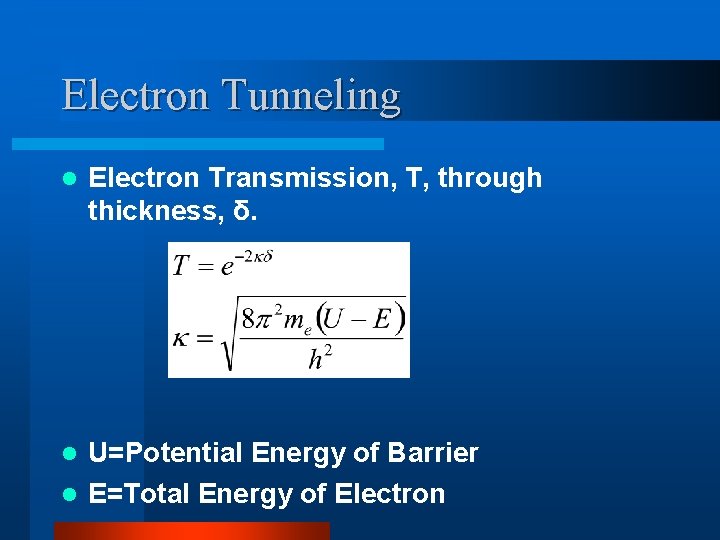

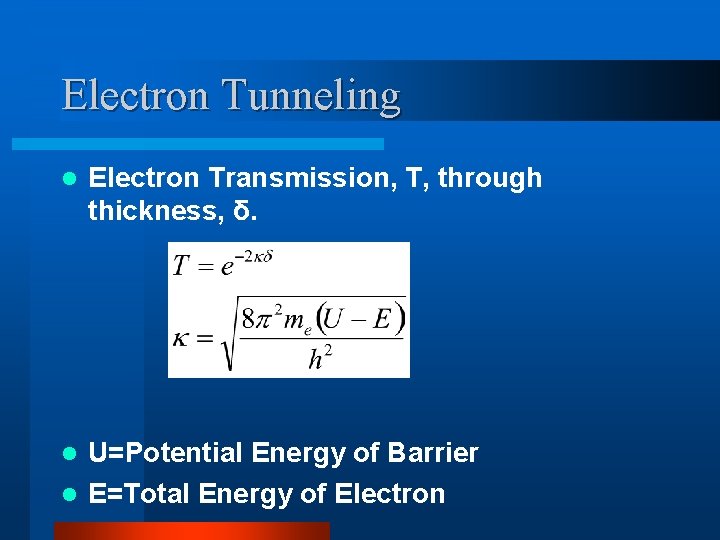

Electron Tunneling l Electron Transmission, T, through thickness, δ. U=Potential Energy of Barrier l E=Total Energy of Electron l

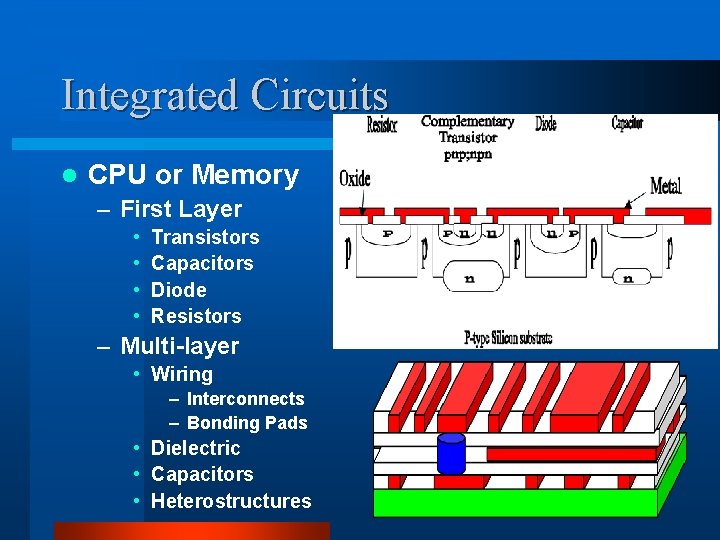

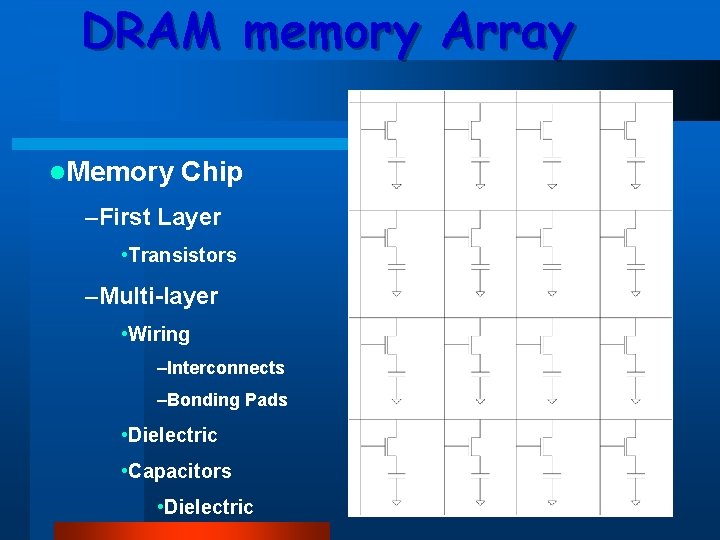

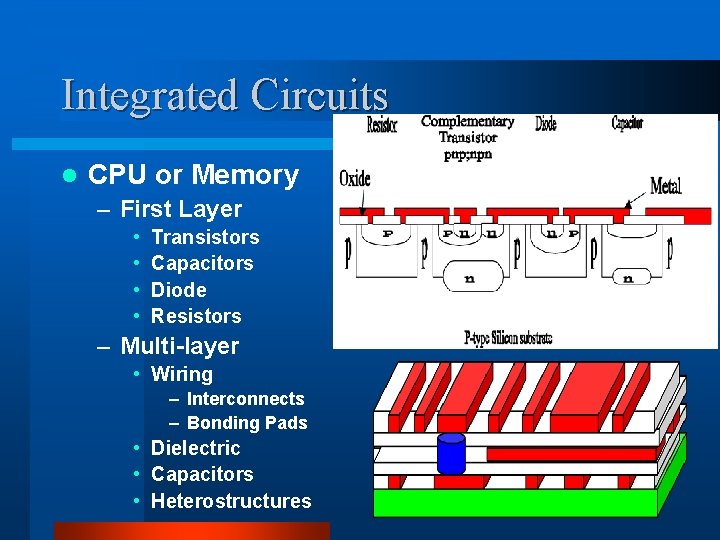

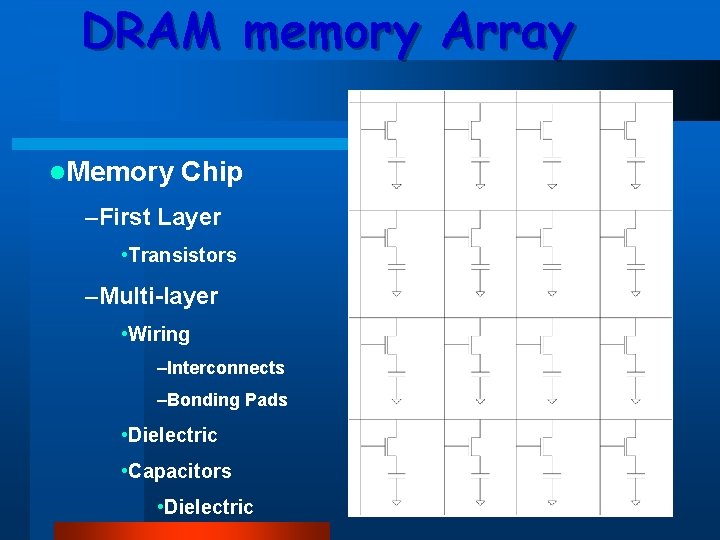

Integrated Circuits l CPU or Memory – First Layer • • Transistors Capacitors Diode Resistors – Multi-layer • Wiring – Interconnects – Bonding Pads • Dielectric • Capacitors • Heterostructures

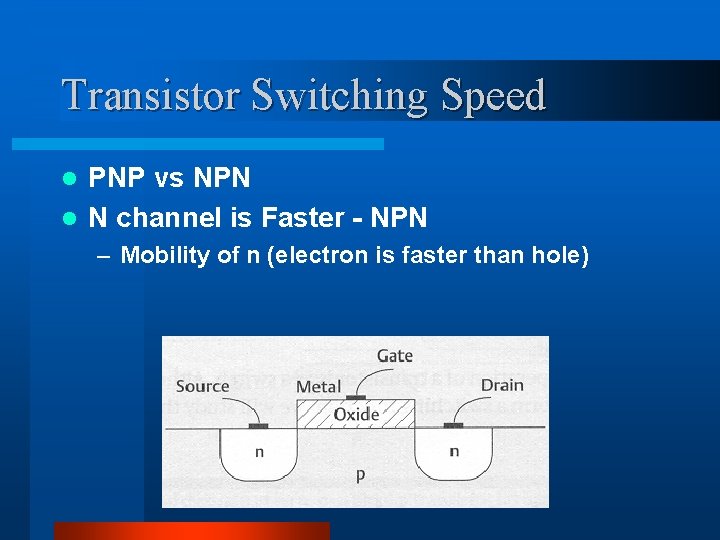

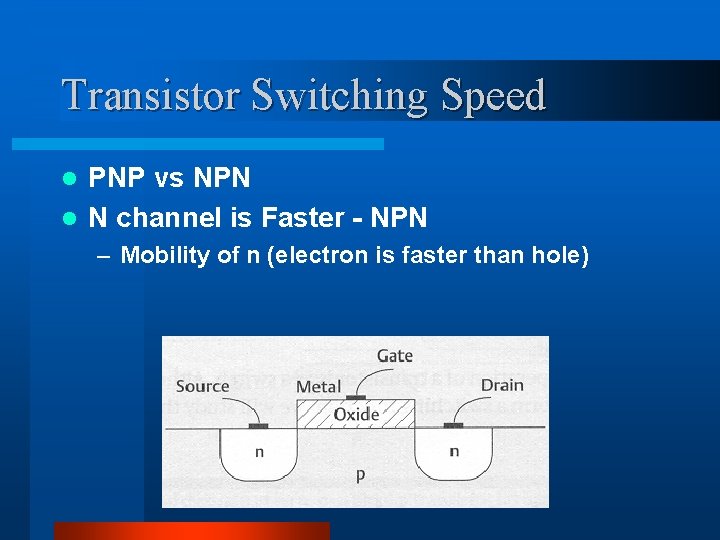

Transistor Switching Speed PNP vs NPN l N channel is Faster - NPN l – Mobility of n (electron is faster than hole)

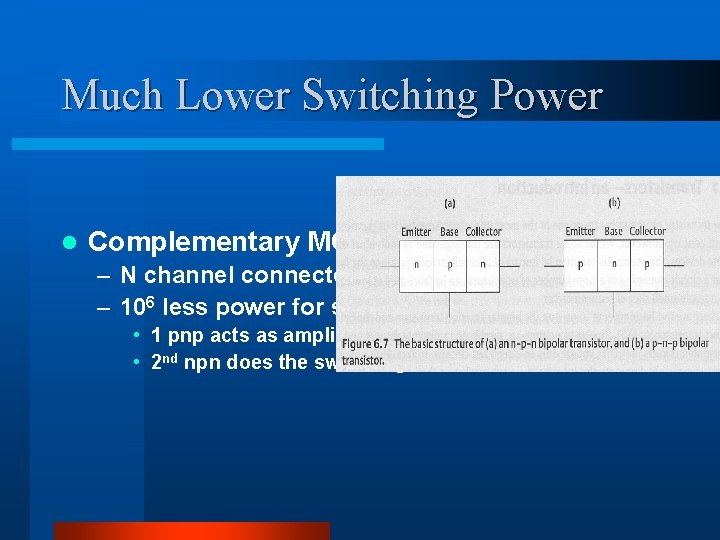

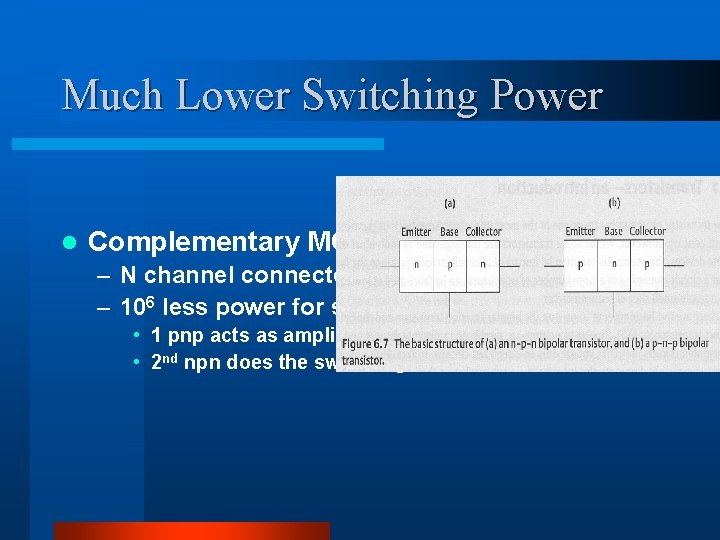

Much Lower Switching Power l Complementary MOS – N channel connected to P channel – 106 less power for switching • 1 pnp acts as amplifier • 2 nd npn does the switching

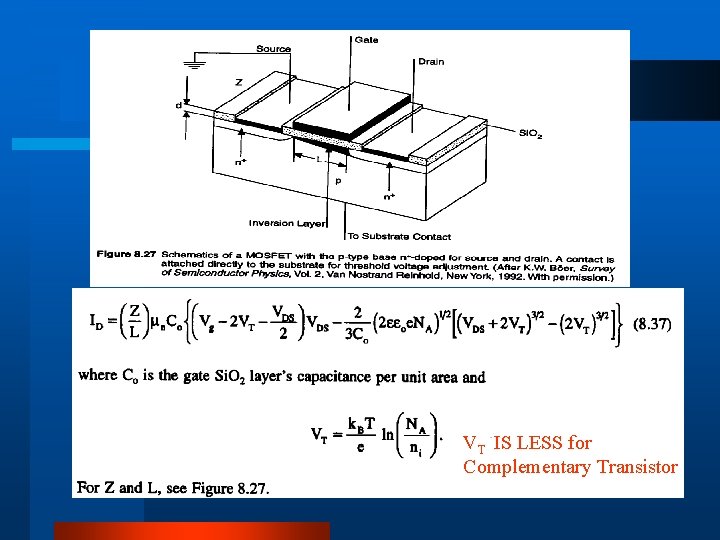

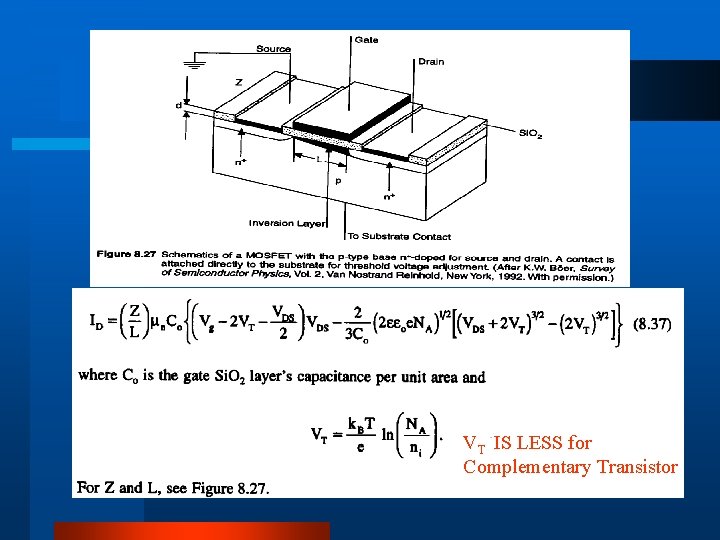

VT IS LESS for Complementary Transistor

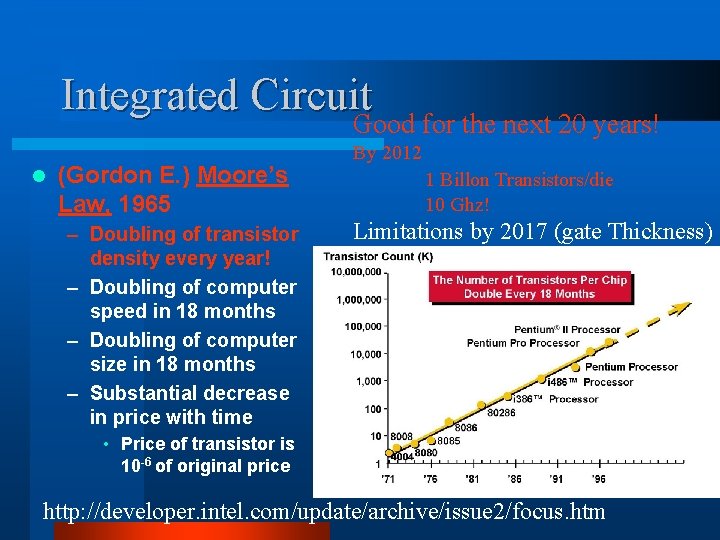

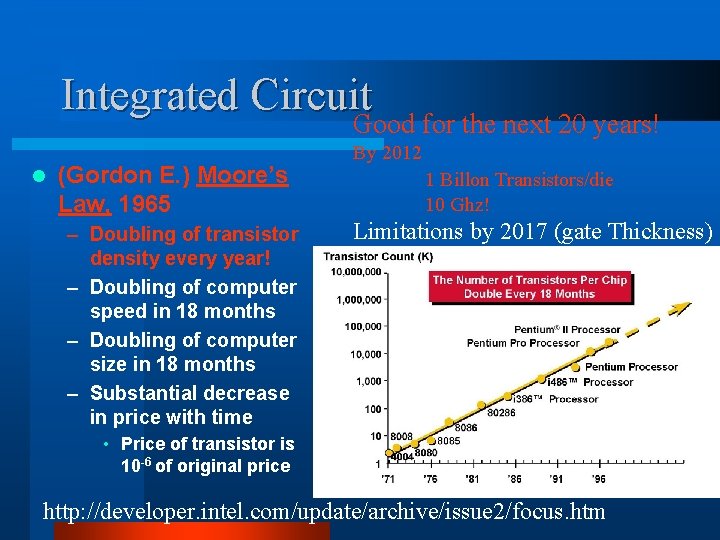

Integrated Circuit Good for the next 20 years! l (Gordon E. ) Moore’s Law, 1965 – Doubling of transistor density every year! – Doubling of computer speed in 18 months – Doubling of computer size in 18 months – Substantial decrease in price with time By 2012 1 Billon Transistors/die 10 Ghz! Limitations by 2017 (gate Thickness) • Price of transistor is 10 -6 of original price http: //developer. intel. com/update/archive/issue 2/focus. htm

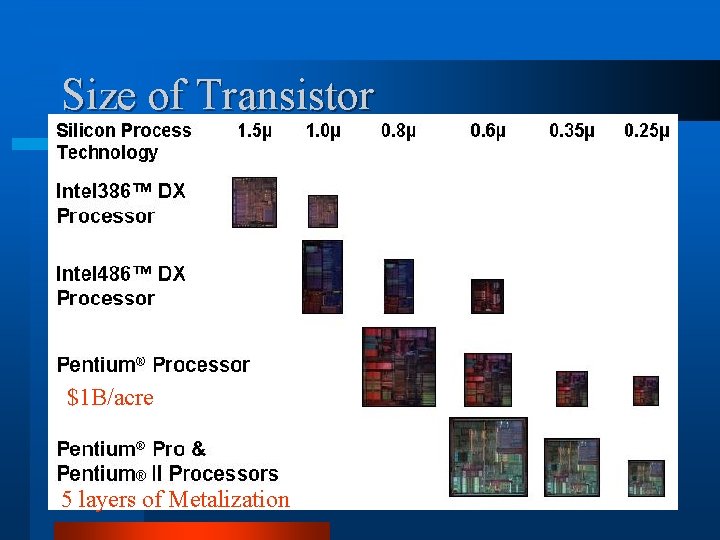

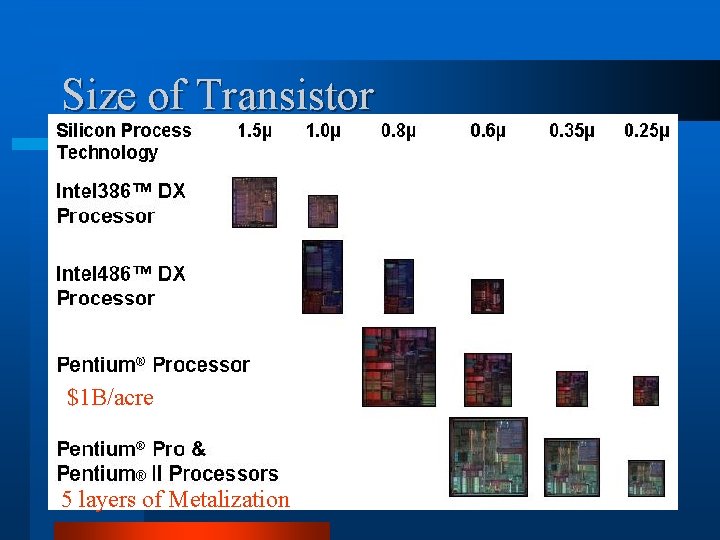

Size of Transistor $1 B/acre 5 layers of Metalization

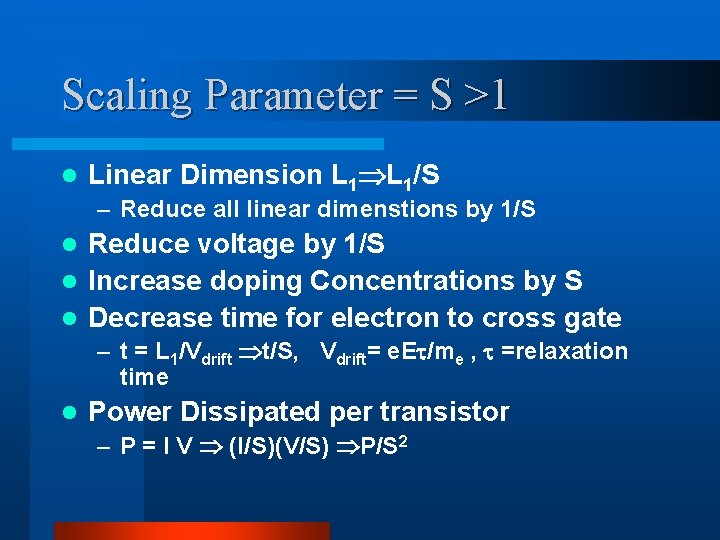

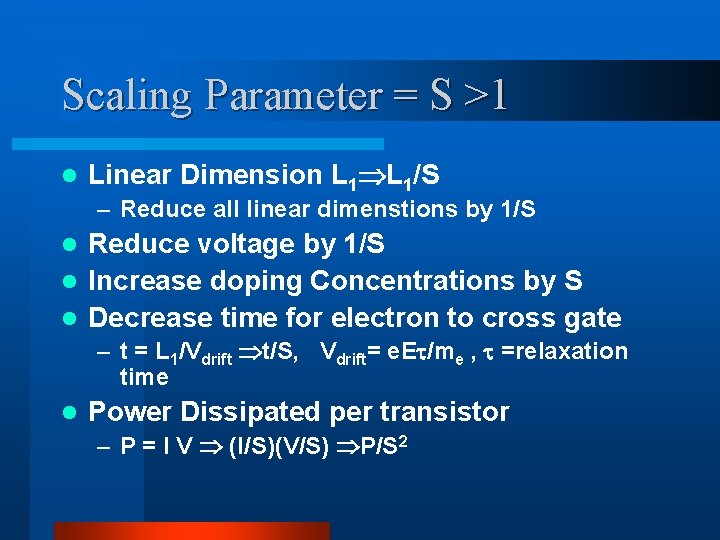

Scaling Parameter = S >1 l Linear Dimension L 1/S – Reduce all linear dimenstions by 1/S Reduce voltage by 1/S l Increase doping Concentrations by S l Decrease time for electron to cross gate l – t = L 1/Vdrift t/S, Vdrift= e. E /me , =relaxation time l Power Dissipated per transistor – P = I V (I/S)(V/S) P/S 2

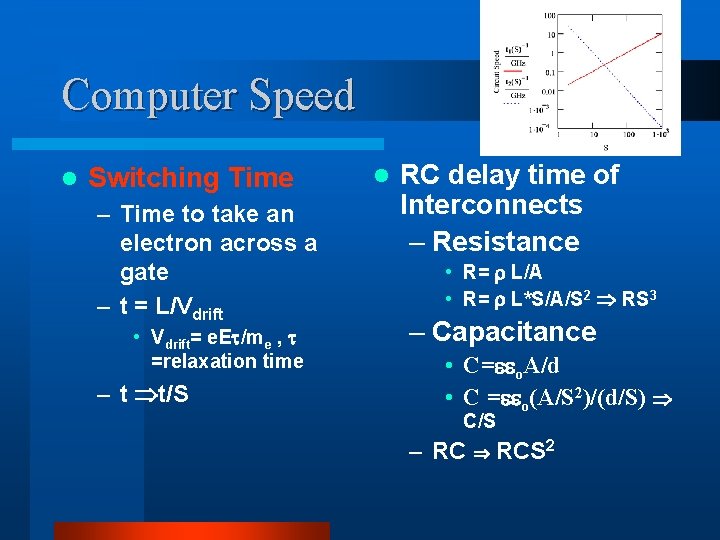

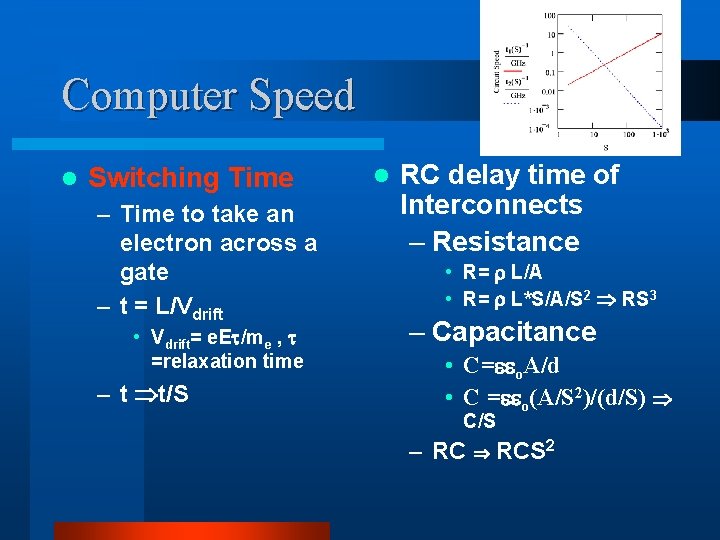

Computer Speed l Switching Time – Time to take an electron across a gate – t = L/Vdrift • Vdrift= e. E /me , =relaxation time – t t/S l RC delay time of Interconnects – Resistance • R= L/A • R= L*S/A/S 2 RS 3 – Capacitance • C= o. A/d • C = o(A/S 2)/(d/S) C/S – RC RCS 2

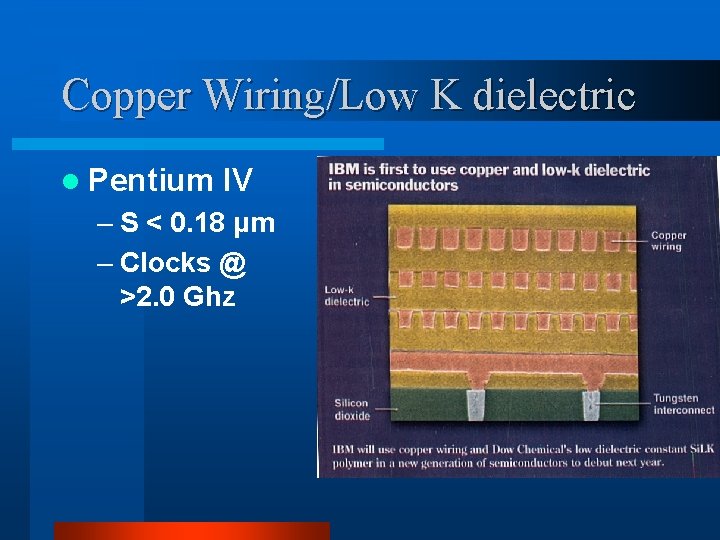

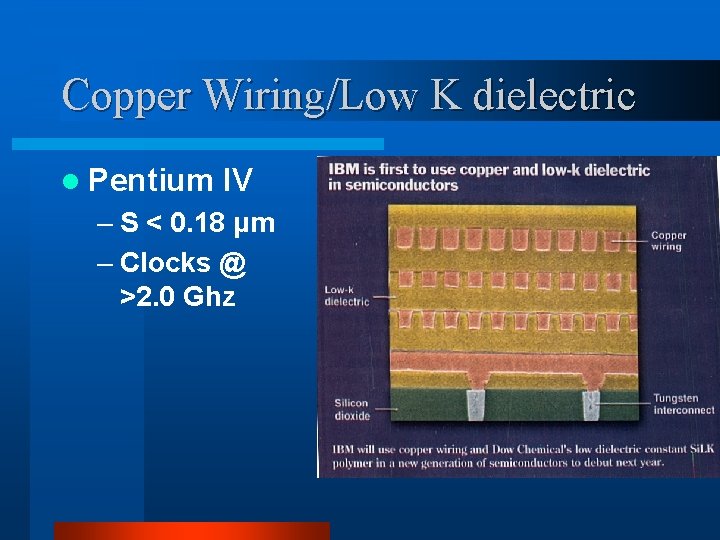

Copper Wiring/Low K dielectric l Pentium IV – S < 0. 18 μm – Clocks @ >2. 0 Ghz

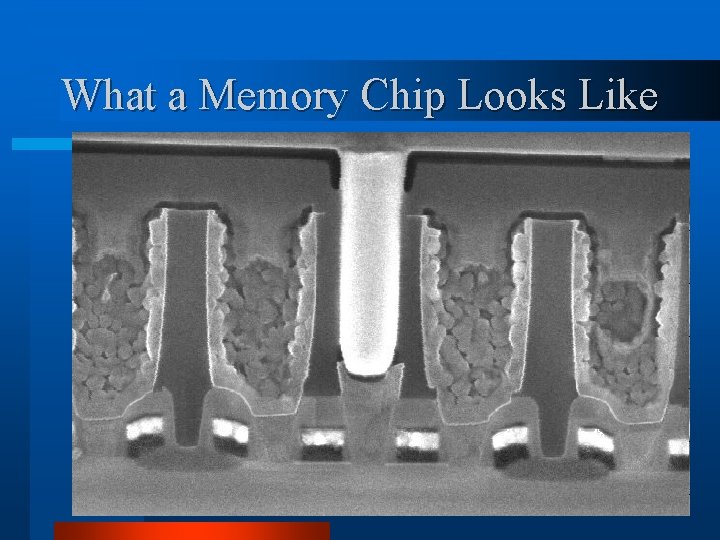

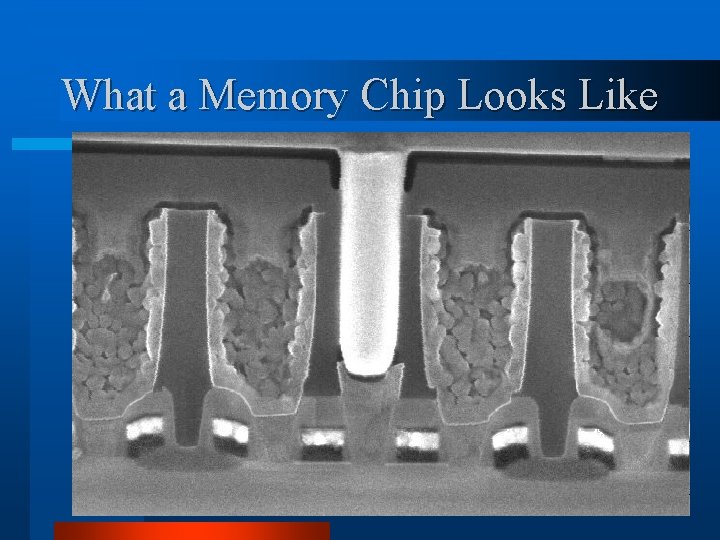

What a Memory Chip Looks Like

DRAM memory Array l. Memory Chip –First Layer • Transistors –Multi-layer • Wiring –Interconnects –Bonding Pads • Dielectric • Capacitors • Dielectric

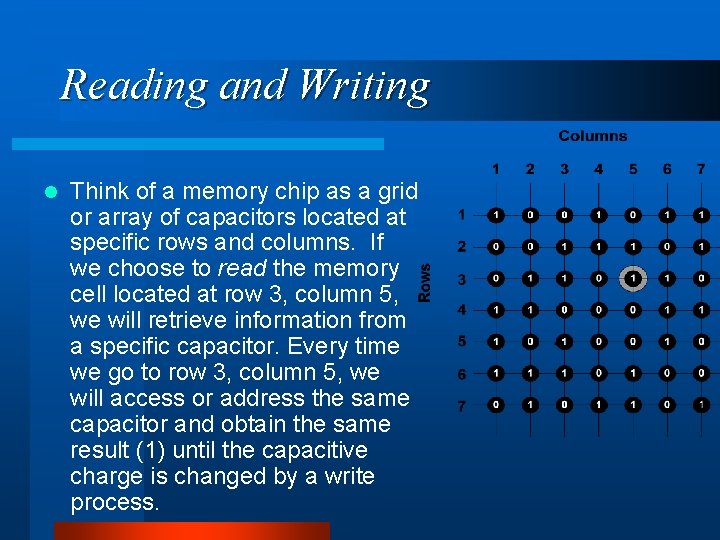

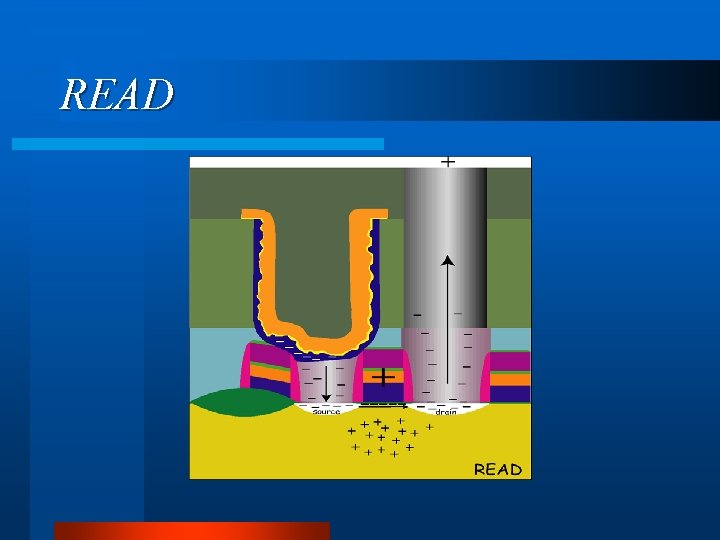

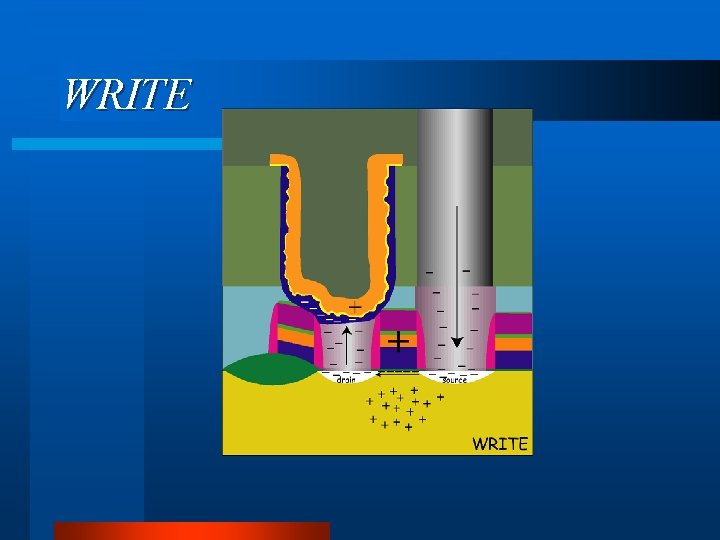

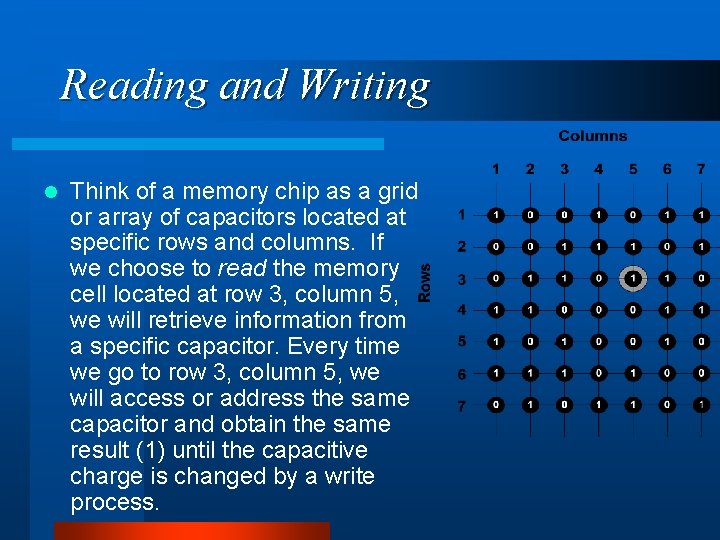

Reading and Writing l Think of a memory chip as a grid or array of capacitors located at specific rows and columns. If we choose to read the memory cell located at row 3, column 5, we will retrieve information from a specific capacitor. Every time we go to row 3, column 5, we will access or address the same capacitor and obtain the same result (1) until the capacitive charge is changed by a write process.

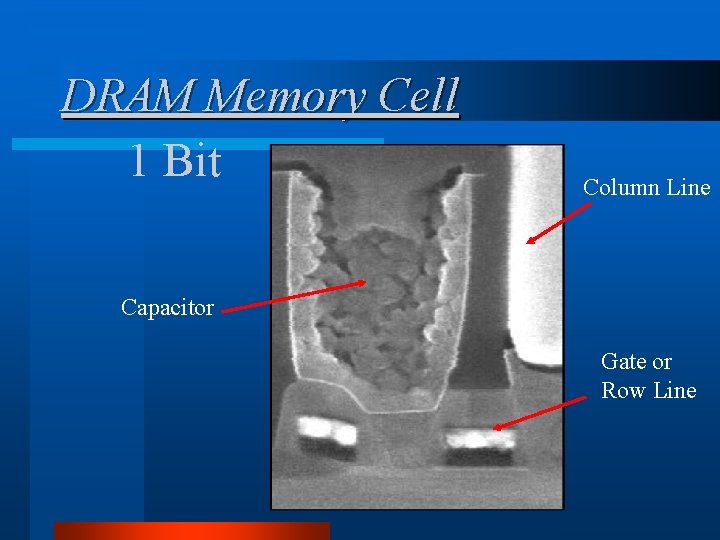

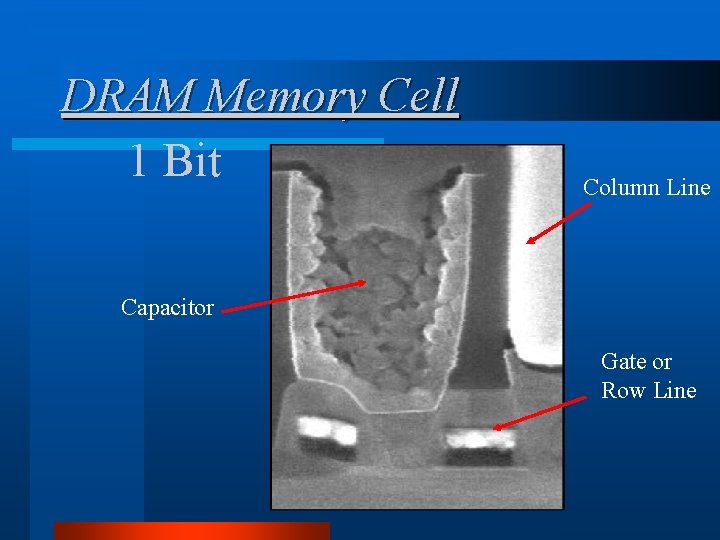

DRAM Memory Cell 1 Bit Column Line Capacitor Gate or Row Line

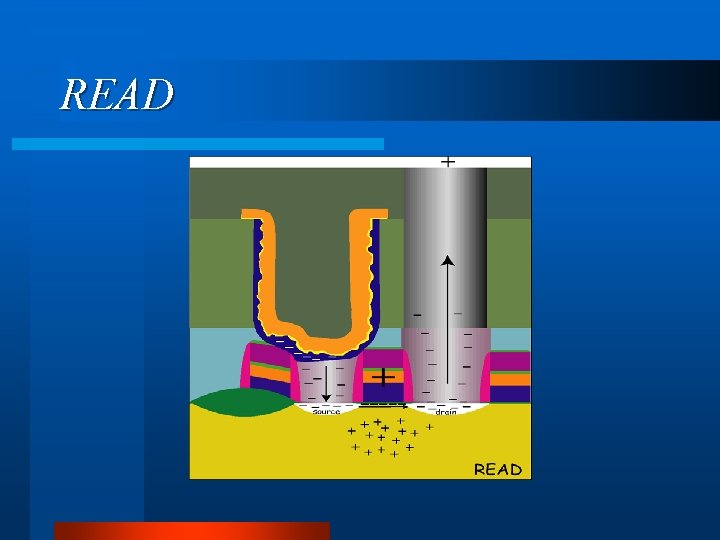

READ

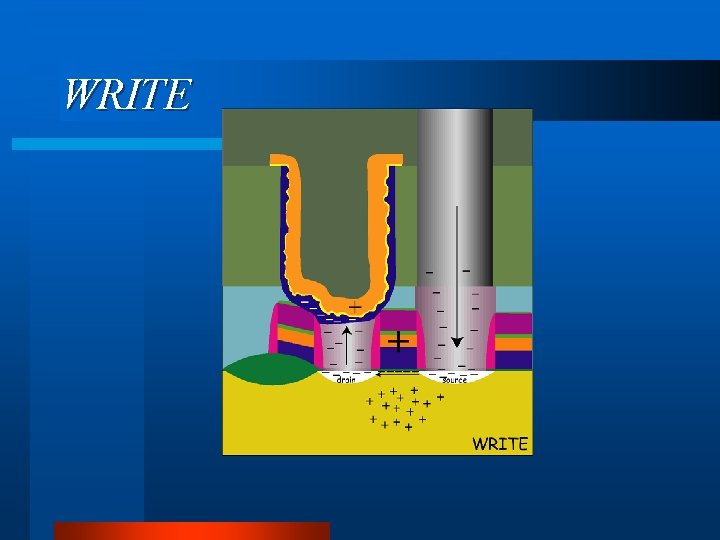

WRITE