Lecture 5 Fault Simulation n n Problem and

Lecture 5 Fault Simulation n n Problem and motivation Fault simulation algorithms n n n Serial Parallel Deductive Concurrent Random Fault Sampling Summary Original slides copyright by Mike Bushnell and Vishwani Agrawal 1

Problem and Motivation n Fault simulation Problem: Given § A circuit § A sequence of test vectors § A fault model Determine § Fault coverage - fraction (or percentage) of modeled faults detected by test vectors § Set of undetected faults n Motivation § Determine test quality and in turn product quality § Find undetected fault targets to improve tests 2

Usage Scenarios n n n Functional test fault grading - Fault simulate functional patterns against SAF and TF to estimate test quality - Identify low-coverage regions - Typically very expensive Drop fortuitously detected faults - Generate test T for fault A - Fault simulate T against remaining fault list, drop detected faults Estimate test quality for non-target faults - Simulate tests for fault model X against fault model Y - E. g. fault simulate SAF tests against bridge faults 3

Fault Simulator in a VLSI Design Process Verified design netlist Verification input stimuli Fault simulator Test vectors Modeled Remove fault list tested faults Fault coverage ? Low Test Delete compactor vectors Test generator Add vectors Adequate Stop 4

Fault Simulation Scenario n Circuit model: mixed-level n n n Signal states: logic n n n Mostly logic with some switch-level for highimpedance (Z) and bidirectional signals High-level models (memory, etc. ) with pin faults Two (0, 1) or three (0, 1, X) states for purely Boolean logic circuits Four states (0, 1, X, Z) for sequential MOS circuits Timing: n n Zero-delay for combinational and synchronous circuits Mostly unit-delay for circuits with feedback 5

Fault Simulation Scenario (continued) n Faults: n n n Mostly single stuck-at faults Sometimes stuck-open, transition, and path-delay faults; analog circuit fault simulators are not yet in common use Equivalence fault collapsing of single stuck-at faults Fault-dropping -- a fault once detected is dropped from consideration as more vectors are simulated; fault-dropping may be suppressed for diagnosis Fault sampling -- a random sample of faults is simulated when the circuit is large 6

Fault Simulation Algorithms n n n Serial Parallel Deductive Concurrent Differential 7

Serial Algorithm n Algorithm: Simulate fault-free circuit and save responses. Repeat following steps for each fault in the fault list: n n Modify netlist by injecting one fault Simulate modified netlist, vector by vector, comparing responses with saved responses If response differs, report fault detection and suspend simulation of remaining vectors Advantages: n n Easy to implement; needs only a true-value simulator, less memory Most faults, including analog faults, can be simulated 8

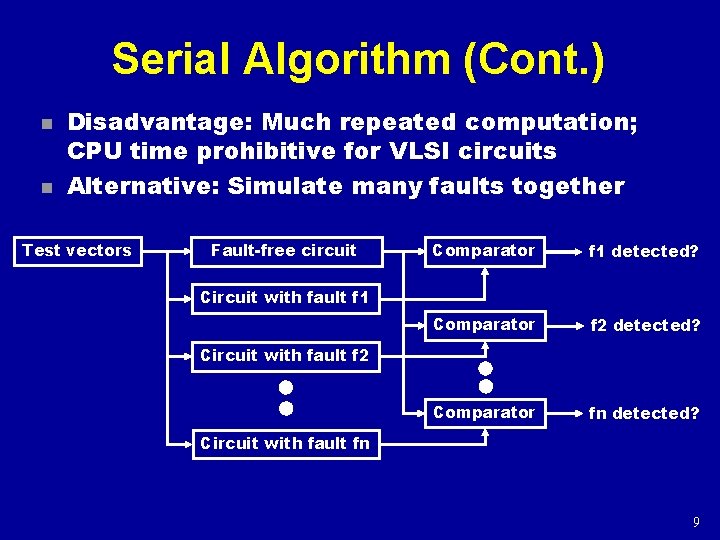

Serial Algorithm (Cont. ) n n Disadvantage: Much repeated computation; CPU time prohibitive for VLSI circuits Alternative: Simulate many faults together Test vectors Fault-free circuit Comparator f 1 detected? Comparator f 2 detected? Comparator fn detected? Circuit with fault f 1 Circuit with fault f 2 Circuit with fault fn 9

Parallel Fault Simulation n n n Compiled-code method; best with twostates (0, 1) Exploits inherent bit-parallelism of logic operations on computer words Storage: one word per line for two-state simulation Multi-pass simulation: Each pass simulates w-1 new faults, where w is the machine word length Speed up over serial method ~ w-1 Not suitable for circuits with timing-critical and non-Boolean logic 10

Parallel Fault Sim. Example Bit 0: fault-free circuit Bit 1: circuit with c s-a-0 Bit 2: circuit with f s-a-1 1 a b c s-a-0 detected 1 0 1 1 1 0 1 c e 1 0 1 s-a-0 0 d f s-a-1 g 0 0 1 11

Deductive Fault Simulation n n One-pass simulation Each line k contains a list Lk of faults detectable on k Following true-value simulation of each vector, fault lists of all gate output lines are updated using set-theoretic rules, signal values, and gate input fault lists PO fault lists provide detection data Limitations: n n Set-theoretic rules difficult to derive for non. Boolean gates Gate delays are difficult to use 12

Deductive Fault Sim. Example Notation: Lk is fault list for line k kn is s-a-n fault on line k b 1 {b 0 } {a 0 } {b 0 , c 0 } c d {b 0 , d 0 } Le = La U Lc U { e 0} = { a 0 , b 0 , c 0 , e 0} e f 1 0 {b 0 , d 0 , f 1 } 1 g Lg = ( Le Lf ) U { g 0} = { a 0 , c 0 , e 0 , g 0} Faults detected by the input vector U a 1 13

Concurrent Fault Simulation n n Event-driven simulation of fault-free circuit and only those parts of the faulty circuit that differ in signal states from the fault-free circuit. A list per gate containing copies of the gate from all faulty circuits in which this gate differs. List element contains fault ID, gate input and output values and internal states, if any. All events of fault-free and all faulty circuits are implicitly simulated. Faults can be simulated in any modeling style or detail supported in true-value simulation (offers most flexibility. ) Faster than parallel simulation, but uses most memory. 14

Conc. Fault Sim. Example a 0 0 a b 1 1 0 1 1 c d 1 1 1 0 c 0 b 0 1 1 0 0 0 e 0 0 0 1 1 e 1 0 0 f d 0 0 0 1 f 1 1 1 0 b 0 1 a 0 0 1 0 g b 0 0 0 1 0 0 g 0 1 1 f 1 c 0 0 1 1 e 0 0 1 d 0 15

Parallel Pattern Simulation n n Use parallel patterns instead of parallel faults PPSFP - parallel pattern, single fault propagation Multi-pass simulation: Each pass simulates w new patterns for one fault at a time Must first simulate fault-free response Speed up over serial method ~ w Faster than parallel or concurrent Most faults dropped in first w patterns so a lower constant factor than other methods Avoids pointer manipulation cost of concurrent simulation 16

Parallel Fault Sim. Example Bit 0: vector 0 Bit 1: vector 1 Bit 2: vector 2 0 1 1 a b 0 0 0 1 0 0 0 c e s-a-0 1 1 0 d c s-a-0 detected 1 1 0 g f 17

Algorithm Switching n n Different algorithms are more efficient at different points in simulation Initially have high drop rate Each vector detects many faults Each pass greatly shrinks fault list Parallel fault simulation most efficient Later have lower drop rate Less fault list reduction per vector Need batch of vectors to get large fault list reduction per pass Parallel pattern most efficient Example: Cadence Encounter Test 18

Fault Sampling n n A randomly selected subset (sample) of faults is simulated. Measured coverage in the sample is used to estimate fault coverage in the entire circuit. Advantage: Saving in computing resources (CPU time and memory. ) Disadvantage: Limited data on undetected faults - hard to identify location of coverage problems. 19

Motivation for Sampling n Complexity of fault simulation depends on: n n Number of gates Number of faults Number of vectors Complexity of fault simulation with fault sampling depends on: n n Number of gates Number of vectors 20

Random Sampling Model Detected fault All faults with a fixed but unknown coverage Undetected fault Random picking Np = total number of faults (population size) C = fault coverage (unknown) Ns = sample size Ns << Np c = sample coverage (a random variable) 21

Probability Density of Sample Coverage, c (x--C )2 -- ------ 1 p (x ) = Prob(x < c < x +dx ) = -------s (2 p) p (x ) C (1 - C) 2 Variance, s = ------Ns s C e 2 Sampling error s Mean = C C -3 s 1/2 2 s x C +3 s 1. 0 x Sample coverage 22

![Sampling Error Bounds |x-C|=3 C (1 - C ) 1/2 [ -------] N s Sampling Error Bounds |x-C|=3 C (1 - C ) 1/2 [ -------] N s](http://slidetodoc.com/presentation_image_h2/40eea8223a37d1c30e5602402023c1a5/image-23.jpg)

Sampling Error Bounds |x-C|=3 C (1 - C ) 1/2 [ -------] N s Solving the quadratic equation for C, we get the 3 -sigma (99. 7% confidence) estimate: 4. 5 C 3 s = x ± ------- [1 + 0. 44 Ns x (1 - x )]1/2 Ns Where Ns is sample size and x is the measured fault coverage in the sample. Example: A circuit with 39, 096 faults has an actual fault coverage of 87. 1%. The measured coverage in a random sample of 1, 000 faults is 88. 7%. The above formula gives an estimate of 88. 7% 3%. CPU time for sample simulation was about 10% of that for all faults. ± 23

Summary n n Fault simulator is an essential tool for test development. Parallel pattern simulation or combined parallel pattern and parallel fault simulation is the fastest method. For restricted class of circuits (combinational and synchronous sequential with only Boolean primitives), differential algorithm can provide better speed and memory efficiency For large circuits, the accuracy of random fault sampling only depends on the sample size (1, 000 to 2, 000 faults) and not on the circuit size. The method has significant advantages in reducing CPU time and memory needs of the simulator. - Primary use is fault grading existing test set, e. g. functional patterns 24

- Slides: 24