Lecture 42 OUTLINE IC technology MOSFET fabrication process

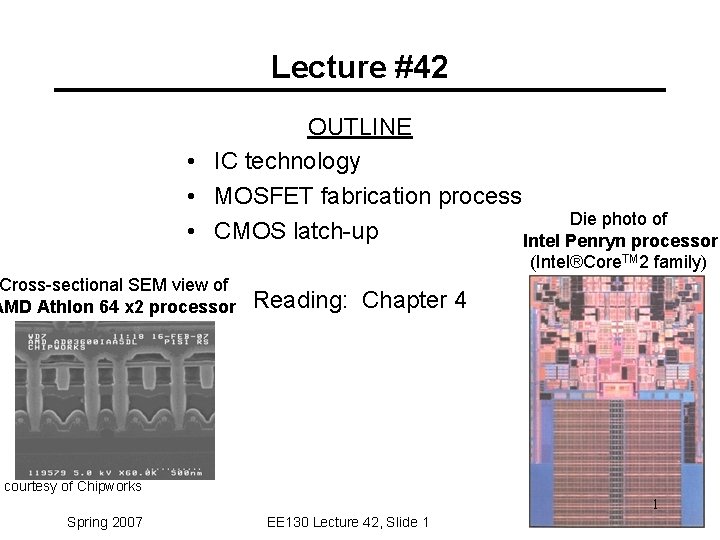

Lecture #42 OUTLINE • IC technology • MOSFET fabrication process Die photo of • CMOS latch-up Intel Penryn processor (Intel®Core. TM 2 family) Cross-sectional SEM view of AMD Athlon 64 x 2 processor Reading: Chapter 4 courtesy of Chipworks 1 Spring 2007 EE 130 Lecture 42, Slide 1

Integrated Circuit Technology “Planar” fabrication process: Simultaneous fabrication of many “chips” on a wafer, each comprising an integrated circuit (e. g. a microprocessor or memory chip) containing millions or billions of transistors 300 mm Si wafer Method: Sequentially lay down and pattern thin films of semiconductors, metals and insulators. Materials used in a basic CMOS integrated circuit: • Si substrate – selectively doped in various regions • Si. O 2 insulator • Polycrystalline silicon – used for the gate electrodes Spring 2007 EE 130 Lecture 42, Slide 2 2

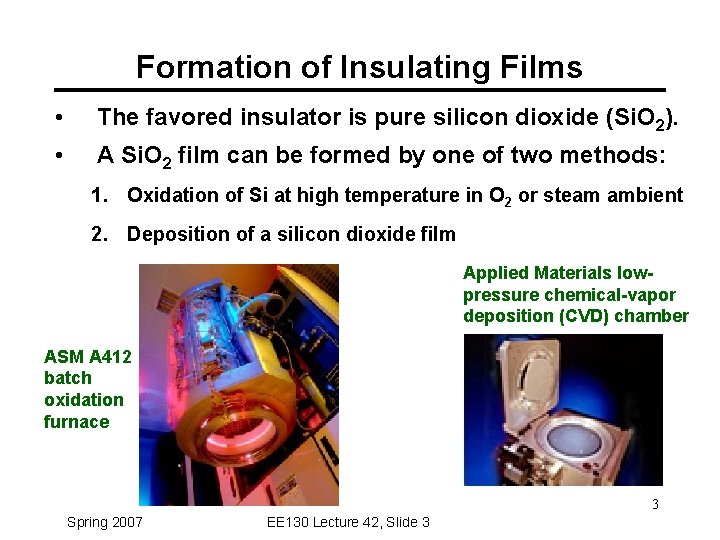

Formation of Insulating Films • The favored insulator is pure silicon dioxide (Si. O 2). • A Si. O 2 film can be formed by one of two methods: 1. Oxidation of Si at high temperature in O 2 or steam ambient 2. Deposition of a silicon dioxide film Applied Materials lowpressure chemical-vapor deposition (CVD) chamber ASM A 412 batch oxidation furnace 3 Spring 2007 EE 130 Lecture 42, Slide 3

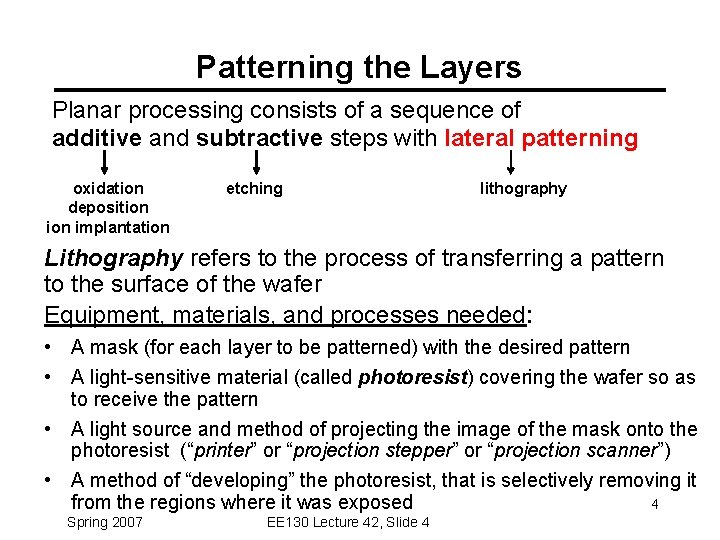

Patterning the Layers Planar processing consists of a sequence of additive and subtractive steps with lateral patterning oxidation deposition implantation etching lithography Lithography refers to the process of transferring a pattern to the surface of the wafer Equipment, materials, and processes needed: • A mask (for each layer to be patterned) with the desired pattern • A light-sensitive material (called photoresist) covering the wafer so as to receive the pattern • A light source and method of projecting the image of the mask onto the photoresist (“printer” or “projection stepper” or “projection scanner”) • A method of “developing” the photoresist, that is selectively removing it from the regions where it was exposed 4 Spring 2007 EE 130 Lecture 42, Slide 4

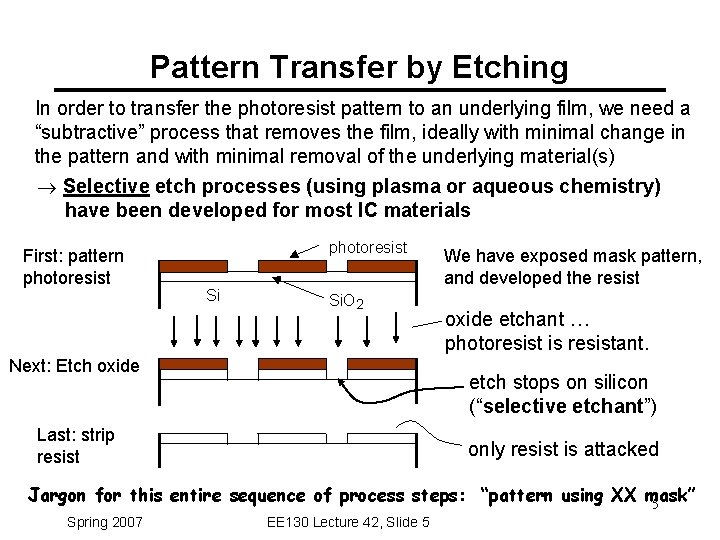

Pattern Transfer by Etching In order to transfer the photoresist pattern to an underlying film, we need a “subtractive” process that removes the film, ideally with minimal change in the pattern and with minimal removal of the underlying material(s) ® Selective etch processes (using plasma or aqueous chemistry) have been developed for most IC materials First: pattern photoresist Si Si. O 2 Next: Etch oxide We have exposed mask pattern, and developed the resist oxide etchant … photoresist is resistant. etch stops on silicon (“selective etchant”) Last: strip resist only resist is attacked Jargon for this entire sequence of process steps: “pattern using XX mask” 5 Spring 2007 EE 130 Lecture 42, Slide 5

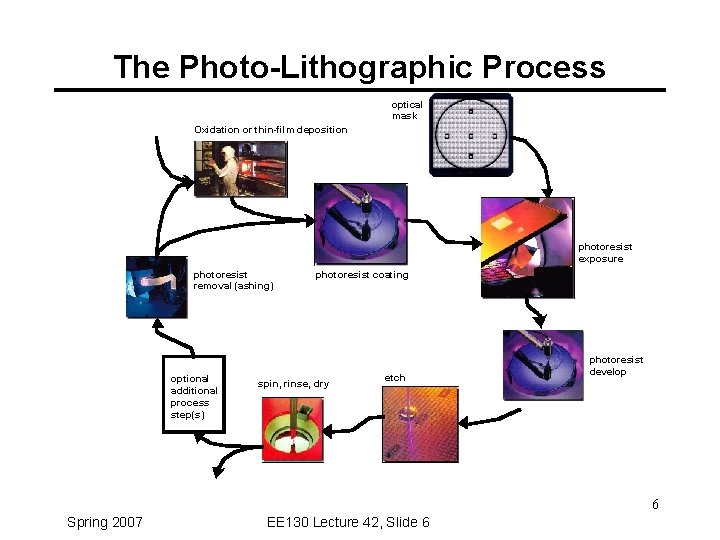

The Photo-Lithographic Process optical mask Oxidation or thin-film deposition photoresist exposure photoresist removal (ashing) optional additional process step(s) photoresist coating spin, rinse, dry etch photoresist develop 6 Spring 2007 EE 130 Lecture 42, Slide 6

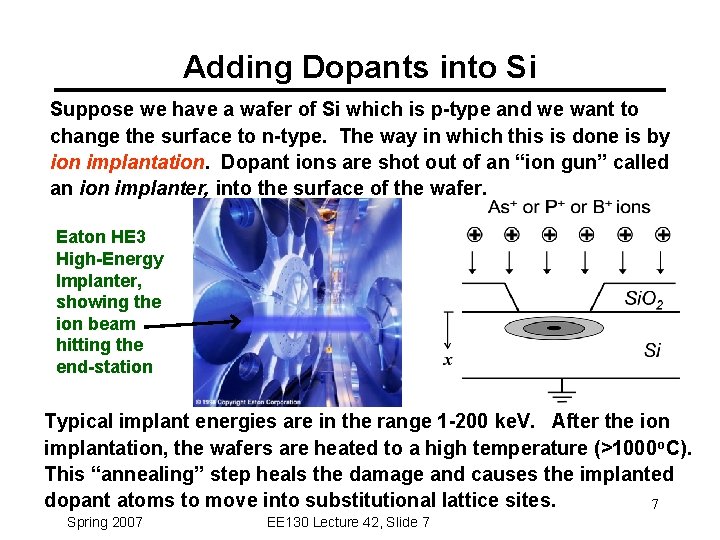

Adding Dopants into Si Suppose we have a wafer of Si which is p-type and we want to change the surface to n-type. The way in which this is done is by ion implantation. Dopant ions are shot out of an “ion gun” called an ion implanter, into the surface of the wafer. Eaton HE 3 High-Energy Implanter, showing the ion beam hitting the end-station Typical implant energies are in the range 1 -200 ke. V. After the ion implantation, the wafers are heated to a high temperature (>1000 o. C). This “annealing” step heals the damage and causes the implanted dopant atoms to move into substitutional lattice sites. 7 Spring 2007 EE 130 Lecture 42, Slide 7

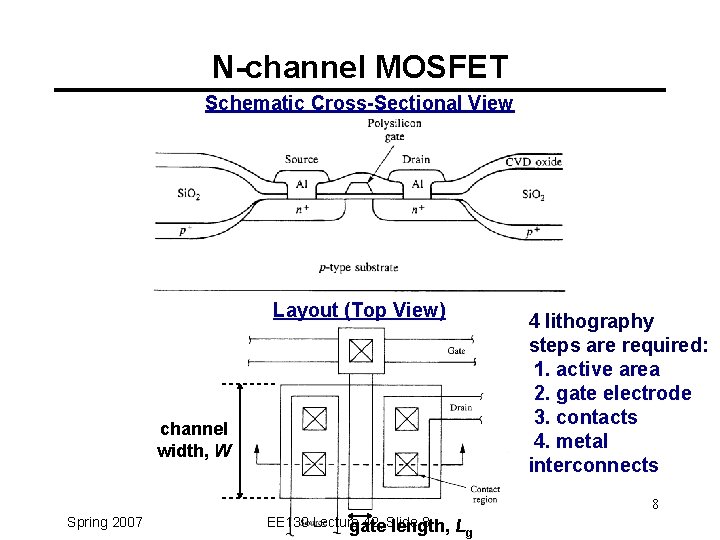

N-channel MOSFET Schematic Cross-Sectional View Layout (Top View) 4 lithography steps are required: 1. active area 2. gate electrode 3. contacts 4. metal interconnects channel width, W 8 Spring 2007 EE 130 Lecture 42, Slide 8 gate length, Lg

CMOS Technology Both n-channel and p-channel MOSFETs are fabricated on the same chip (VTp = -VTn ) • Primary advantage: – Lower average power dissipation • Ideally, in steady state either the NMOS or PMOS device is off, so there is no DC current path between VDD & GND • Disadvantages: – More complex (expensive) process – Latch-up problem Spring 2007

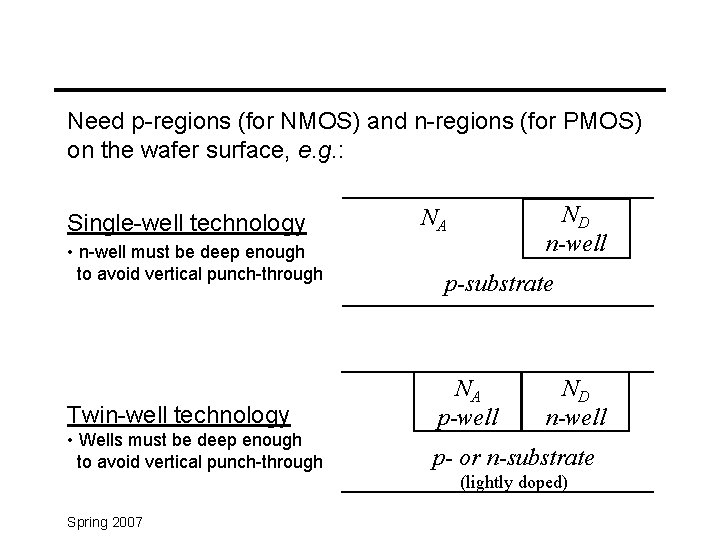

Need p-regions (for NMOS) and n-regions (for PMOS) on the wafer surface, e. g. : Single-well technology • n-well must be deep enough to avoid vertical punch-through Twin-well technology • Wells must be deep enough to avoid vertical punch-through ND n-well NA p-substrate NA p-well ND n-well p- or n-substrate (lightly doped) Spring 2007

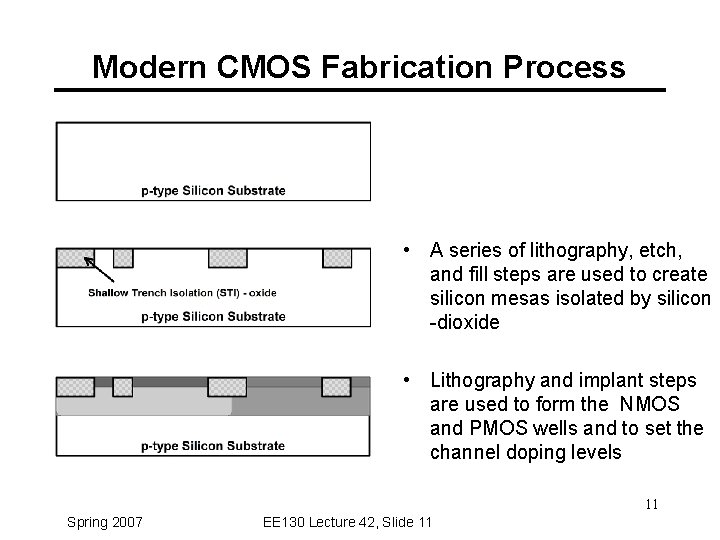

Modern CMOS Fabrication Process • A series of lithography, etch, and fill steps are used to create silicon mesas isolated by silicon -dioxide • Lithography and implant steps are used to form the NMOS and PMOS wells and to set the channel doping levels 11 Spring 2007 EE 130 Lecture 42, Slide 11

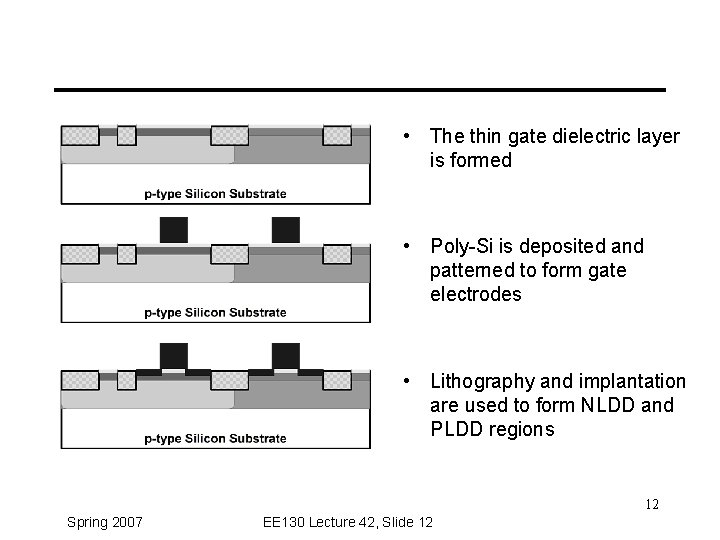

• The thin gate dielectric layer is formed • Poly-Si is deposited and patterned to form gate electrodes • Lithography and implantation are used to form NLDD and PLDD regions 12 Spring 2007 EE 130 Lecture 42, Slide 12

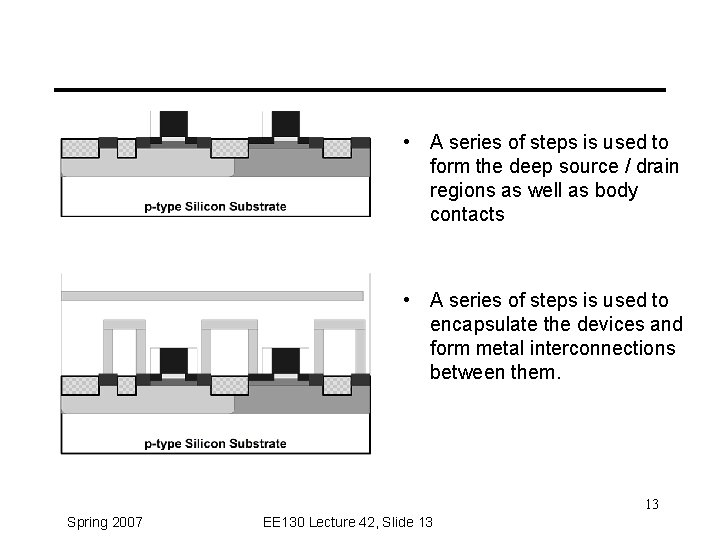

• A series of steps is used to form the deep source / drain regions as well as body contacts • A series of steps is used to encapsulate the devices and form metal interconnections between them. 13 Spring 2007 EE 130 Lecture 42, Slide 13

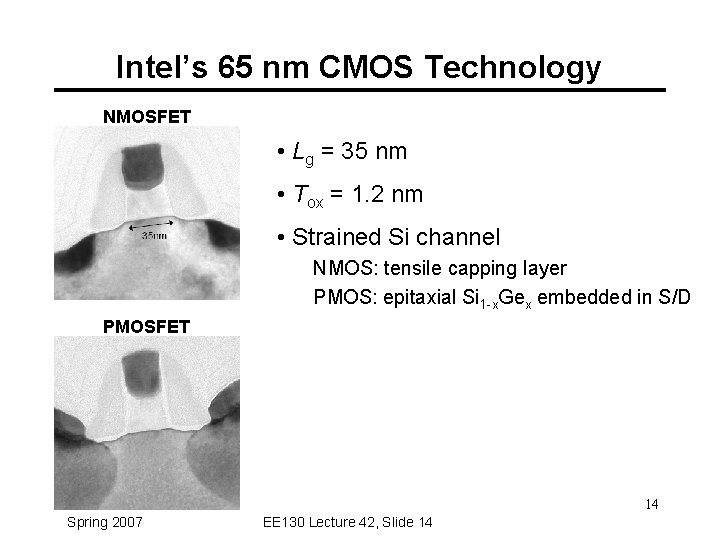

Intel’s 65 nm CMOS Technology NMOSFET • Lg = 35 nm • Tox = 1. 2 nm • Strained Si channel NMOS: tensile capping layer PMOS: epitaxial Si 1 -x. Gex embedded in S/D PMOSFET 14 Spring 2007 EE 130 Lecture 42, Slide 14

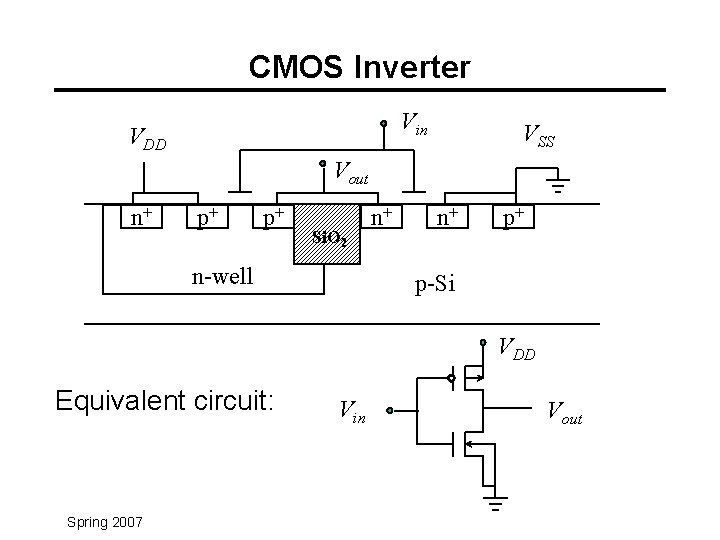

CMOS Inverter Vin VDD VSS Vout n+ p+ p+ Si. O 2 n-well n+ n+ p+ p-Si VDD Equivalent circuit: Spring 2007 Vin Vout

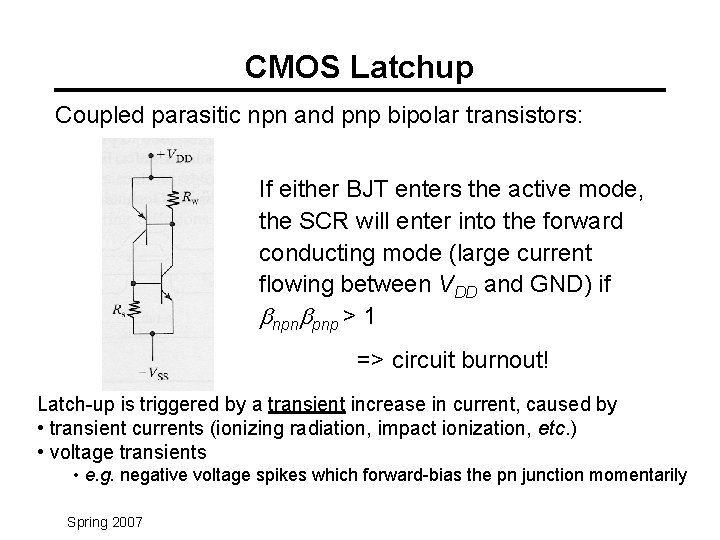

CMOS Latchup Coupled parasitic npn and pnp bipolar transistors: If either BJT enters the active mode, the SCR will enter into the forward conducting mode (large current flowing between VDD and GND) if bnpnbpnp > 1 => circuit burnout! Latch-up is triggered by a transient increase in current, caused by • transient currents (ionizing radiation, impact ionization, etc. ) • voltage transients • e. g. negative voltage spikes which forward-bias the pn junction momentarily Spring 2007

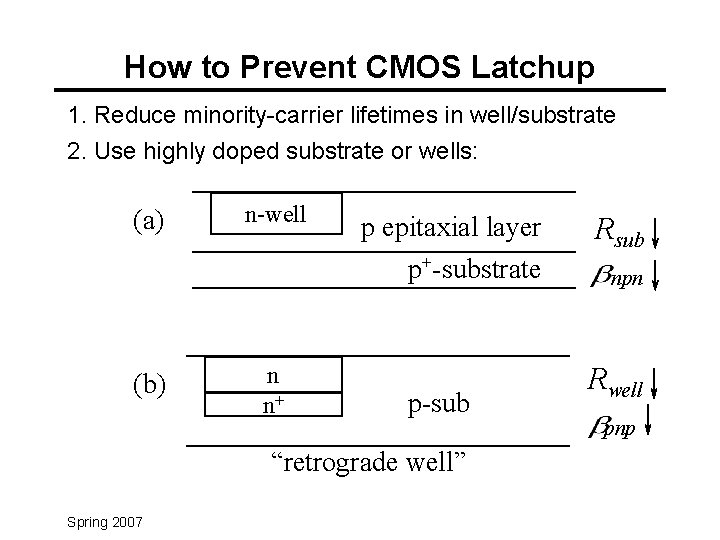

How to Prevent CMOS Latchup 1. Reduce minority-carrier lifetimes in well/substrate 2. Use highly doped substrate or wells: (a) (b) n-well n n+ p epitaxial layer p+-substrate p-sub “retrograde well” Spring 2007 Rsub npn Rwell pnp

IC Technology Trends • Increasing # of levels of wiring (Cu interconnects) Up to 8 levels of metal are used in ICs today. Photo from IBM Microelectronics Gallery: Colorized scanning-electron micrograph of the copper interconnect layers, after removal of the insulating layers by a chemical etch • Increasing variety of materials – high-k gate dielectric, metal gate, low-k intermetal dielectrics, etc. • Continued scaling of MOSFETs toward 10 nm Lg: – CMOSFETs with gate lengths below 20 nm have already been demonstrated by leading semiconductor manufacturers. The most advanced transistor designs are based on UC-Berkeley research (Prof’s Hu, King Liu, Bokor). 18 Spring 2007 EE 130 Lecture 42, Slide 18

- Slides: 18