Lecture 4 MIPS Subroutines and x 86 Architecture

Lecture 4: MIPS Subroutines and x 86 Architecture Professor Mike Schulte Computer Architecture ECE 201

MIPS Subroutine Calls • When making a subroutine (procedure) call, it is necessary to – – Place inputs where they can be accessed by subroutine Transfer control to subroutine Peform the desired task Place the result value(s) where the calling program can access it – Return control to the point of origin – The subroutine caller or callee should save and restore registers used by the subroutine • MIPS – Provides instructions to assist in subroutine calls (jal) and returns (jr) – Uses software conventions to » place subroutine input and output values » control which registers are saved/restored by caller and callee – Uses a software stack to save/restore values

Subroutine Calls Stacking of Subroutine Calls & Returns and Environments: A: A CALL B B: A B CALL C C: A B C RET A B RET A Some machines provide a memory stack as part of the architecture (e. g. , VAX) Sometimes stacks are implemented via software convention (e. g. , MIPS)

MIPS: Software conventions for registers 0 zero constant 0 16 s 0 callee saves 1 at . . . 2 v 0 expression evaluation & 23 s 7 3 v 1 function results 24 t 8 4 a 0 arguments 25 t 9 5 a 1 26 k 0 reserved for OS kernel 6 a 2 27 k 1 7 a 3 28 gp Pointer to global area 8 t 0 reserved for assembler temporary: caller saves temporary (cont’d) 29 sp stack pointer . . . (callee can clobber) 30 fp frame pointer 15 t 7 31 ra Return Address (HW)

Call-Return Linkage: Stack Frames High Mem FP Saved argument registers Saved return address Saved saved registers Local arrays and structures SP Low Mem

History of the Intel 80 x 86 • 1971: Intel invents microprocessor - 4004 • 1975: 8080 introduced – 8 -bit microprocessor – Accumulator machine • 1978: 8086 introduced – 16 bit microprocessor – Accumulator plus dedicated registers • 1980: IBM selects 8088 as basis for IBM PC – 8088 is 8 -bit external bus version of 8086 • 1980: 8087 floating point coprocessor – adds 60 floating point instructions – 80 bit floating point registers – uses hybrid stack/register scheme

History of the Intel 80 x 86 • 1982: 80286 introduced – 24 -bit address – memory mapping & protection • 1985: 80386 introduced – 32 -bit address – 32 -bit GP registers • • 1989: 80486 introduced 1992: Pentium introduced 1995: Pentium Pro introduced 1996: Pentium with MMX extensions – 57 new instructions – Primarily for multimedia applications • 1997: Pentium II (Pentium Pro with MMX)

History of the Intel 80 x 86 • 1999: Pentium III Introduced • Supports Intel’s Internet Streaming SIMD technology – Additional multimedia instructions – Four 32 -bit floating point operations in parallel – Average, absolute difference, packed maximum/minimum – Useful in speech recognition, video encoding/decoding • 2000: Intanium introduced – – – Release of IA-64 (RISC-like) architecture Explicitly Parallel Instruction Computing (EPIC) 128 -bit bundle with three instructions and a template 128 general purpose registers and 128 floating point registers Done by a partnership between HP and Intel Able to run both UNIX and Microsoft windows • Intel architecture was due to the desire for backward compatability – Highly irregular architecture – Over 50 million sold per year

Intel 80 x 86 Integer Registers

X 86 Operand Types • x 86 instructions typically have two operands, where one operand is both a source and a destination operand. • Possible combinations include Source/destination type Second source type Register Immediate Register Memory Immediate • No memory-memory or immediate-immediate • Immediates can be 8, 16, or 32 bits

80 x 86 Instructions • Data movement (move, push, pop) • Arithmetic and logic (logic ops, tests CCs, shifts, integer and decimal arithmetic) • Control flow (branches, jumps, calls, returns) • String instructions (move and compare) • FP data movement (load, load const. , store) • Arithmetic instructions (add, subtract, multiply, divide, square root, absolute value) • Comparisons (can send result to ALU) • Transcendental functions (sin, cos, log, etc. )

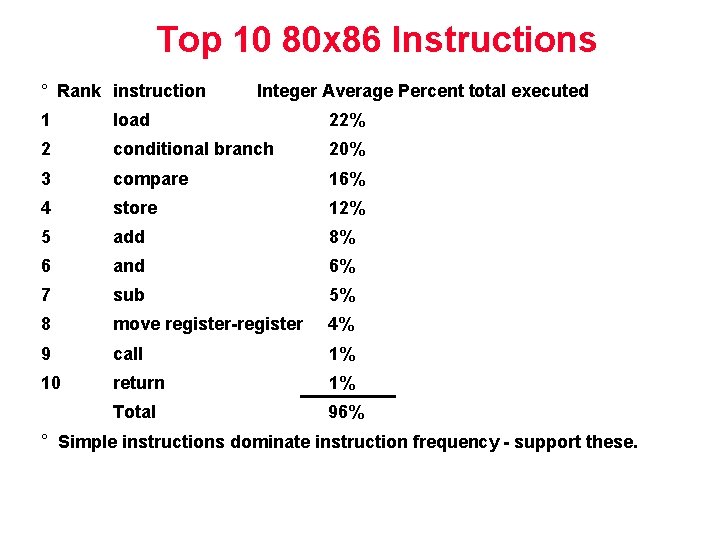

Top 10 80 x 86 Instructions ° Rank instruction Integer Average Percent total executed 1 load 22% 2 conditional branch 20% 3 compare 16% 4 store 12% 5 add 8% 6 and 6% 7 sub 5% 8 move register-register 4% 9 call 1% 10 return 1% Total 96% ° Simple instructions dominate instruction frequency - support these.

Addressing modes • The x 86 offers several different addressing modes for accessing memory Register indirect Address in register (mem[R 1]) Base with displacement (8, 16, or 32 -bit displacement) Address in base register plus displacement (mem[R 1+100]) Base plus scaled index (8, 16, or 32 -bit displacement) Address is Base + 2 scale x Index scale = 0, 1, 2 or 3 Base plus scaled index with displacement (8, 16, or 32 -bit displacement) Address is Base + 2 scale x Index + disp. scale = 0, 1, 2 or 3

80 x 86 Instruction Format • Instructions sizes vary from 1 to 17 bytes

80 x 86 Length Distribution

Performance Comparison Pentium Pro vs. MIPS R 10000 Benchmark SPECint 95 SPECfp 95 Pro 8. 7 6. 0 MIPS 8. 9 17. 2 MIIPS÷Pro 1. 02 2. 87 • The Pentium Pro and MIPS R 1000 have comparable performance on integer computations. • The MIPS R 10000 has much better performance than the Pentium Pro for floating point computations.

Comparison • How would you expect the x 86 and MIPS architectures to compare on the following. – – – CPI on SPEC benchmarks Ease of design and implementation Ease of writing assembly language & compilers Code density Overall performance • What other advantages/disadvantages are there to the two architectures.

- Slides: 17