Lecture 4 DAlgorithm and PODEM n Definitions DAlgorithm

- Slides: 56

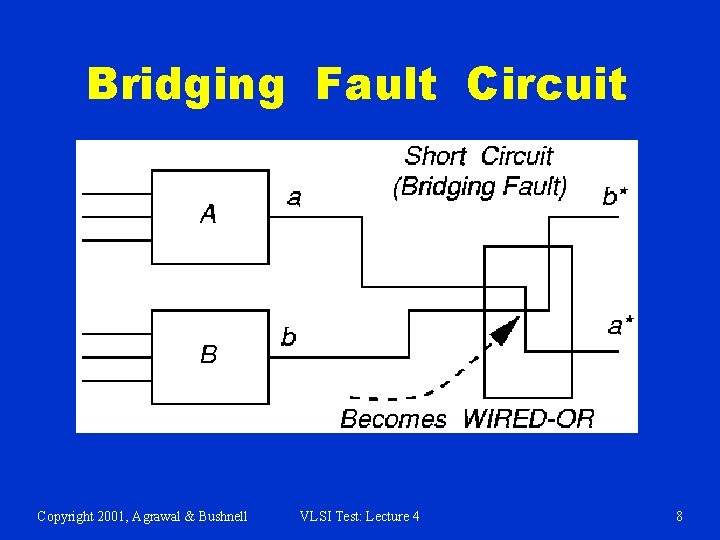

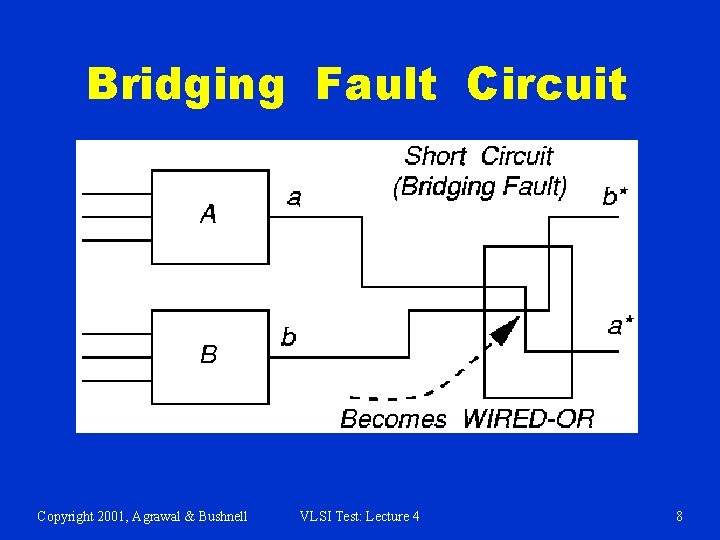

Lecture 4 D-Algorithm and PODEM n Definitions D-Algorithm (Roth) -- 1966 n PODEM (Goel) -- 1981 n § D-cubes § Bridging faults § Logic gate function change faults § X-Path-Check § Backtracing Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 1

D-Algorithm -- Roth IBM (1966) n Fundamental concepts invented: § First complete ATPG algorithm § D-Cube § D-Calculus § Implications – forward and backward § Implication stack § Backtrack § Test Search Space Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 2

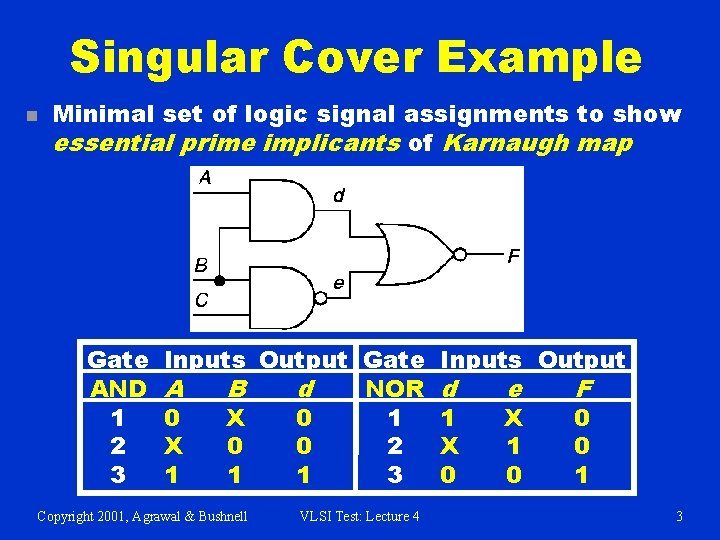

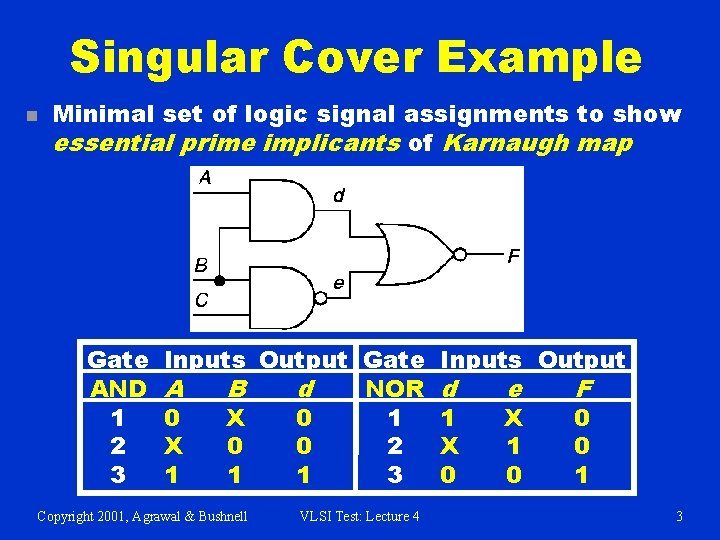

Singular Cover Example n Minimal set of logic signal assignments to show essential prime implicants of Karnaugh map Gate AND 1 2 3 Inputs Output Gate B A d NOR X 0 0 1 0 X 0 2 1 1 1 3 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 Inputs Output d 1 X 0 e X 1 0 F 0 0 1 3

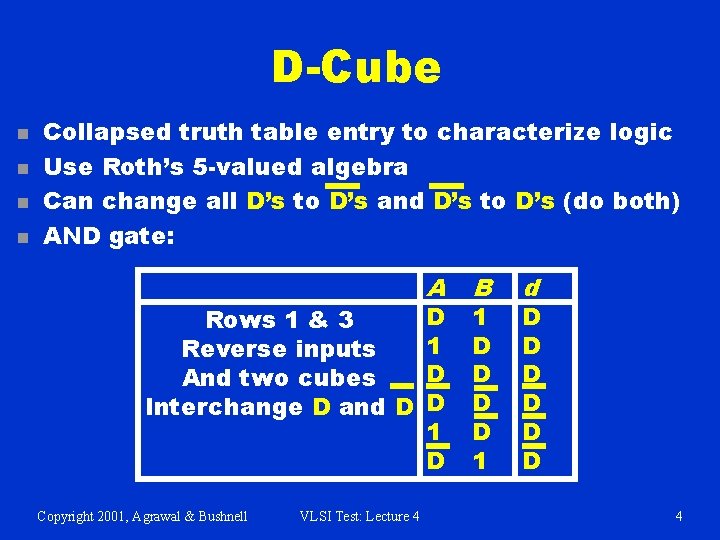

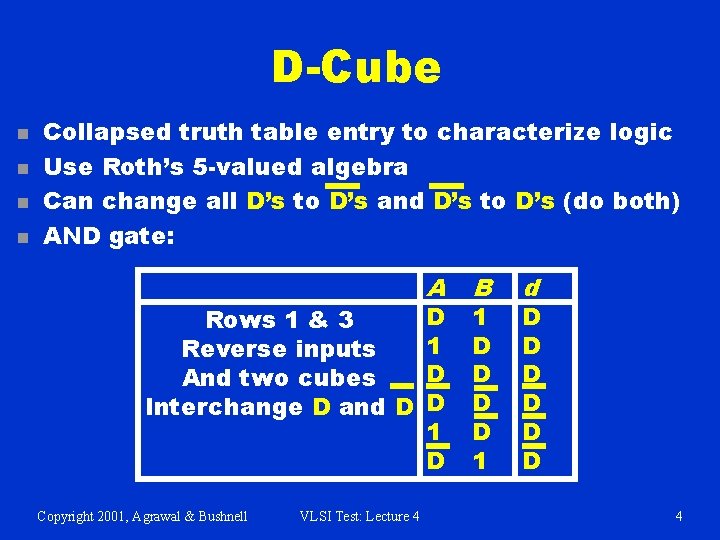

D-Cube n n Collapsed truth table entry to characterize logic Use Roth’s 5 -valued algebra Can change all D’s to D’s and D’s to D’s (do both) AND gate: Rows 1 & 3 Reverse inputs And two cubes Interchange D and D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 A D 1 D B 1 D D 1 d D D D 4

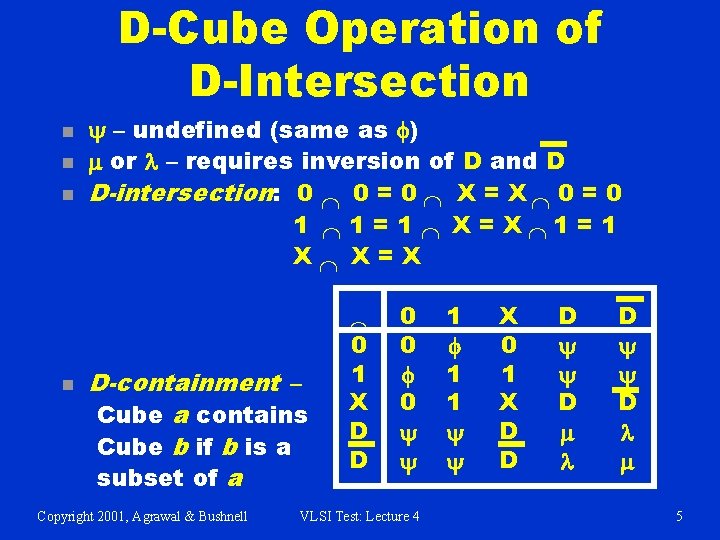

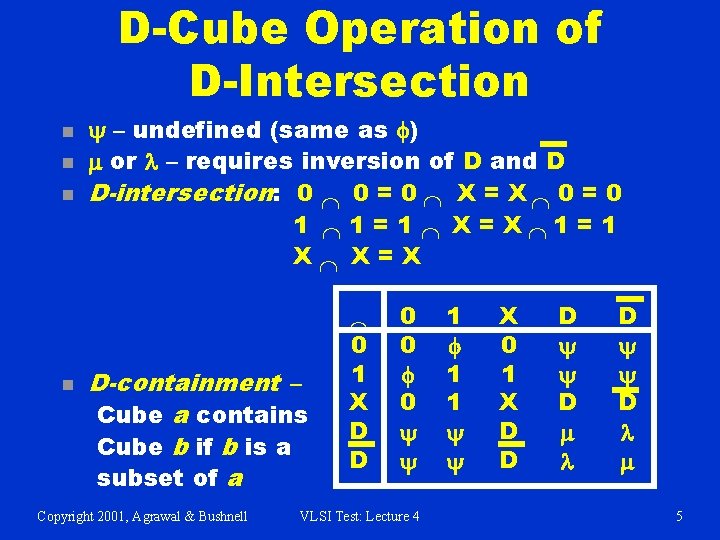

D-Cube Operation of D-Intersection n y – undefined (same as f) m or l – requires inversion of D and D D-intersection: 0 Ç 0 = 0 Ç X = X Ç 0 = 0 1 Ç 1 = 1 Ç X = XÇ1 = 1 XÇ X=X n Ç 0 1 X D D n n D-containment – Cube a contains Cube b if b is a subset of a Copyright 2001, Agrawal & Bushnell 0 0 f 0 y y VLSI Test: Lecture 4 1 f 1 1 y y X 0 1 X D D D y y D m l D y y D l m 5

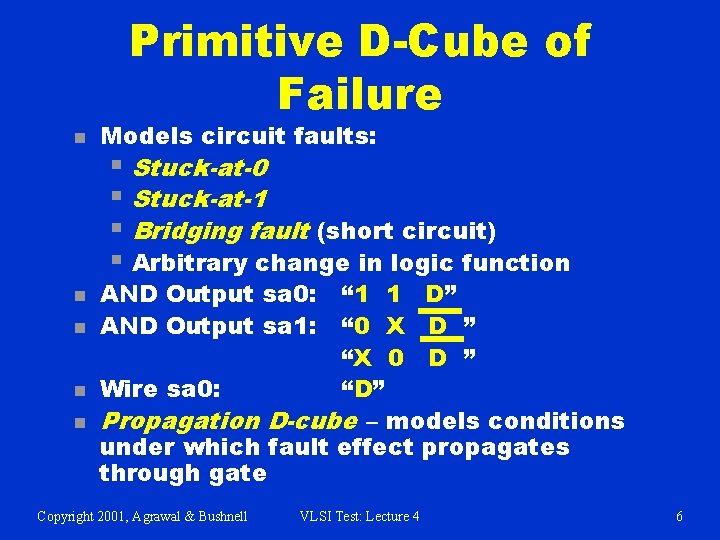

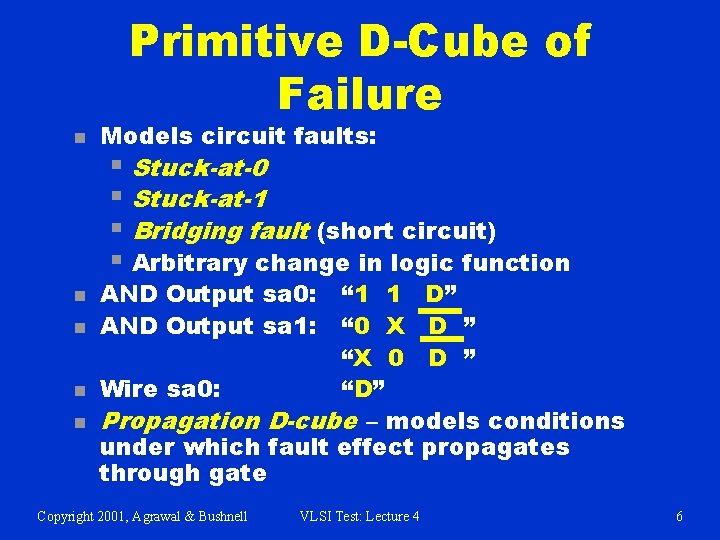

Primitive D-Cube of Failure n n n Models circuit faults: § Stuck-at-0 § Stuck-at-1 § Bridging fault (short circuit) § Arbitrary change in logic function AND Output sa 0: “ 1 1 D” AND Output sa 1: “ 0 X D ” “X 0 D ” Wire sa 0: “D” Propagation D-cube – models conditions under which fault effect propagates through gate Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 6

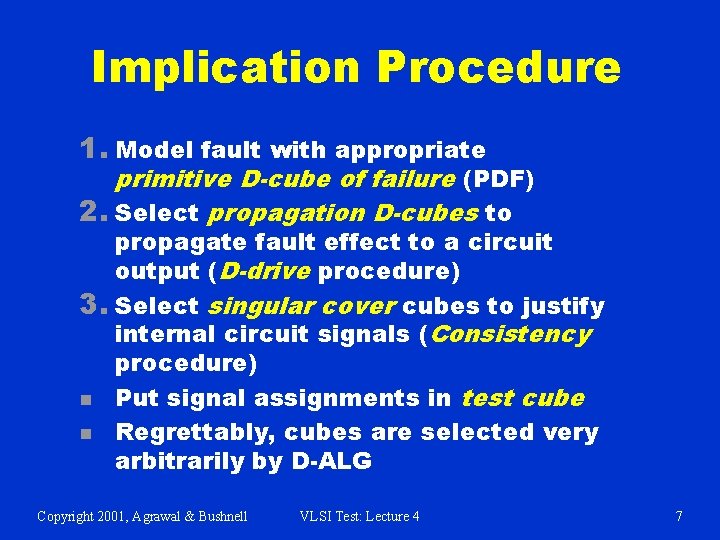

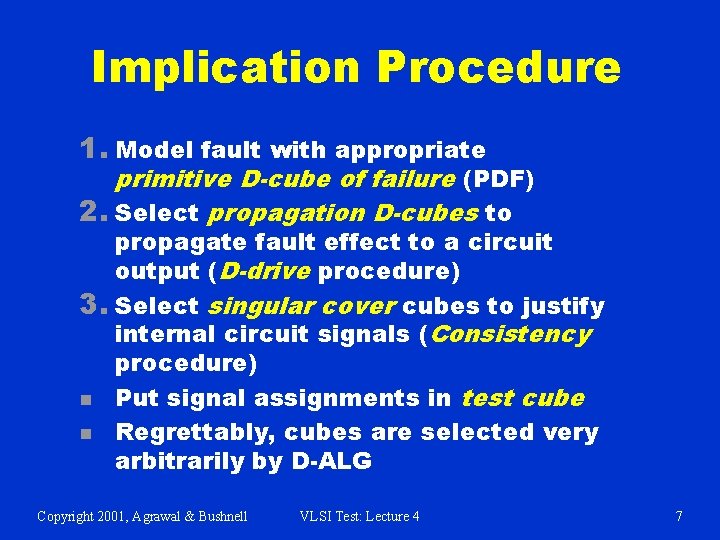

Implication Procedure 1. Model fault with appropriate primitive D-cube of failure (PDF) 2. Select propagation D-cubes to propagate fault effect to a circuit output (D-drive procedure) 3. Select singular cover cubes to justify internal circuit signals (Consistency procedure) n Put signal assignments in test cube n Regrettably, cubes are selected very arbitrarily by D-ALG Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 7

Bridging Fault Circuit Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 8

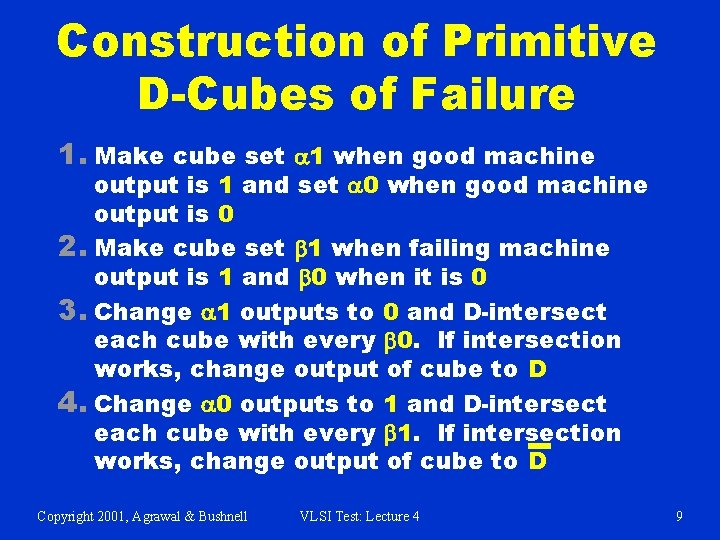

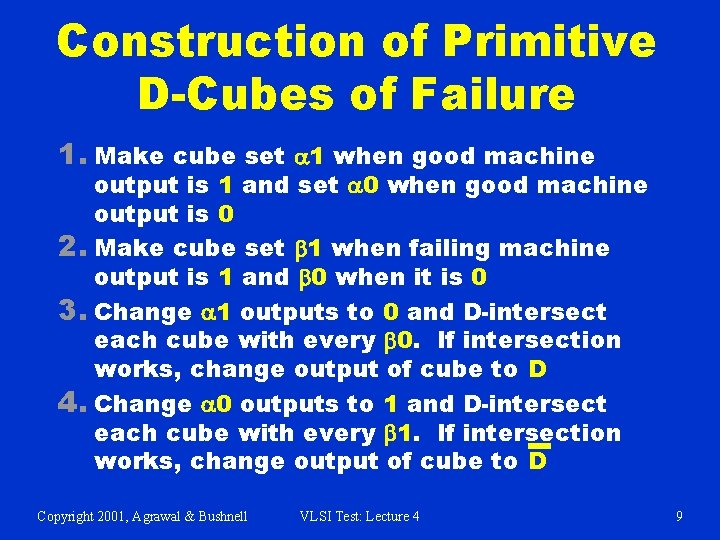

Construction of Primitive D-Cubes of Failure 1. Make cube set a 1 when good machine output is 1 and set a 0 when good machine output is 0 2. Make cube set b 1 when failing machine output is 1 and b 0 when it is 0 3. Change a 1 outputs to 0 and D-intersect each cube with every b 0. If intersection works, change output of cube to D 4. Change a 0 outputs to 1 and D-intersect each cube with every b 1. If intersection works, change output of cube to D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 9

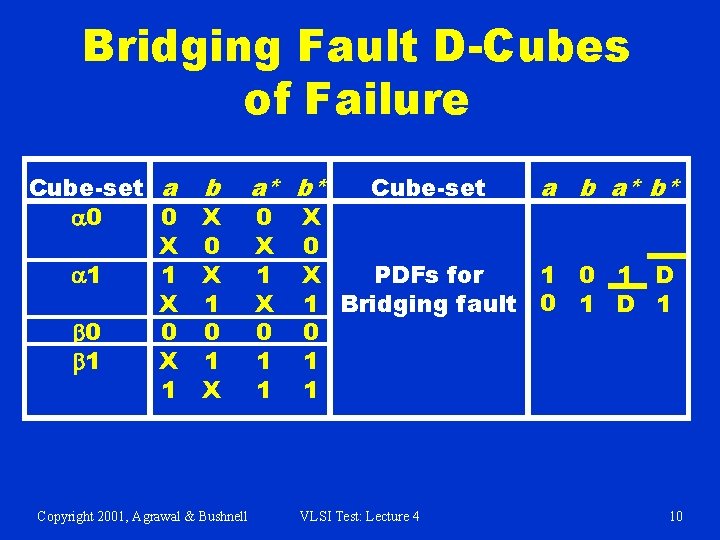

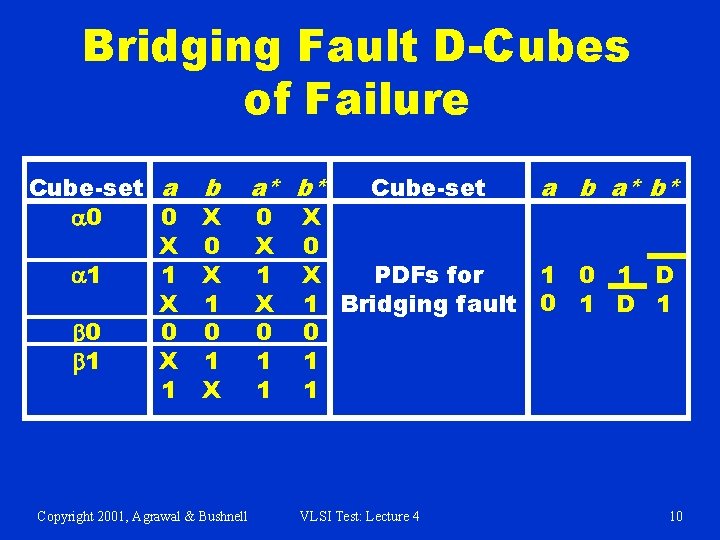

Bridging Fault D-Cubes of Failure Cube-set a a 0 0 X a 1 1 X b 0 0 b 1 X 1 b X 0 X 1 0 1 X Copyright 2001, Agrawal & Bushnell a* b* 0 X 1 X 0 1 1 Cube-set a b a* b* X 0 1 D X PDFs for 1 Bridging fault 0 1 D 1 0 1 1 VLSI Test: Lecture 4 10

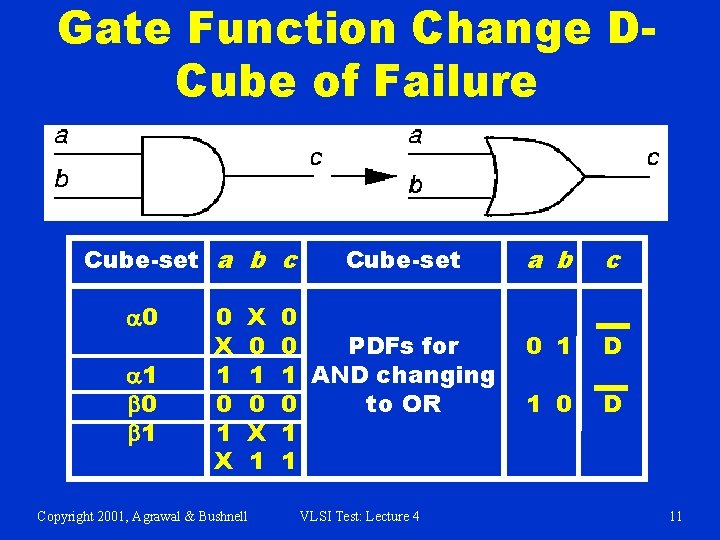

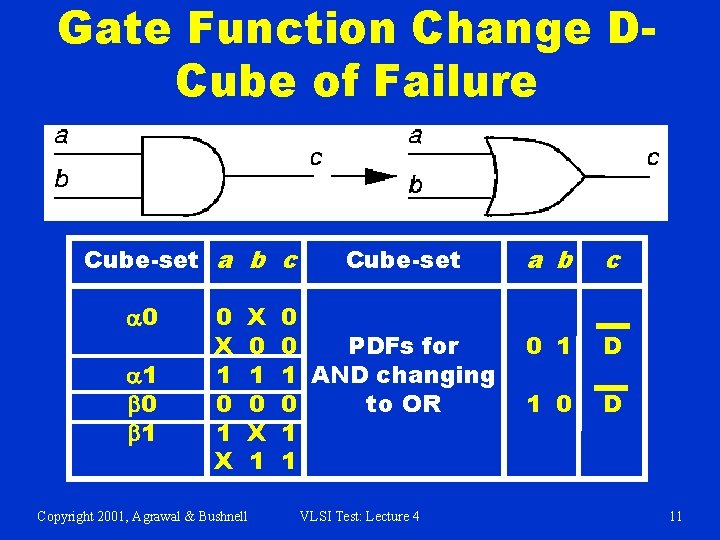

Gate Function Change DCube of Failure Cube-set a b c a 0 a 1 b 0 b 1 0 X 1 0 1 X X 0 1 0 X 1 Copyright 2001, Agrawal & Bushnell Cube-set 0 0 PDFs for 1 AND changing 0 to OR 1 1 VLSI Test: Lecture 4 a b c 0 1 D 1 0 D 11

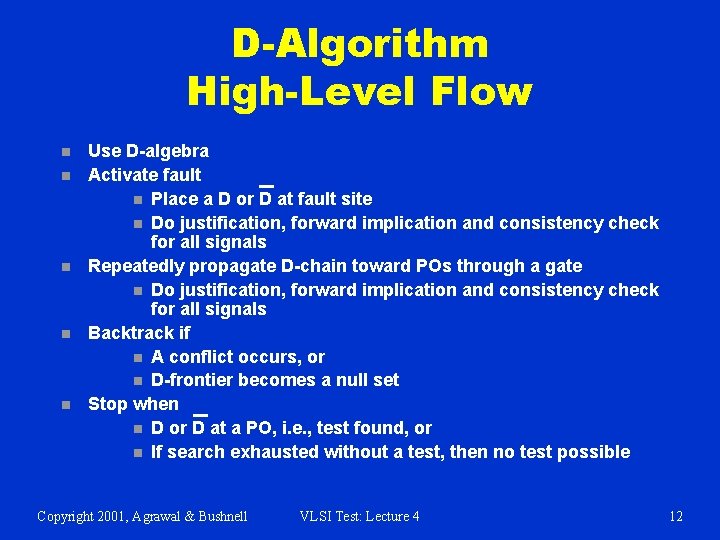

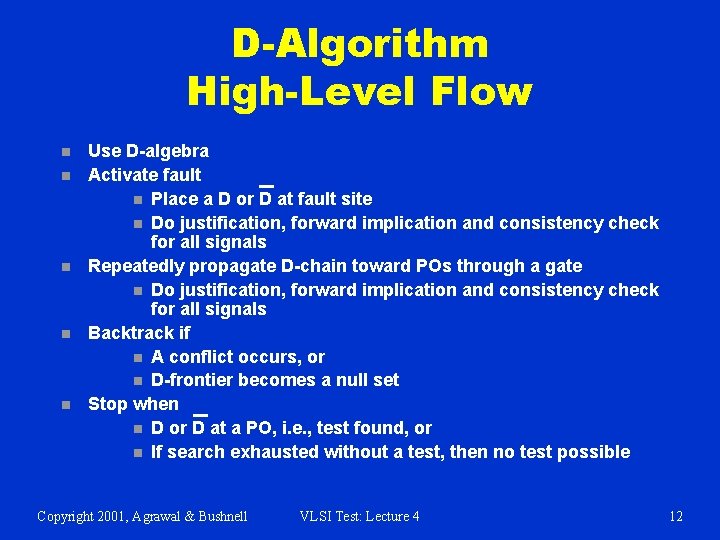

D-Algorithm High-Level Flow n n n Use D-algebra Activate fault n Place a D or D at fault site n Do justification, forward implication and consistency check for all signals Repeatedly propagate D-chain toward POs through a gate n Do justification, forward implication and consistency check for all signals Backtrack if n A conflict occurs, or n D-frontier becomes a null set Stop when n D or D at a PO, i. e. , test found, or n If search exhausted without a test, then no test possible Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 12

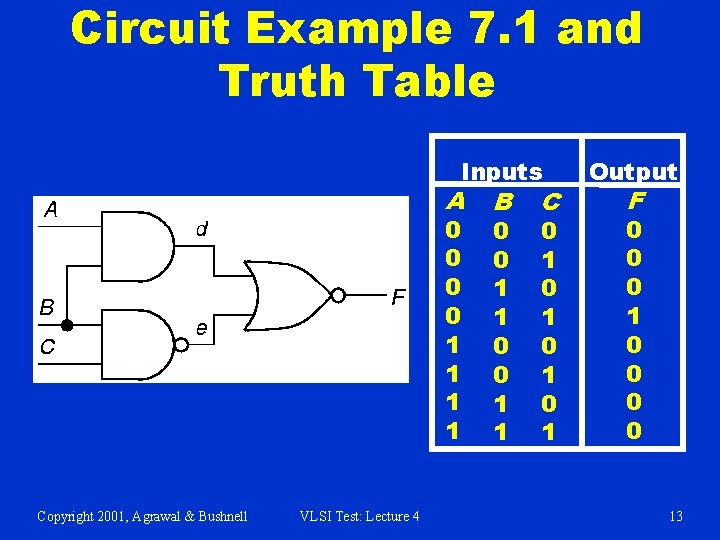

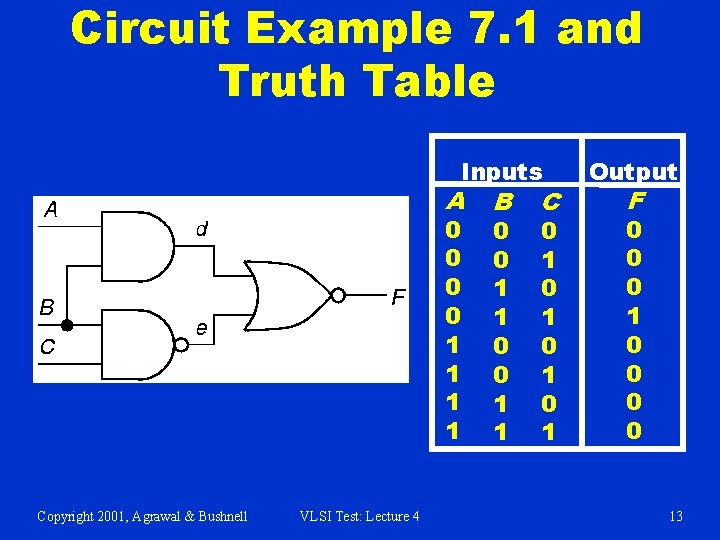

Circuit Example 7. 1 and Truth Table Inputs A 0 0 1 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 B 0 0 1 1 C 0 1 0 1 Output F 0 0 0 13

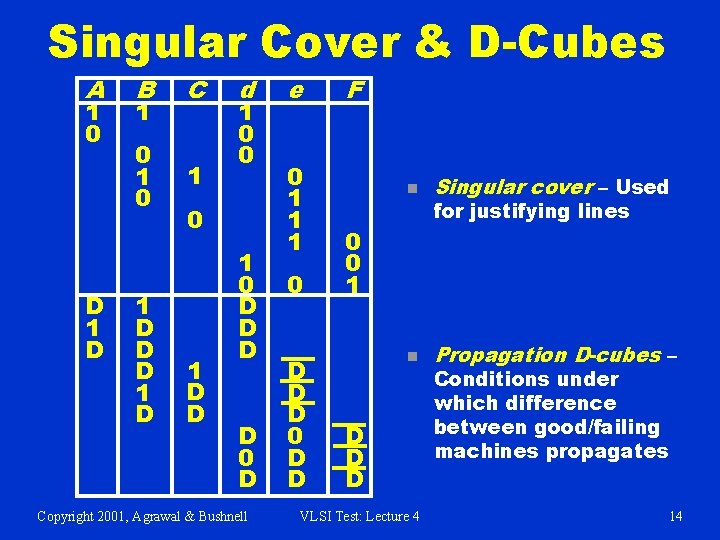

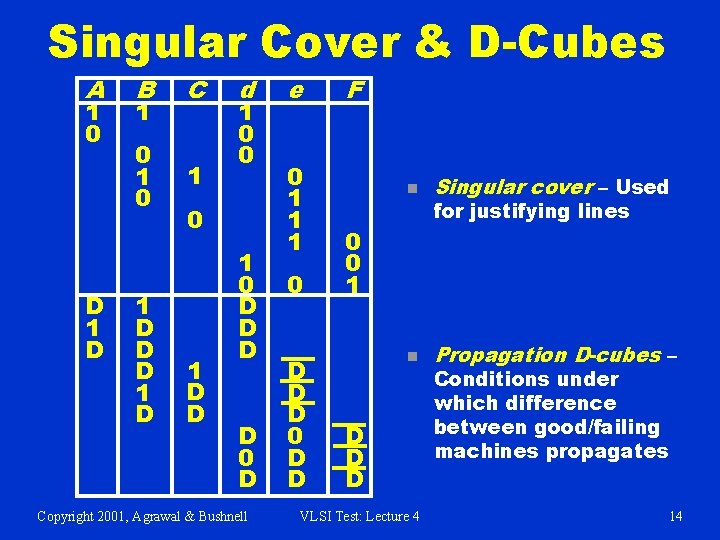

Singular Cover & D-Cubes A 1 0 D 1 D B C 0 1 1 1 D D D 1 D d 1 0 0 0 1 D D 1 0 D D 0 D Copyright 2001, Agrawal & Bushnell e 0 1 1 1 0 D D D 0 D D F n Singular cover – Used n Propagation D-cubes – 0 0 1 D D D VLSI Test: Lecture 4 for justifying lines Conditions under which difference between good/failing machines propagates 14

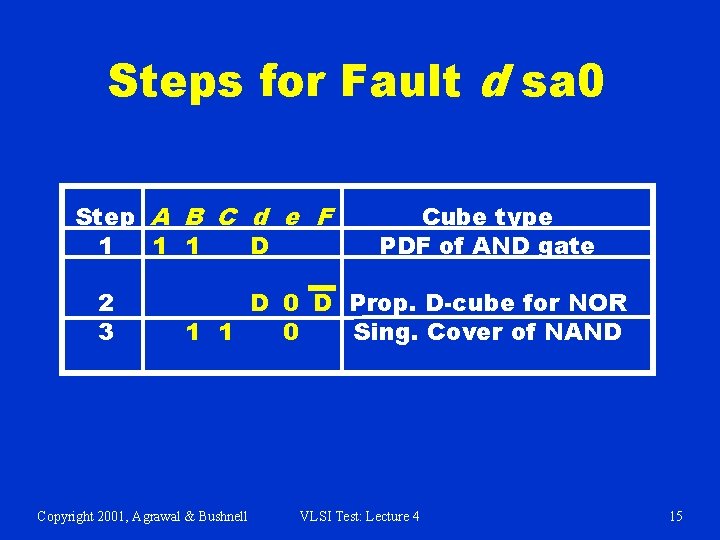

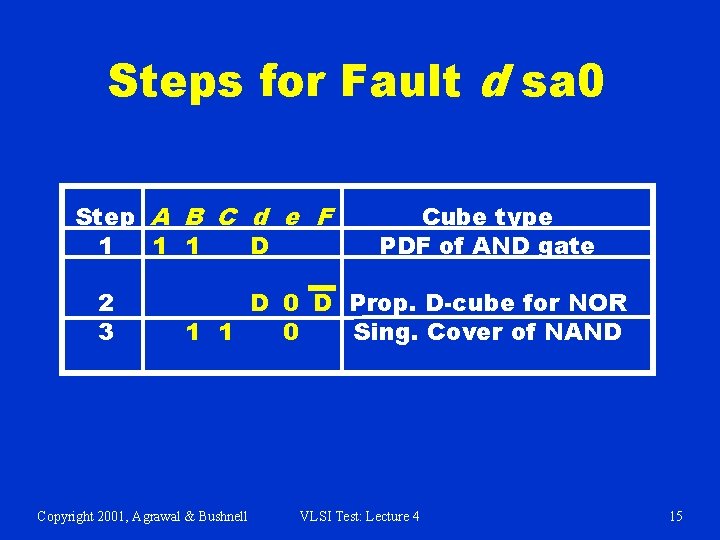

Steps for Fault d sa 0 Step A B C d e F 1 1 1 D 2 3 Cube type PDF of AND gate D 0 D Prop. D-cube for NOR 1 1 0 Sing. Cover of NAND Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 15

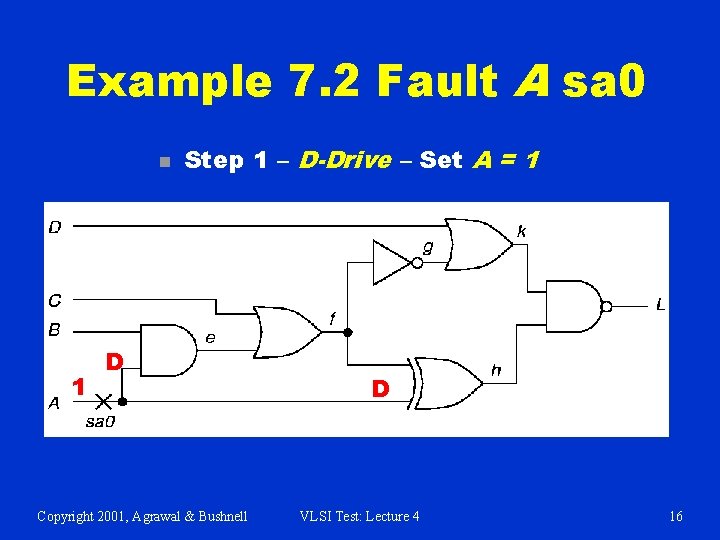

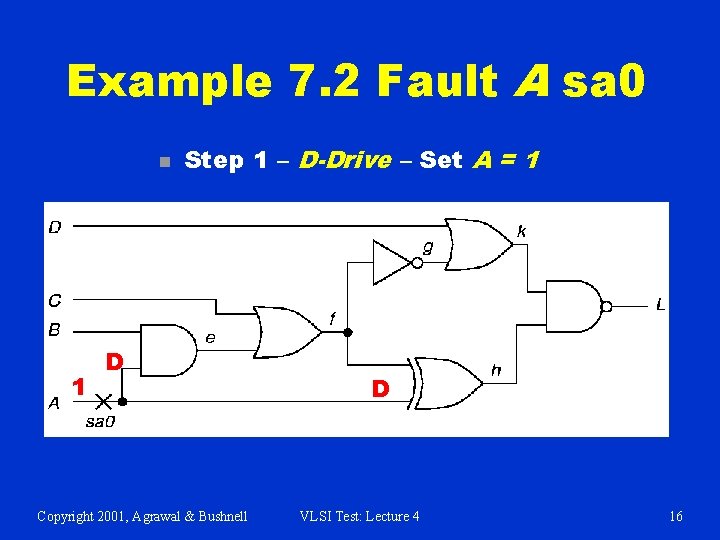

Example 7. 2 Fault A sa 0 n 1 Step 1 – D-Drive – Set A = 1 D Copyright 2001, Agrawal & Bushnell D VLSI Test: Lecture 4 16

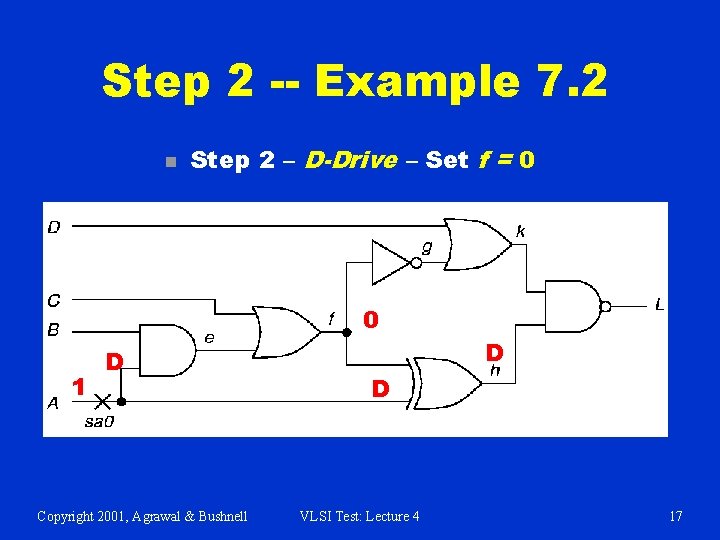

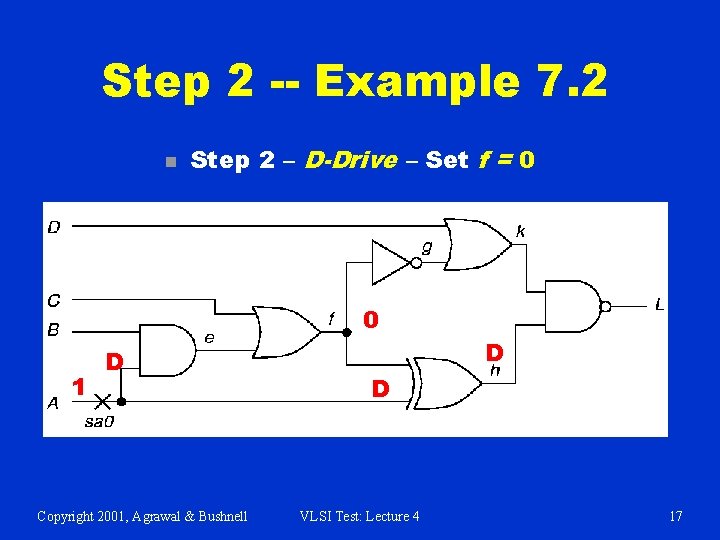

Step 2 -- Example 7. 2 n Step 2 – D-Drive – Set f = 0 0 1 D Copyright 2001, Agrawal & Bushnell D D VLSI Test: Lecture 4 17

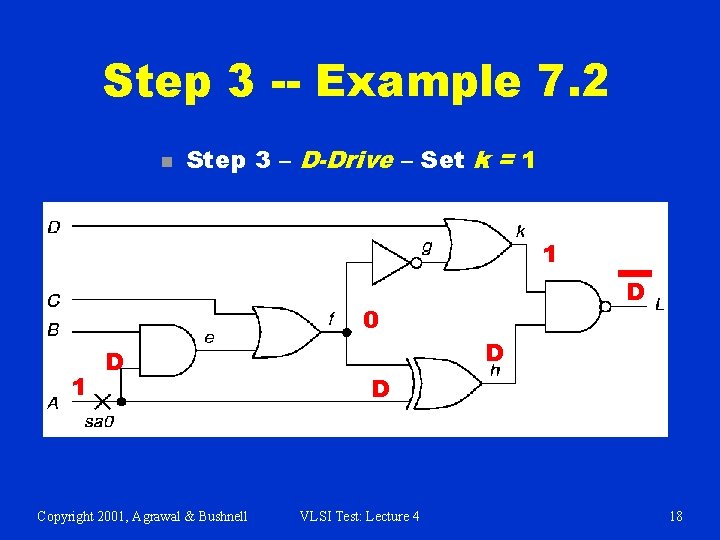

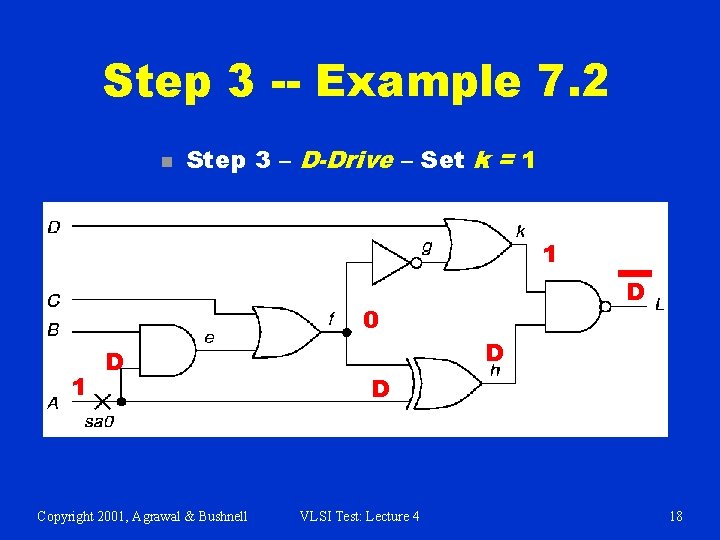

Step 3 -- Example 7. 2 n Step 3 – D-Drive – Set k = 1 1 0 1 D Copyright 2001, Agrawal & Bushnell D D D VLSI Test: Lecture 4 18

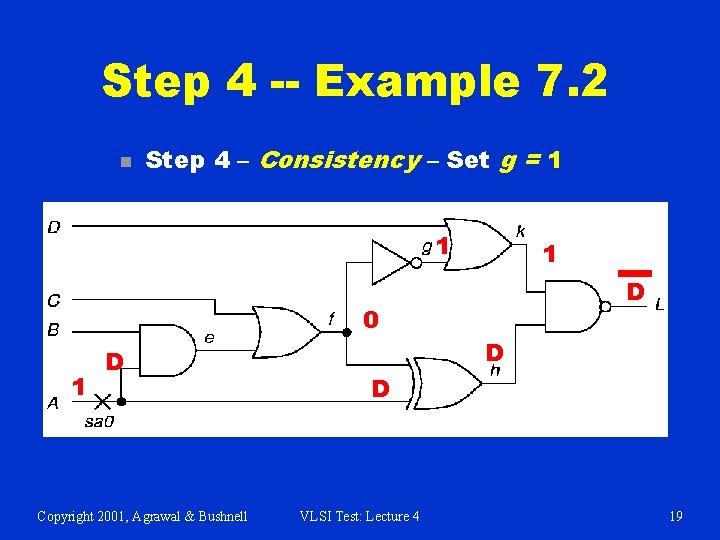

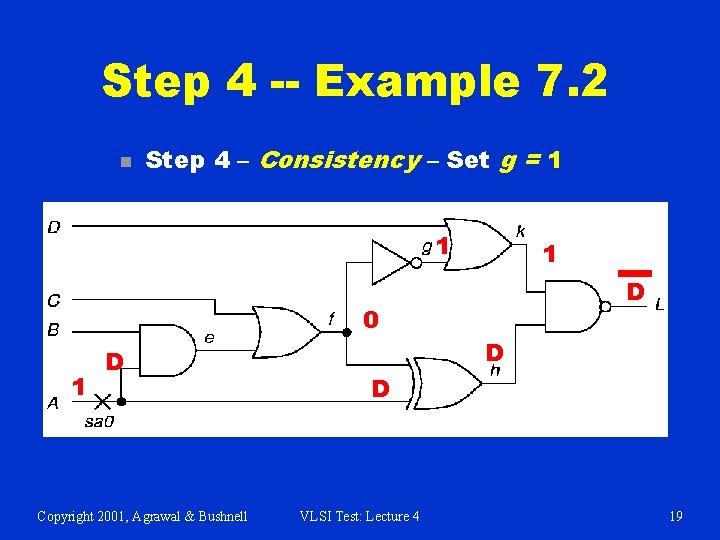

Step 4 -- Example 7. 2 n Step 4 – Consistency – Set g = 1 1 0 1 D Copyright 2001, Agrawal & Bushnell 1 D D D VLSI Test: Lecture 4 19

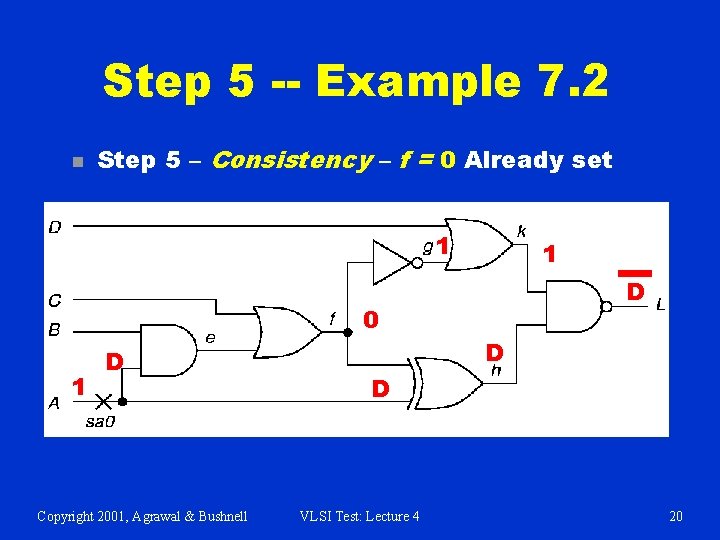

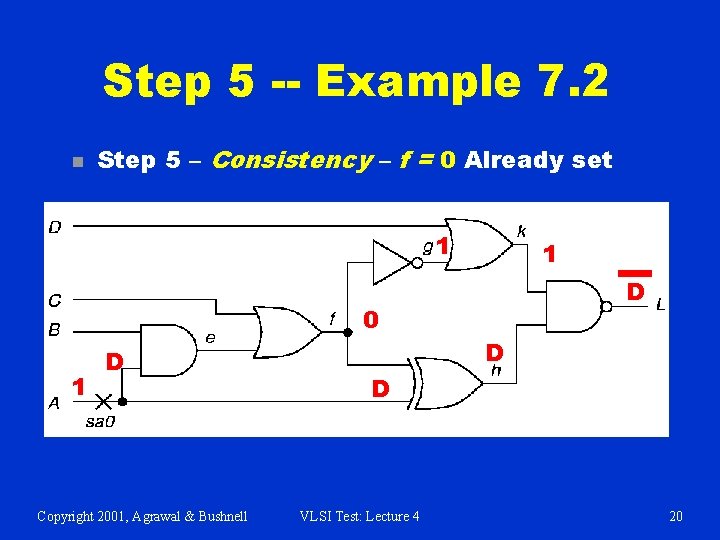

Step 5 -- Example 7. 2 n Step 5 – Consistency – f = 0 Already set 1 0 1 D Copyright 2001, Agrawal & Bushnell 1 D D D VLSI Test: Lecture 4 20

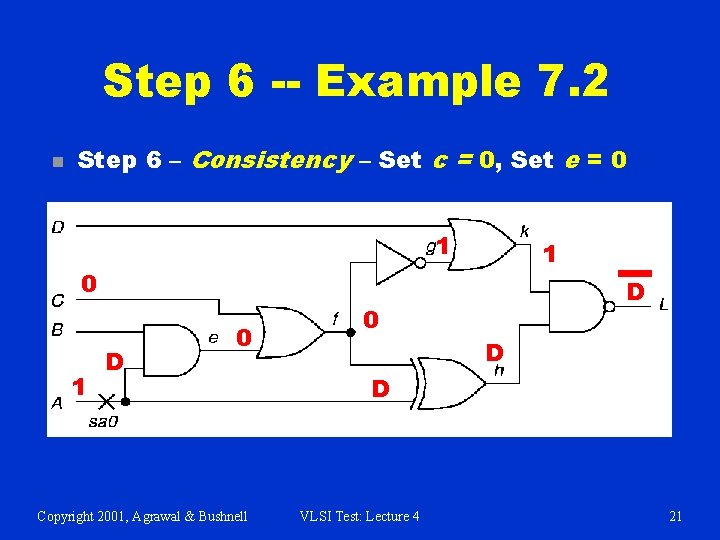

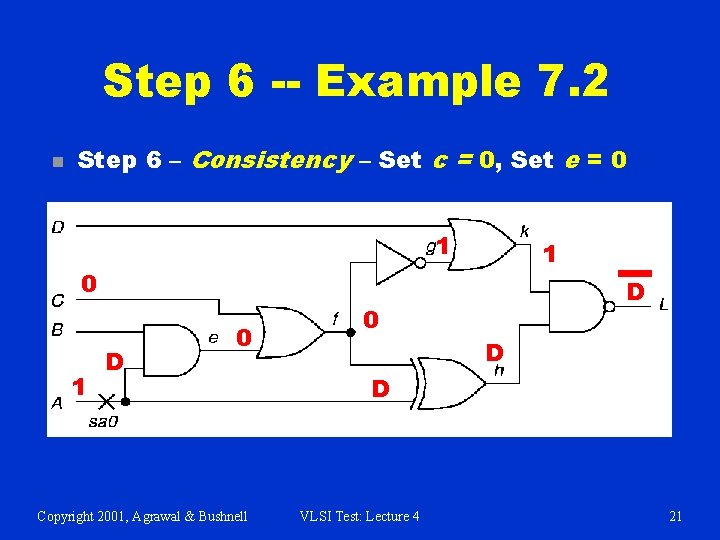

Step 6 -- Example 7. 2 n Step 6 – Consistency – Set c = 0, Set e = 0 1 1 0 1 D 0 Copyright 2001, Agrawal & Bushnell 0 D D D VLSI Test: Lecture 4 21

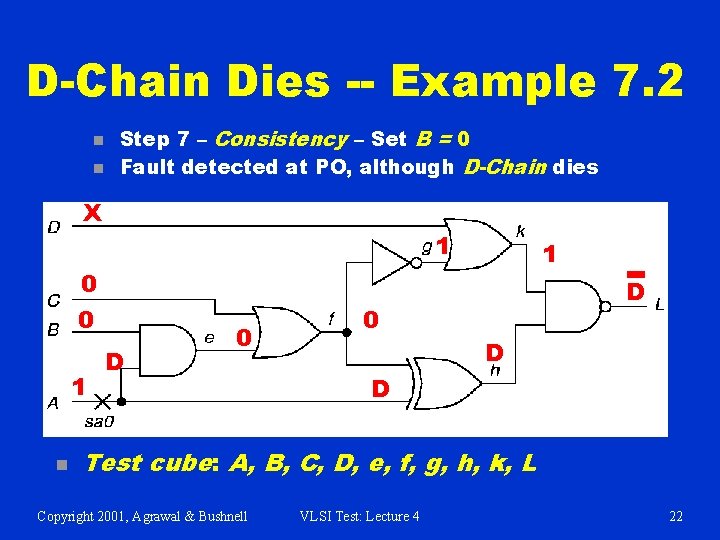

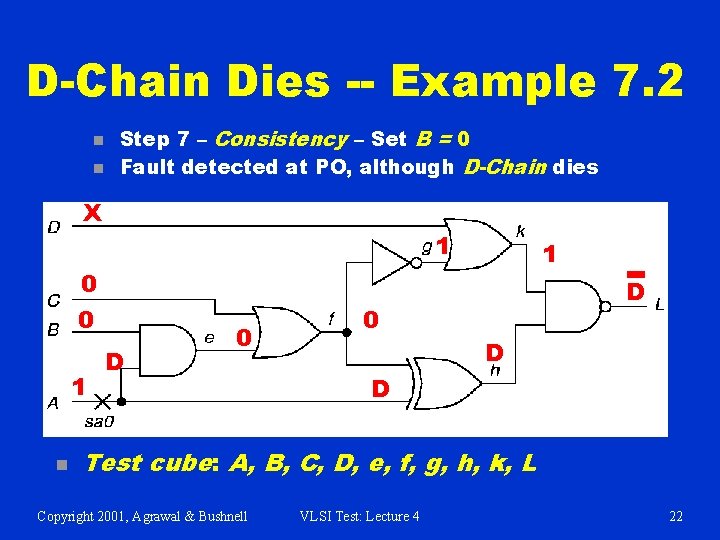

D-Chain Dies -- Example 7. 2 n n Step 7 – Consistency – Set B = 0 Fault detected at PO, although D-Chain dies X 1 0 0 1 n D 0 0 1 D D D Test cube: A, B, C, D, e, f, g, h, k, L Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 22

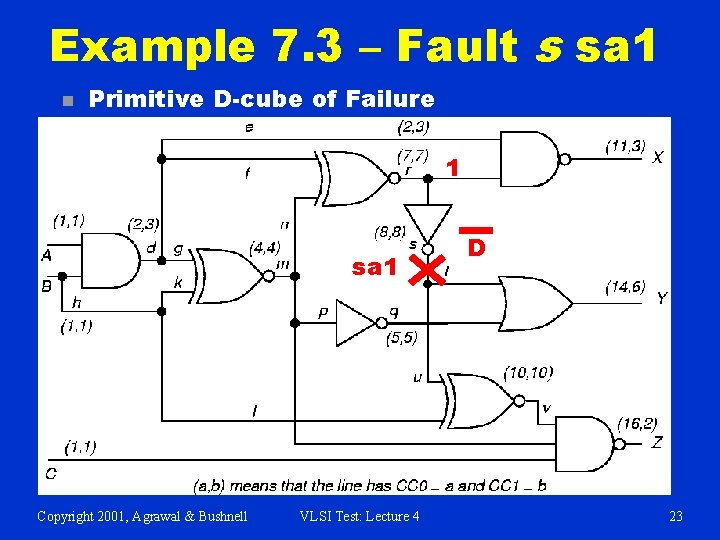

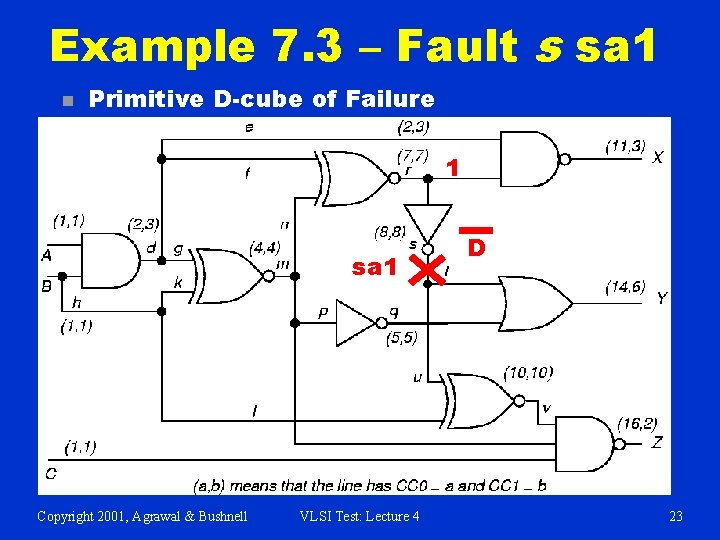

Example 7. 3 – Fault s sa 1 n Primitive D-cube of Failure 1 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 D 23

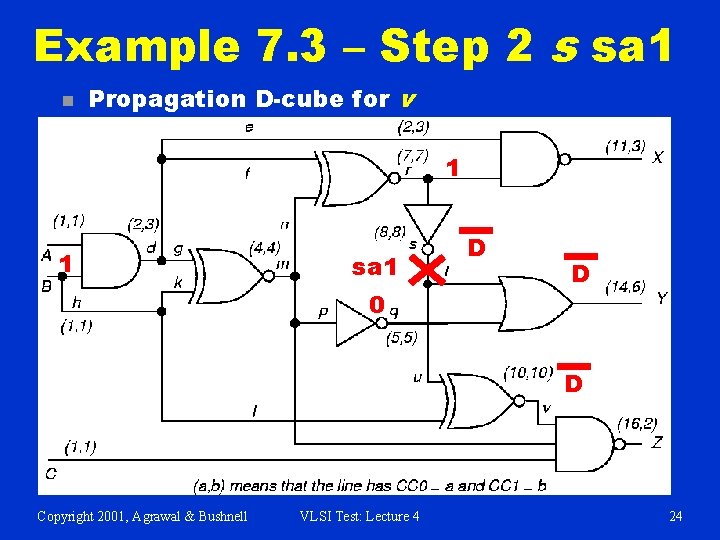

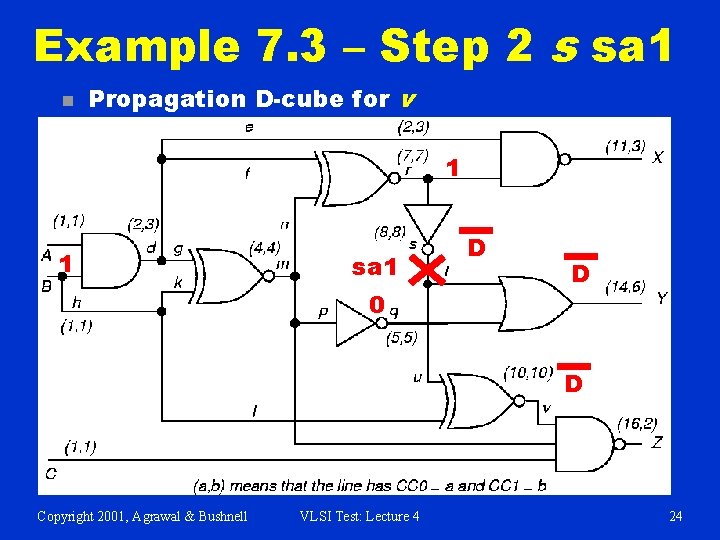

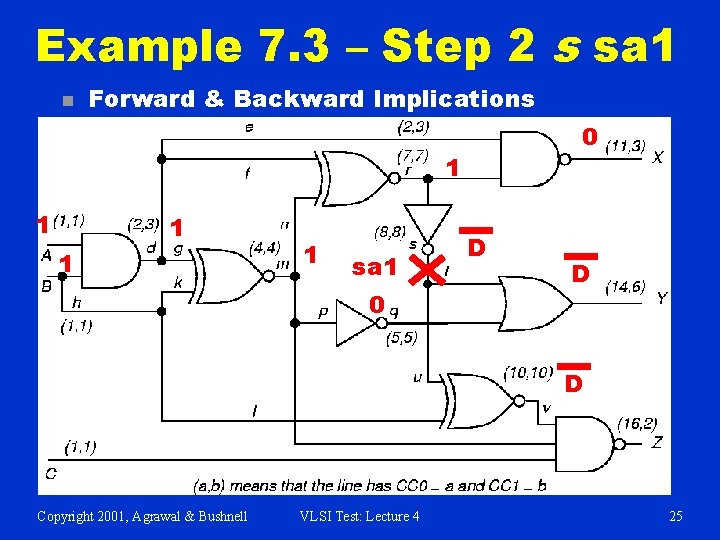

Example 7. 3 – Step 2 s sa 1 n Propagation D-cube for v 1 1 sa 1 0 D D D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 24

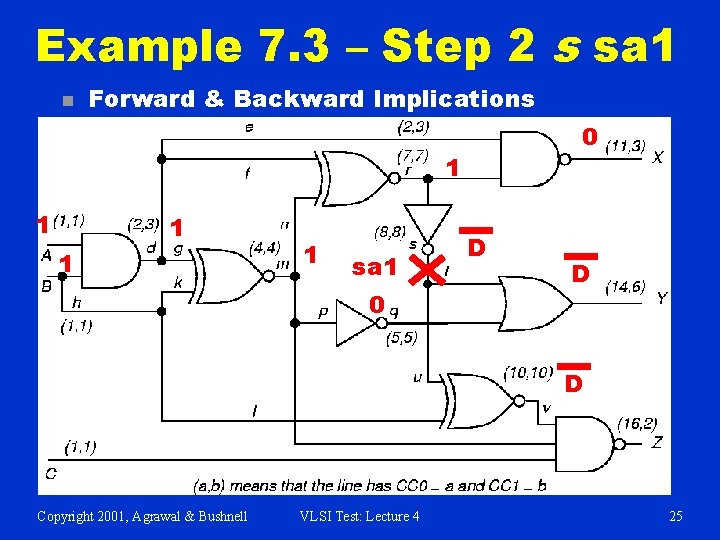

Example 7. 3 – Step 2 s sa 1 n Forward & Backward Implications 0 1 1 1 sa 1 0 D D D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 25

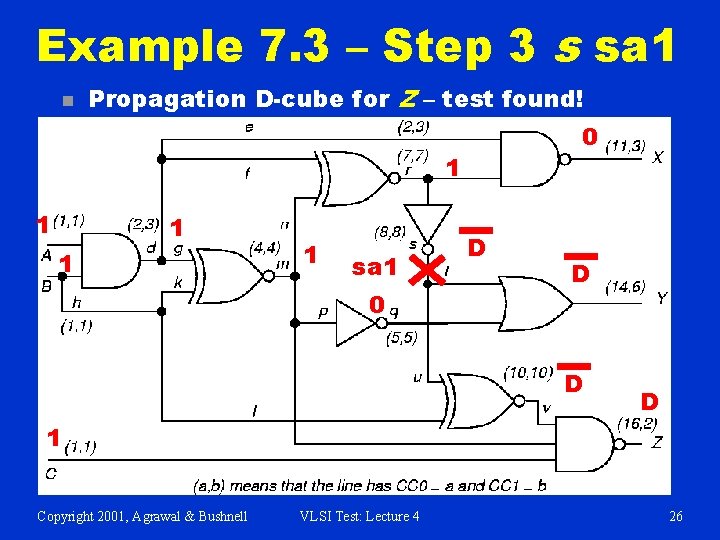

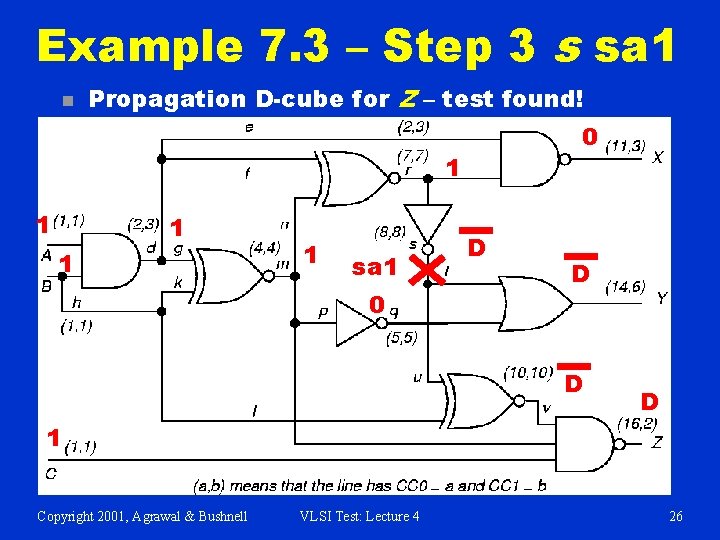

Example 7. 3 – Step 3 s sa 1 n Propagation D-cube for Z – test found! 0 1 1 1 sa 1 0 D D 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 26

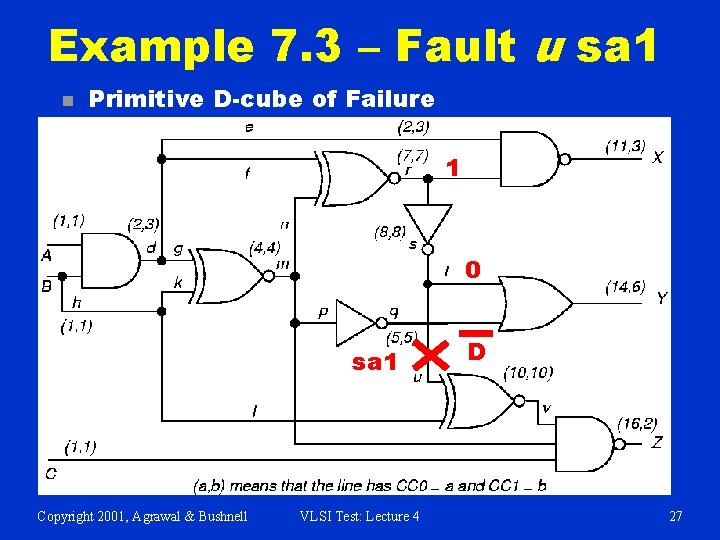

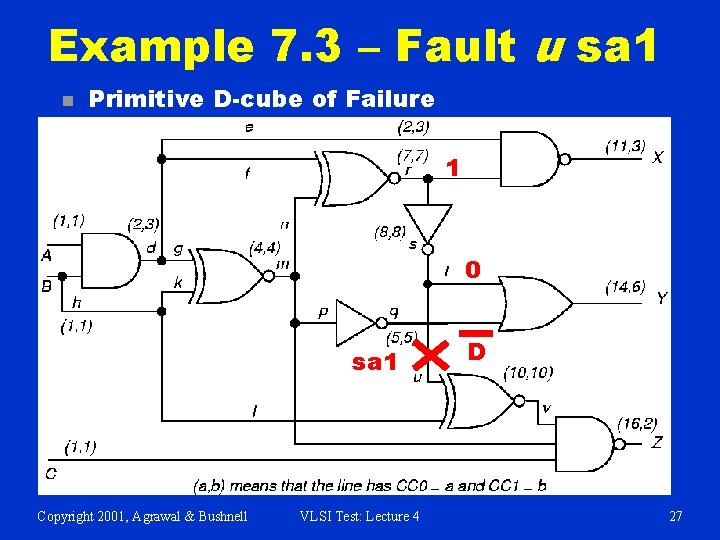

Example 7. 3 – Fault u sa 1 n Primitive D-cube of Failure 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 D 27

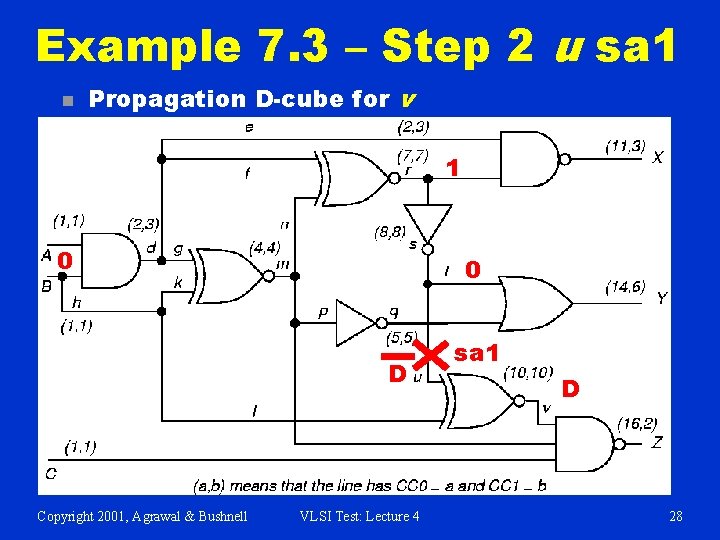

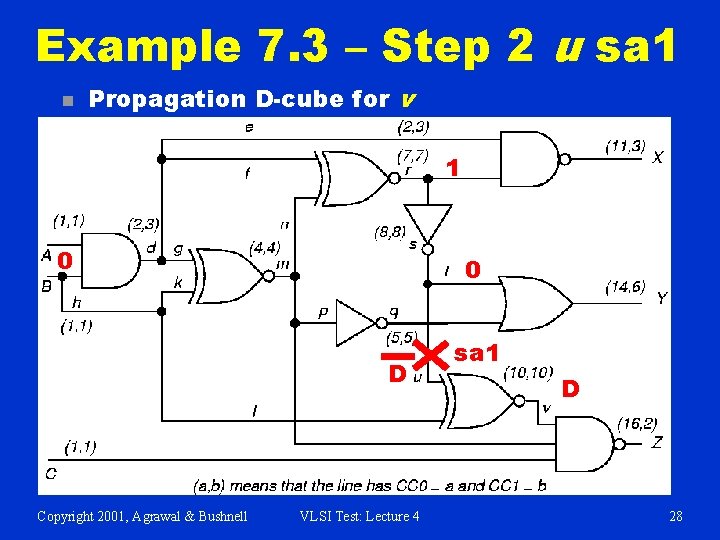

Example 7. 3 – Step 2 u sa 1 n Propagation D-cube for v 1 0 0 D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 sa 1 D 28

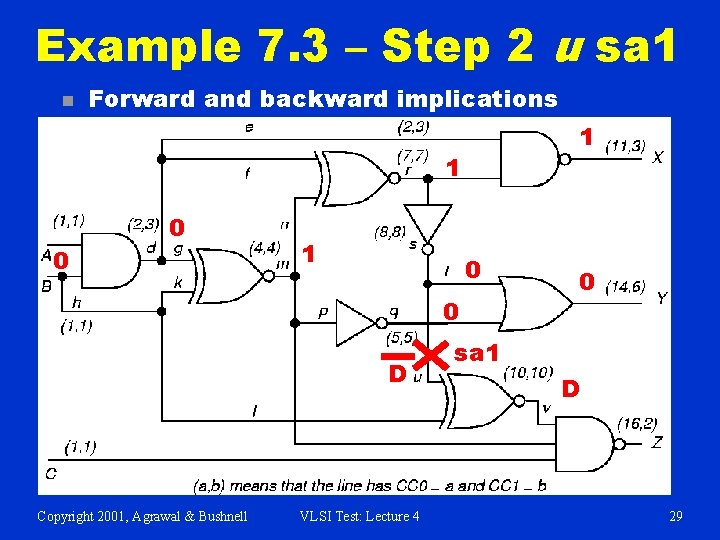

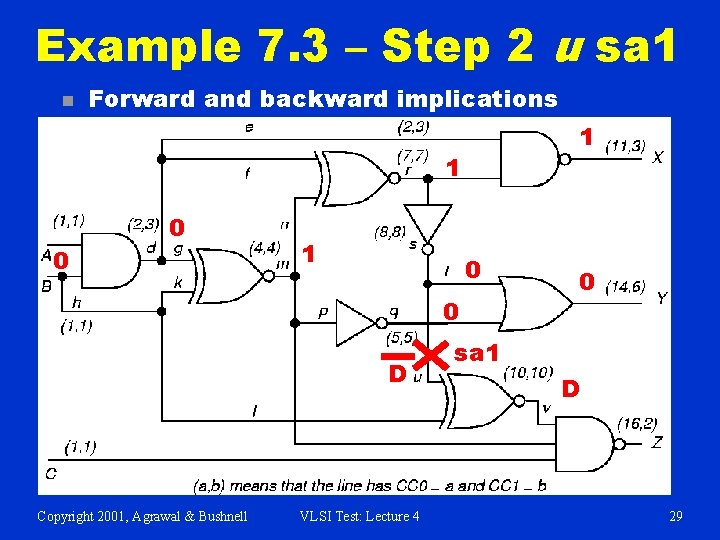

Example 7. 3 – Step 2 u sa 1 n Forward and backward implications 1 1 0 0 D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 0 sa 1 D 29

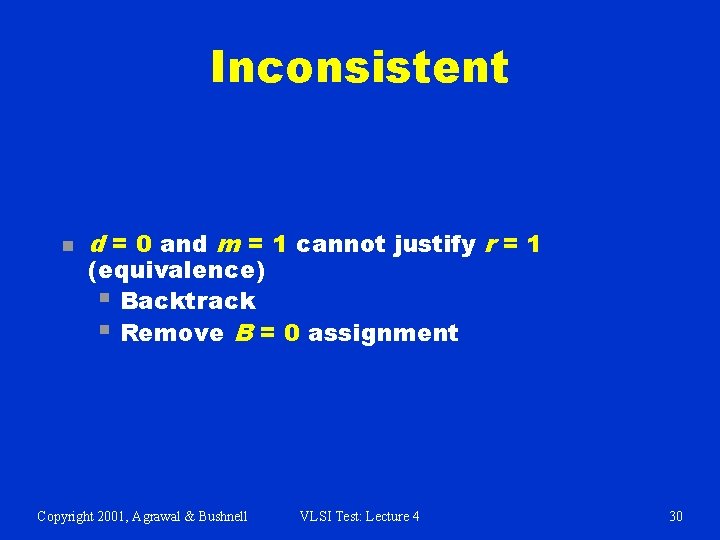

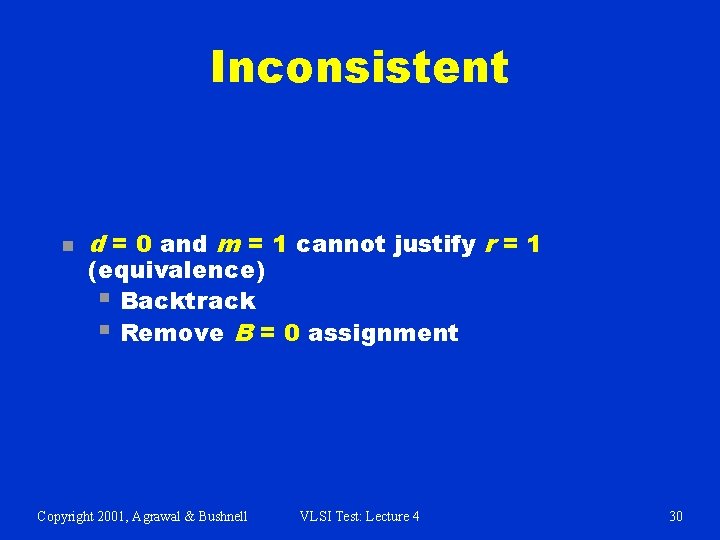

Inconsistent n d = 0 and m = 1 cannot justify r = 1 (equivalence) § Backtrack § Remove B = 0 assignment Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 30

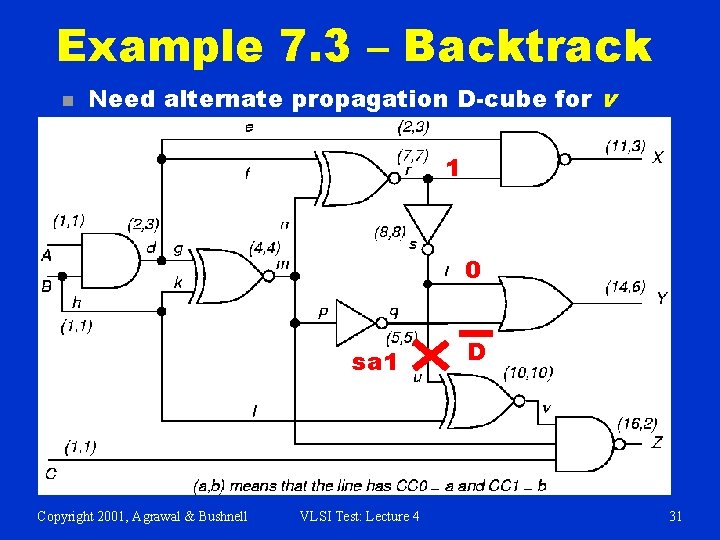

Example 7. 3 – Backtrack n Need alternate propagation D-cube for v 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 D 31

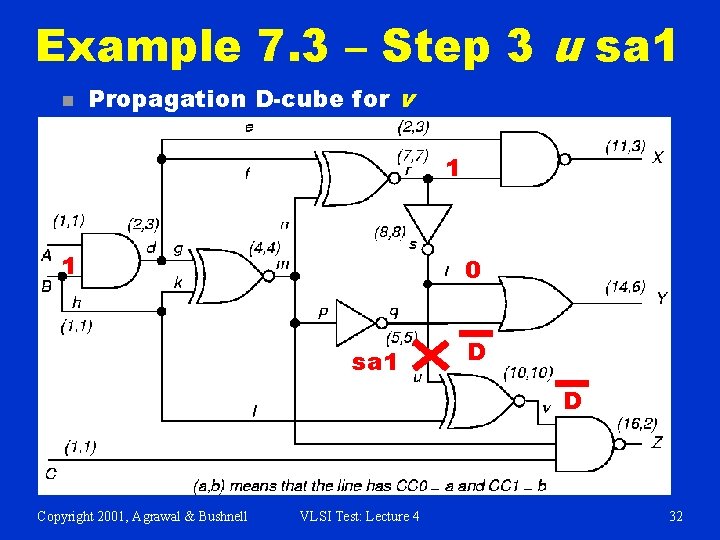

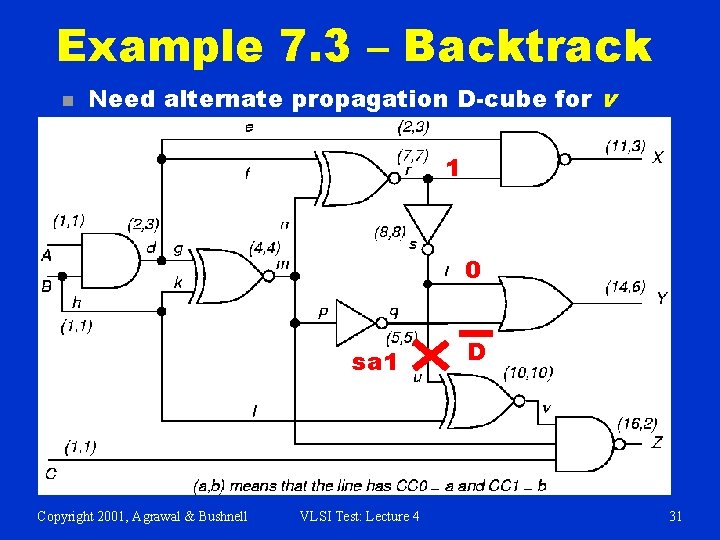

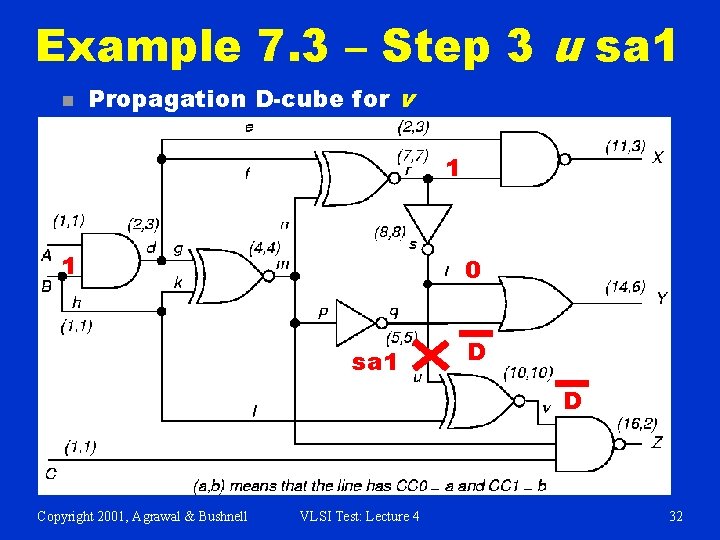

Example 7. 3 – Step 3 u sa 1 n Propagation D-cube for v 1 1 0 sa 1 D D Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 32

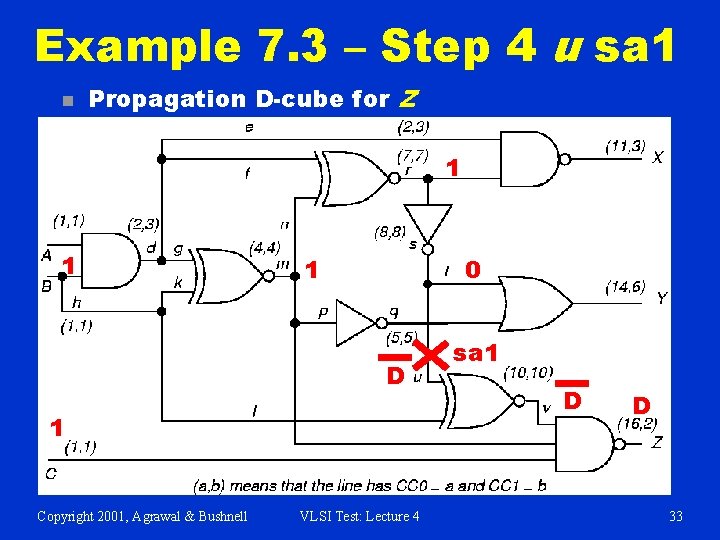

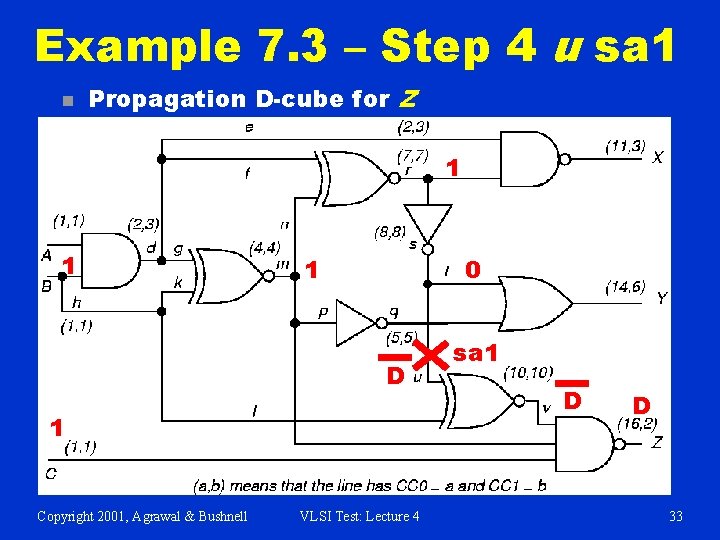

Example 7. 3 – Step 4 u sa 1 n Propagation D-cube for Z 1 1 1 0 D 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 sa 1 D D 33

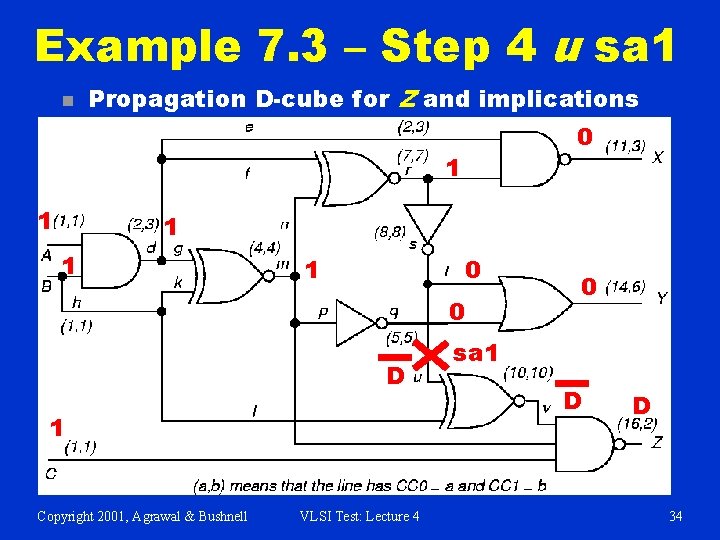

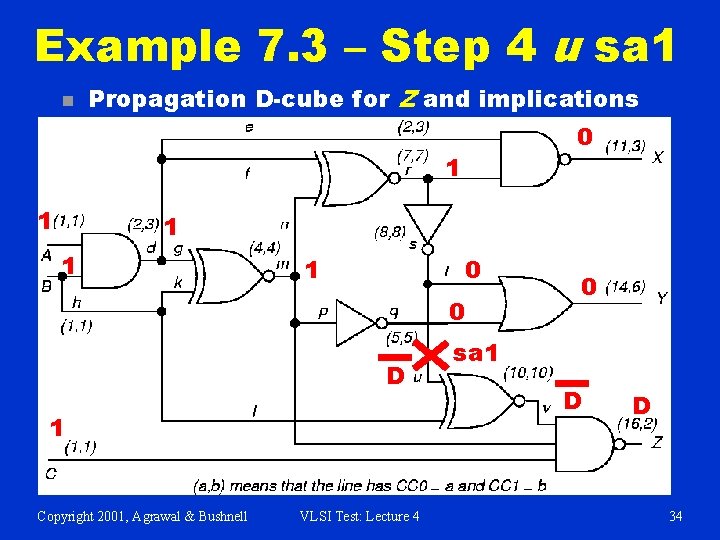

Example 7. 3 – Step 4 u sa 1 n Propagation D-cube for Z and implications 0 1 1 1 0 0 D 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 0 sa 1 D D 34

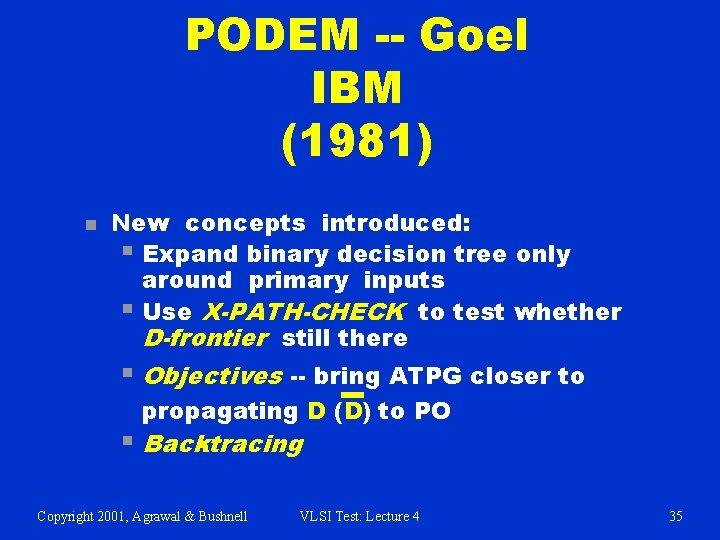

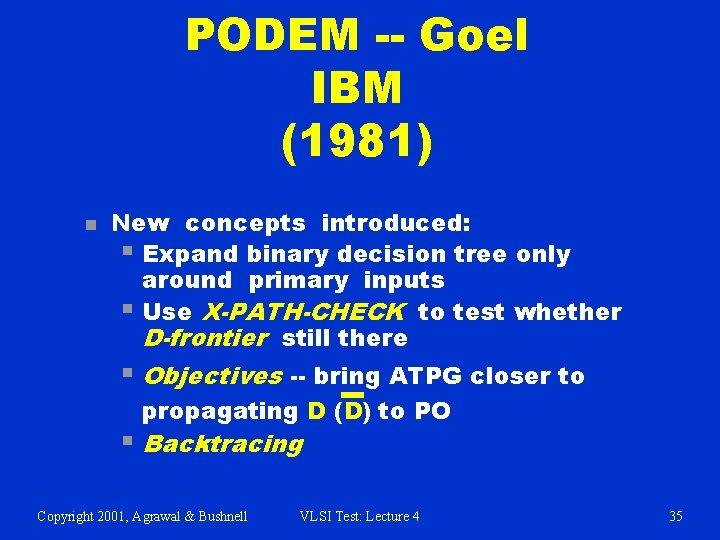

PODEM -- Goel IBM (1981) n New concepts introduced: § Expand binary decision tree only around primary inputs § Use X-PATH-CHECK to test whether D-frontier still there § Objectives -- bring ATPG closer to propagating D (D) to PO § Backtracing Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 35

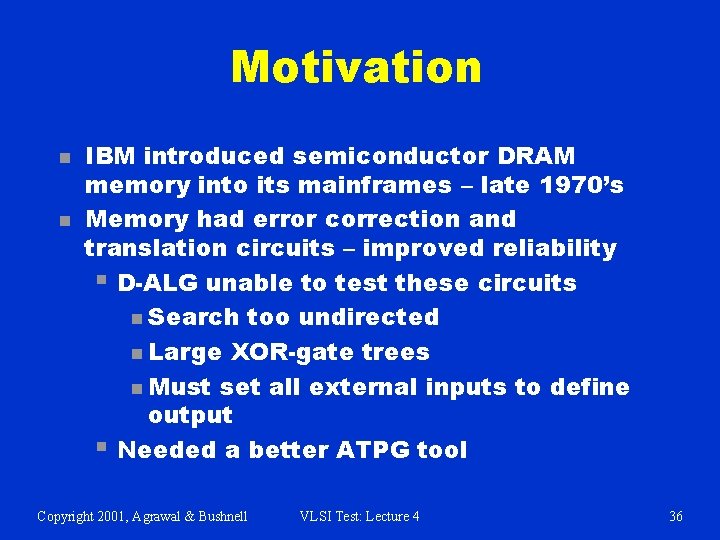

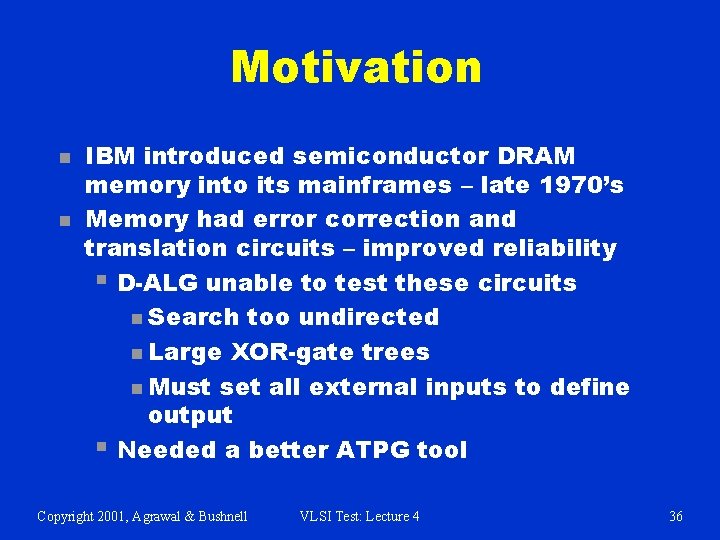

Motivation n n IBM introduced semiconductor DRAM memory into its mainframes – late 1970’s Memory had error correction and translation circuits – improved reliability § D-ALG unable to test these circuits n Search too undirected n Large XOR-gate trees n Must set all external inputs to define output § Needed a better ATPG tool Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 36

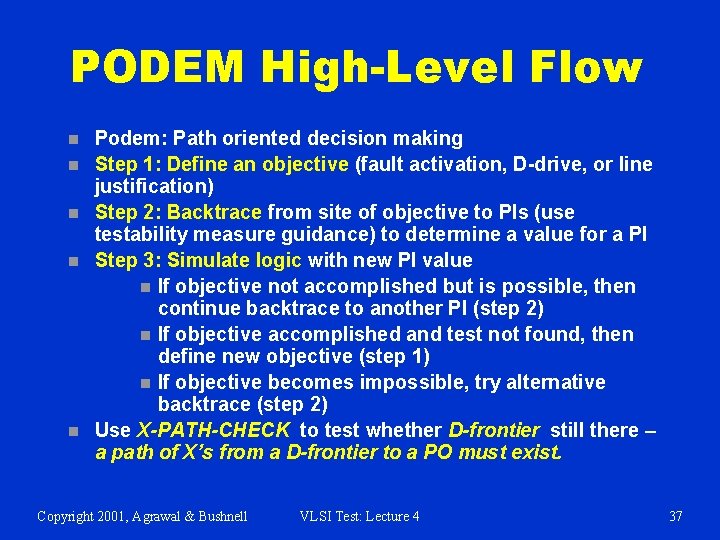

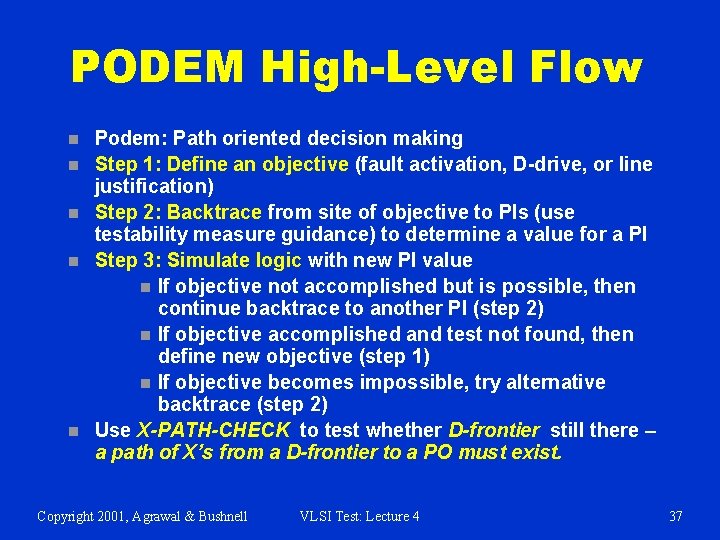

PODEM High-Level Flow n n n Podem: Path oriented decision making Step 1: Define an objective (fault activation, D-drive, or line justification) Step 2: Backtrace from site of objective to PIs (use testability measure guidance) to determine a value for a PI Step 3: Simulate logic with new PI value n If objective not accomplished but is possible, then continue backtrace to another PI (step 2) n If objective accomplished and test not found, then define new objective (step 1) n If objective becomes impossible, try alternative backtrace (step 2) Use X-PATH-CHECK to test whether D-frontier still there – a path of X’s from a D-frontier to a PO must exist. Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 37

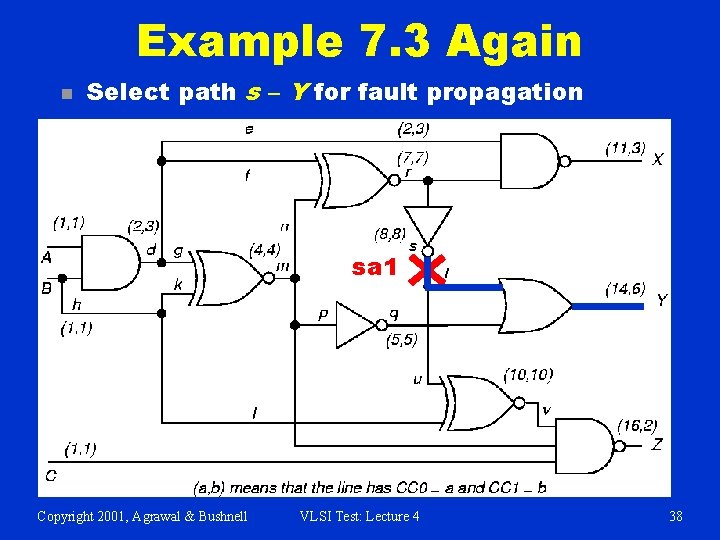

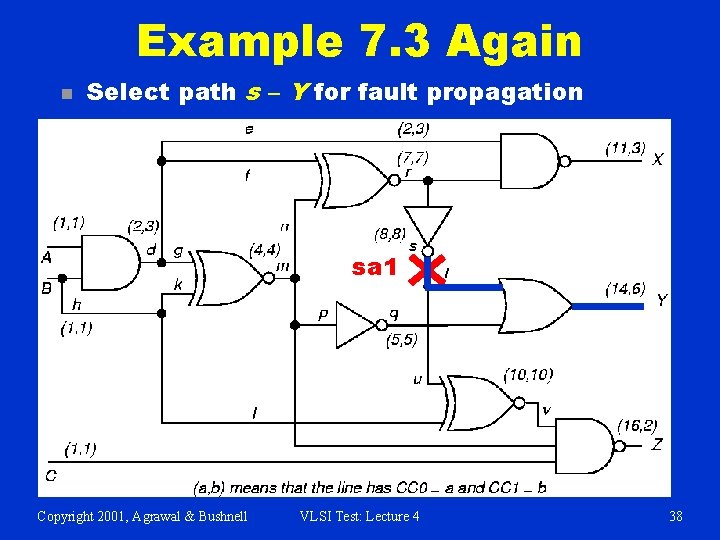

Example 7. 3 Again n Select path s – Y for fault propagation sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 38

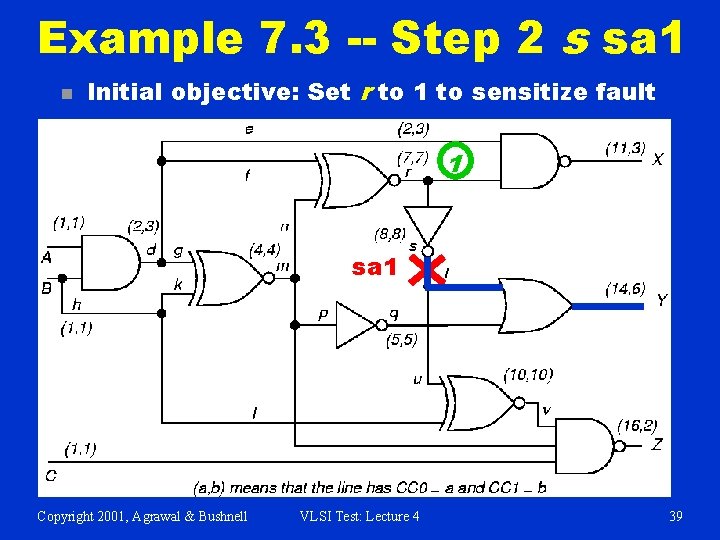

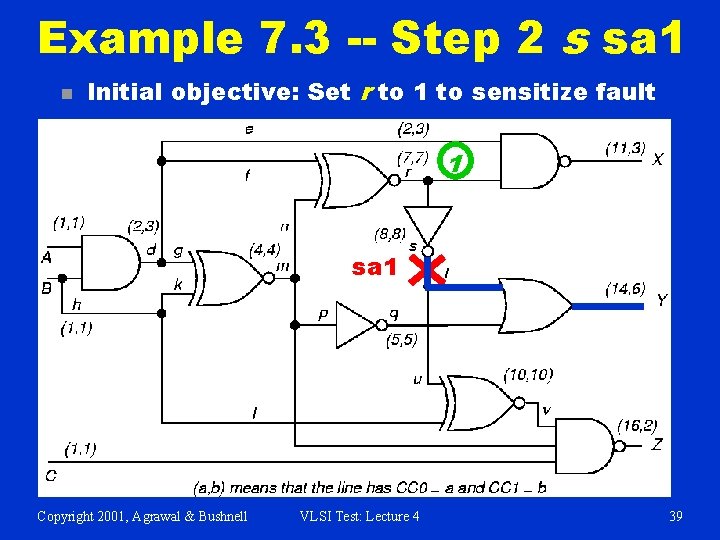

Example 7. 3 -- Step 2 s sa 1 n Initial objective: Set r to 1 to sensitize fault 1 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 39

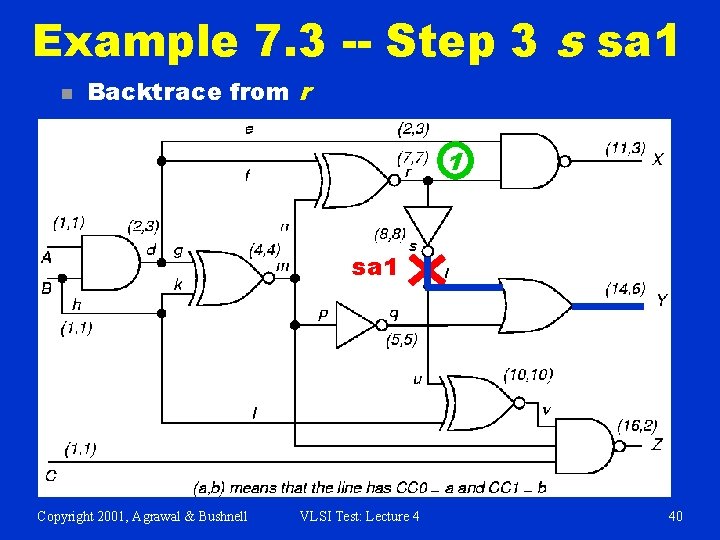

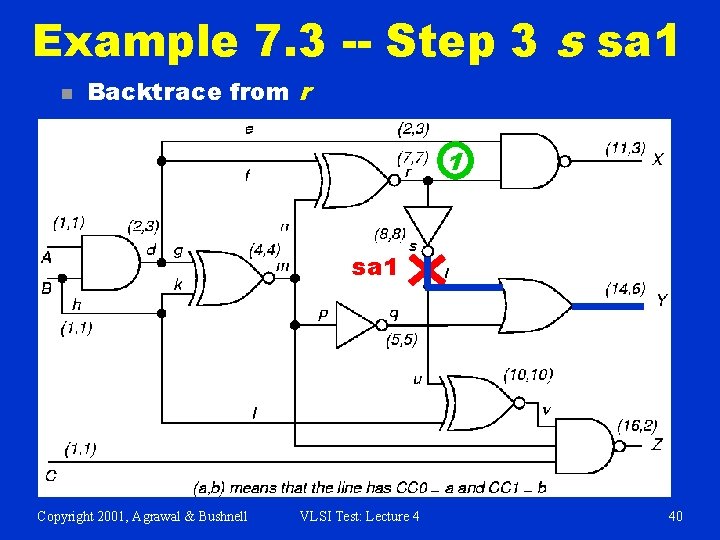

Example 7. 3 -- Step 3 s sa 1 n Backtrace from r 1 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 40

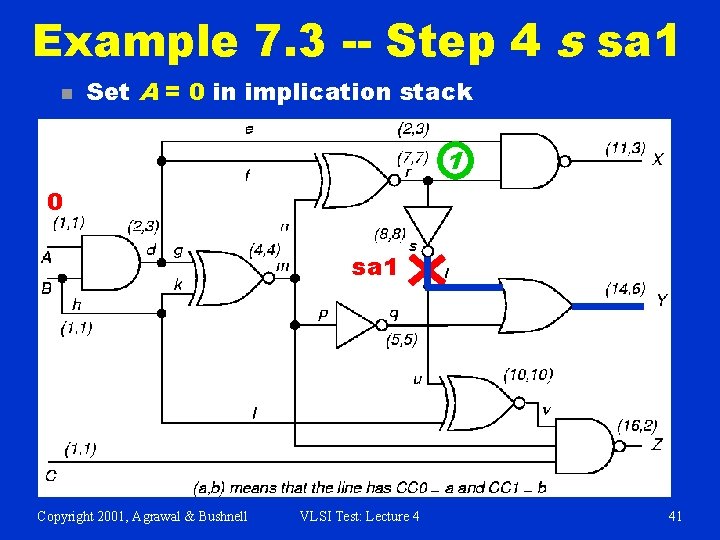

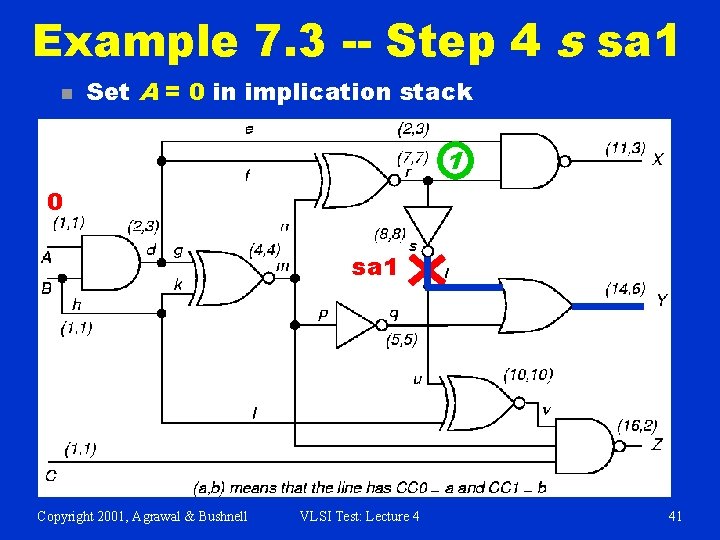

Example 7. 3 -- Step 4 s sa 1 n Set A = 0 in implication stack 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 41

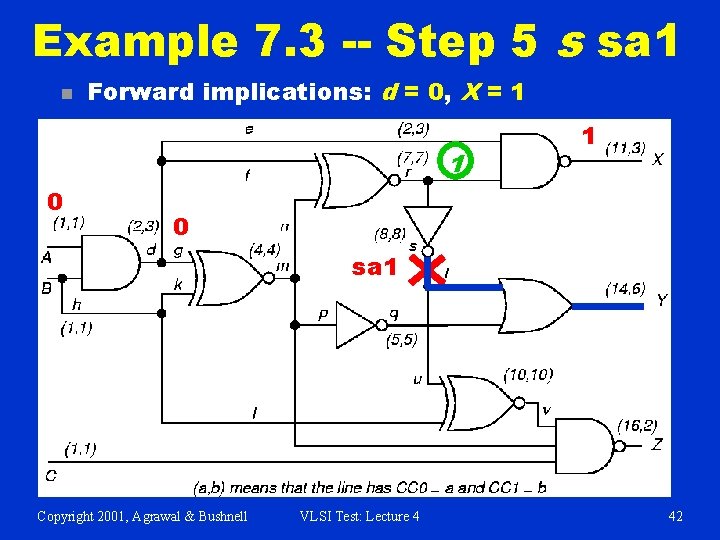

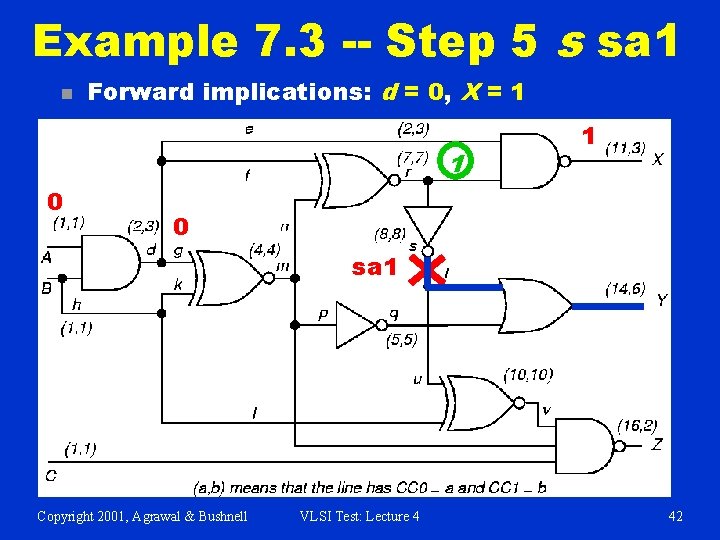

Example 7. 3 -- Step 5 s sa 1 n Forward implications: d = 0, X = 1 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 42

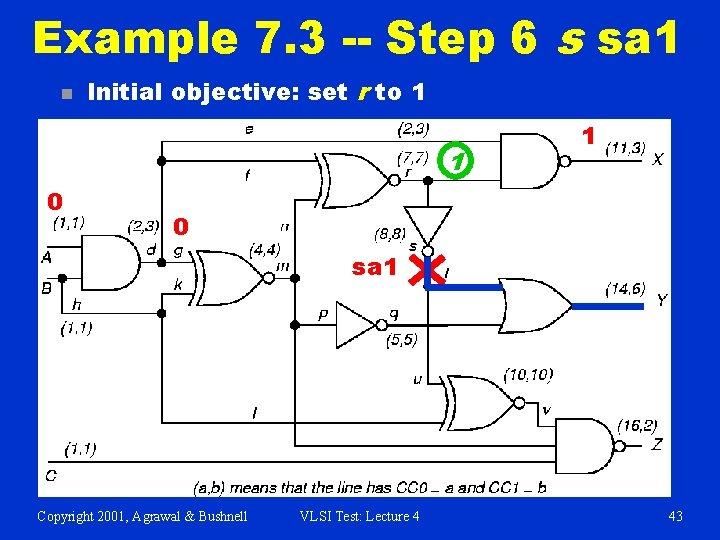

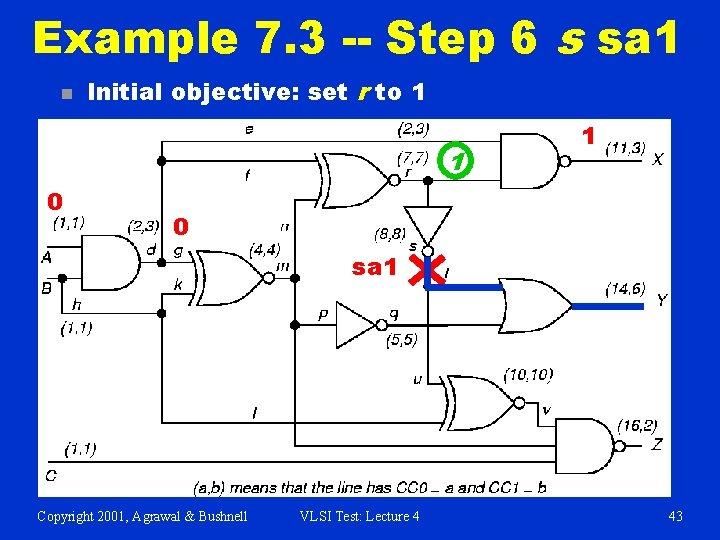

Example 7. 3 -- Step 6 s sa 1 n Initial objective: set r to 1 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 43

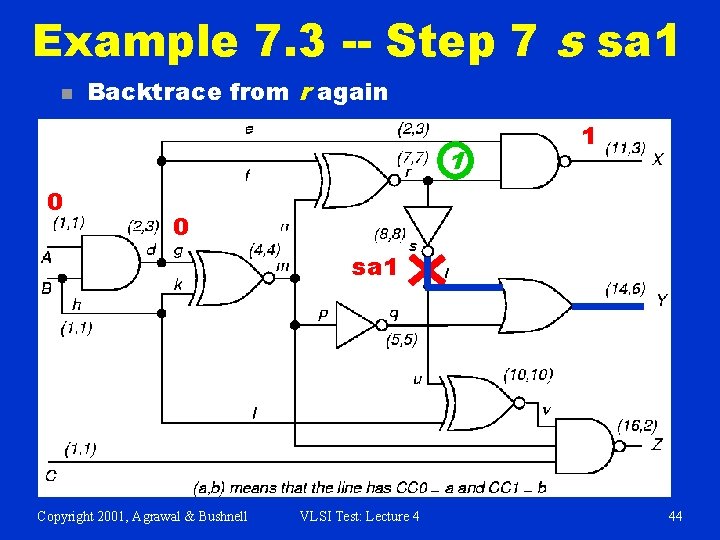

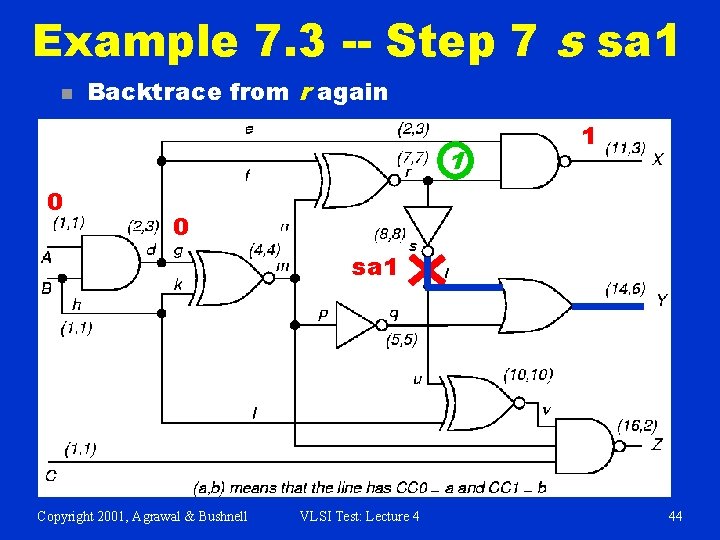

Example 7. 3 -- Step 7 s sa 1 n Backtrace from r again 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 44

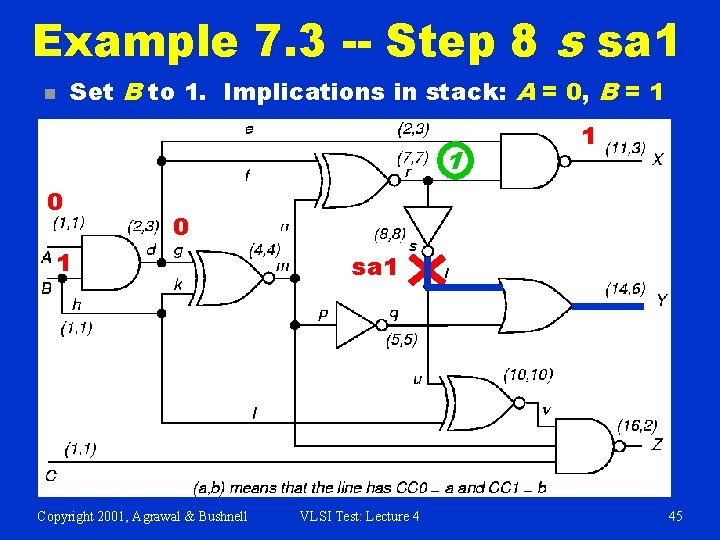

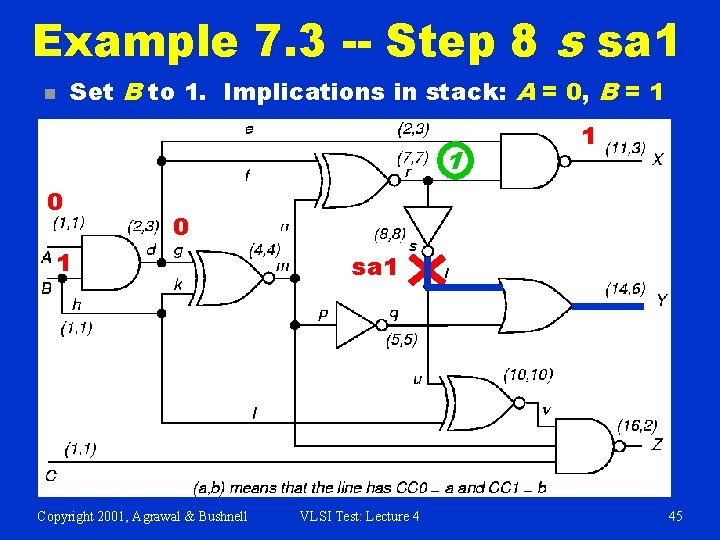

Example 7. 3 -- Step 8 s sa 1 n Set B to 1. Implications in stack: A = 0, B = 1 1 0 1 Copyright 2001, Agrawal & Bushnell sa 1 VLSI Test: Lecture 4 45

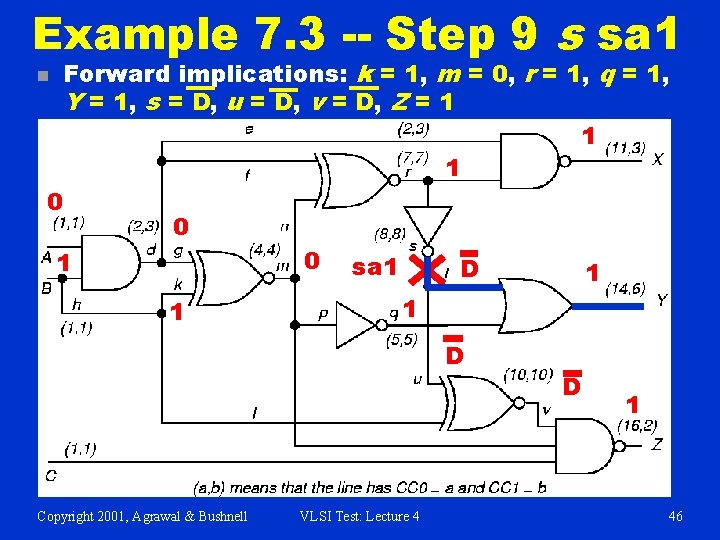

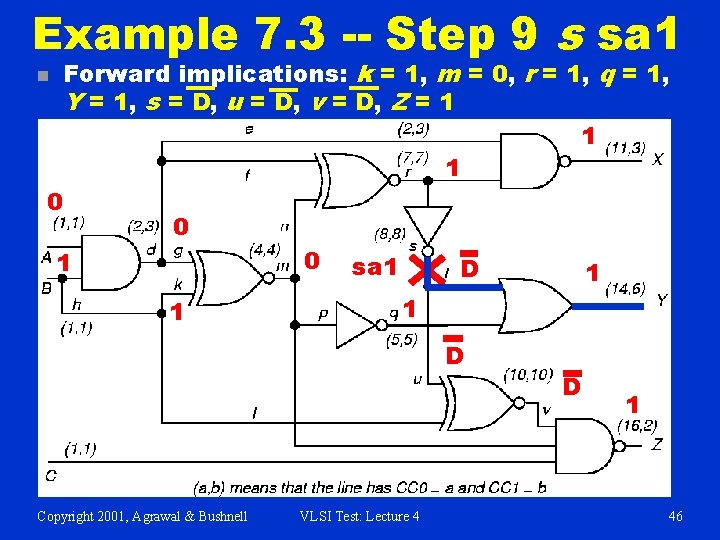

Example 7. 3 -- Step 9 s sa 1 n 0 Forward implications: k = 1, m = 0, r = 1, q = 1, Y = 1, s = D, u = D, v = D, Z = 1 1 1 0 0 1 1 sa 1 D Copyright 2001, Agrawal & Bushnell 1 VLSI Test: Lecture 4 D 1 46

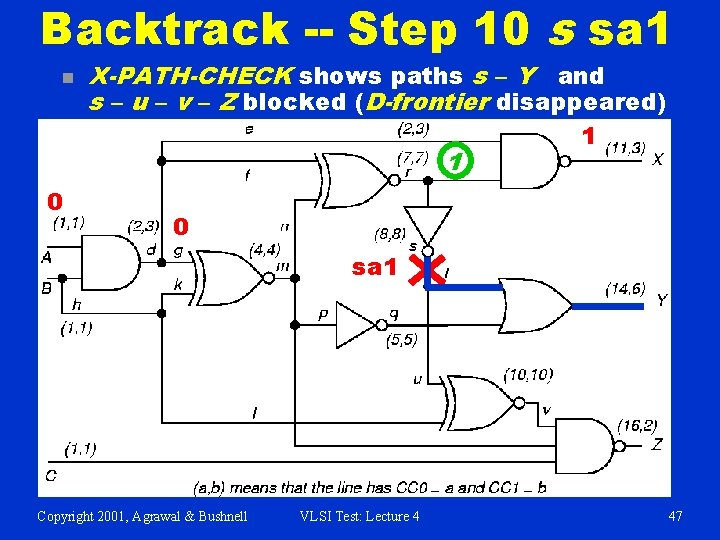

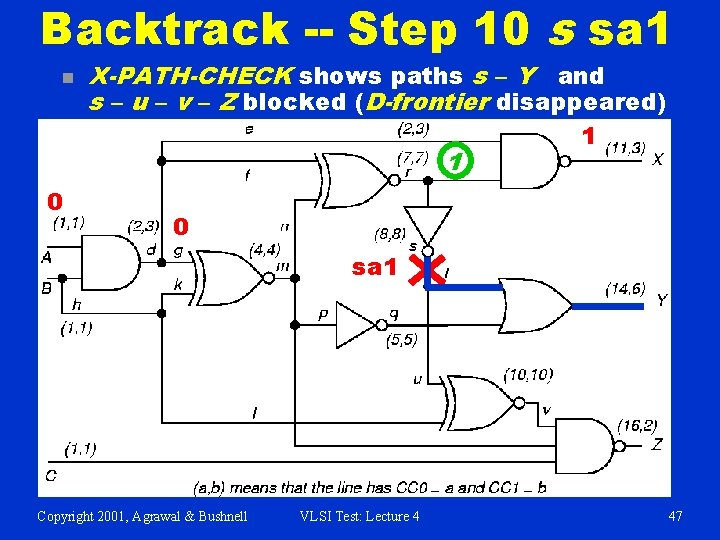

Backtrack -- Step 10 s sa 1 n X-PATH-CHECK shows paths s – Y and s – u – v – Z blocked (D-frontier disappeared) 1 0 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 47

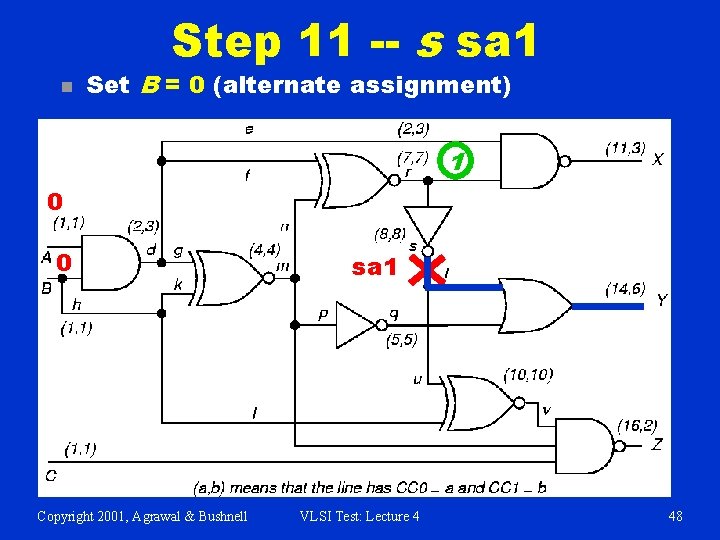

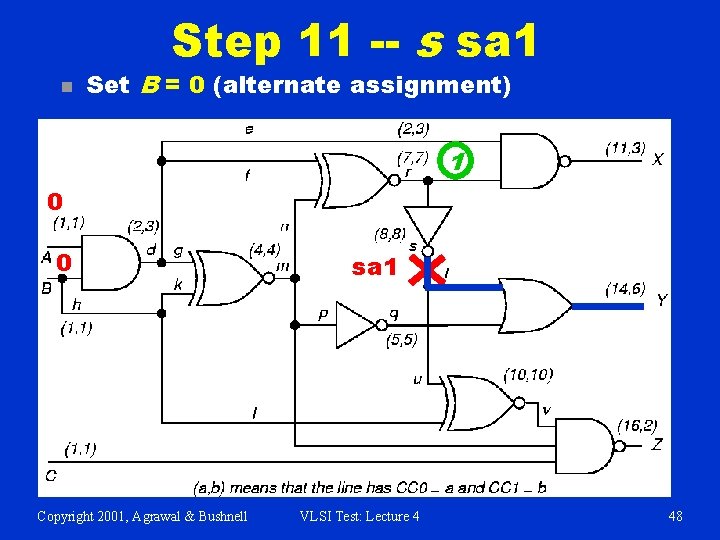

Step 11 -- s sa 1 n Set B = 0 (alternate assignment) 1 0 0 Copyright 2001, Agrawal & Bushnell sa 1 VLSI Test: Lecture 4 48

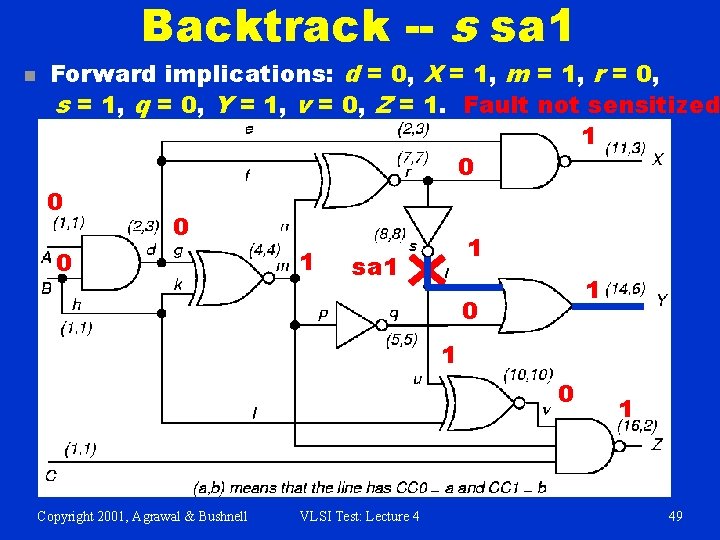

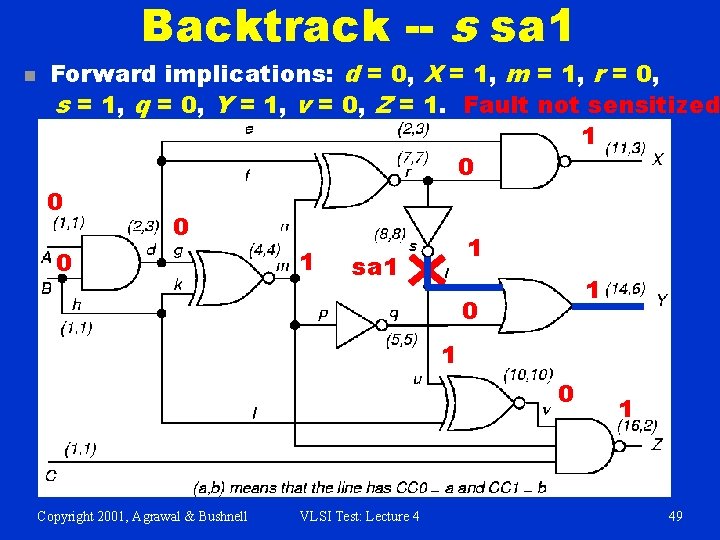

Backtrack -- s sa 1 n Forward implications: d = 0, X = 1, m = 1, r = 0, s = 1, q = 0, Y = 1, v = 0, Z = 1. Fault not sensitized 1 0 0 0 1 1 0 sa 1 1 0 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 1 49

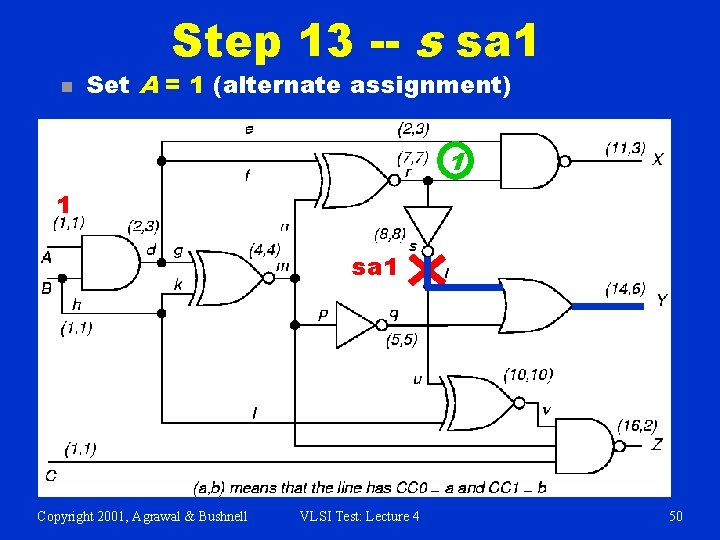

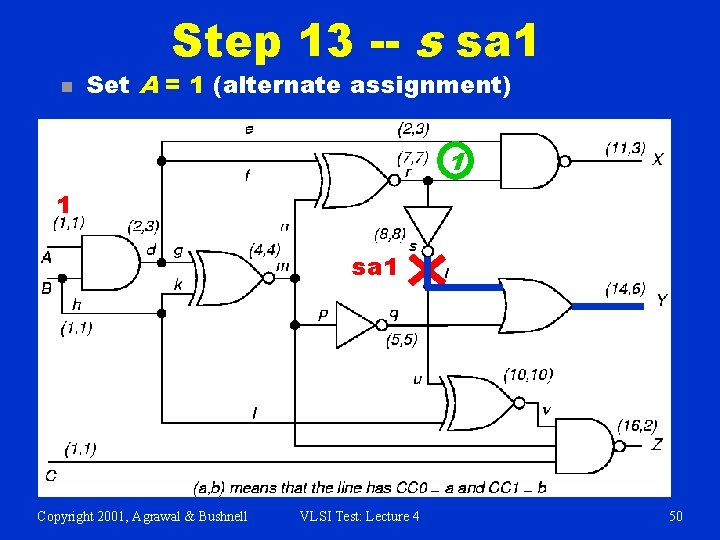

Step 13 -- s sa 1 n Set A = 1 (alternate assignment) 1 1 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 50

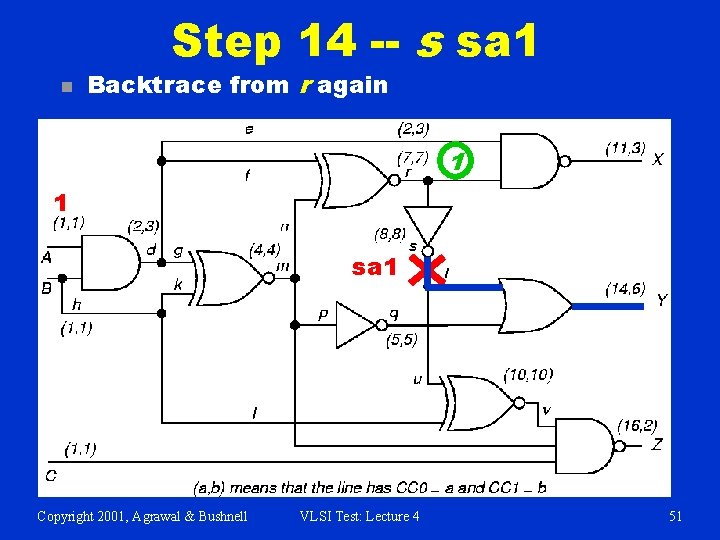

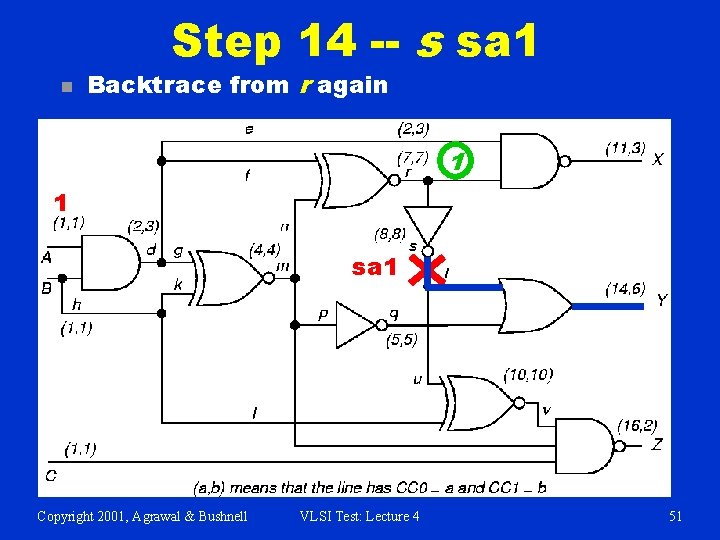

Step 14 -- s sa 1 n Backtrace from r again 1 1 sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 51

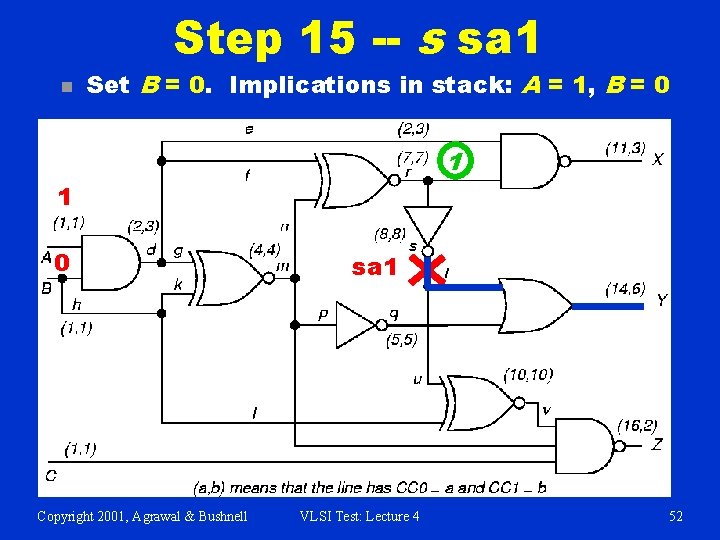

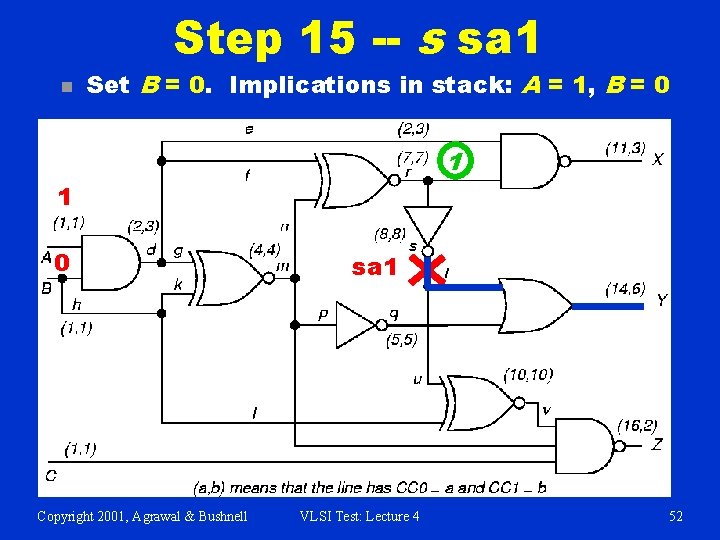

Step 15 -- s sa 1 n Set B = 0. Implications in stack: A = 1, B = 0 1 1 0 Copyright 2001, Agrawal & Bushnell sa 1 VLSI Test: Lecture 4 52

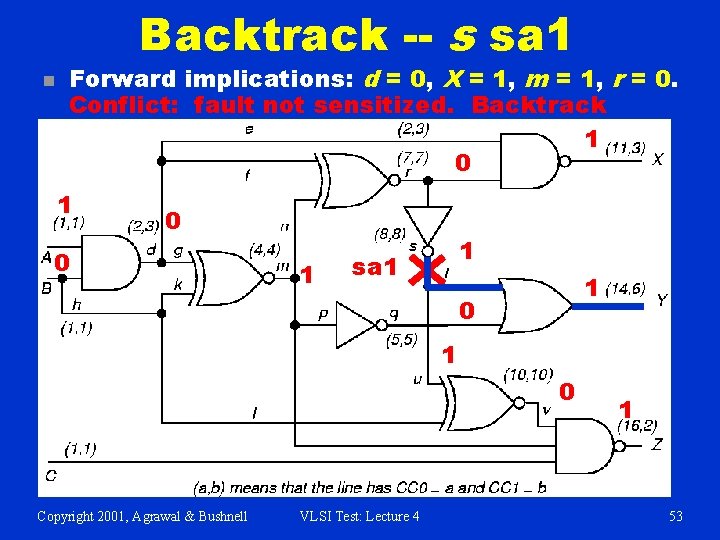

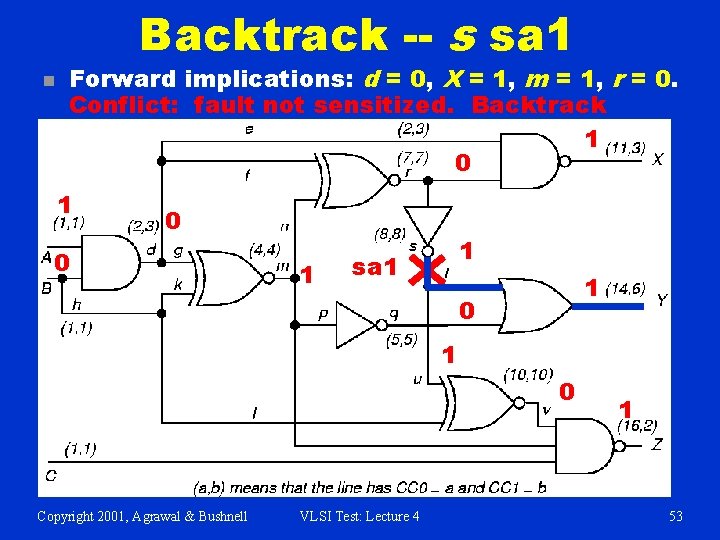

Backtrack -- s sa 1 n Forward implications: d = 0, X = 1, m = 1, r = 0. Conflict: fault not sensitized. Backtrack 1 0 0 1 1 sa 1 1 0 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 1 53

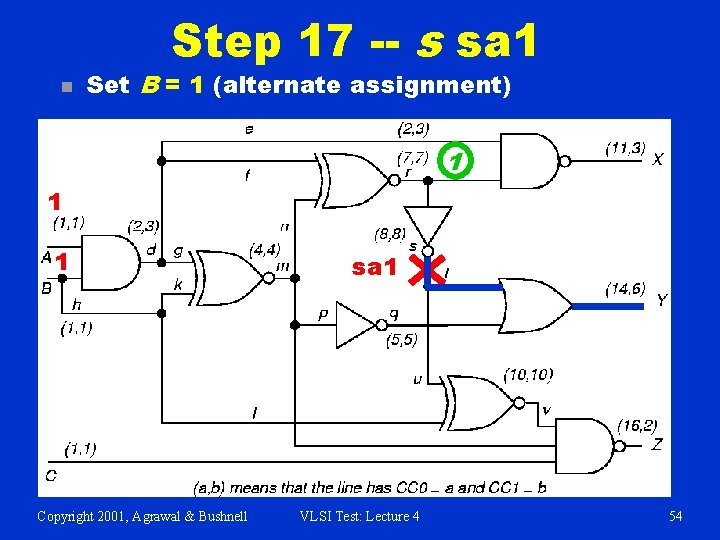

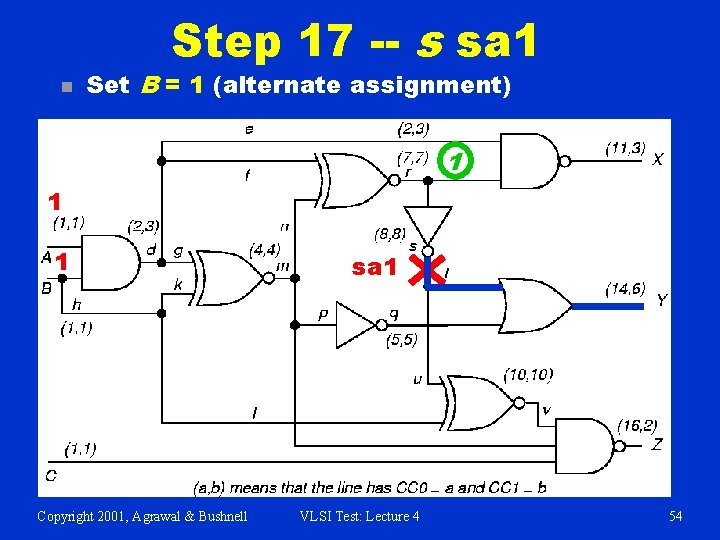

Step 17 -- s sa 1 n Set B = 1 (alternate assignment) 1 1 1 Copyright 2001, Agrawal & Bushnell sa 1 VLSI Test: Lecture 4 54

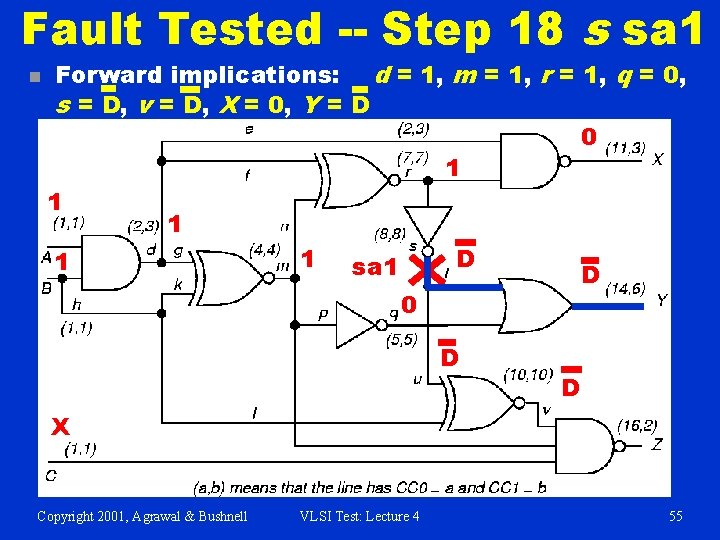

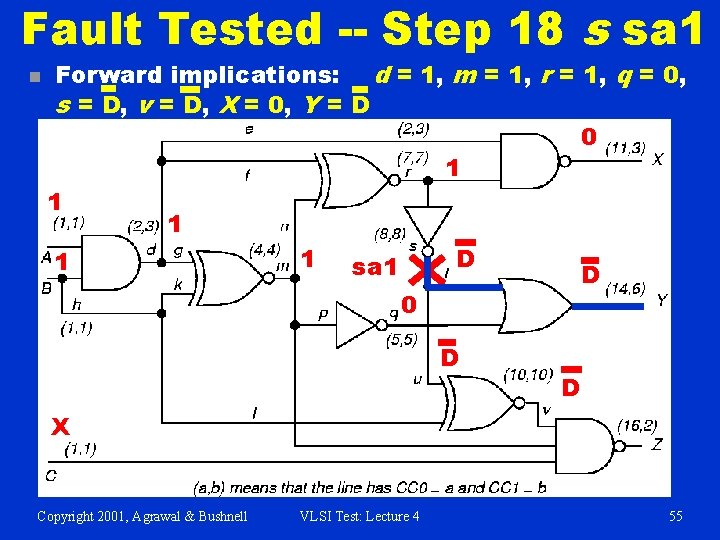

Fault Tested -- Step 18 s sa 1 n Forward implications: d = 1, m = 1, r = 1, q = 0, s = D, v = D, X = 0, Y = D 0 1 1 D 1 sa 1 D 0 D D X Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 55

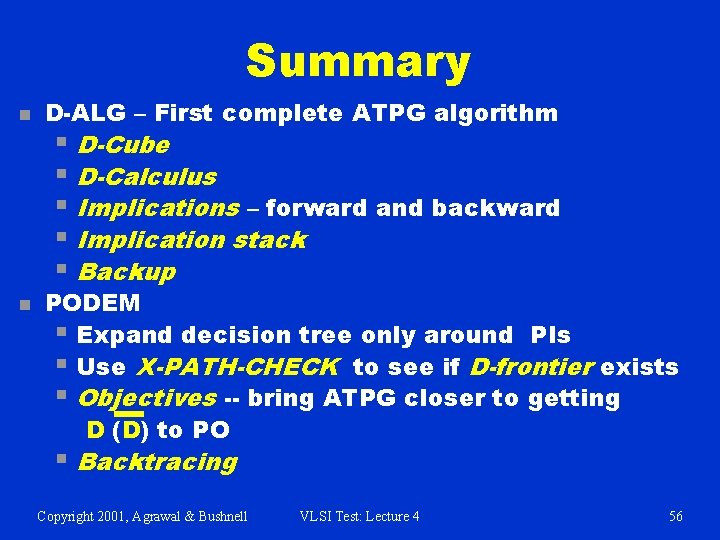

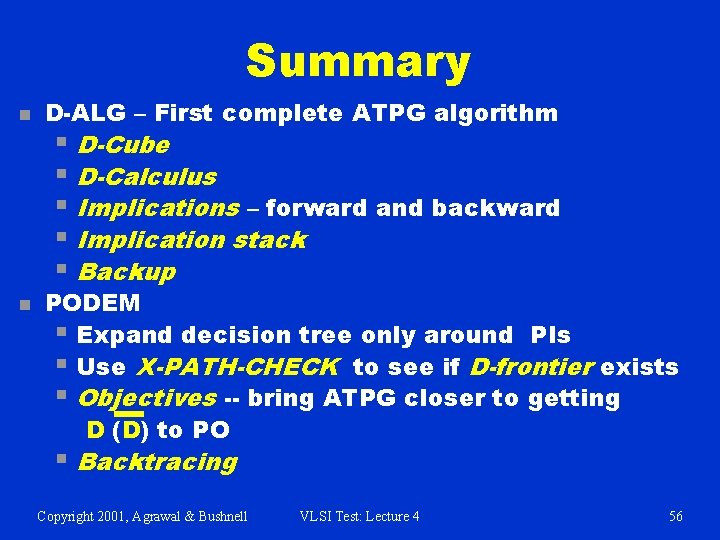

Summary n n D-ALG – First complete ATPG algorithm § D-Cube § D-Calculus § Implications – forward and backward § Implication stack § Backup PODEM § Expand decision tree only around PIs § Use X-PATH-CHECK to see if D-frontier exists § Objectives -- bring ATPG closer to getting D (D) to PO § Backtracing Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 4 56