Lecture 3 Instructions and Operations MIPS Architecture Chapter

- Slides: 25

Lecture 3: Instructions and Operations MIPS Architecture Chapter 3 Professor Mike Schulte Computer Architecture ECE 201

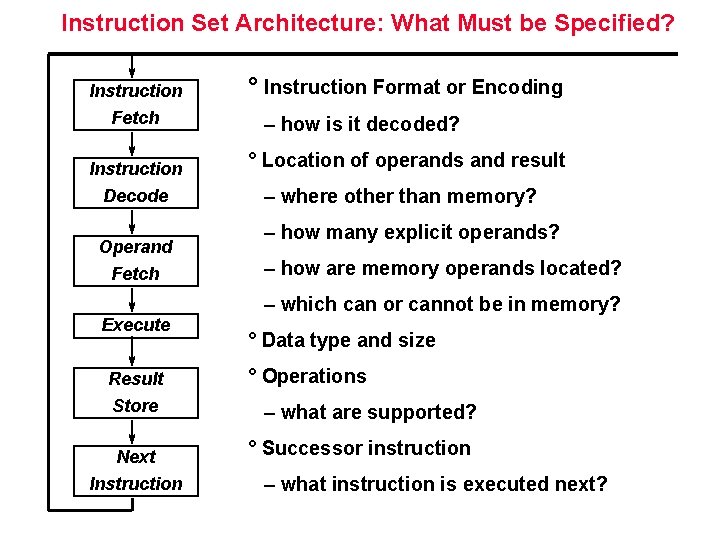

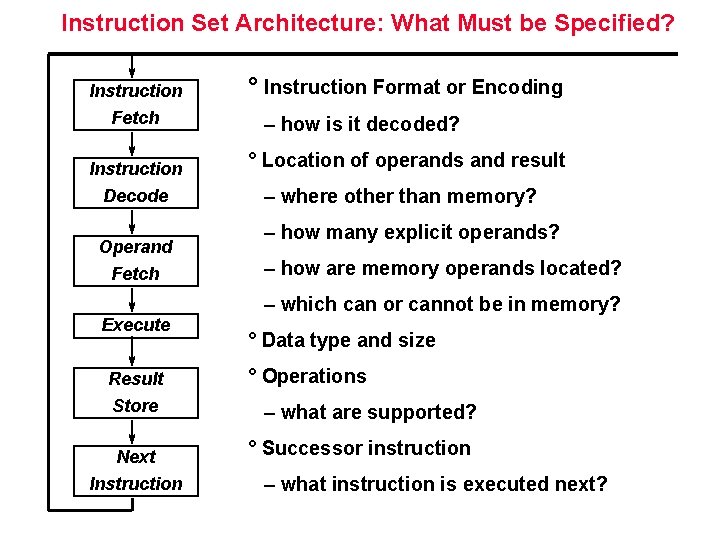

Instruction Set Architecture: What Must be Specified? Instruction Fetch Instruction Decode Operand Fetch Execute Result Store Next Instruction ° Instruction Format or Encoding – how is it decoded? ° Location of operands and result – where other than memory? – how many explicit operands? – how are memory operands located? – which can or cannot be in memory? ° Data type and size ° Operations – what are supported? ° Successor instruction – what instruction is executed next?

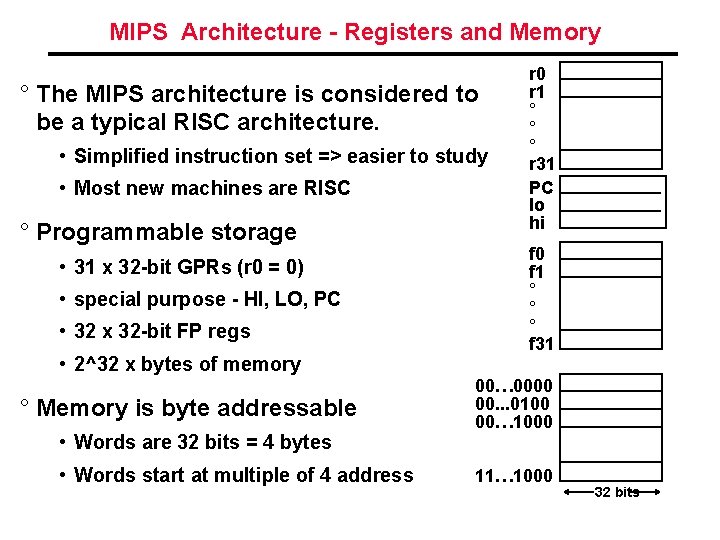

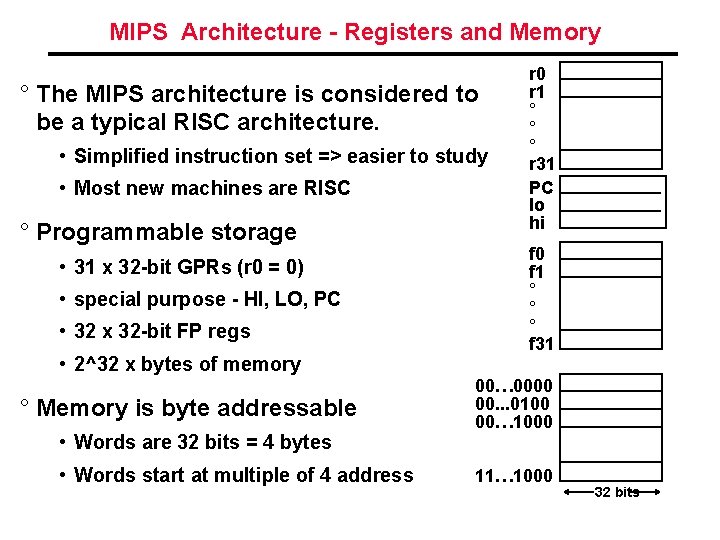

MIPS Architecture - Registers and Memory ° The MIPS architecture is considered to be a typical RISC architecture. • Simplified instruction set => easier to study • Most new machines are RISC ° Programmable storage • 31 x 32 -bit GPRs (r 0 = 0) • special purpose - HI, LO, PC • 32 x 32 -bit FP regs • 2^32 x bytes of memory ° Memory is byte addressable • Words are 32 bits = 4 bytes • Words start at multiple of 4 address r 0 r 1 ° ° ° r 31 PC lo hi f 0 f 1 ° ° ° f 31 00… 0000 00. . . 0100 00… 1000 11… 1000 32 bits

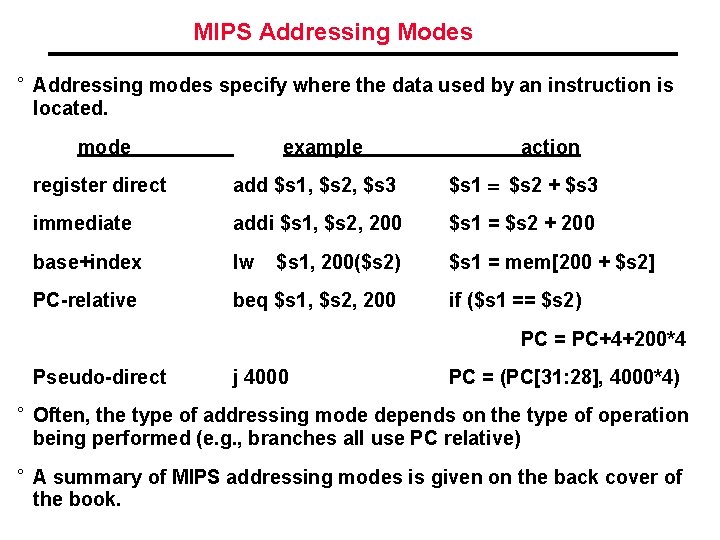

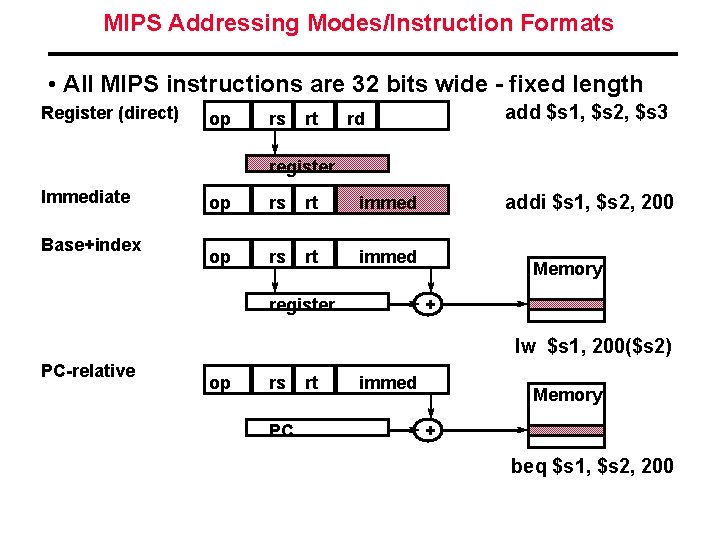

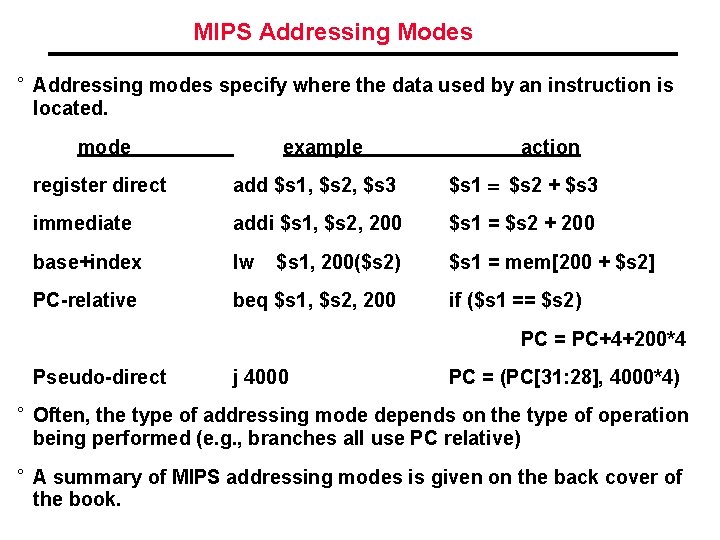

MIPS Addressing Modes ° Addressing modes specify where the data used by an instruction is located. mode example action register direct add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 immediate addi $s 1, $s 2, 200 $s 1 = $s 2 + 200 base+index lw $s 1 = mem[200 + $s 2] PC-relative beq $s 1, $s 2, 200 $s 1, 200($s 2) if ($s 1 == $s 2) PC = PC+4+200*4 Pseudo-direct j 4000 PC = (PC[31: 28], 4000*4) ° Often, the type of addressing mode depends on the type of operation being performed (e. g. , branches all use PC relative) ° A summary of MIPS addressing modes is given on the back cover of the book.

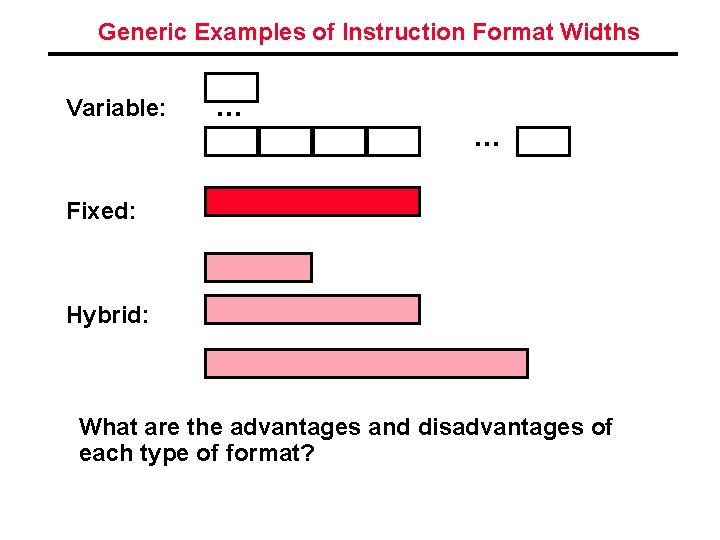

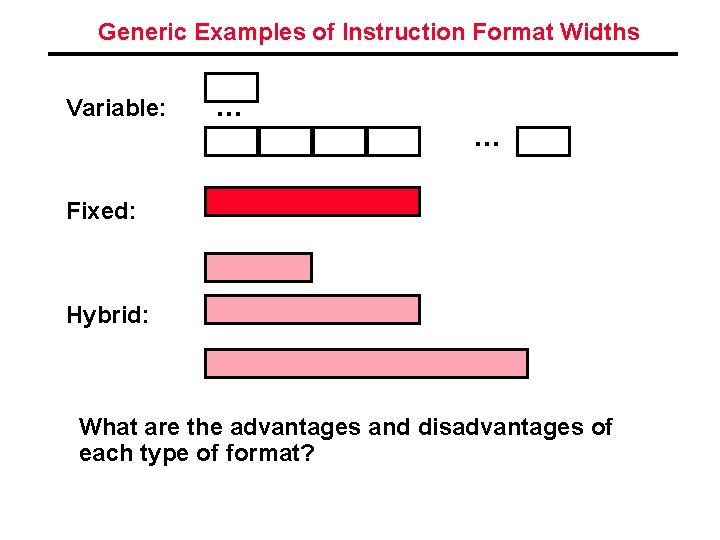

Generic Examples of Instruction Format Widths Variable: … … Fixed: Hybrid: What are the advantages and disadvantages of each type of format?

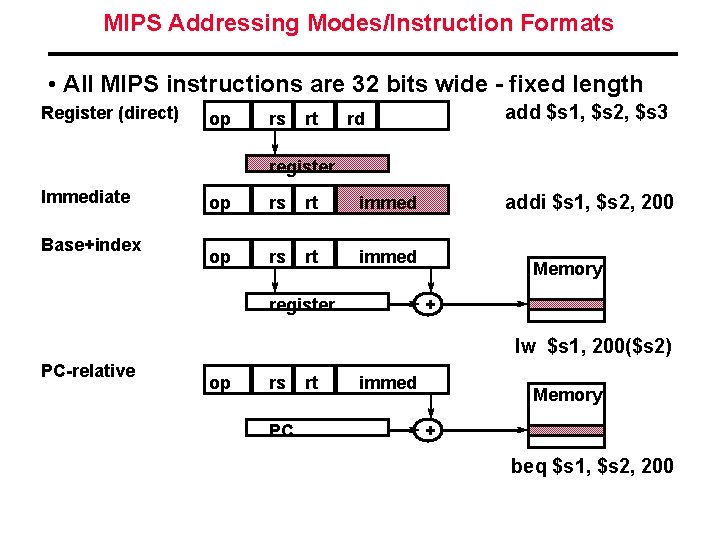

MIPS Addressing Modes/Instruction Formats • All MIPS instructions are 32 bits wide - fixed length Register (direct) op rs rt add $s 1, $s 2, $s 3 rd register Immediate Base+index op rs rt immed register addi $s 1, $s 2, 200 Memory + lw $s 1, 200($s 2) PC-relative op rs PC rt immed Memory + beq $s 1, $s 2, 200

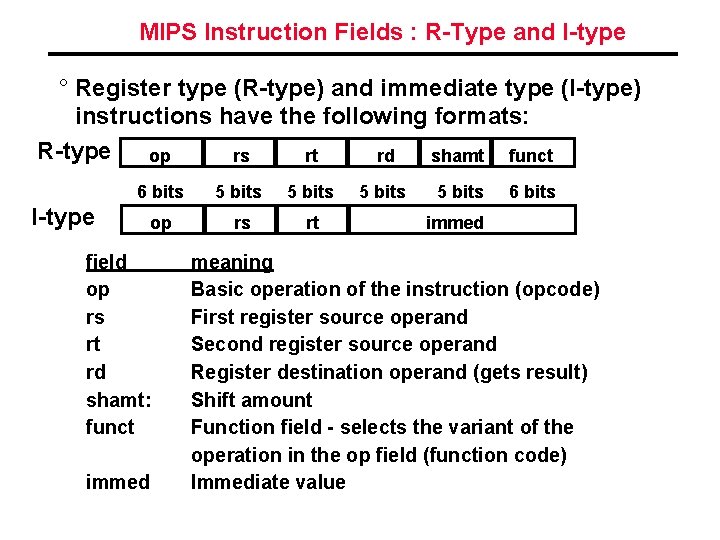

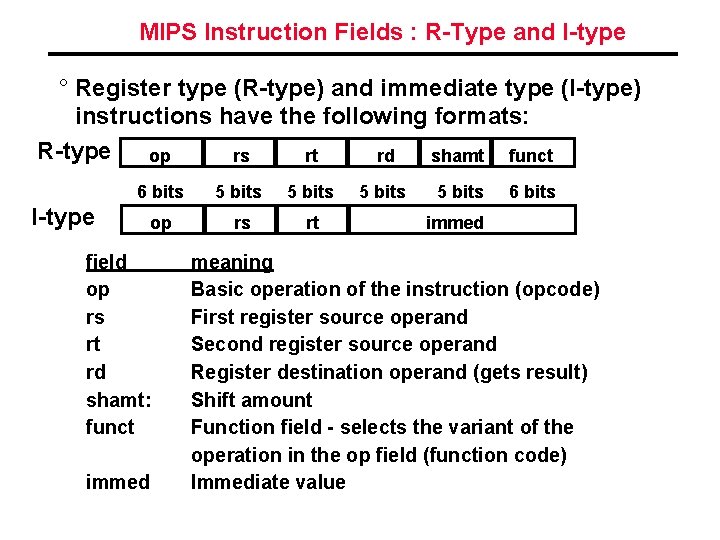

MIPS Instruction Fields : R-Type and I-type ° Register type (R-type) and immediate type (I-type) instructions have the following formats: R-type op rs rt rd shamt funct I-type 6 bits 5 bits op rs rt field op rs rt rd shamt: funct immed 5 bits 6 bits immed meaning Basic operation of the instruction (opcode) First register source operand Second register source operand Register destination operand (gets result) Shift amount Function field - selects the variant of the operation in the op field (function code) Immediate value

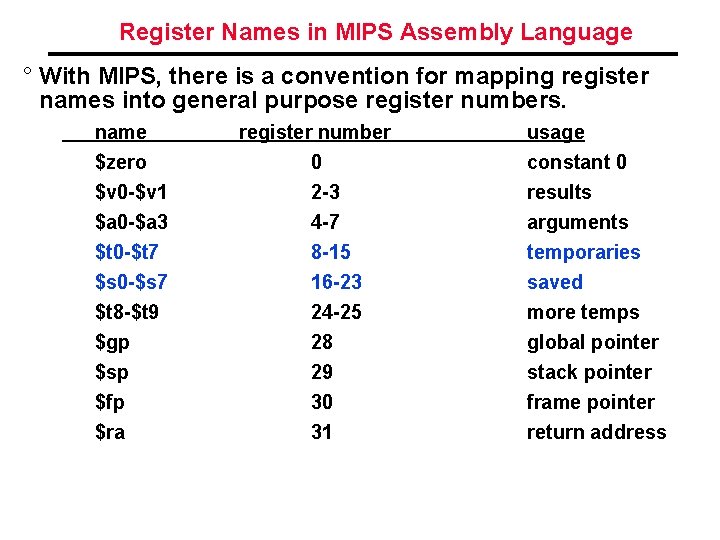

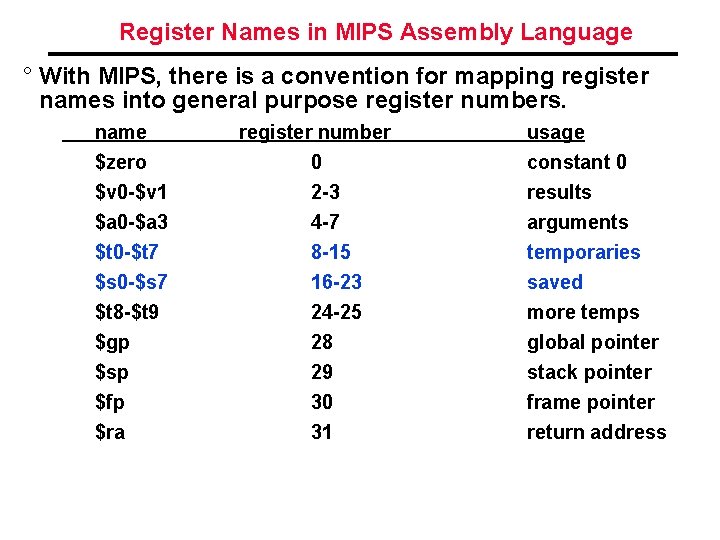

Register Names in MIPS Assembly Language ° With MIPS, there is a convention for mapping register names into general purpose register numbers. name $zero $v 0 -$v 1 register number 0 2 -3 usage constant 0 results $a 0 -$a 3 4 -7 arguments $t 0 -$t 7 8 -15 temporaries $s 0 -$s 7 16 -23 saved $t 8 -$t 9 24 -25 more temps $gp $sp $fp $ra 28 29 30 31 global pointer stack pointer frame pointer return address

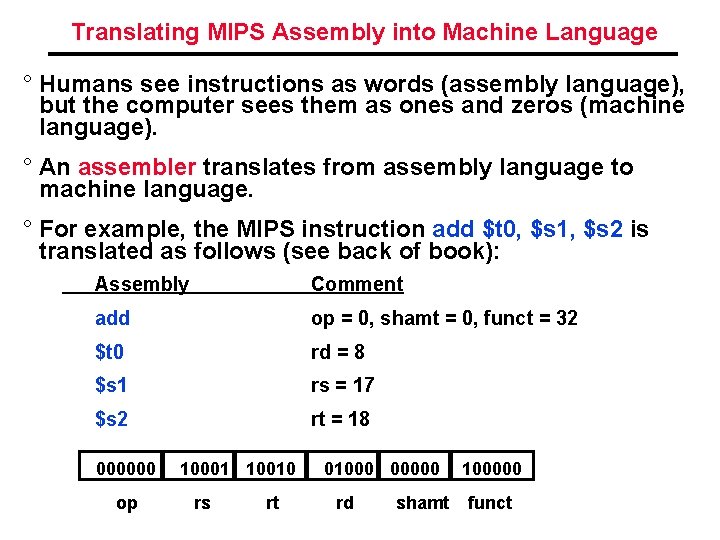

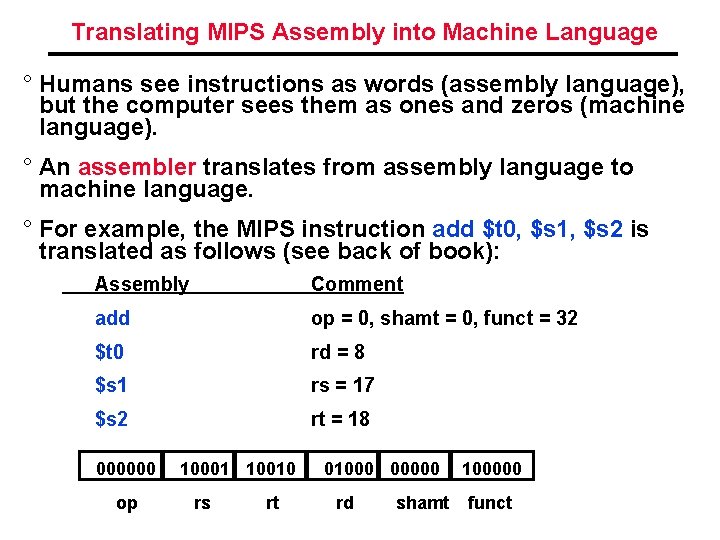

Translating MIPS Assembly into Machine Language ° Humans see instructions as words (assembly language), but the computer sees them as ones and zeros (machine language). ° An assembler translates from assembly language to machine language. ° For example, the MIPS instruction add $t 0, $s 1, $s 2 is translated as follows (see back of book): Assembly Comment add op = 0, shamt = 0, funct = 32 $t 0 rd = 8 $s 1 rs = 17 $s 2 rt = 18 000000 op 10001 10010 rs rt 01000 00000 rd shamt 100000 funct

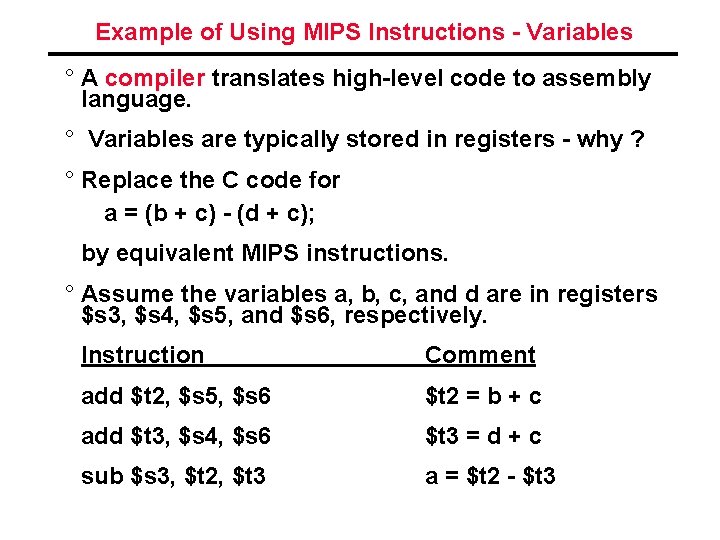

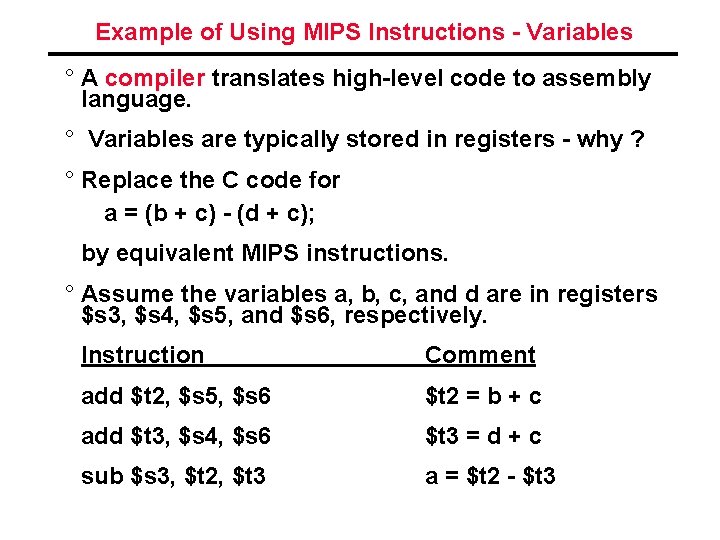

Example of Using MIPS Instructions - Variables ° A compiler translates high-level code to assembly language. ° Variables are typically stored in registers - why ? ° Replace the C code for a = (b + c) - (d + c); by equivalent MIPS instructions. ° Assume the variables a, b, c, and d are in registers $s 3, $s 4, $s 5, and $s 6, respectively. Instruction Comment add $t 2, $s 5, $s 6 $t 2 = b + c add $t 3, $s 4, $s 6 $t 3 = d + c sub $s 3, $t 2, $t 3 a = $t 2 - $t 3

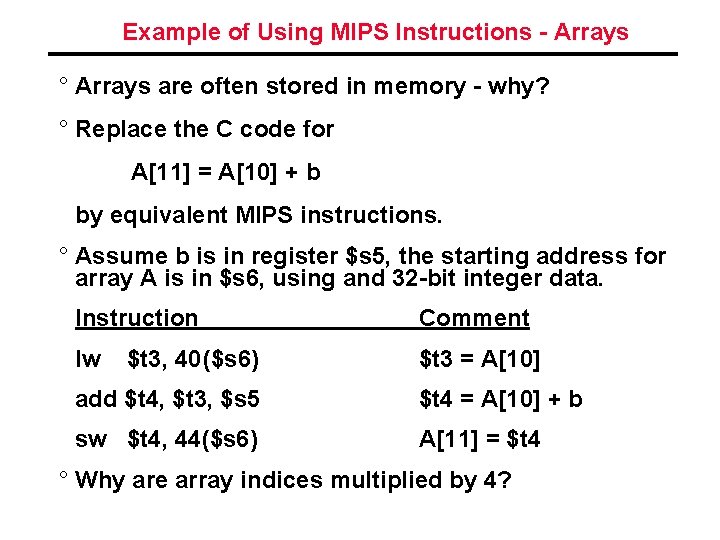

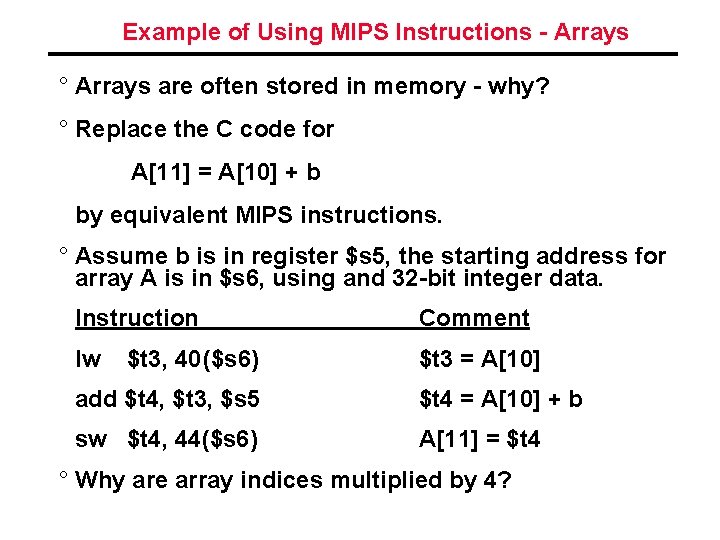

Example of Using MIPS Instructions - Arrays ° Arrays are often stored in memory - why? ° Replace the C code for A[11] = A[10] + b by equivalent MIPS instructions. ° Assume b is in register $s 5, the starting address for array A is in $s 6, using and 32 -bit integer data. Instruction Comment lw $t 3 = A[10] $t 3, 40($s 6) add $t 4, $t 3, $s 5 $t 4 = A[10] + b sw $t 4, 44($s 6) A[11] = $t 4 ° Why are array indices multiplied by 4?

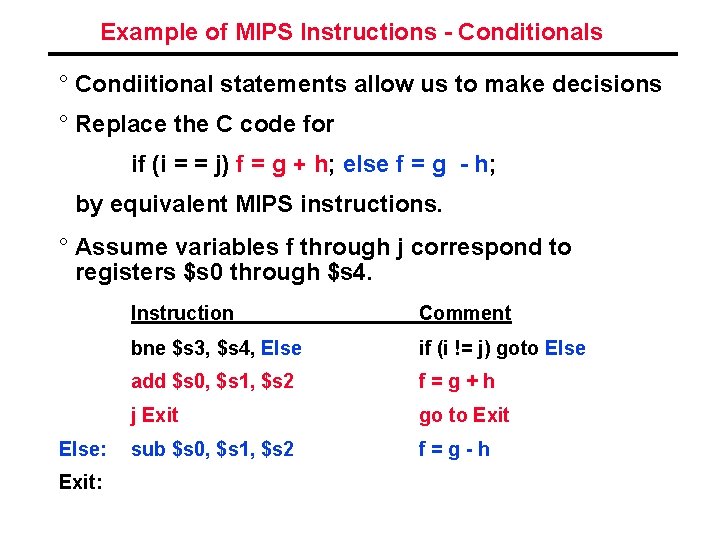

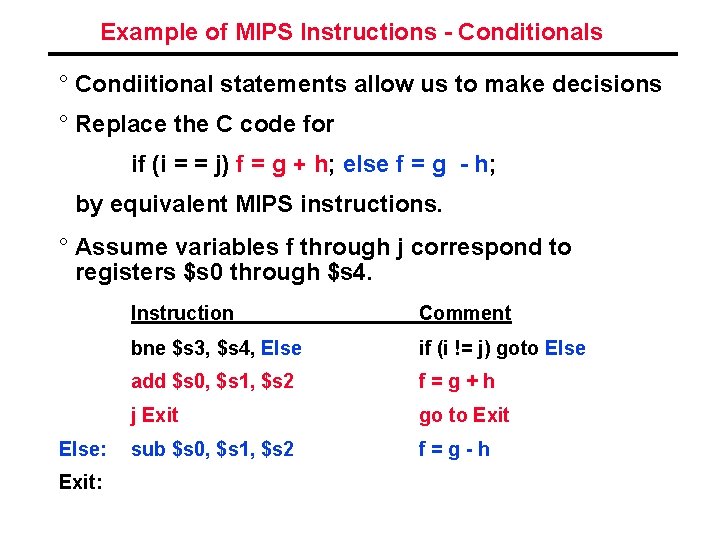

Example of MIPS Instructions - Conditionals ° Condiitional statements allow us to make decisions ° Replace the C code for if (i = = j) f = g + h; else f = g - h; by equivalent MIPS instructions. ° Assume variables f through j correspond to registers $s 0 through $s 4. Else: Exit: Instruction Comment bne $s 3, $s 4, Else if (i != j) goto Else add $s 0, $s 1, $s 2 f=g+h j Exit go to Exit sub $s 0, $s 1, $s 2 f=g-h

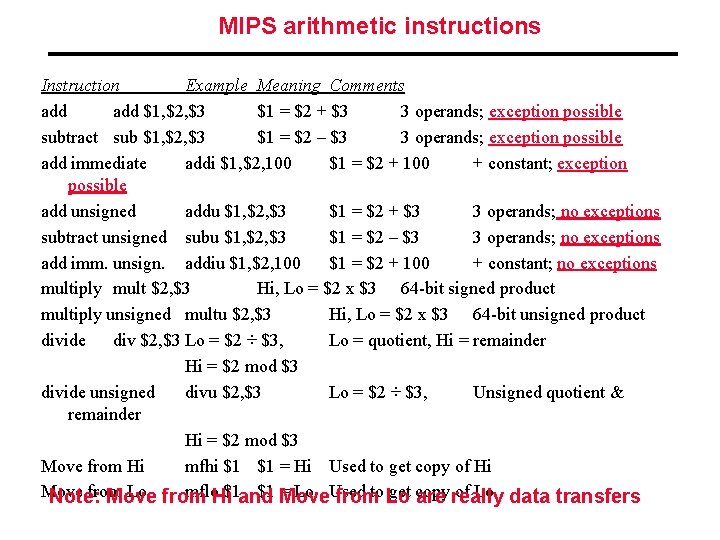

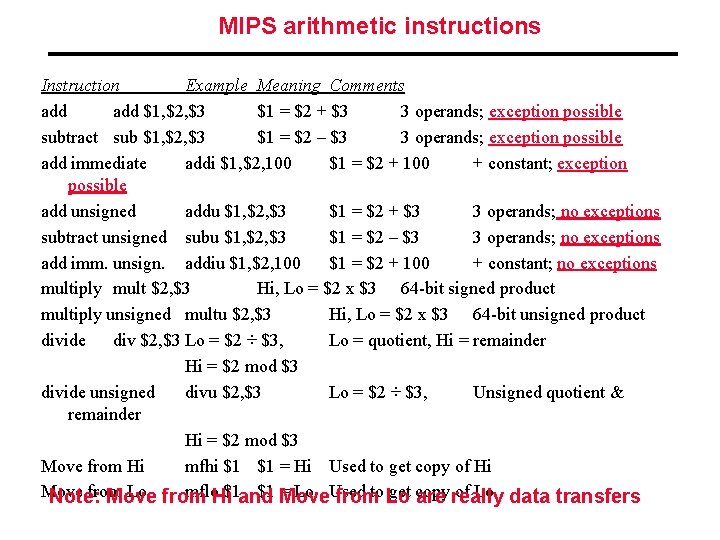

MIPS arithmetic instructions Instruction Example Meaning Comments add $1, $2, $3 $1 = $2 + $3 3 operands; exception possible subtract sub $1, $2, $3 $1 = $2 – $3 3 operands; exception possible add immediate addi $1, $2, 100 $1 = $2 + 100 + constant; exception possible add unsigned addu $1, $2, $3 $1 = $2 + $3 3 operands; no exceptions subtract unsigned subu $1, $2, $3 $1 = $2 – $3 3 operands; no exceptions add imm. unsign. addiu $1, $2, 100 $1 = $2 + 100 + constant; no exceptions multiply mult $2, $3 Hi, Lo = $2 x $3 64 -bit signed product multiply unsigned multu $2, $3 Hi, Lo = $2 x $3 64 -bit unsigned product divide div $2, $3 Lo = $2 ÷ $3, Lo = quotient, Hi = remainder Hi = $2 mod $3 divide unsigned divu $2, $3 Lo = $2 ÷ $3, Unsigned quotient & remainder Hi = $2 mod $3 Move from Hi mfhi $1 $1 = Hi Used to get copy of Hi Move from Lo from mflo. Hi$1 and $1 Move = Lo Used get copy of Lo data transfers Note: Move fromto Lo are really

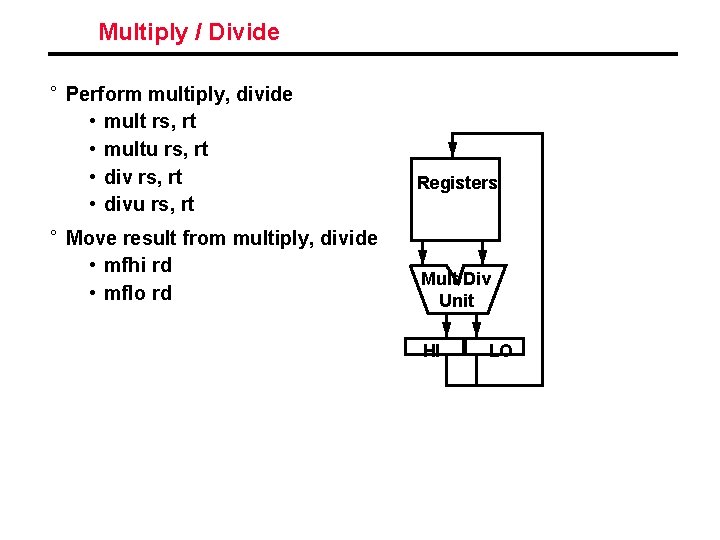

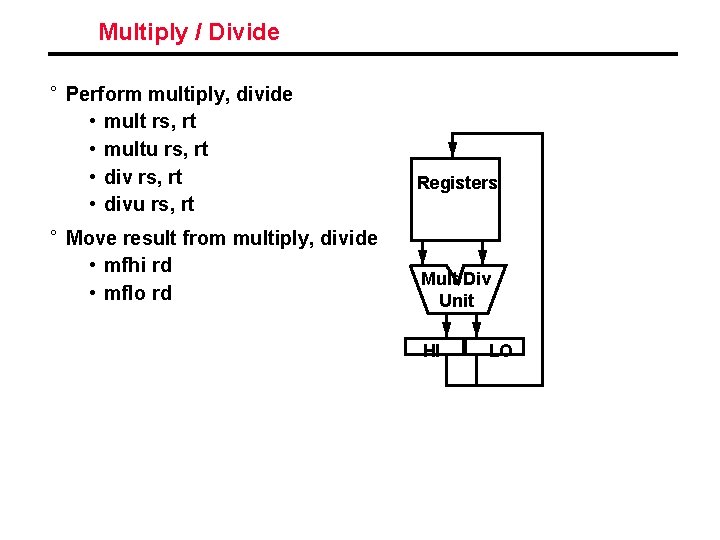

Multiply / Divide ° Perform multiply, divide • mult rs, rt • multu rs, rt • divu rs, rt ° Move result from multiply, divide • mfhi rd • mflo rd Registers Mult/Div Unit HI LO

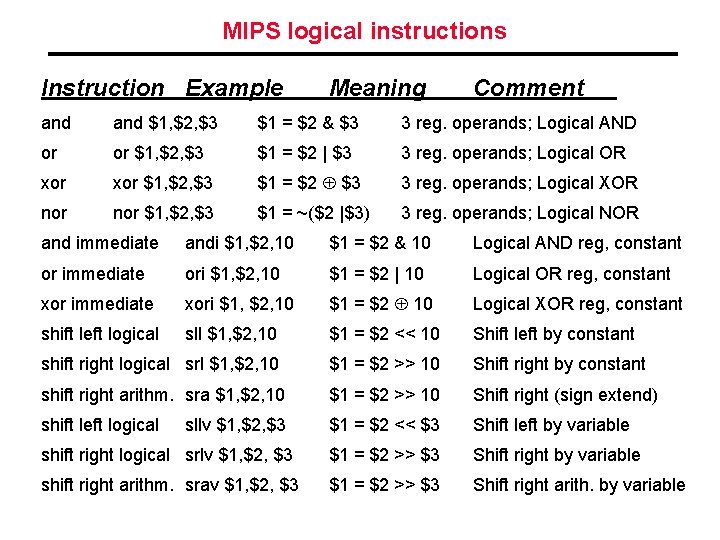

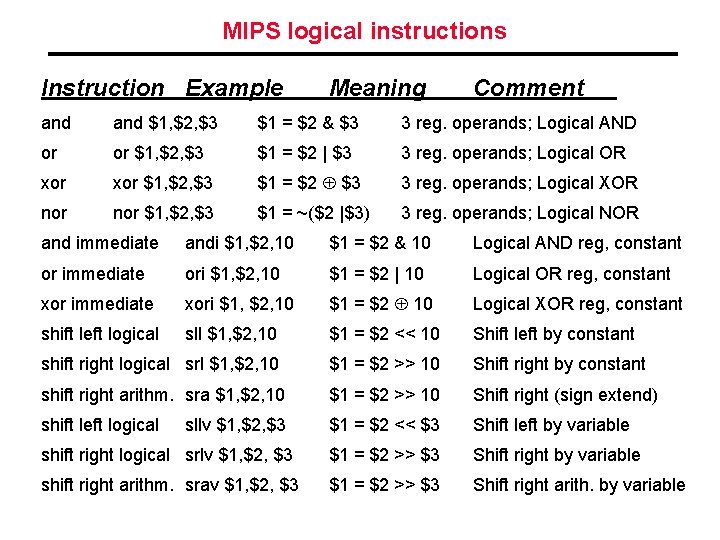

MIPS logical instructions Instruction Example Meaning Comment and $1, $2, $3 $1 = $2 & $3 3 reg. operands; Logical AND or or $1, $2, $3 $1 = $2 | $3 3 reg. operands; Logical OR xor $1, $2, $3 $1 = $2 Å $3 3 reg. operands; Logical XOR nor $1, $2, $3 $1 = ~($2 |$3) 3 reg. operands; Logical NOR and immediate andi $1, $2, 10 $1 = $2 & 10 Logical AND reg, constant or immediate ori $1, $2, 10 $1 = $2 | 10 Logical OR reg, constant xor immediate xori $1, $2, 10 $1 = $2 Å 10 Logical XOR reg, constant shift left logical sll $1, $2, 10 $1 = $2 << 10 Shift left by constant shift right logical srl $1, $2, 10 $1 = $2 >> 10 Shift right by constant shift right arithm. sra $1, $2, 10 $1 = $2 >> 10 Shift right (sign extend) shift left logical $1 = $2 << $3 Shift left by variable shift right logical srlv $1, $2, $3 $1 = $2 >> $3 Shift right by variable shift right arithm. srav $1, $2, $3 $1 = $2 >> $3 Shift right arith. by variable sllv $1, $2, $3

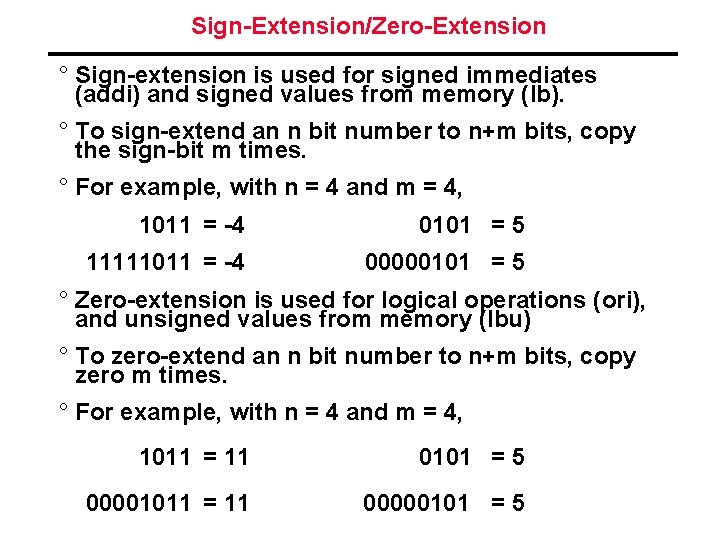

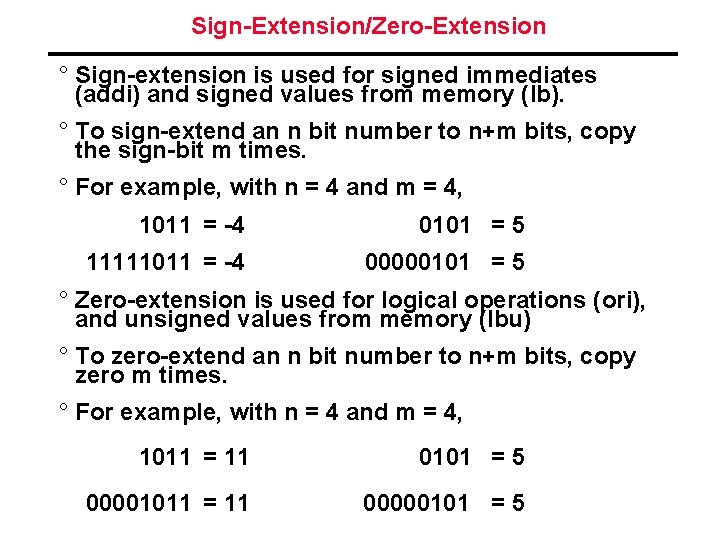

Sign-Extension/Zero-Extension ° Sign-extension is used for signed immediates (addi) and signed values from memory (lb). ° To sign-extend an n bit number to n+m bits, copy the sign-bit m times. ° For example, with n = 4 and m = 4, 1011 = -4 0101 = 5 11111011 = -4 00000101 = 5 ° Zero-extension is used for logical operations (ori), and unsigned values from memory (lbu) ° To zero-extend an n bit number to n+m bits, copy zero m times. ° For example, with n = 4 and m = 4, 1011 = 11 0101 = 5 00001011 = 11 00000101 = 5

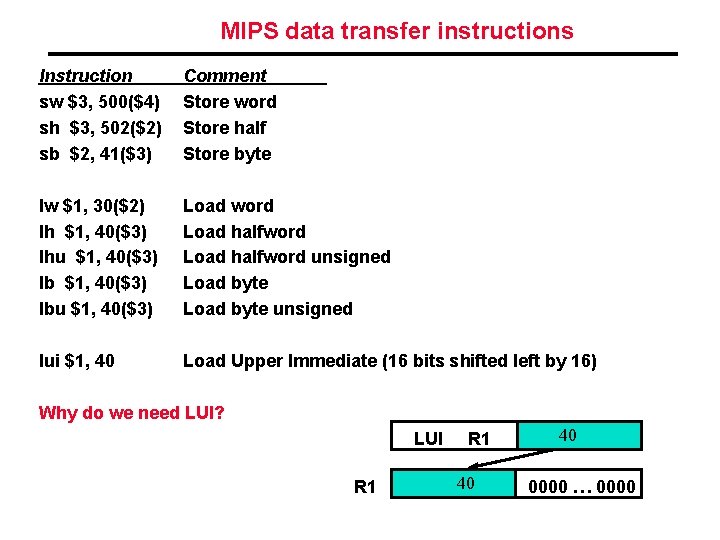

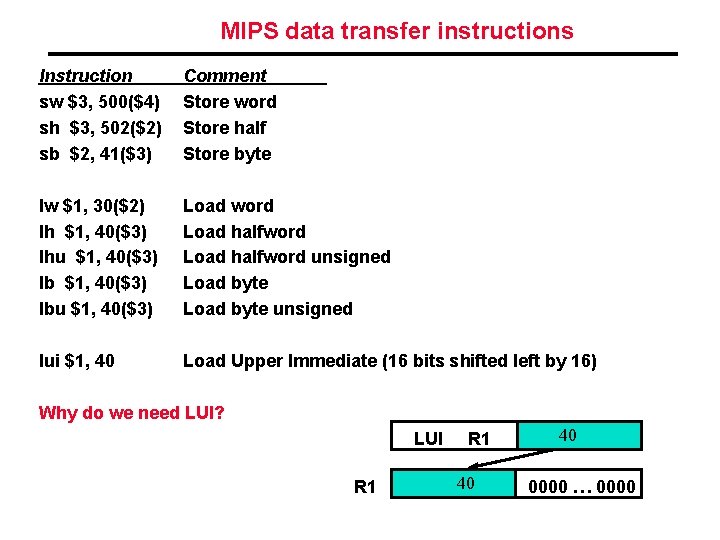

MIPS data transfer instructions Instruction sw $3, 500($4) sh $3, 502($2) sb $2, 41($3) Comment Store word Store half Store byte lw $1, 30($2) lh $1, 40($3) lhu $1, 40($3) lbu $1, 40($3) Load word Load halfword unsigned Load byte unsigned lui $1, 40 Load Upper Immediate (16 bits shifted left by 16) Why do we need LUI? LUI R 1 40 40 0000 … 0000

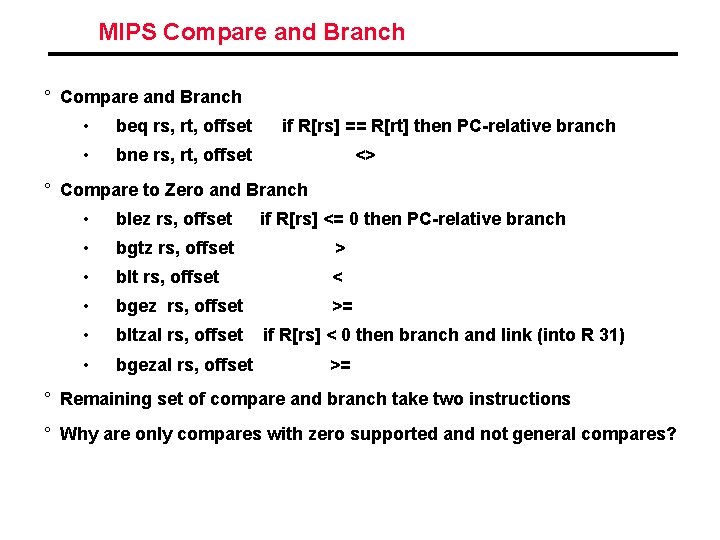

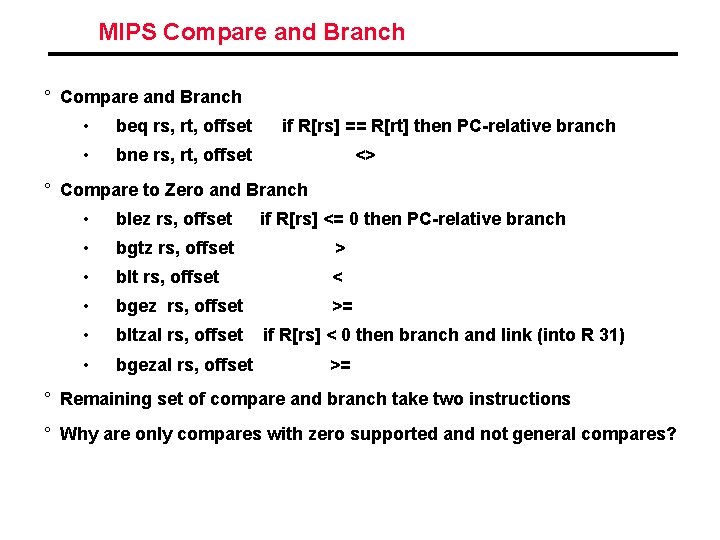

MIPS Compare and Branch ° Compare and Branch • beq rs, rt, offset • bne rs, rt, offset if R[rs] == R[rt] then PC-relative branch <> ° Compare to Zero and Branch • blez rs, offset • bgtz rs, offset > • blt rs, offset < • bgez rs, offset >= • bltzal rs, offset • bgezal rs, offset if R[rs] <= 0 then PC-relative branch if R[rs] < 0 then branch and link (into R 31) >= ° Remaining set of compare and branch take two instructions ° Why are only compares with zero supported and not general compares?

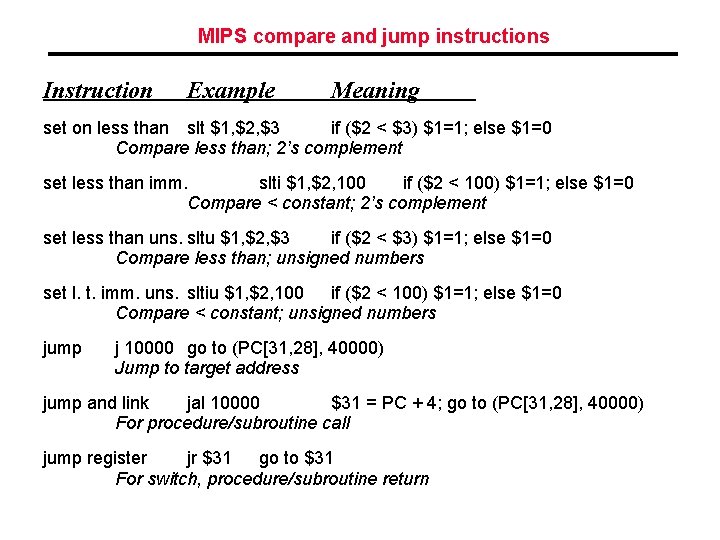

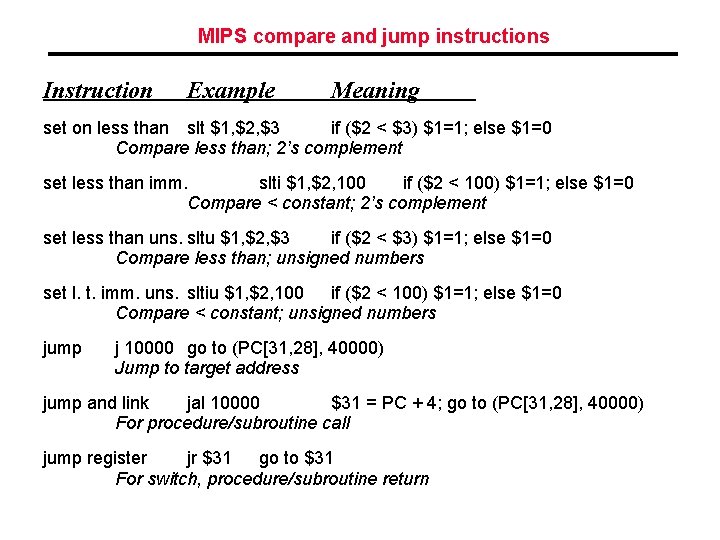

MIPS compare and jump instructions Instruction Example Meaning set on less than slt $1, $2, $3 if ($2 < $3) $1=1; else $1=0 Compare less than; 2’s complement set less than imm. slti $1, $2, 100 if ($2 < 100) $1=1; else $1=0 Compare < constant; 2’s complement set less than uns. sltu $1, $2, $3 if ($2 < $3) $1=1; else $1=0 Compare less than; unsigned numbers set l. t. imm. uns. sltiu $1, $2, 100 if ($2 < 100) $1=1; else $1=0 Compare < constant; unsigned numbers jump j 10000 go to (PC[31, 28], 40000) Jump to target address jump and link jal 10000 $31 = PC + 4; go to (PC[31, 28], 40000) For procedure/subroutine call jump register jr $31 go to $31 For switch, procedure/subroutine return

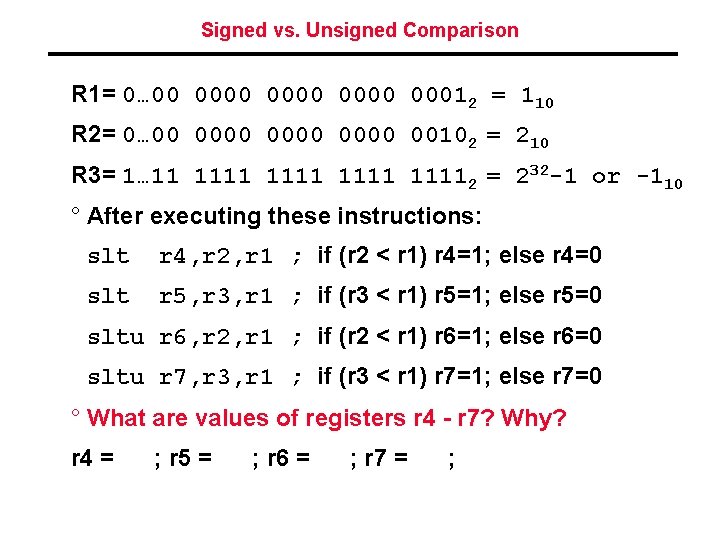

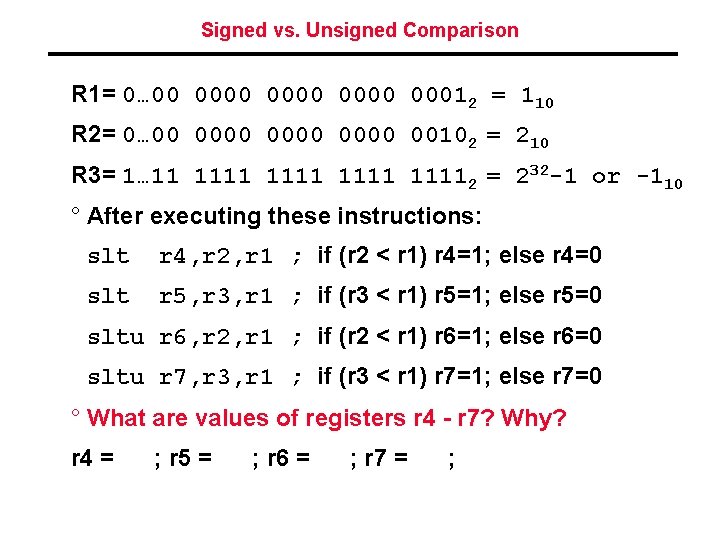

Signed vs. Unsigned Comparison R 1= 0… 00 0000 00012 = 110 R 2= 0… 00 0000 00102 = 210 R 3= 1… 11 11112 = 232 -1 or -110 ° After executing these instructions: slt r 4, r 2, r 1 ; if (r 2 < r 1) r 4=1; else r 4=0 slt r 5, r 3, r 1 ; if (r 3 < r 1) r 5=1; else r 5=0 sltu r 6, r 2, r 1 ; if (r 2 < r 1) r 6=1; else r 6=0 sltu r 7, r 3, r 1 ; if (r 3 < r 1) r 7=1; else r 7=0 ° What are values of registers r 4 - r 7? Why? r 4 = ; r 5 = ; r 6 = ; r 7 = ;

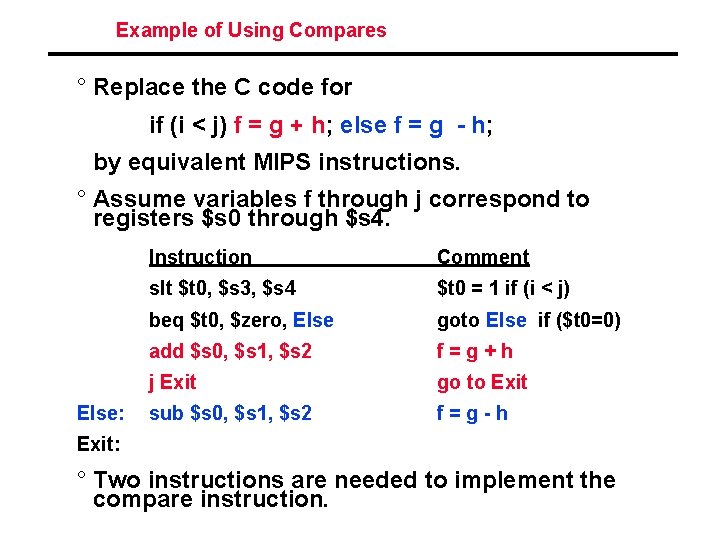

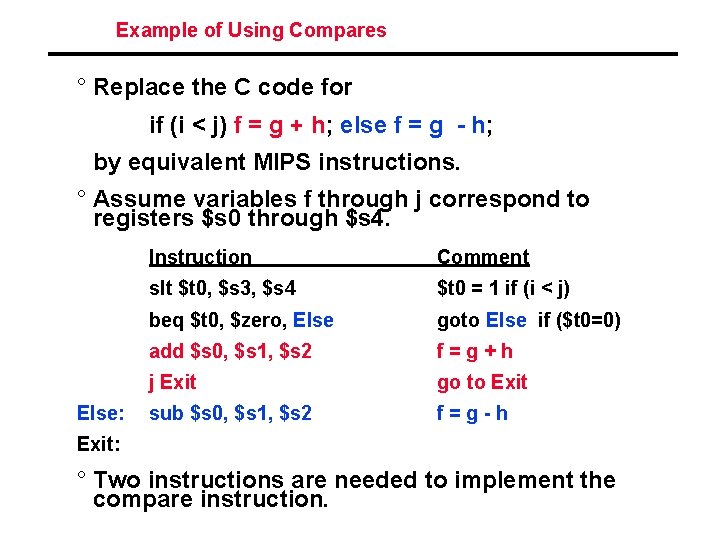

Example of Using Compares ° Replace the C code for if (i < j) f = g + h; else f = g - h; by equivalent MIPS instructions. ° Assume variables f through j correspond to registers $s 0 through $s 4. Else: Instruction Comment slt $t 0, $s 3, $s 4 $t 0 = 1 if (i < j) beq $t 0, $zero, Else goto Else if ($t 0=0) add $s 0, $s 1, $s 2 f=g+h j Exit go to Exit sub $s 0, $s 1, $s 2 f=g-h Exit: ° Two instructions are needed to implement the compare instruction.

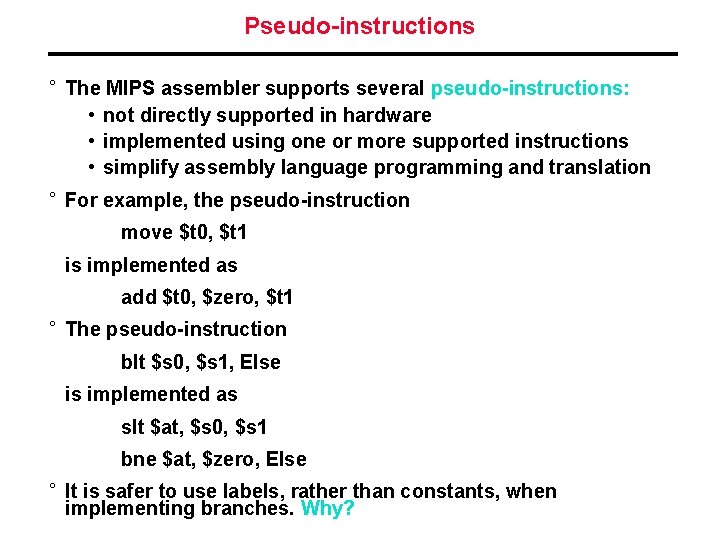

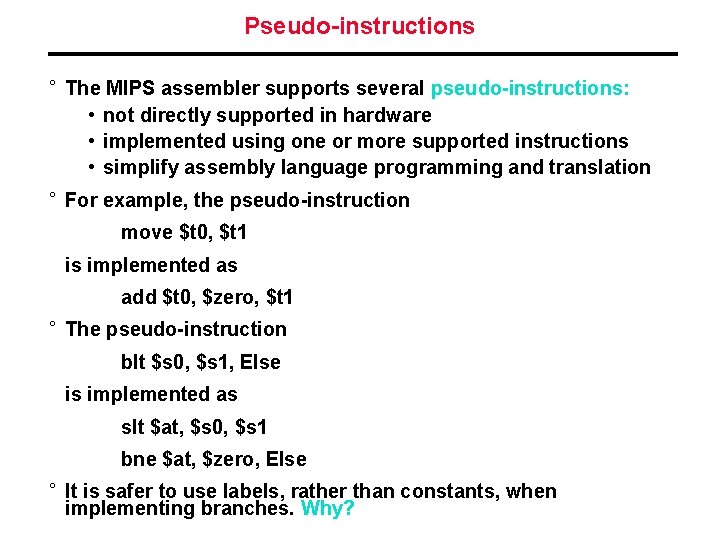

Pseudo-instructions ° The MIPS assembler supports several pseudo-instructions: • not directly supported in hardware • implemented using one or more supported instructions • simplify assembly language programming and translation ° For example, the pseudo-instruction move $t 0, $t 1 is implemented as add $t 0, $zero, $t 1 ° The pseudo-instruction blt $s 0, $s 1, Else is implemented as slt $at, $s 0, $s 1 bne $at, $zero, Else ° It is safer to use labels, rather than constants, when implementing branches. Why?

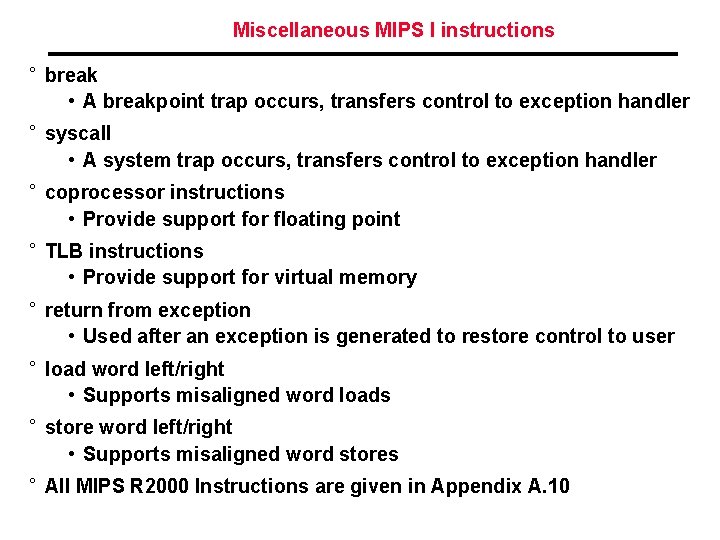

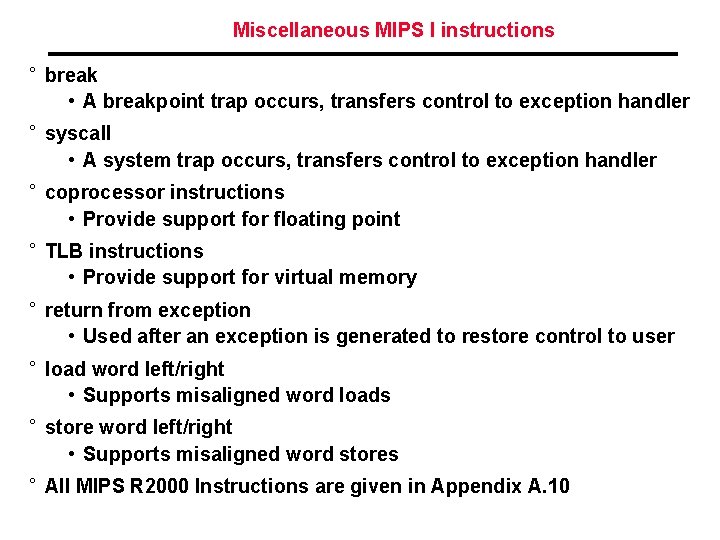

Miscellaneous MIPS I instructions ° break • A breakpoint trap occurs, transfers control to exception handler ° syscall • A system trap occurs, transfers control to exception handler ° coprocessor instructions • Provide support for floating point ° TLB instructions • Provide support for virtual memory ° return from exception • Used after an exception is generated to restore control to user ° load word left/right • Supports misaligned word loads ° store word left/right • Supports misaligned word stores ° All MIPS R 2000 Instructions are given in Appendix A. 10

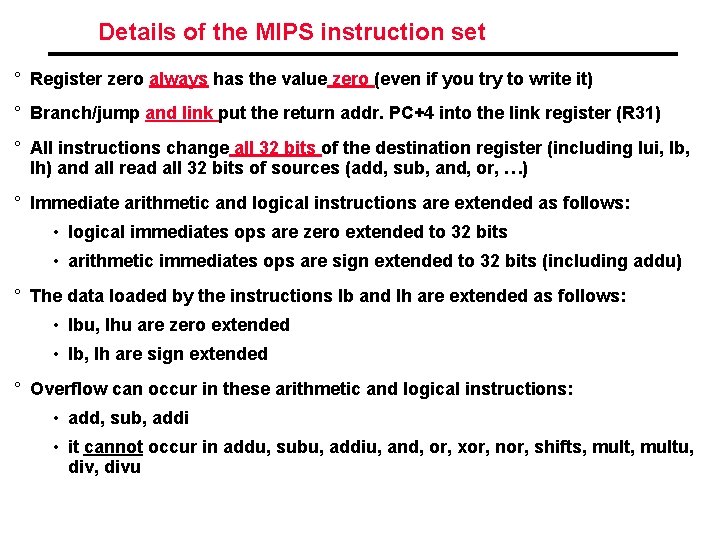

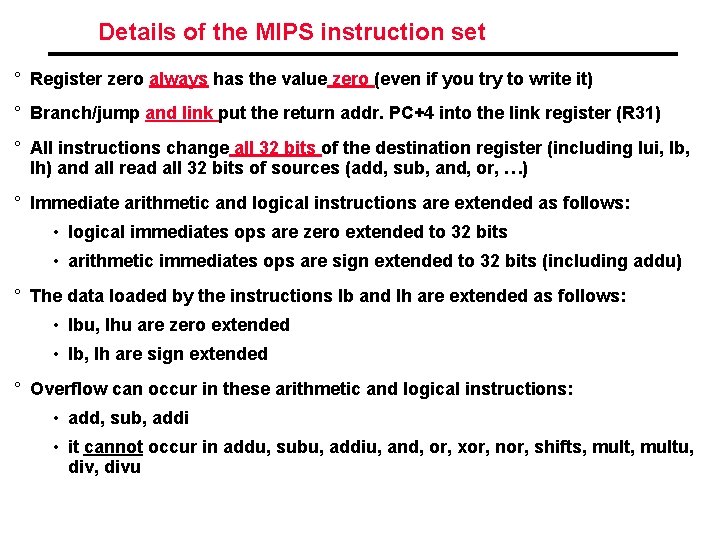

Details of the MIPS instruction set ° Register zero always has the value zero (even if you try to write it) ° Branch/jump and link put the return addr. PC+4 into the link register (R 31) ° All instructions change all 32 bits of the destination register (including lui, lb, lh) and all read all 32 bits of sources (add, sub, and, or, …) ° Immediate arithmetic and logical instructions are extended as follows: • logical immediates ops are zero extended to 32 bits • arithmetic immediates ops are sign extended to 32 bits (including addu) ° The data loaded by the instructions lb and lh are extended as follows: • lbu, lhu are zero extended • lb, lh are sign extended ° Overflow can occur in these arithmetic and logical instructions: • add, sub, addi • it cannot occur in addu, subu, addiu, and, or, xor, nor, shifts, multu, divu

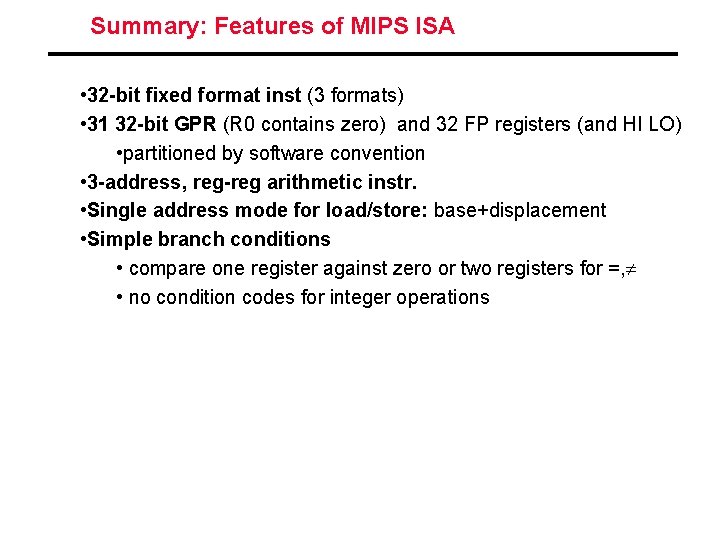

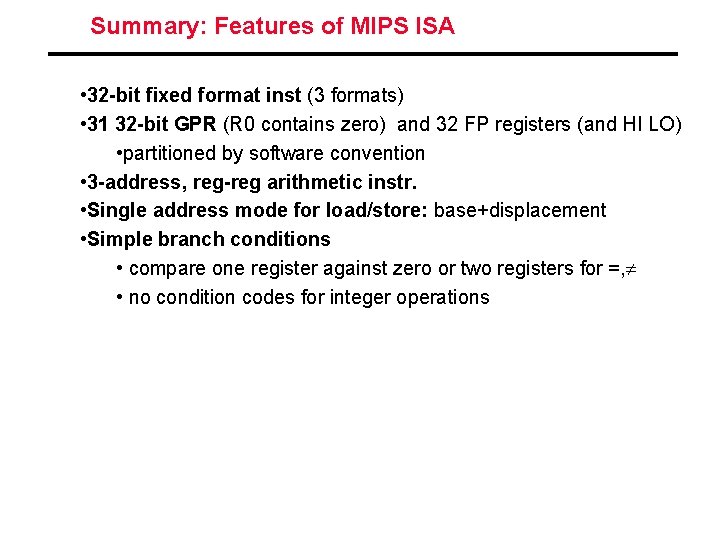

Summary: Features of MIPS ISA • 32 -bit fixed format inst (3 formats) • 31 32 -bit GPR (R 0 contains zero) and 32 FP registers (and HI LO) • partitioned by software convention • 3 -address, reg-reg arithmetic instr. • Single address mode for load/store: base+displacement • Simple branch conditions • compare one register against zero or two registers for =, • no condition codes for integer operations