Lecture 21 n State minimization via implication charts

![More complex minimization inputs here 00 10 00 S 0 [1] 01 10 S More complex minimization inputs here 00 10 00 S 0 [1] 01 10 S](https://slidetodoc.com/presentation_image_h2/b0fe8ef6c1d60e8b42162f14ed5787f1/image-15.jpg)

- Slides: 21

Lecture 21 n State minimization via implication charts 1

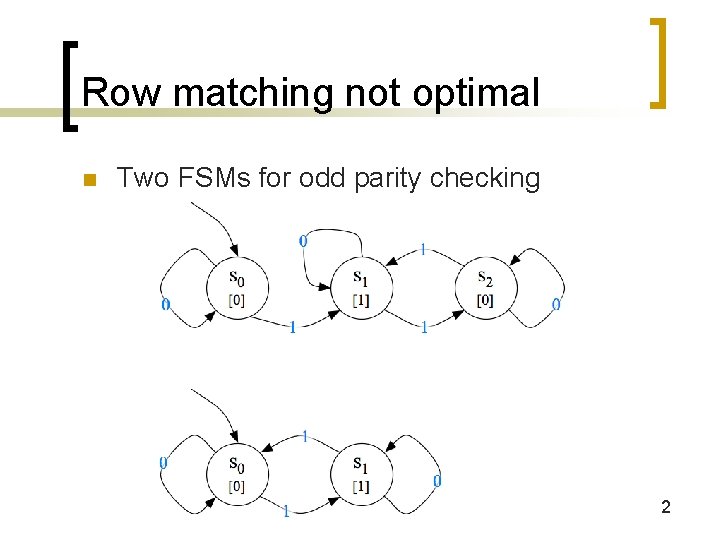

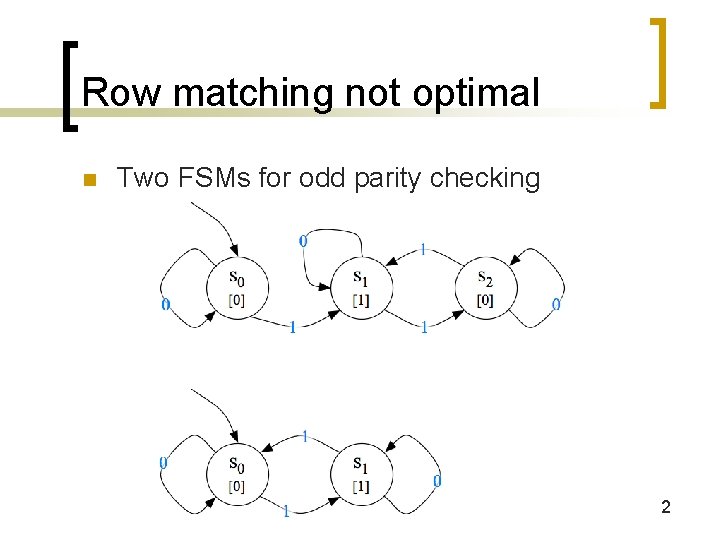

Row matching not optimal n Two FSMs for odd parity checking 2

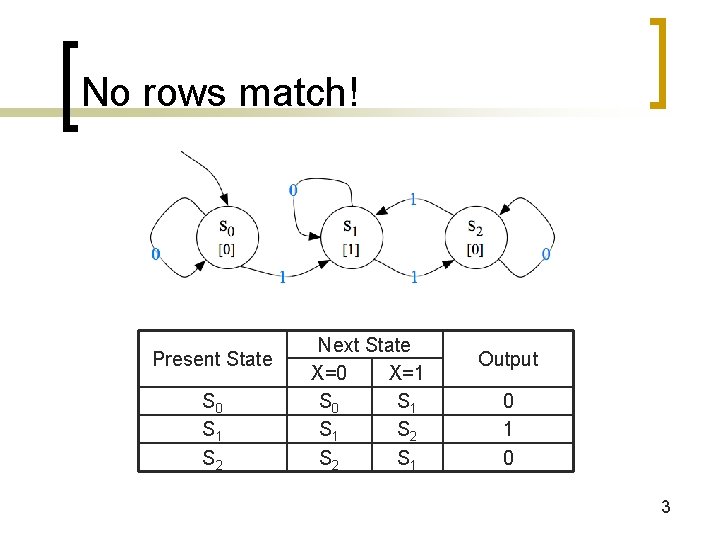

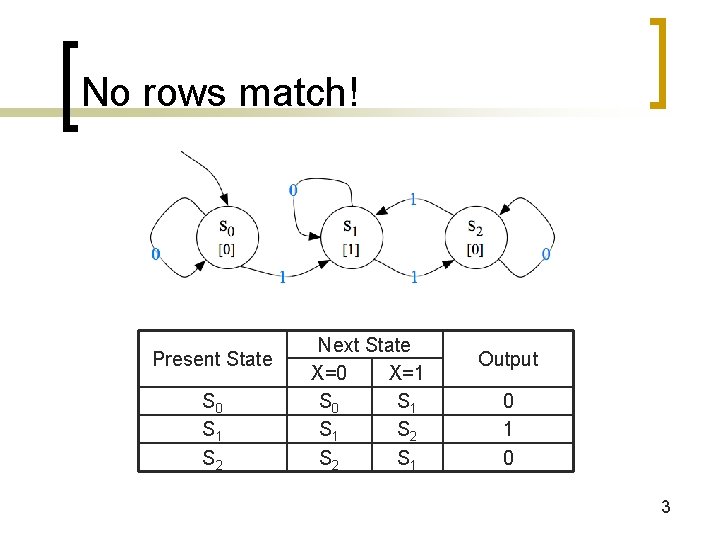

No rows match! Present State S 0 S 1 S 2 Next State X=0 X=1 S 0 S 1 S 2 S 1 Output 0 1 0 3

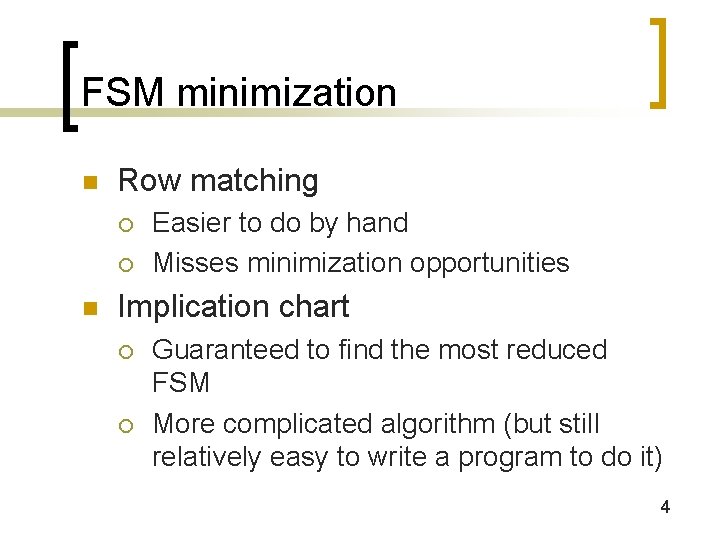

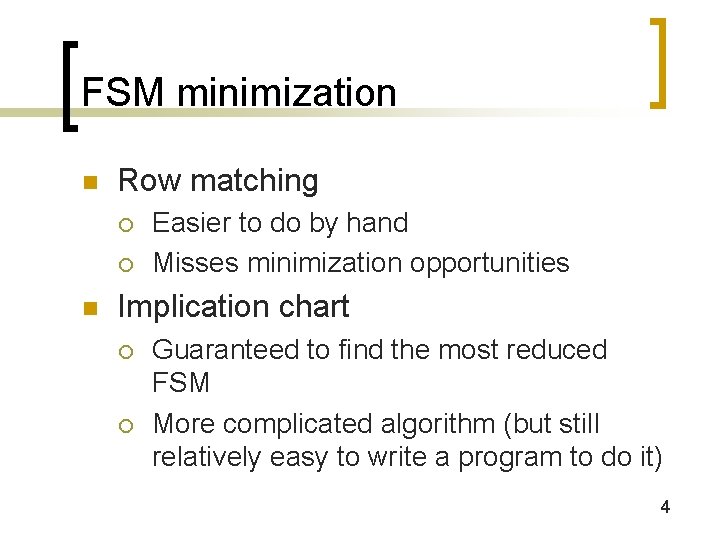

FSM minimization n Row matching ¡ ¡ n Easier to do by hand Misses minimization opportunities Implication chart ¡ ¡ Guaranteed to find the most reduced FSM More complicated algorithm (but still relatively easy to write a program to do it) 4

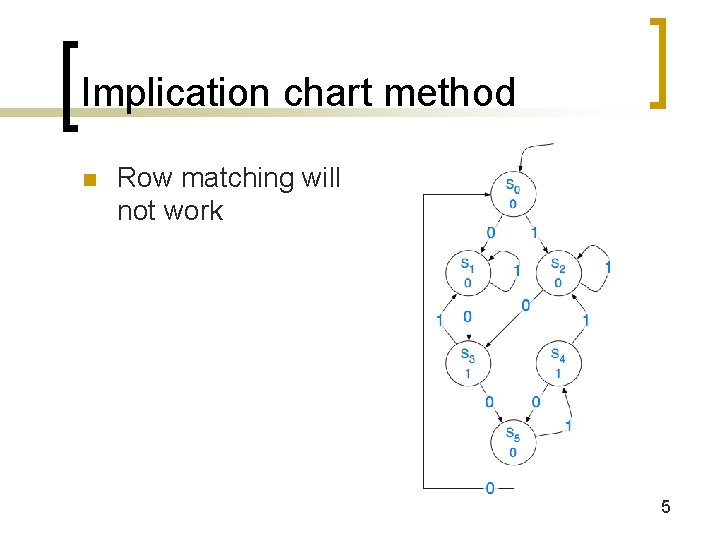

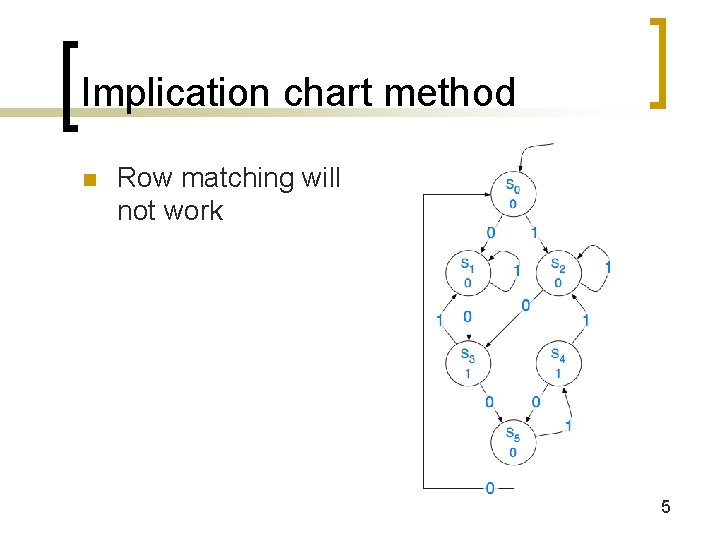

Implication chart method n Row matching will not work 5

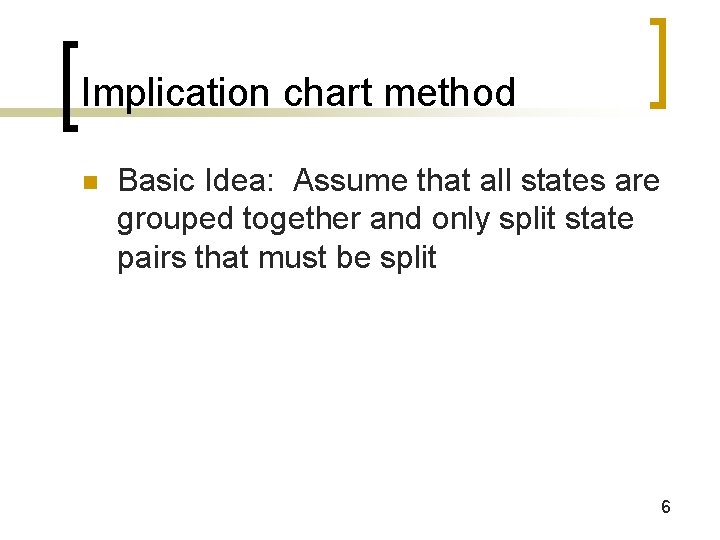

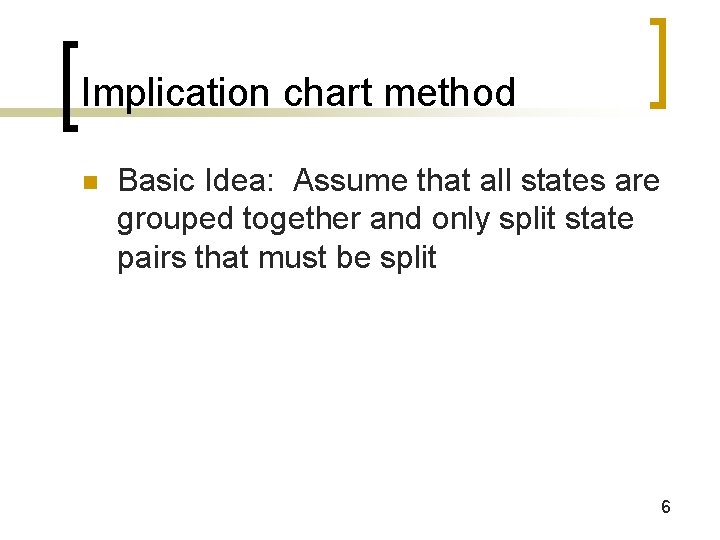

Implication chart method n Basic Idea: Assume that all states are grouped together and only split state pairs that must be split 6

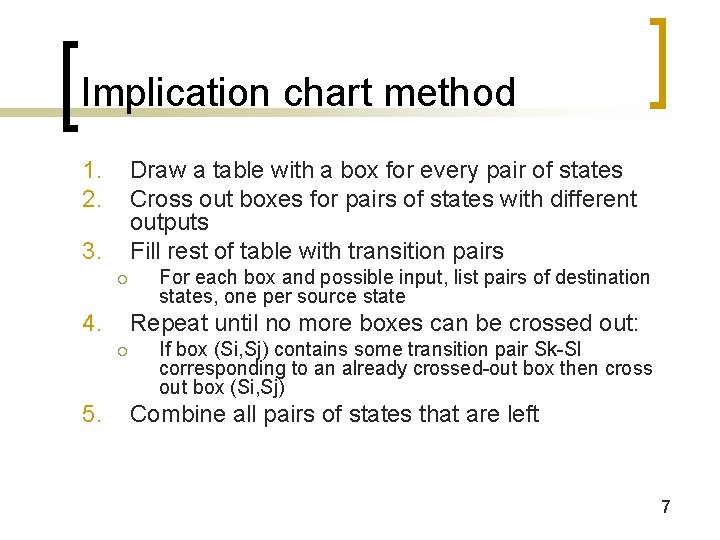

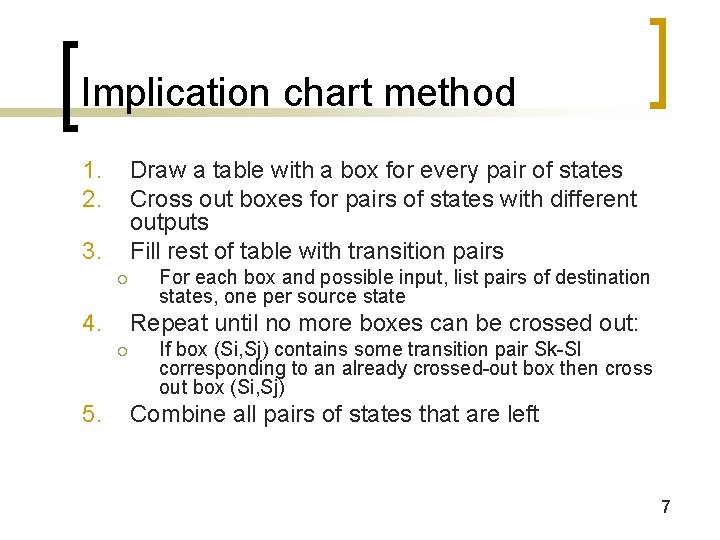

Implication chart method 1. 2. Draw a table with a box for every pair of states Cross out boxes for pairs of states with different outputs Fill rest of table with transition pairs 3. ¡ 4. Repeat until no more boxes can be crossed out: ¡ 5. For each box and possible input, list pairs of destination states, one per source state If box (Si, Sj) contains some transition pair Sk-Sl corresponding to an already crossed-out box then cross out box (Si, Sj) Combine all pairs of states that are left 7

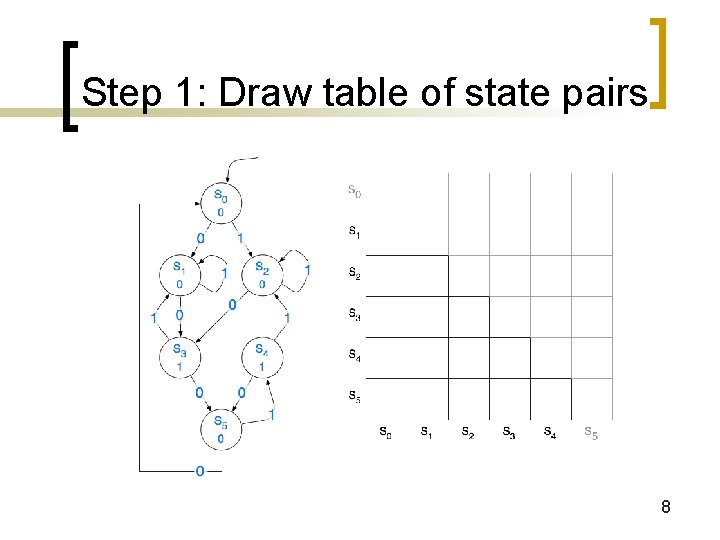

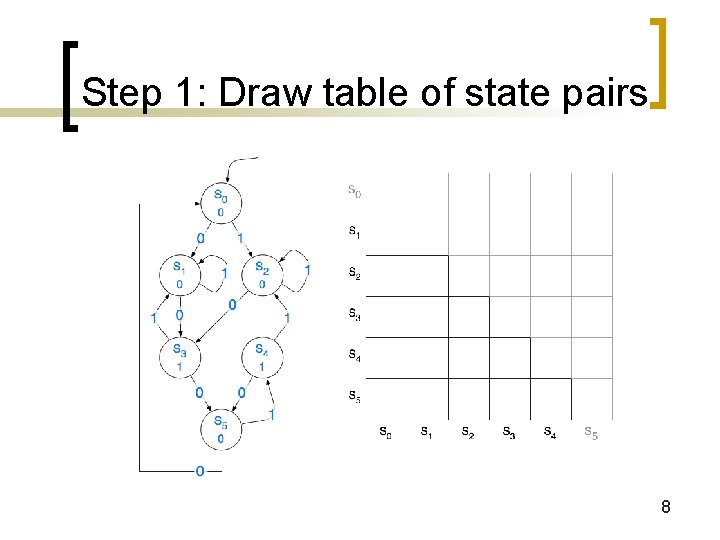

Step 1: Draw table of state pairs 8

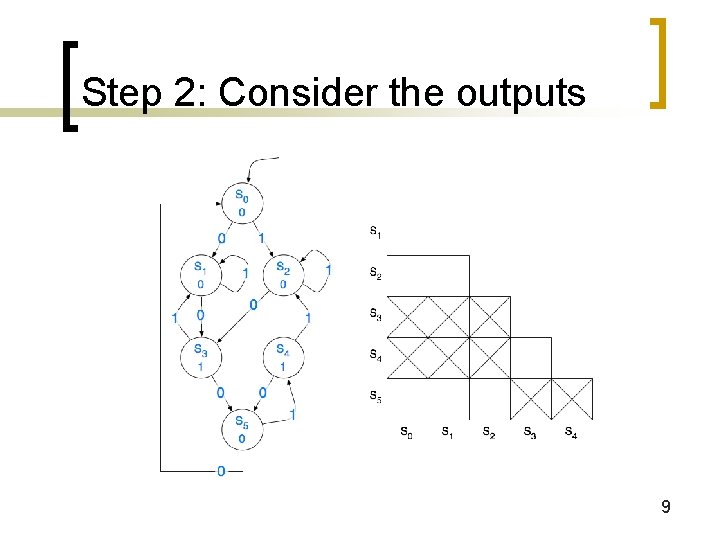

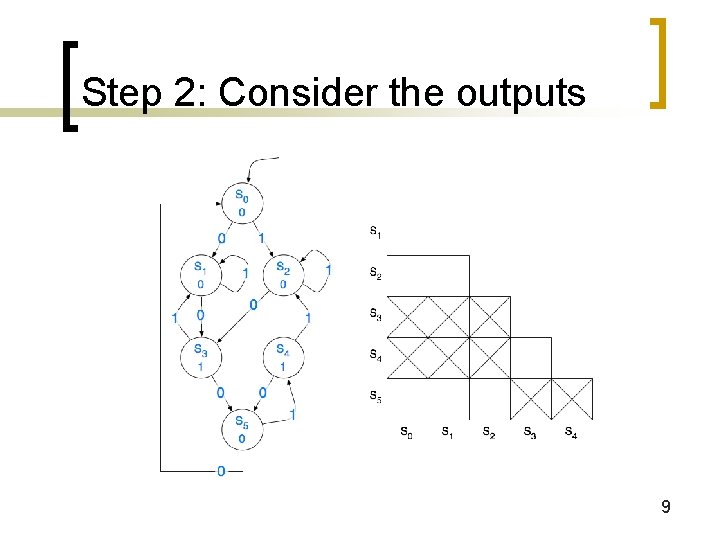

Step 2: Consider the outputs 9

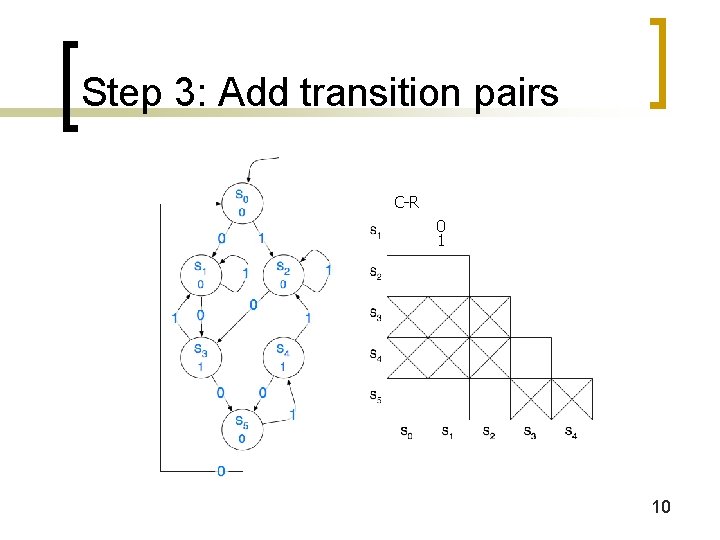

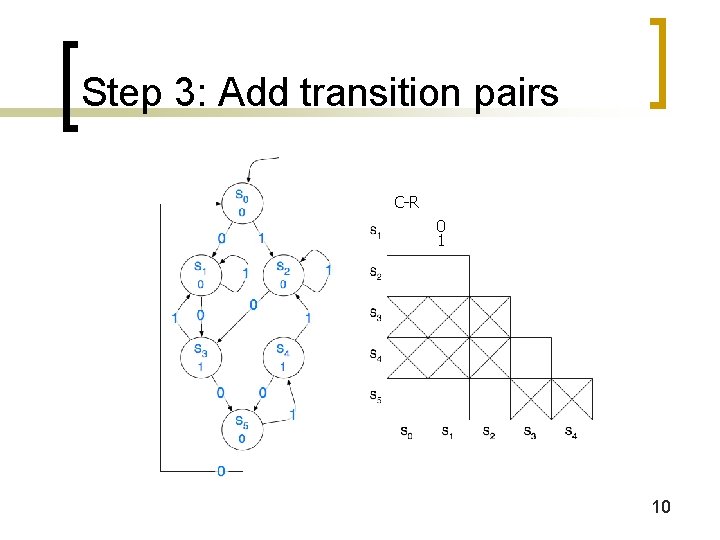

Step 3: Add transition pairs C-R 0 1 10

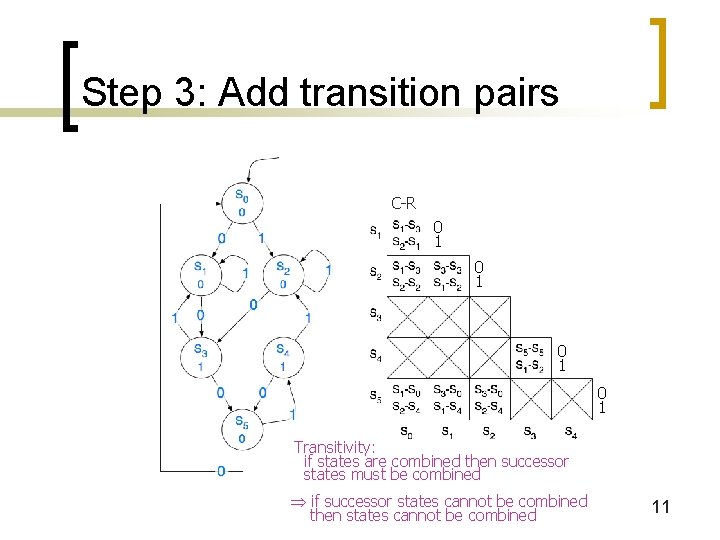

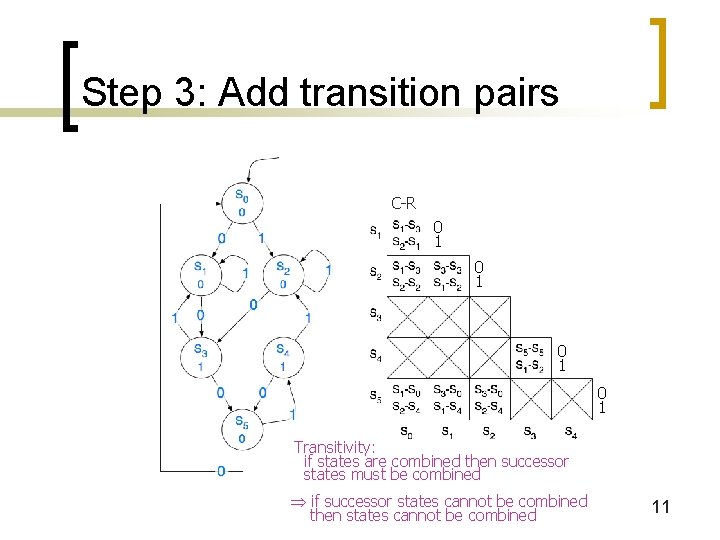

Step 3: Add transition pairs C-R 0 1 0 1 Transitivity: if states are combined then successor states must be combined if successor states cannot be combined then states cannot be combined 11

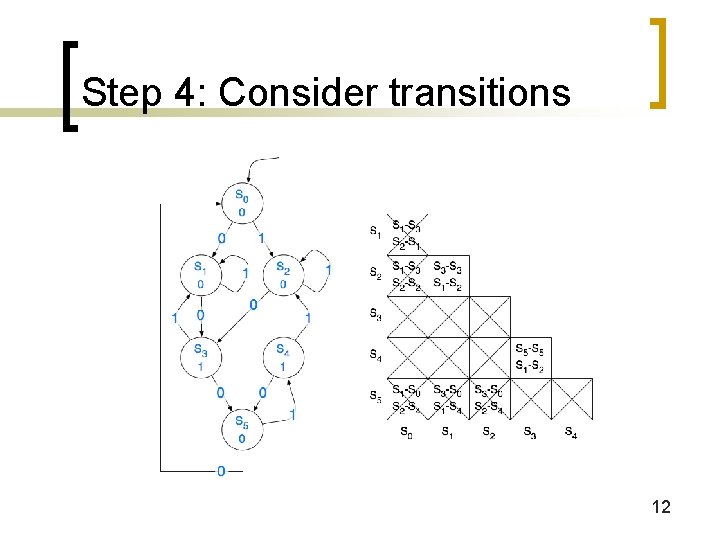

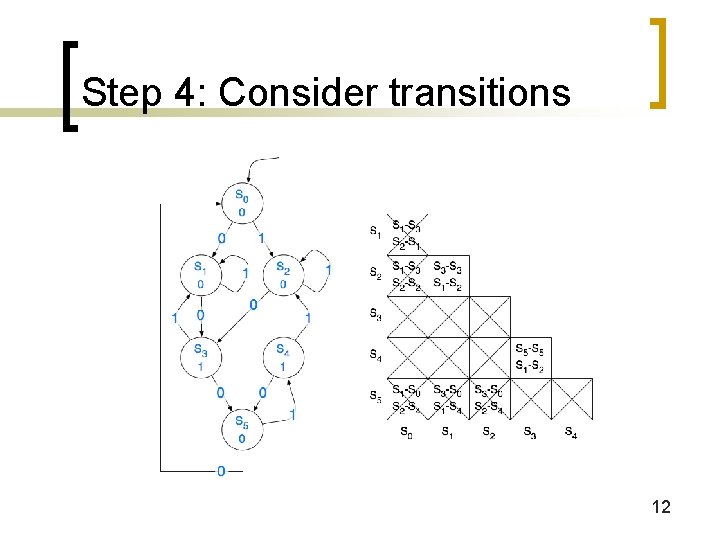

Step 4: Consider transitions 12

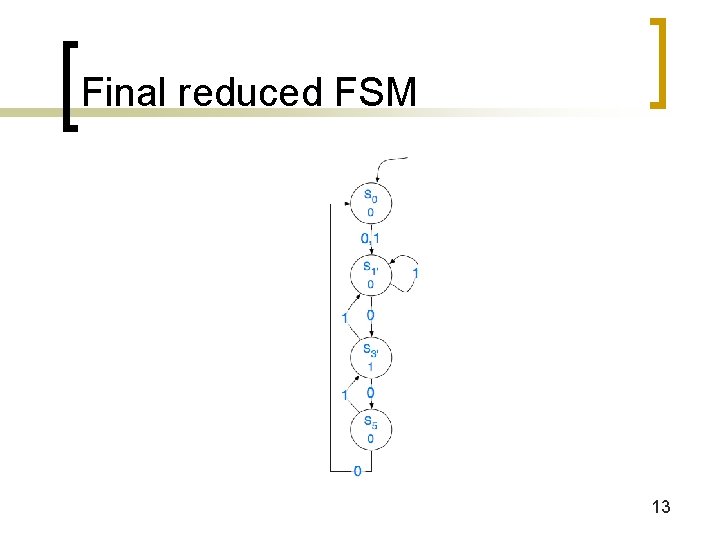

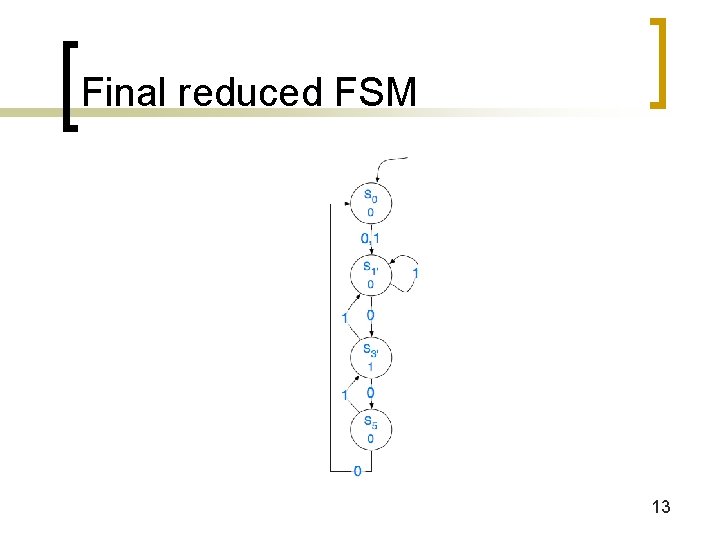

Final reduced FSM 13

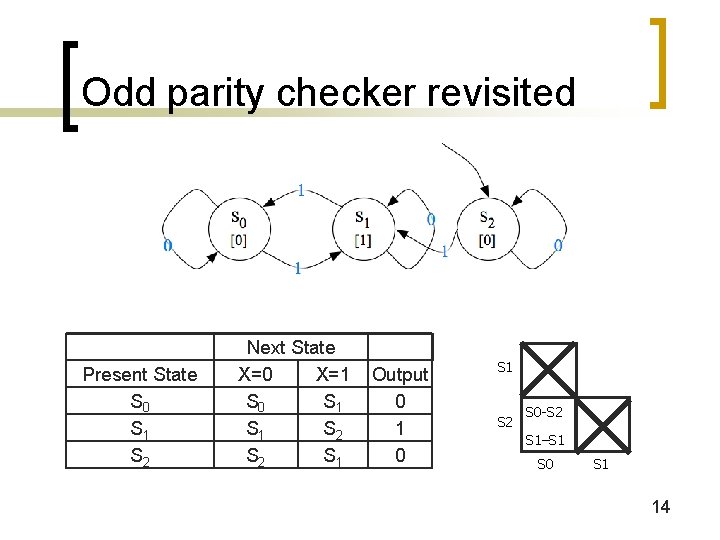

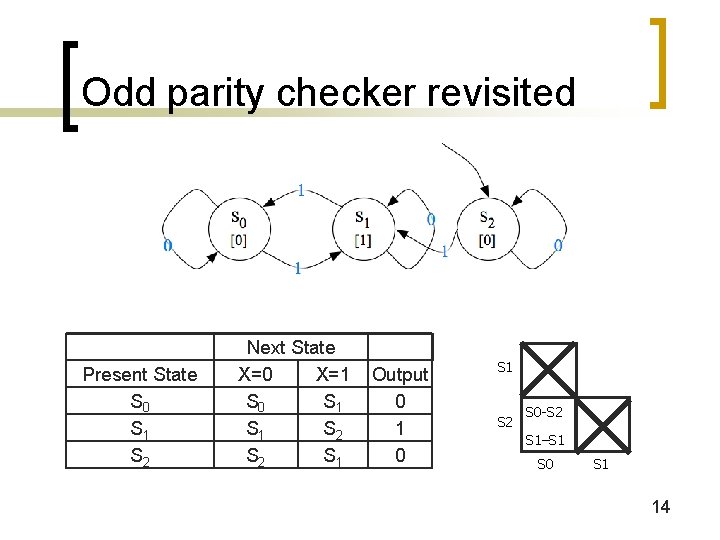

Odd parity checker revisited Present State S 0 S 1 S 2 Next State X=0 X=1 S 0 S 1 S 2 S 1 Output 0 1 0 S 1 S 2 S 0 -S 2 S 1–S 1 S 0 S 1 14

![More complex minimization inputs here 00 10 00 S 0 1 01 10 S More complex minimization inputs here 00 10 00 S 0 [1] 01 10 S](https://slidetodoc.com/presentation_image_h2/b0fe8ef6c1d60e8b42162f14ed5787f1/image-15.jpg)

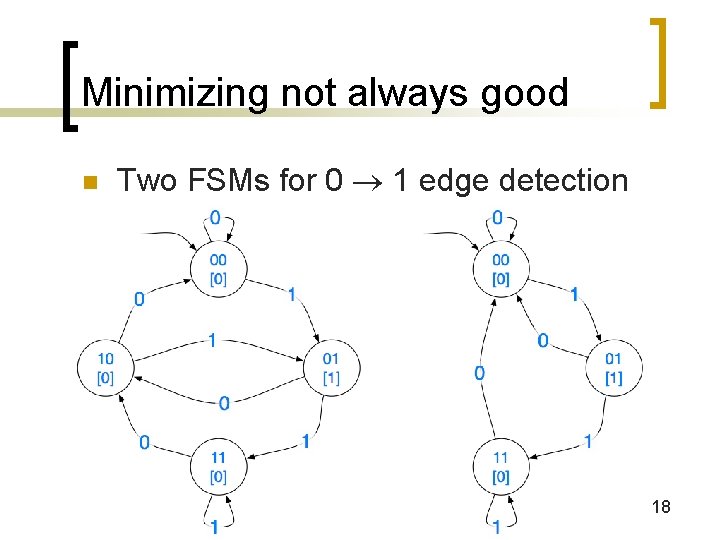

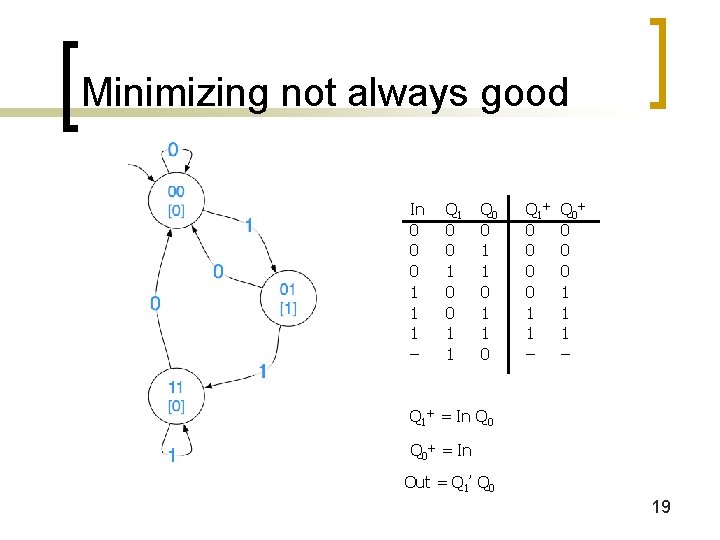

More complex minimization inputs here 00 10 00 S 0 [1] 01 10 S 2 [1] 01 11 10 01 S 4 [1] S 3 [0] 11 10 10 00 present state S 0 S 1 S 2 S 3 S 4 S 5 11 00 01 01 11 00 10 S 1 [0] 11 01 S 5 [0] 00 11 00 S 0 S 1 next state 01 10 11 S 2 S 3 S 1 S 4 S 3 S 2 S 4 S 0 S 4 S 5 S 1 S 2 S 5 S 4 S 0 S 5 output 1 0 1 0 symbolic state transition table 15

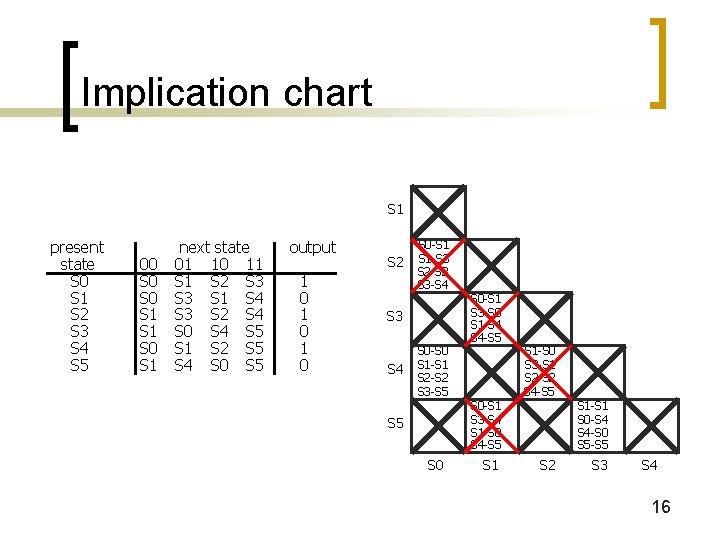

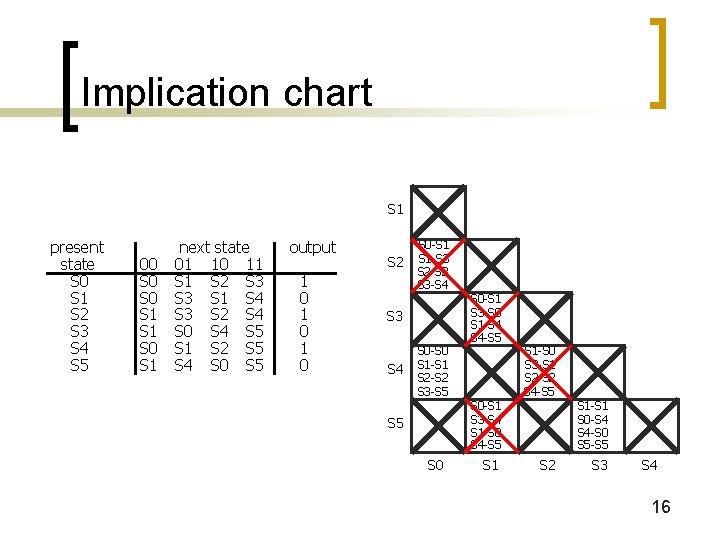

Implication chart S 1 present state S 0 S 1 S 2 S 3 S 4 S 5 00 S 0 S 1 next state 01 10 11 S 2 S 3 S 1 S 4 S 3 S 2 S 4 S 0 S 4 S 5 S 1 S 2 S 5 S 4 S 0 S 5 output 1 0 1 0 S 2 S 0 -S 1 S 1 -S 3 S 2 -S 2 S 3 -S 4 S 3 S 4 S 0 -S 0 S 1 -S 1 S 2 -S 2 S 3 -S 5 S 0 S 0 -S 1 S 3 -S 0 S 1 -S 4 S 4 -S 5 S 0 -S 1 S 3 -S 4 S 1 -S 0 S 4 -S 5 S 1 -S 0 S 3 -S 1 S 2 -S 2 S 4 -S 5 S 2 S 1 -S 1 S 0 -S 4 S 4 -S 0 S 5 -S 5 S 3 S 4 16

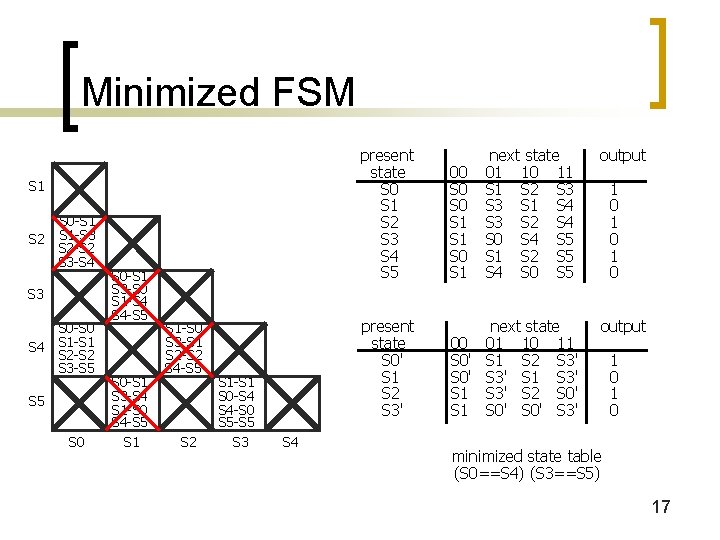

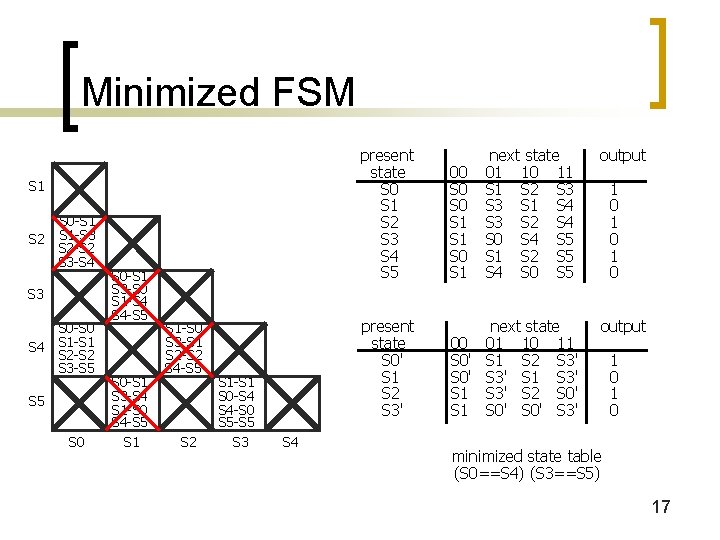

Minimized FSM S 1 S 2 S 0 -S 1 S 1 -S 3 S 2 -S 2 S 3 -S 4 S 3 S 4 S 0 -S 0 S 1 -S 1 S 2 -S 2 S 3 -S 5 S 0 S 0 -S 1 S 3 -S 0 S 1 -S 4 S 4 -S 5 S 0 -S 1 S 3 -S 4 S 1 -S 0 S 4 -S 5 S 1 -S 0 S 3 -S 1 S 2 -S 2 S 4 -S 5 S 2 S 1 -S 1 S 0 -S 4 S 4 -S 0 S 5 -S 5 S 3 S 4 present state S 0 S 1 S 2 S 3 S 4 S 5 00 S 0 S 1 next state 01 10 11 S 2 S 3 S 1 S 4 S 3 S 2 S 4 S 0 S 4 S 5 S 1 S 2 S 5 S 4 S 0 S 5 output present state S 0' S 1 S 2 S 3' next state 00 01 10 11 S 0' S 1 S 2 S 3' S 0' S 3' S 1 S 3' S 2 S 0' S 1 S 0' S 3' output 1 0 1 0 1 0 minimized state table (S 0==S 4) (S 3==S 5) 17

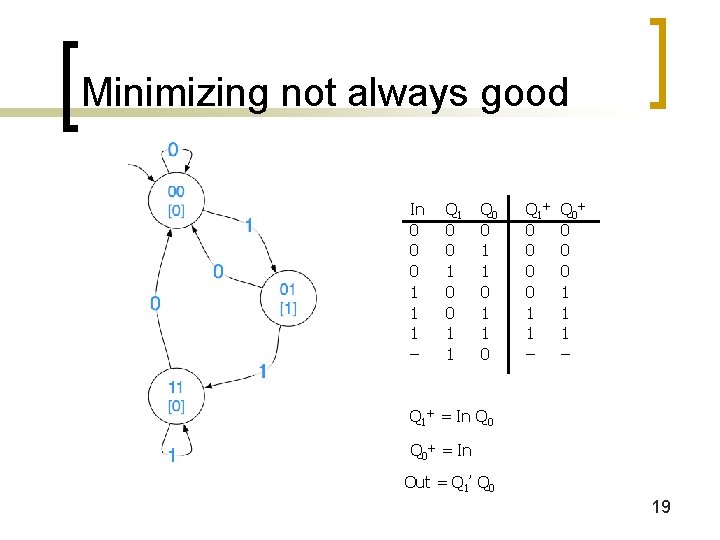

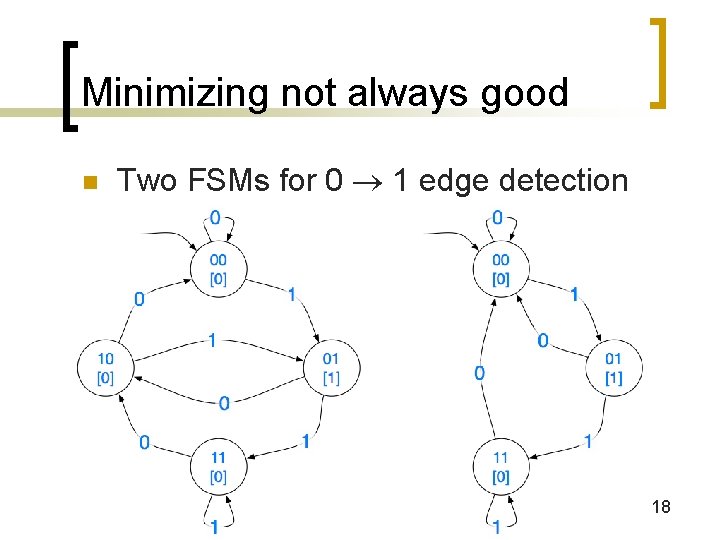

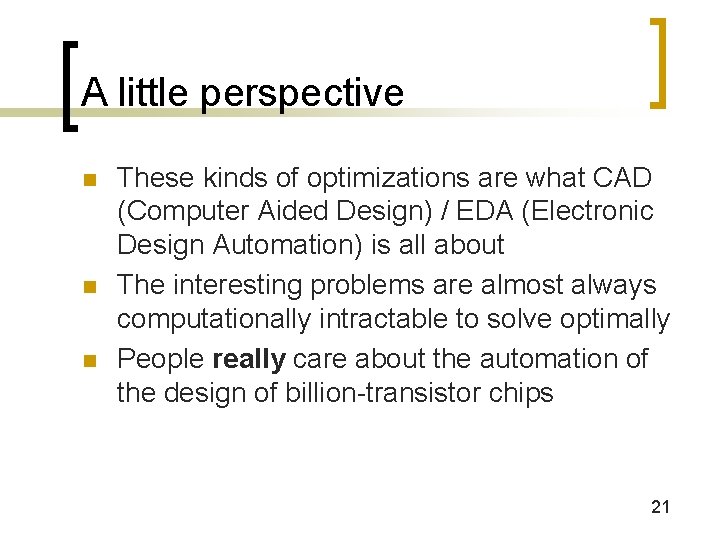

Minimizing not always good n Two FSMs for 0 1 edge detection 18

Minimizing not always good In 0 0 0 1 1 1 – Q 1 0 0 1 1 Q 0 0 1 1 0 Q 1+ 0 0 1 1 – Q 0+ 0 0 0 1 1 1 – Q 1+ = In Q 0+ = In Out = Q 1’ Q 0 19

Minimizing not always good In 0 0 0 Q 1 0 0 1 Q 0 0 1 0 Q 1+ 0 1 0 Q 0+ 0 0 1 1 0 1 0 0 1 1 1 1 Q 1+ = Q 0+ = In Out = Q 1’ Q 0 20

A little perspective n n n These kinds of optimizations are what CAD (Computer Aided Design) / EDA (Electronic Design Automation) is all about The interesting problems are almost always computationally intractable to solve optimally People really care about the automation of the design of billion-transistor chips 21