Lecture 2 Boolean Algebra Basic Algebra An algebra

Lecture 2 Boolean Algebra Basic • Algebra – An algebra A is a mathematics theory involving a set of elements S and a set of operations O that act on the members of S. – The smallest Boolean algebra contains two values, 0 and 1. – If X is a Boolean variable, then either X = 0 or X = 1. – 1 can mean high voltage or True while 0 might correspond to low voltage or False. Chap 2 1 C-H

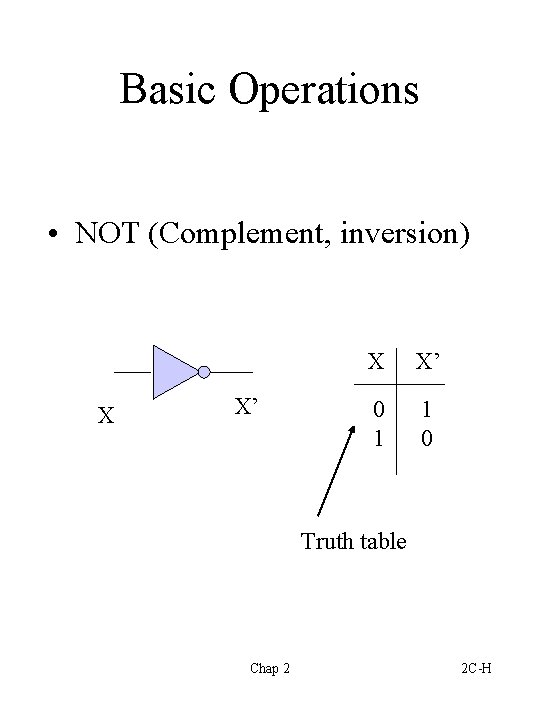

Basic Operations • NOT (Complement, inversion) X X’ 0 1 1 0 Truth table Chap 2 2 C-H

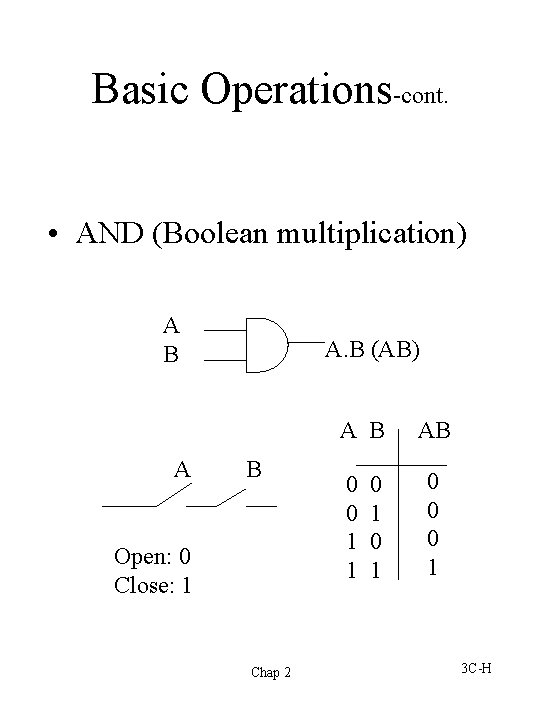

Basic Operations-cont. • AND (Boolean multiplication) A B A. B (AB) A B Open: 0 Close: 1 Chap 2 0 0 1 1 0 1 AB 0 0 0 1 3 C-H

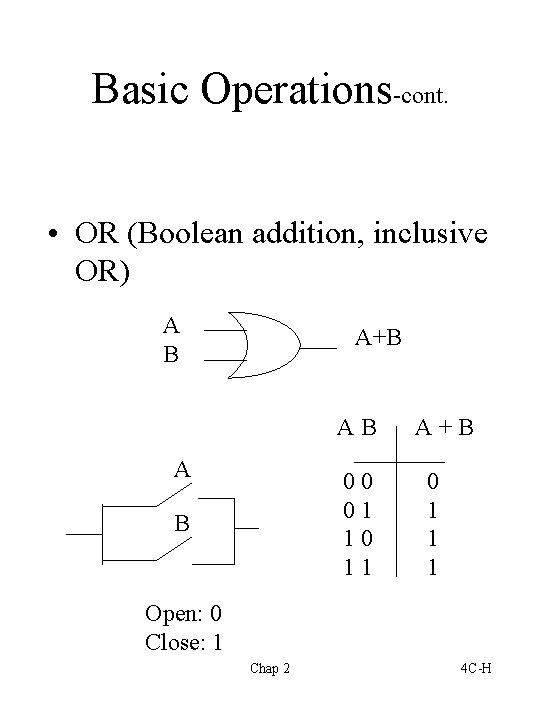

Basic Operations-cont. • OR (Boolean addition, inclusive OR) A B A+B AB A 00 01 10 11 B A+B 0 1 1 1 Open: 0 Close: 1 Chap 2 4 C-H

![Boolean Expressions • Examples: AB’ + C (1) [A(C+ D)]’ + BC (2) – Boolean Expressions • Examples: AB’ + C (1) [A(C+ D)]’ + BC (2) –](http://slidetodoc.com/presentation_image_h2/23dc1ad7361746e41e2d2da6369f92bd/image-5.jpg)

Boolean Expressions • Examples: AB’ + C (1) [A(C+ D)]’ + BC (2) – Each expression corresponds to a network of logic gates. • Exercise: Draw the logic gate network for (1) and (2). – In (2), there are 4 variables and 5 literals. • Operation order: – Parenthesis, NOT-> AND-> OR Chap 2 5 C-H

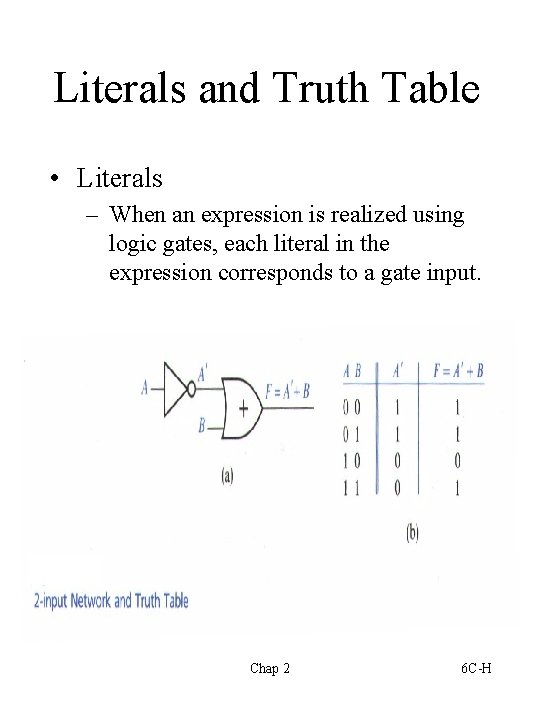

Literals and Truth Table • Literals – When an expression is realized using logic gates, each literal in the expression corresponds to a gate input. Chap 2 6 C-H

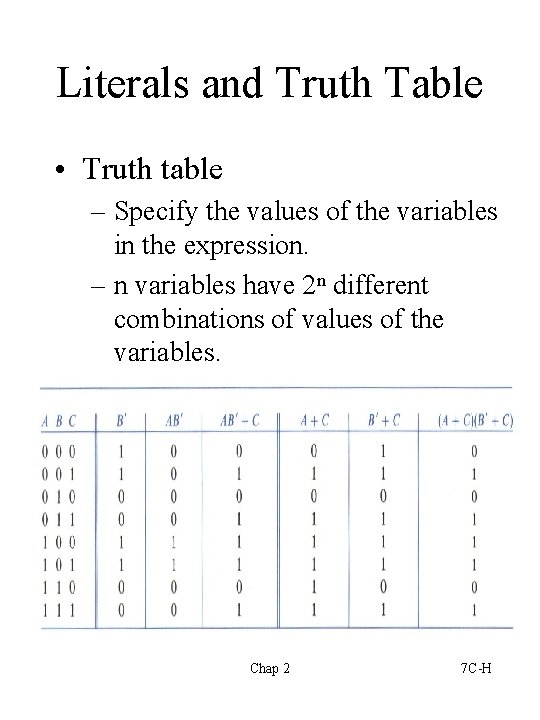

Literals and Truth Table • Truth table – Specify the values of the variables in the expression. – n variables have 2 n different combinations of values of the variables. Chap 2 7 C-H

Basic Theorems • Operation with 0 and 1 X+0=X X+1= 1 X‧ 1 = X X‧ 0 = 0 • Idempotent laws X+X=X X‧X = X • Involution law (X’)’ = X • Laws of complementarity X + X’ = 1 X‧X’ = 0 Chap 2 8 C-H

Basic Theorems-cont. • Commutative laws X+Y= Y+X XY = YX • Associative laws (X+Y) + Z = X + (Y + Z) = X + Y + Z (XY)Z = X(YZ) = XYZ • Distributive laws X(Y + Z) = XY + XZ X + YZ = (X+Y)(X+Z) Chap 2 9 C-H

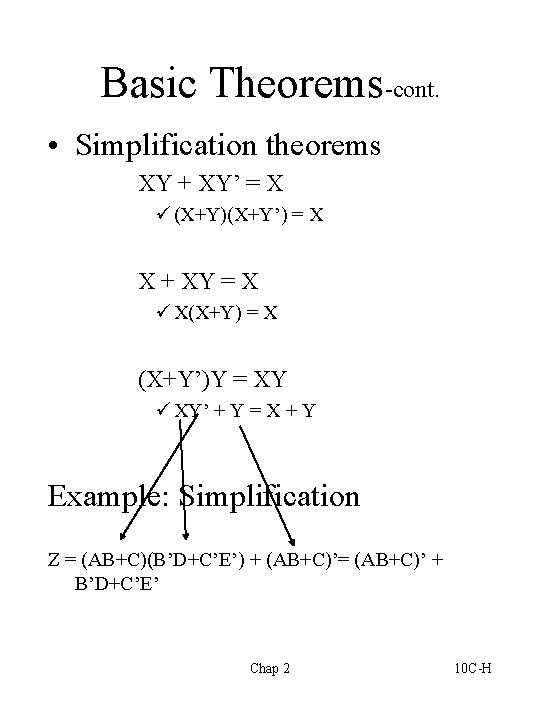

Basic Theorems-cont. • Simplification theorems XY + XY’ = X ü (X+Y)(X+Y’) = X X + XY = X ü X(X+Y) = X (X+Y’)Y = XY ü XY’ + Y = X + Y Example: Simplification Z = (AB+C)(B’D+C’E’) + (AB+C)’= (AB+C)’ + B’D+C’E’ Chap 2 10 C-H

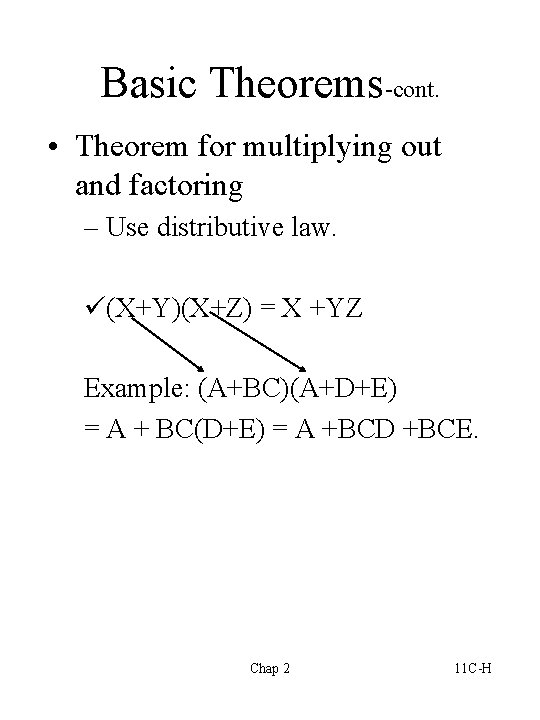

Basic Theorems-cont. • Theorem for multiplying out and factoring – Use distributive law. ü(X+Y)(X+Z) = X +YZ Example: (A+BC)(A+D+E) = A + BC(D+E) = A +BCD +BCE. Chap 2 11 C-H

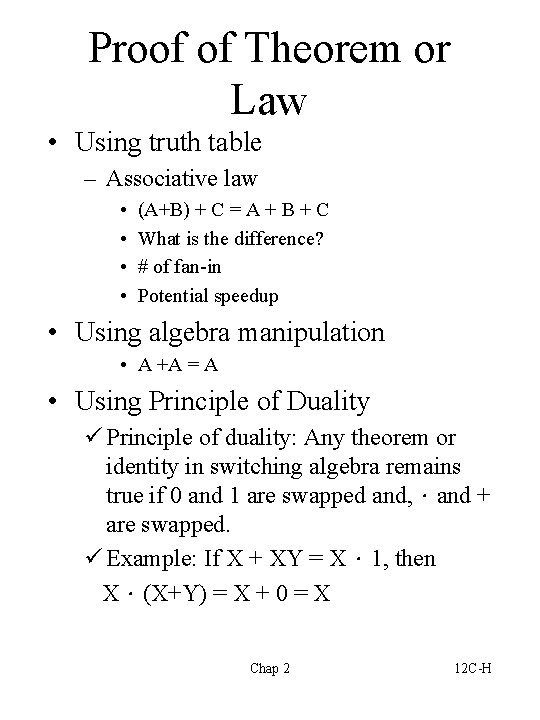

Proof of Theorem or Law • Using truth table – Associative law • • (A+B) + C = A + B + C What is the difference? # of fan-in Potential speedup • Using algebra manipulation • A +A = A • Using Principle of Duality ü Principle of duality: Any theorem or identity in switching algebra remains true if 0 and 1 are swapped and, .and + are swapped. ü Example: If X + XY = X.1, then X.(X+Y) = X + 0 = X Chap 2 12 C-H

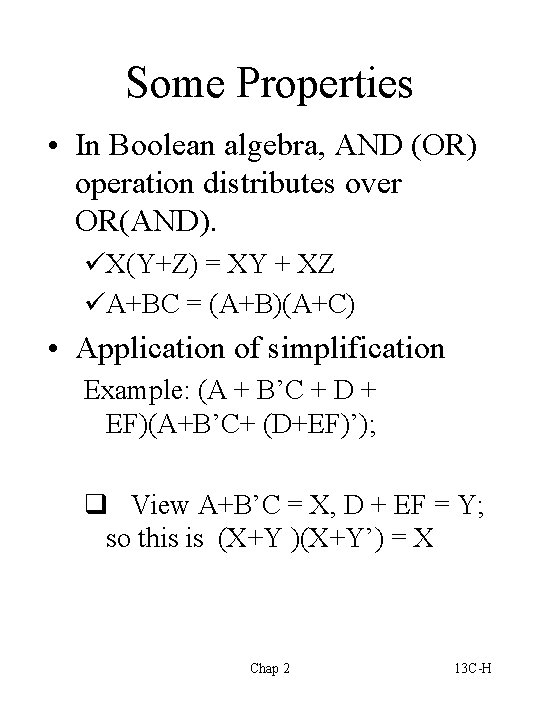

Some Properties • In Boolean algebra, AND (OR) operation distributes over OR(AND). üX(Y+Z) = XY + XZ üA+BC = (A+B)(A+C) • Application of simplification Example: (A + B’C + D + EF)(A+B’C+ (D+EF)’); q View A+B’C = X, D + EF = Y; so this is (X+Y )(X+Y’) = X Chap 2 13 C-H

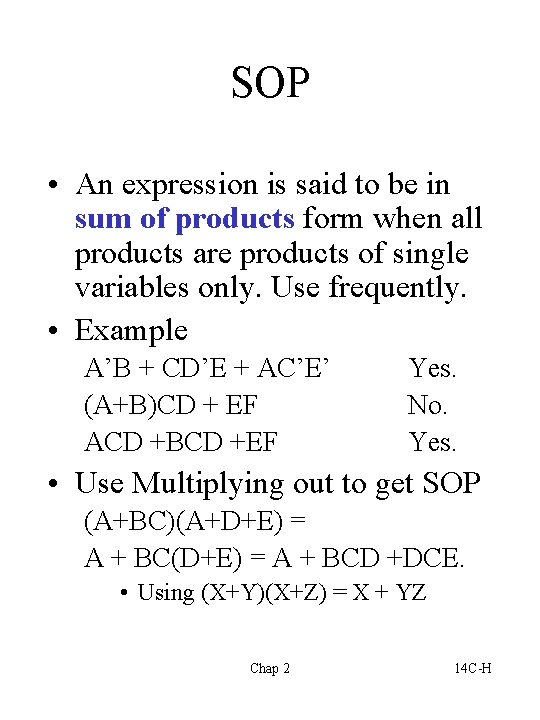

SOP • An expression is said to be in sum of products form when all products are products of single variables only. Use frequently. • Example A’B + CD’E + AC’E’ (A+B)CD + EF ACD +BCD +EF Yes. No. Yes. • Use Multiplying out to get SOP (A+BC)(A+D+E) = A + BC(D+E) = A + BCD +DCE. • Using (X+Y)(X+Z) = X + YZ Chap 2 14 C-H

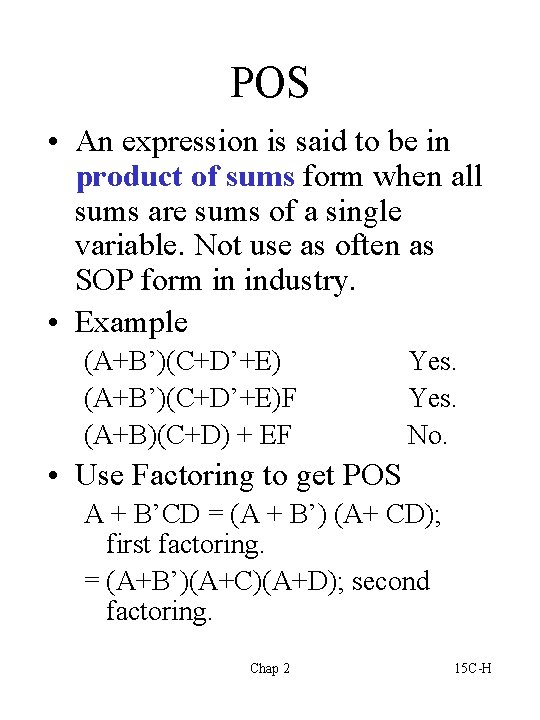

POS • An expression is said to be in product of sums form when all sums are sums of a single variable. Not use as often as SOP form in industry. • Example (A+B’)(C+D’+E)F (A+B)(C+D) + EF Yes. No. • Use Factoring to get POS A + B’CD = (A + B’) (A+ CD); first factoring. = (A+B’)(A+C)(A+D); second factoring. Chap 2 15 C-H

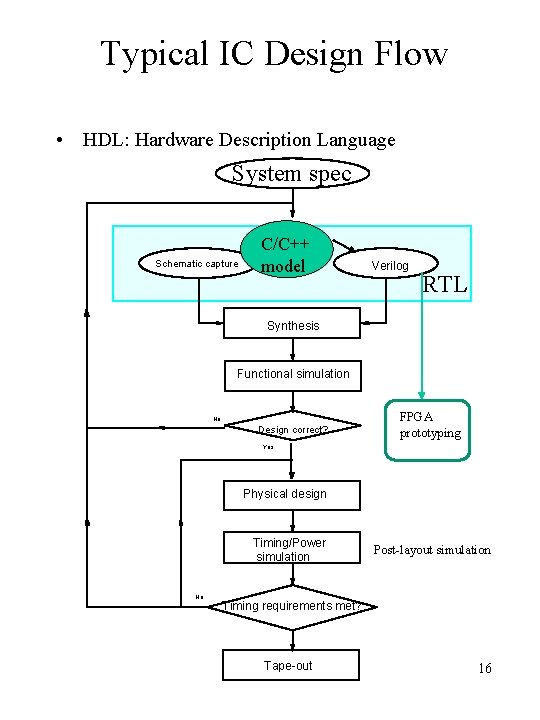

Typical IC Design Flow • HDL: Hardware Description Language System spec DESIGN ENTRY Schematic capture C/C++ model Verilog RTL Synthesis Functional simulation No Design correct? FPGA prototyping Yes Physical design Timing/Power simulation No Post-layout simulation Timing requirements met? Tape-out 16

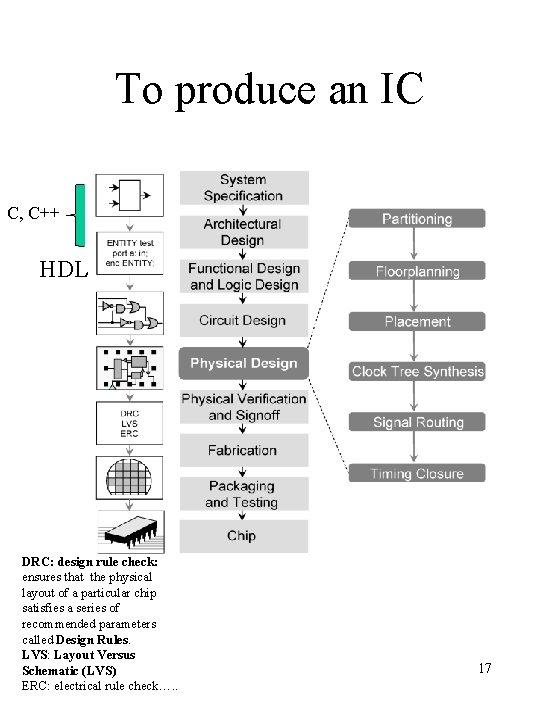

To produce an IC C, C++ HDL DRC: design rule check: ensures that the physical layout of a particular chip satisfies a series of recommended parameters called Design Rules. LVS: Layout Versus Schematic (LVS) ERC: electrical rule check…. . 17

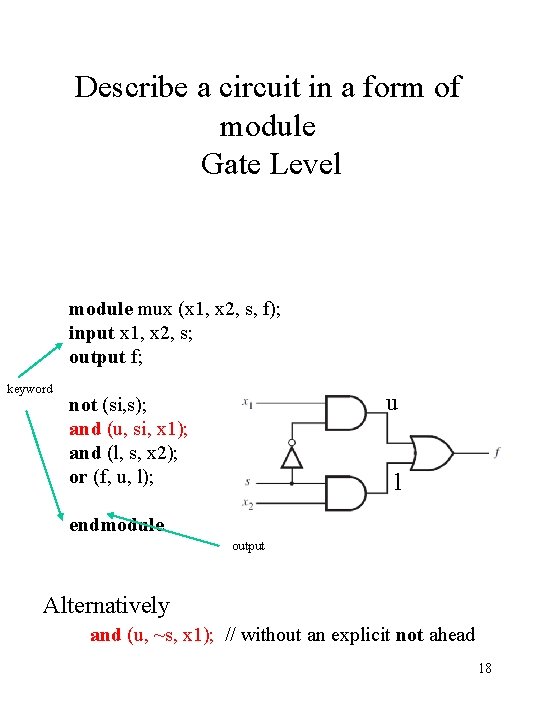

Describe a circuit in a form of module Gate Level module mux (x 1, x 2, s, f); input x 1, x 2, s; output f; keyword u not (si, s); and (u, si, x 1); and (l, s, x 2); or (f, u, l); l endmodule output Alternatively and (u, ~s, x 1); // without an explicit not ahead 18

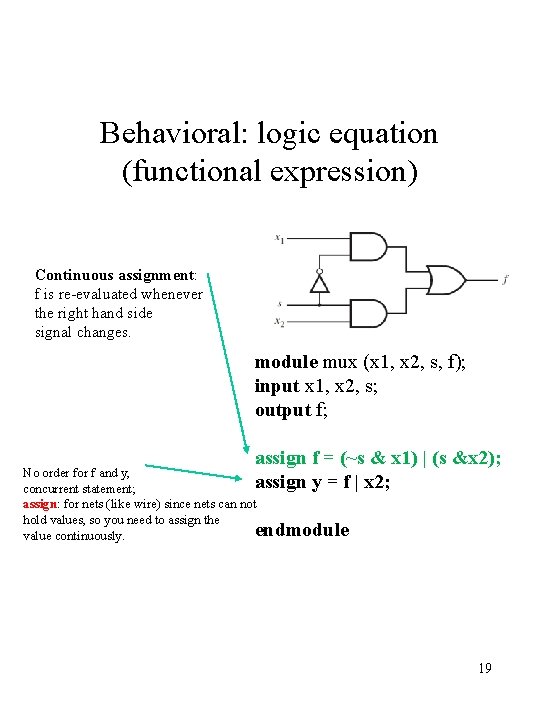

Behavioral: logic equation (functional expression) Continuous assignment: f is re-evaluated whenever the right hand side signal changes. module mux (x 1, x 2, s, f); input x 1, x 2, s; output f; assign f = (~s & x 1) | (s &x 2); | x 2; No order for f and y, assign y = f concurrent statement; assign: for nets (like wire) since nets can not hold values, so you need to assign the endmodule value continuously. 19

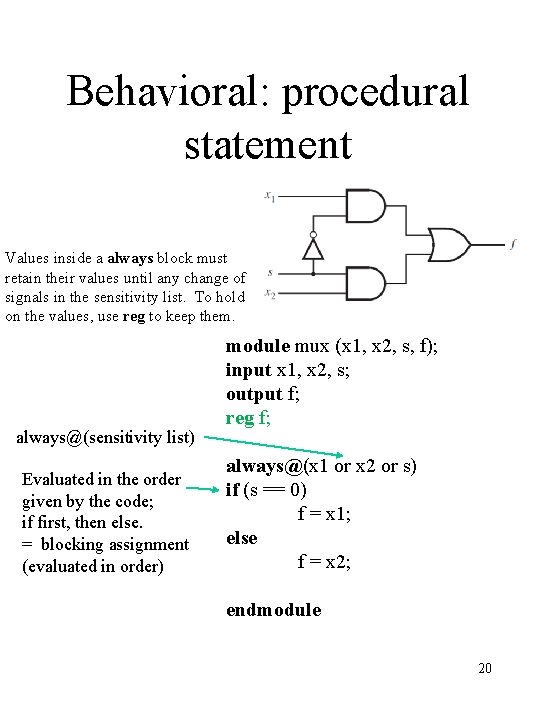

Behavioral: procedural statement Values inside a always block must retain their values until any change of signals in the sensitivity list. To hold on the values, use reg to keep them. always@(sensitivity list) Evaluated in the order given by the code; if first, then else. = blocking assignment (evaluated in order) module mux (x 1, x 2, s, f); input x 1, x 2, s; output f; reg f; always@(x 1 or x 2 or s) if (s == 0) f = x 1; else f = x 2; endmodule 20

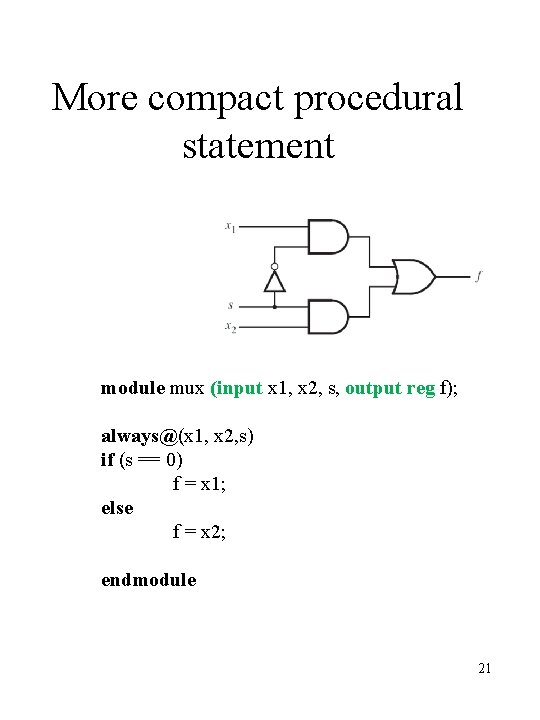

More compact procedural statement module mux (input x 1, x 2, s, output reg f); always@(x 1, x 2, s) if (s == 0) f = x 1; else f = x 2; endmodule 21

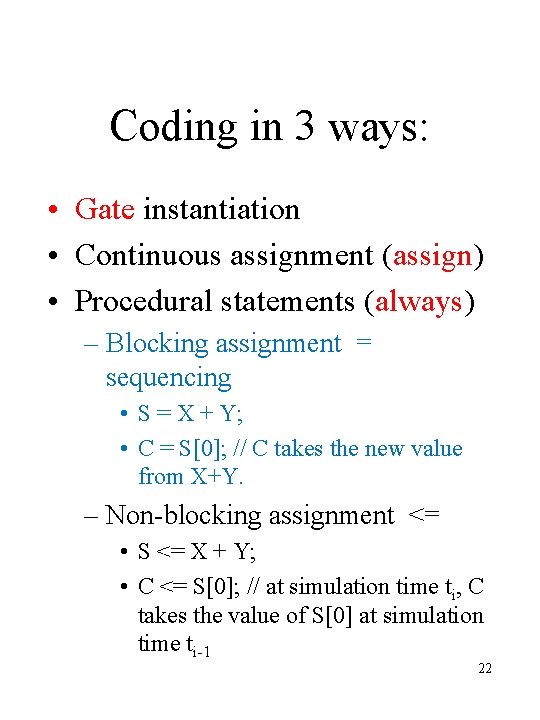

Coding in 3 ways: • Gate instantiation • Continuous assignment (assign) • Procedural statements (always) – Blocking assignment = sequencing • S = X + Y; • C = S[0]; // C takes the new value from X+Y. – Non-blocking assignment <= • S <= X + Y; • C <= S[0]; // at simulation time ti, C takes the value of S[0] at simulation time ti-1 22

- Slides: 22