Lecture 2 AVR Memory Space and Addressing Modes

- Slides: 37

Lecture 2: AVR Memory Space and Addressing Modes 1

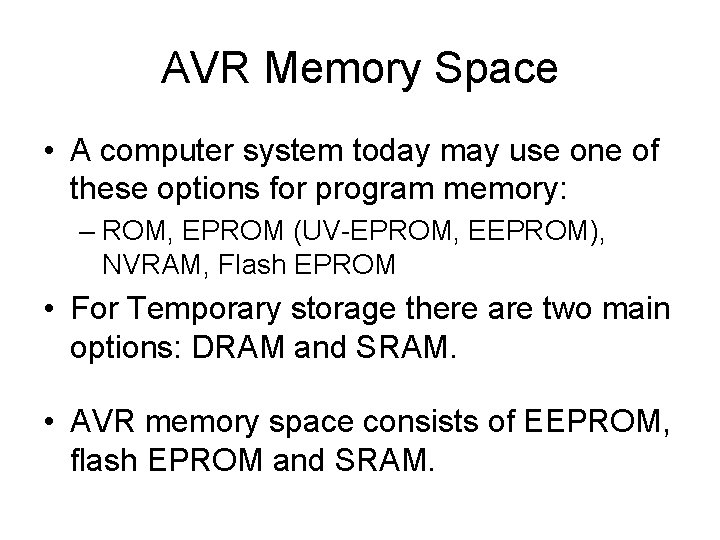

AVR Memory Space • A computer system today may use one of these options for program memory: – ROM, EPROM (UV-EPROM, EEPROM), NVRAM, Flash EPROM • For Temporary storage there are two main options: DRAM and SRAM. • AVR memory space consists of EEPROM, flash EPROM and SRAM.

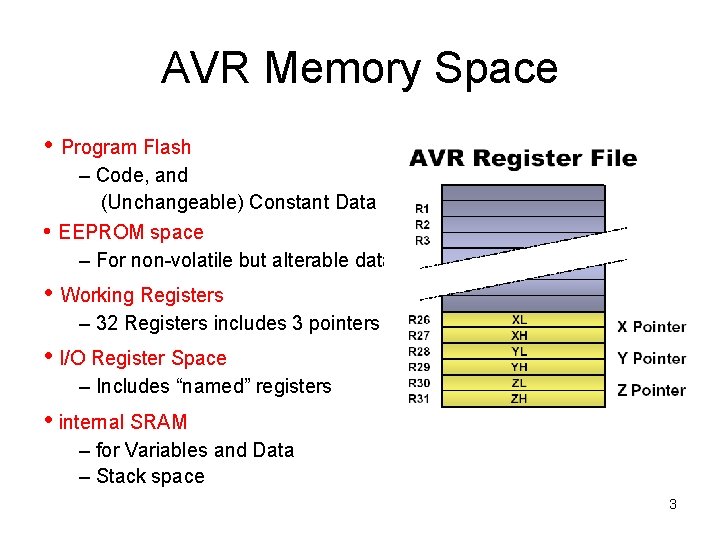

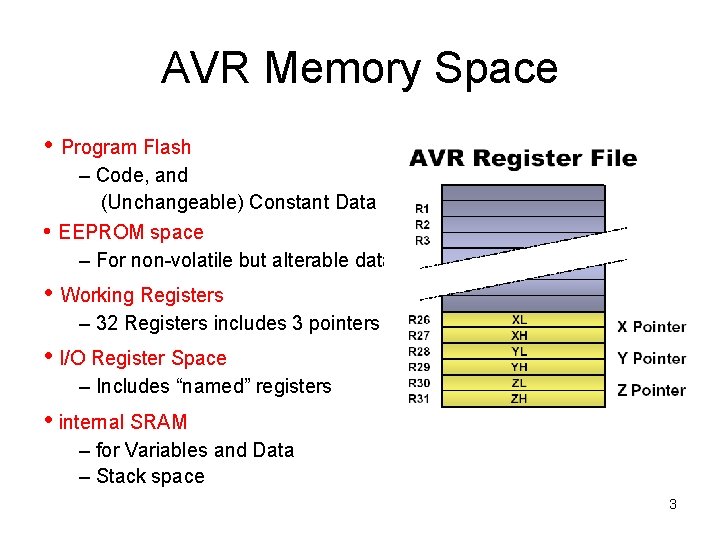

AVR Memory Space • Program Flash – Code, and (Unchangeable) Constant Data • EEPROM space – For non-volatile but alterable data • Working Registers – 32 Registers includes 3 pointers • I/O Register Space – Includes “named” registers • internal SRAM – for Variables and Data – Stack space 3

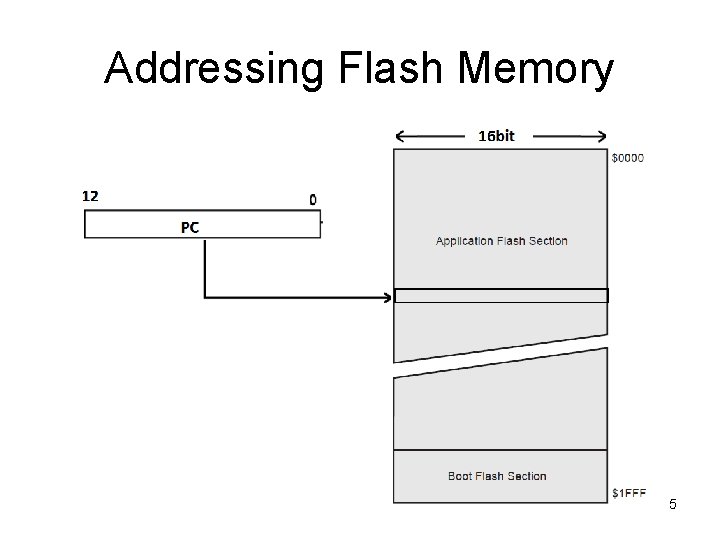

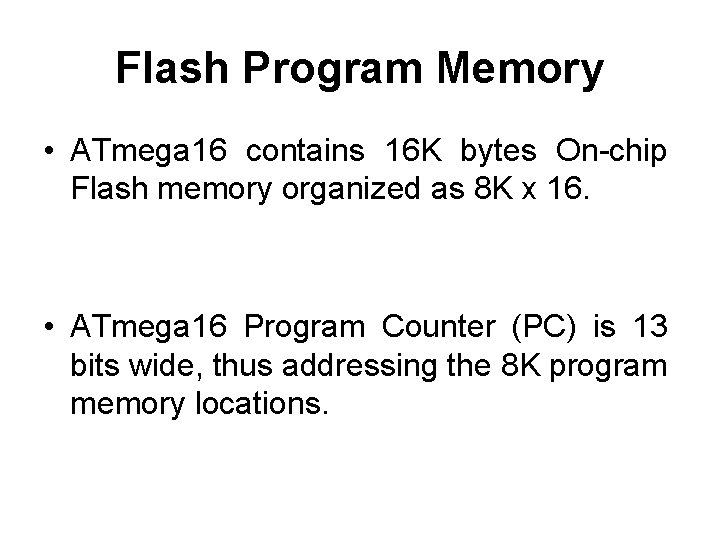

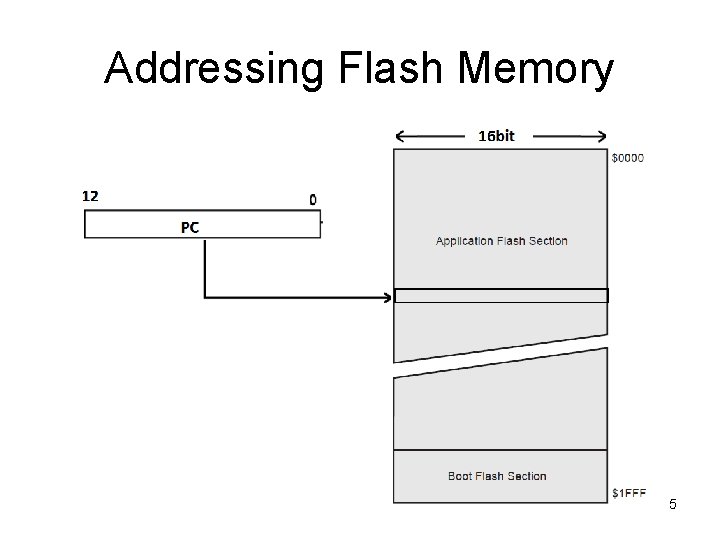

Flash Program Memory • ATmega 16 contains 16 K bytes On-chip Flash memory organized as 8 K x 16. • ATmega 16 Program Counter (PC) is 13 bits wide, thus addressing the 8 K program memory locations.

Addressing Flash Memory 5

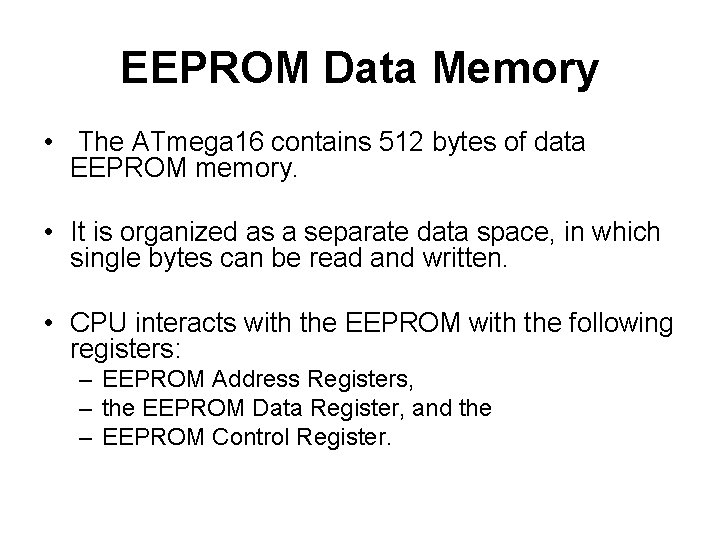

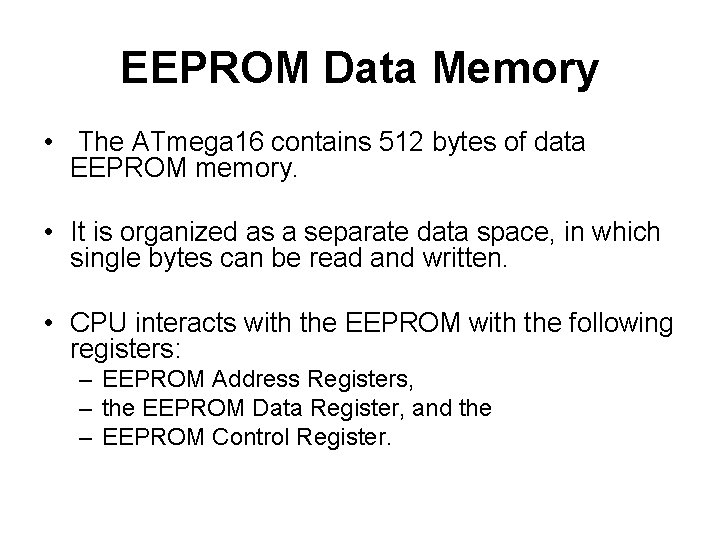

EEPROM Data Memory • The ATmega 16 contains 512 bytes of data EEPROM memory. • It is organized as a separate data space, in which single bytes can be read and written. • CPU interacts with the EEPROM with the following registers: – EEPROM Address Registers, – the EEPROM Data Register, and the – EEPROM Control Register.

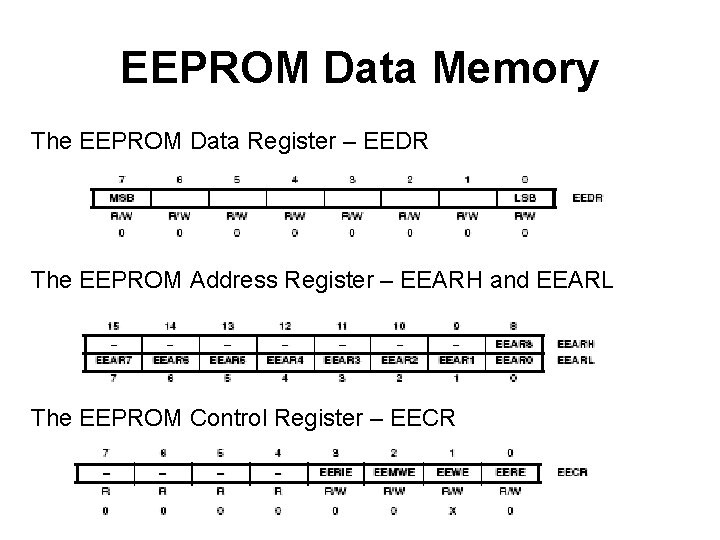

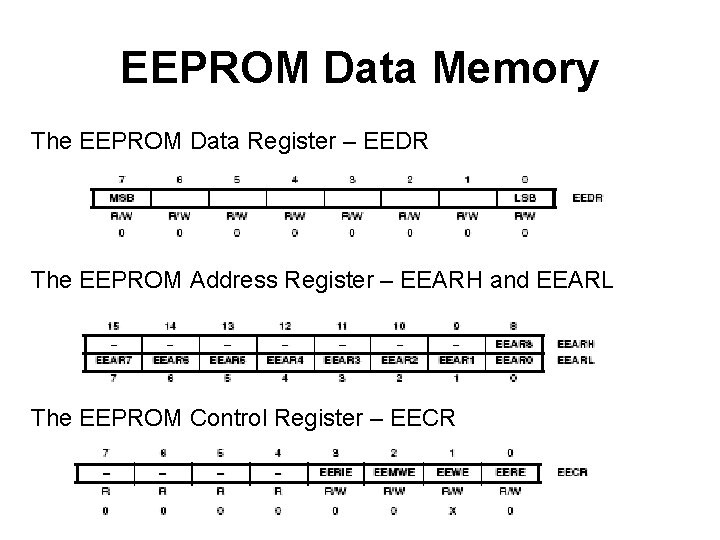

EEPROM Data Memory The EEPROM Data Register – EEDR The EEPROM Address Register – EEARH and EEARL The EEPROM Control Register – EECR

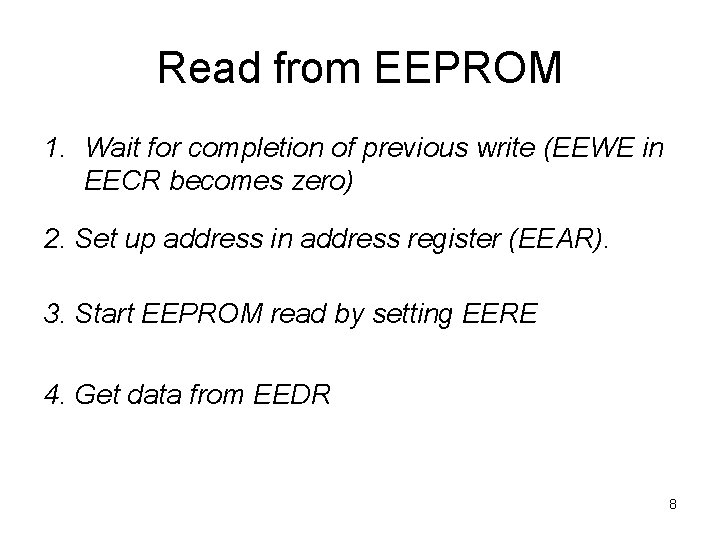

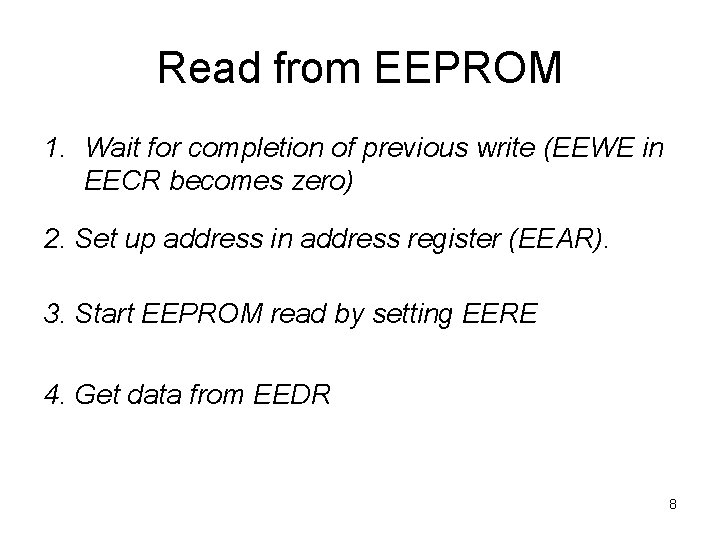

Read from EEPROM 1. Wait for completion of previous write (EEWE in EECR becomes zero) 2. Set up address in address register (EEAR). 3. Start EEPROM read by setting EERE 4. Get data from EEDR 8

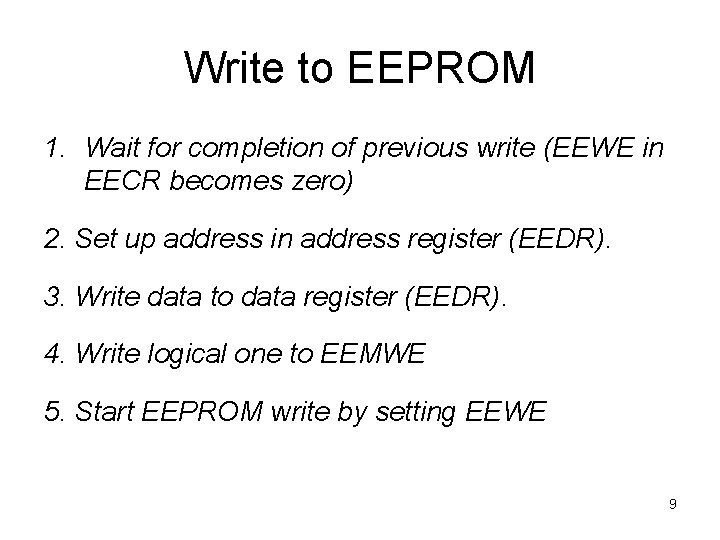

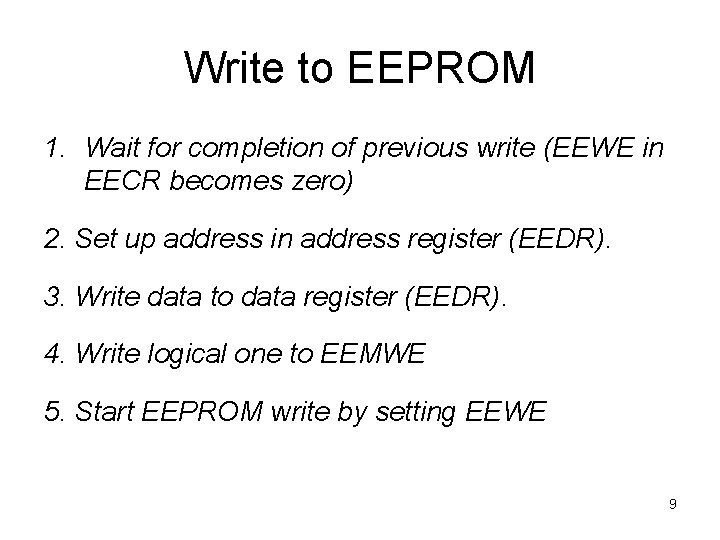

Write to EEPROM 1. Wait for completion of previous write (EEWE in EECR becomes zero) 2. Set up address in address register (EEDR). 3. Write data to data register (EEDR). 4. Write logical one to EEMWE 5. Start EEPROM write by setting EEWE 9

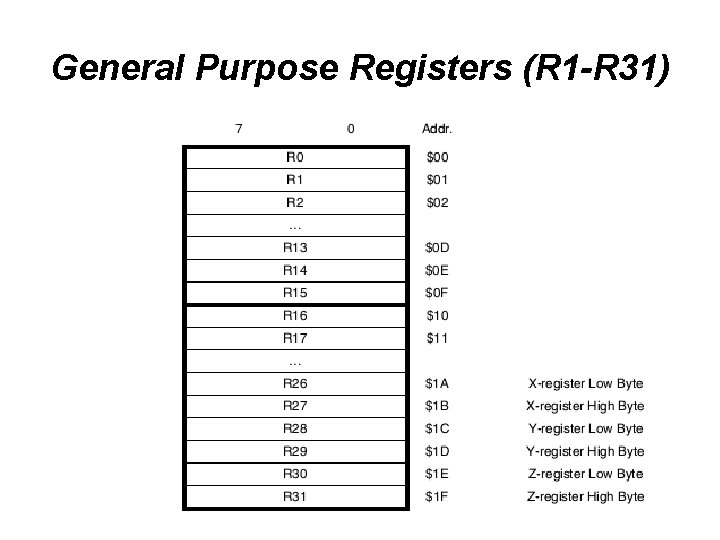

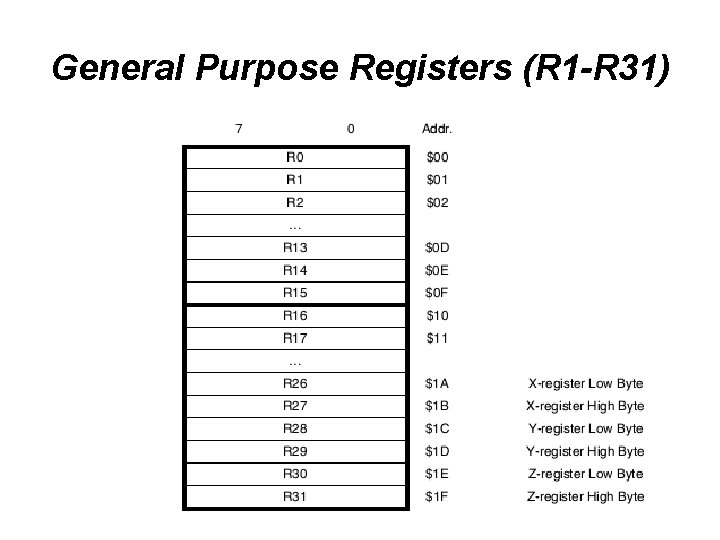

General Purpose Registers (R 1 -R 31)

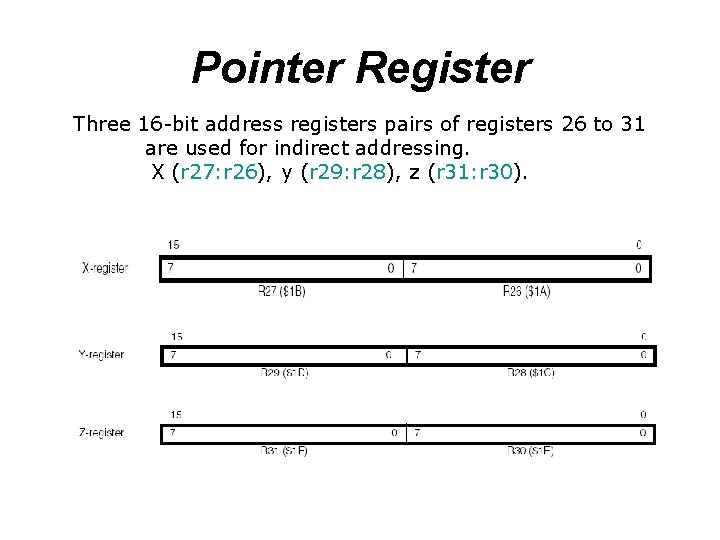

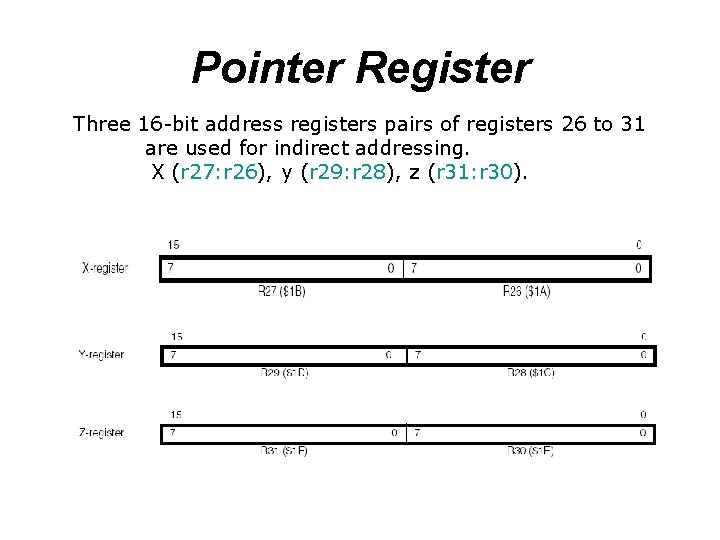

Pointer Register Three 16 -bit address registers pairs of registers 26 to 31 are used for indirect addressing. X (r 27: r 26), y (r 29: r 28), z (r 31: r 30).

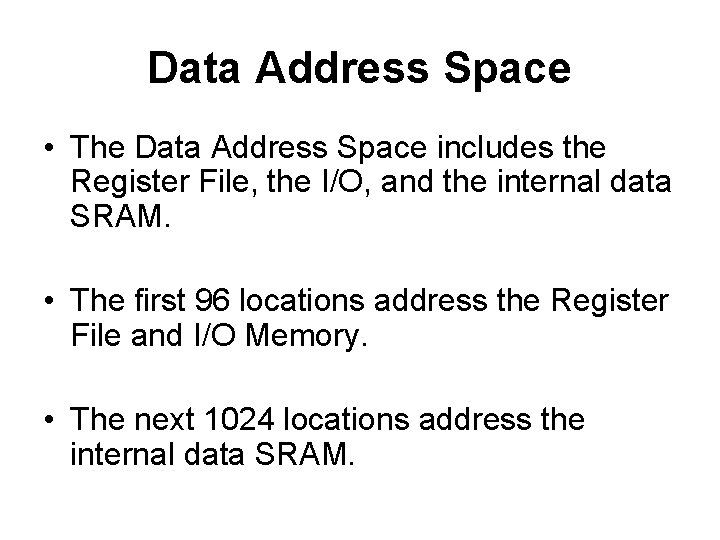

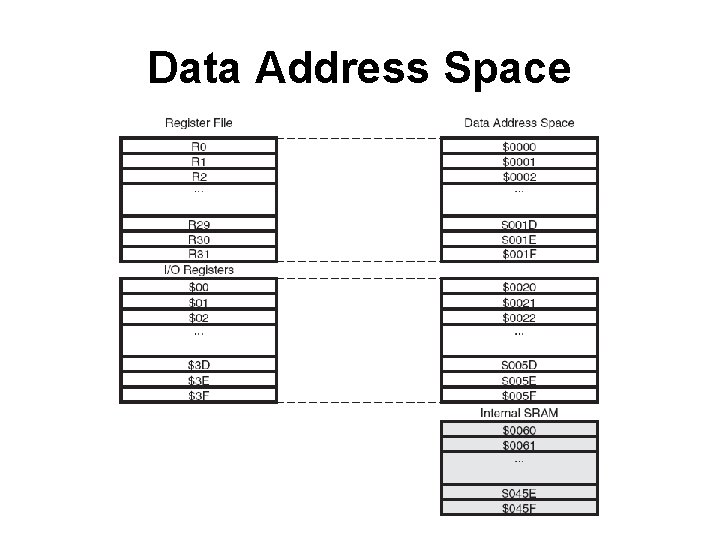

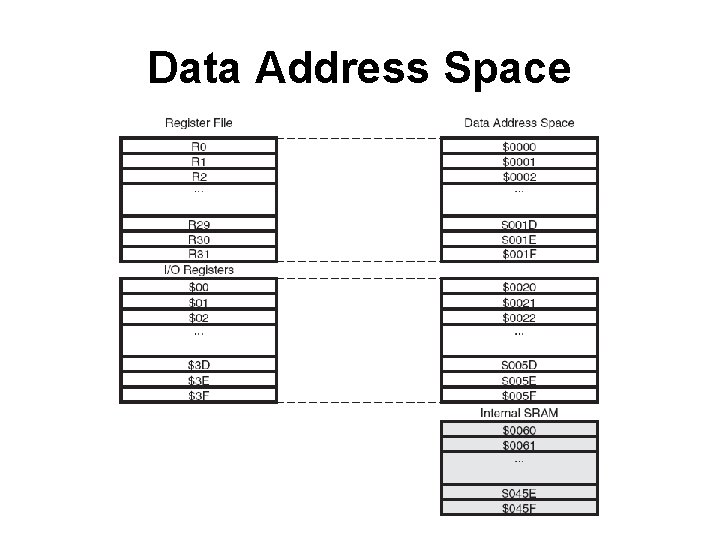

Data Address Space • The Data Address Space includes the Register File, the I/O, and the internal data SRAM. • The first 96 locations address the Register File and I/O Memory. • The next 1024 locations address the internal data SRAM.

Data Address Space

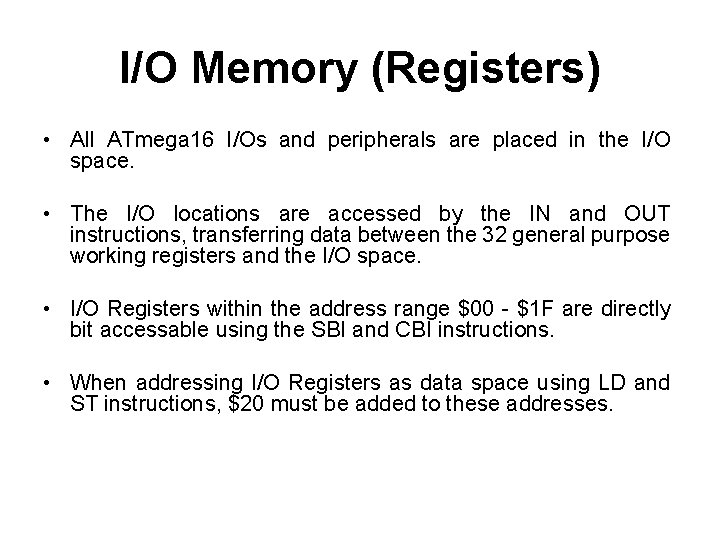

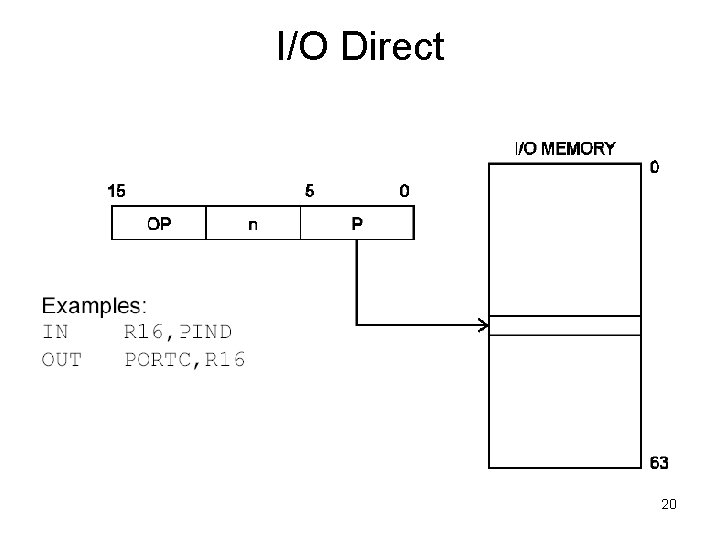

I/O Memory (Registers) • All ATmega 16 I/Os and peripherals are placed in the I/O space. • The I/O locations are accessed by the IN and OUT instructions, transferring data between the 32 general purpose working registers and the I/O space. • I/O Registers within the address range $00 - $1 F are directly bit accessable using the SBI and CBI instructions. • When addressing I/O Registers as data space using LD and ST instructions, $20 must be added to these addresses.

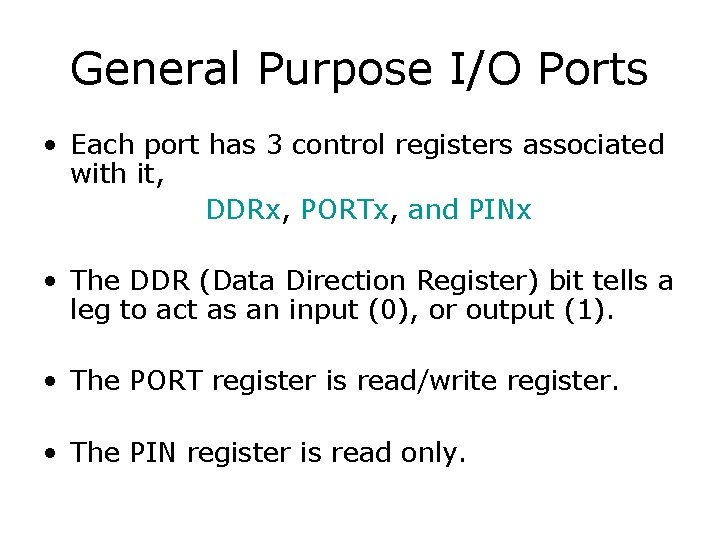

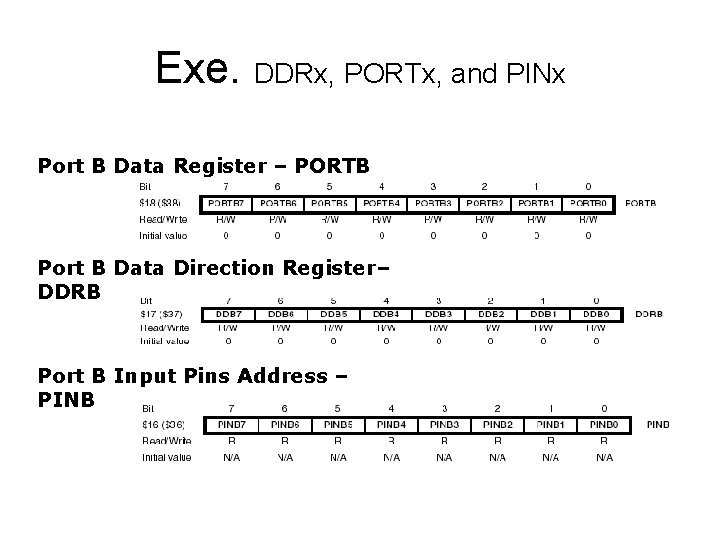

General Purpose I/O Ports • Each port has 3 control registers associated with it, DDRx, PORTx, and PINx • The DDR (Data Direction Register) bit tells a leg to act as an input (0), or output (1). • The PORT register is read/write register. • The PIN register is read only.

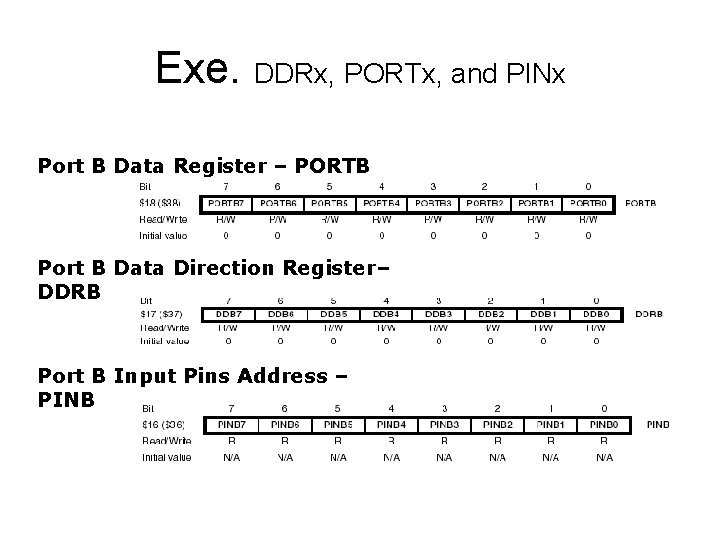

Exe. DDRx, PORTx, and PINx Port B Data Register – PORTB Port B Data Direction Register– DDRB Port B Input Pins Address – PINB

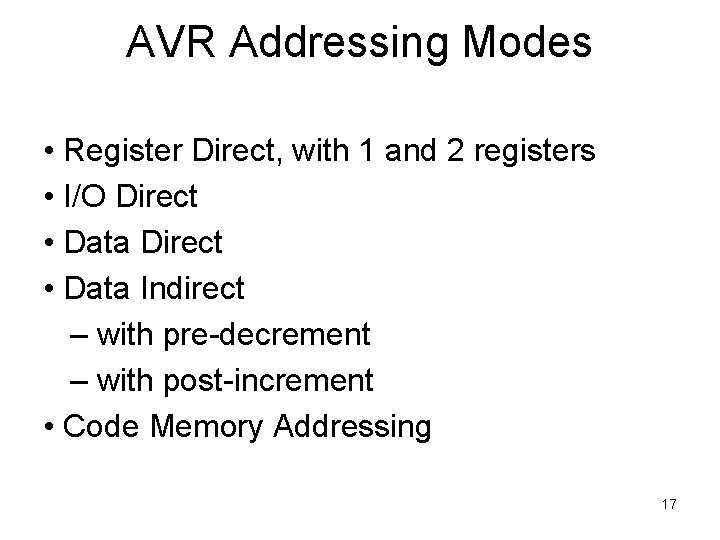

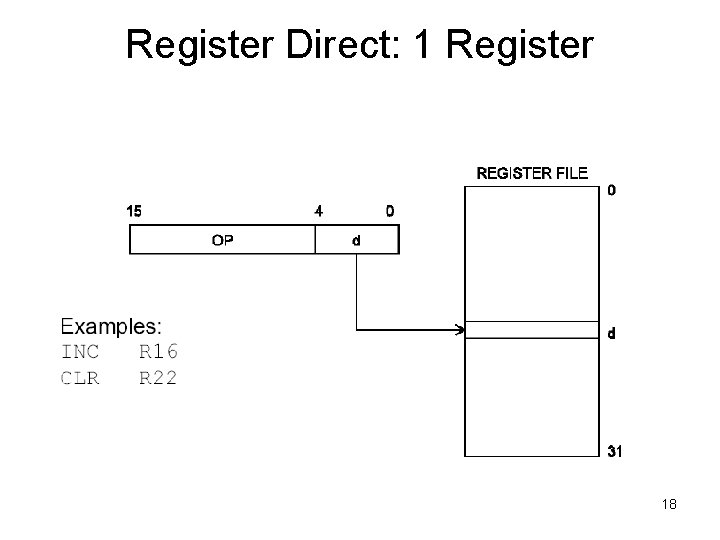

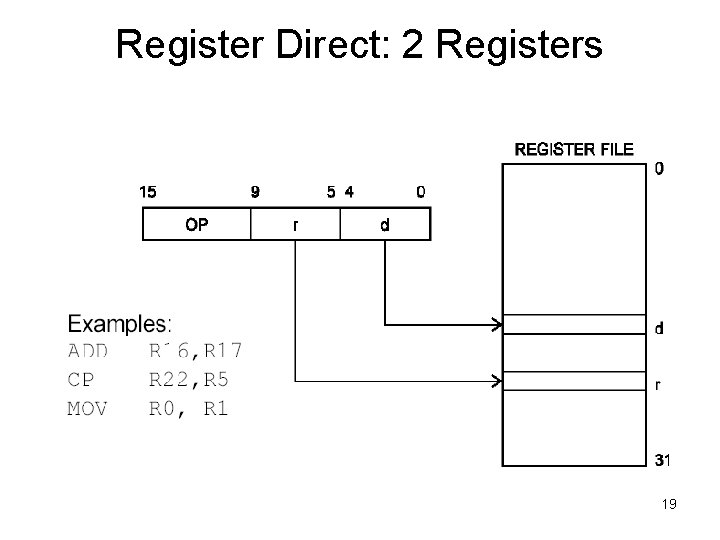

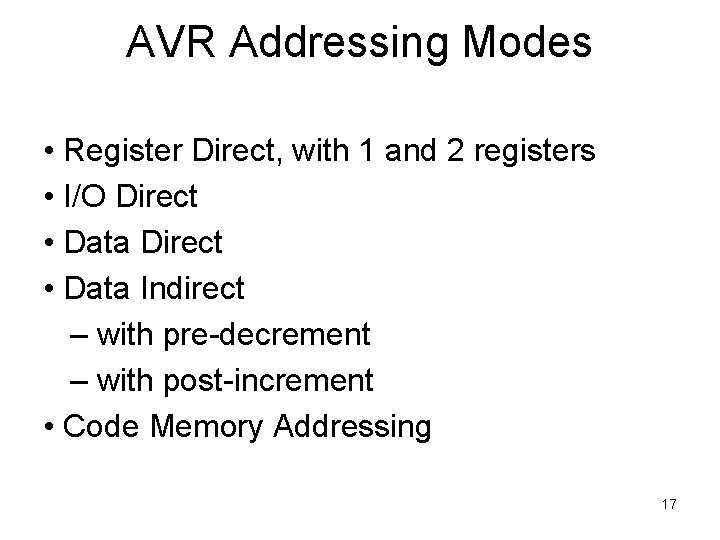

AVR Addressing Modes • Register Direct, with 1 and 2 registers • I/O Direct • Data Indirect – with pre-decrement – with post-increment • Code Memory Addressing 17

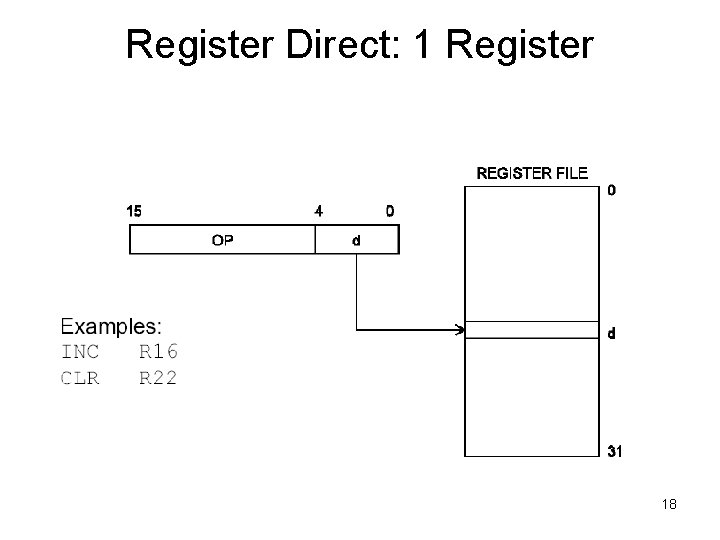

Register Direct: 1 Register 18

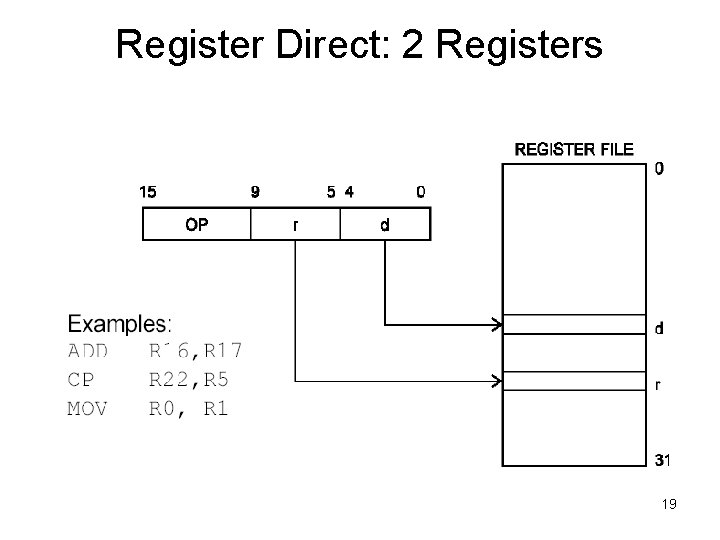

Register Direct: 2 Registers 19

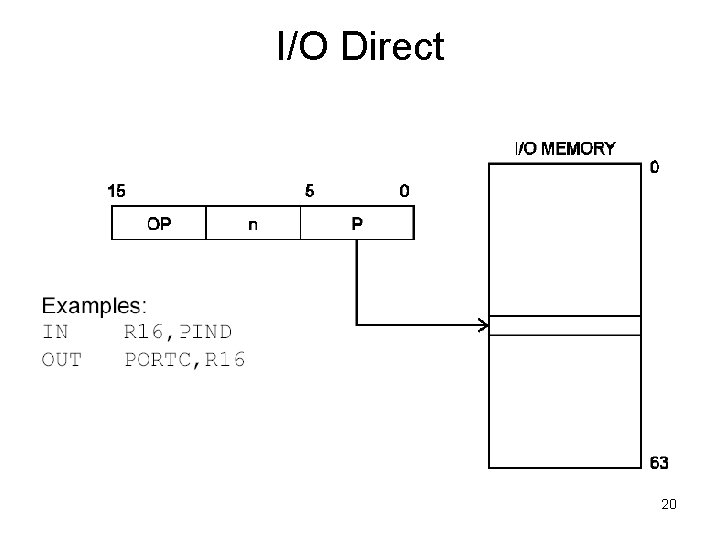

I/O Direct 20

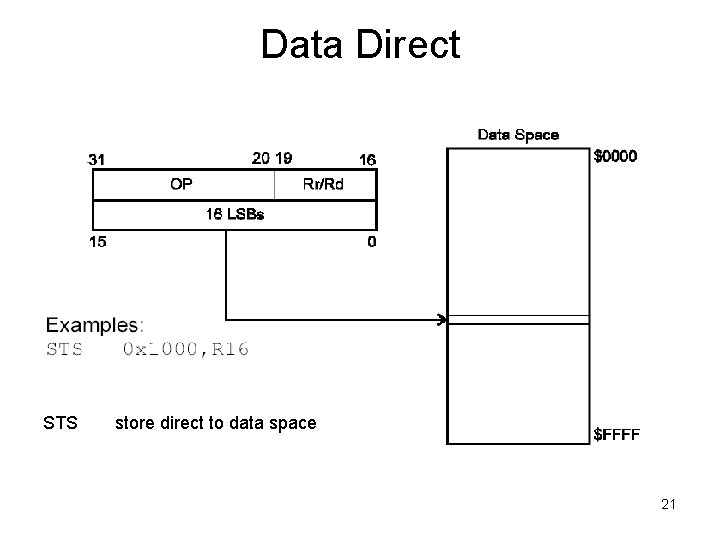

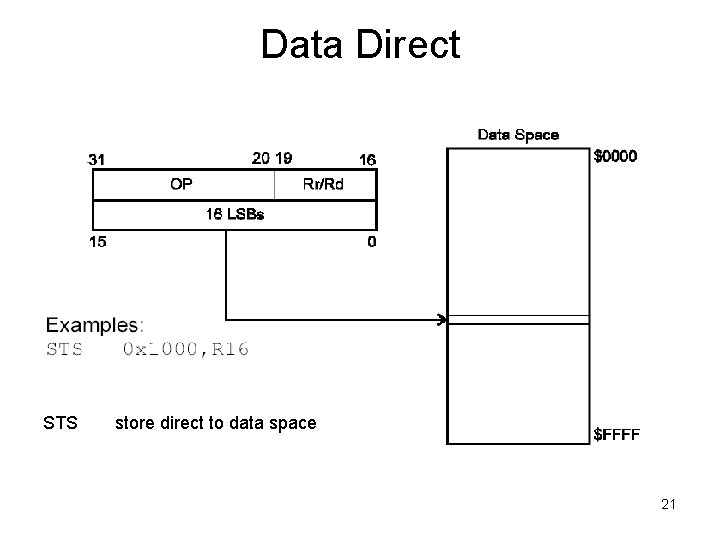

Data Direct STS store direct to data space 21

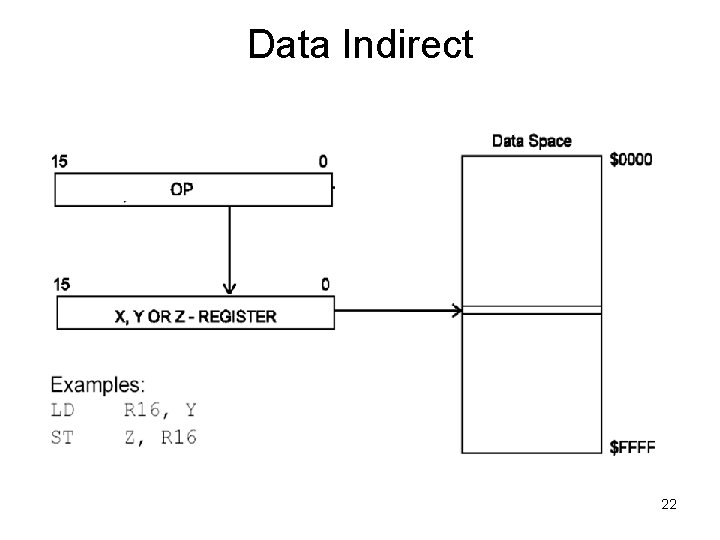

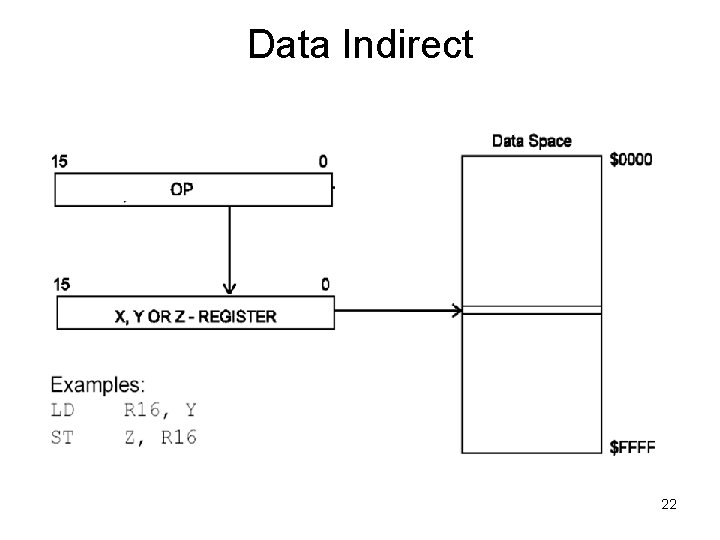

Data Indirect 22

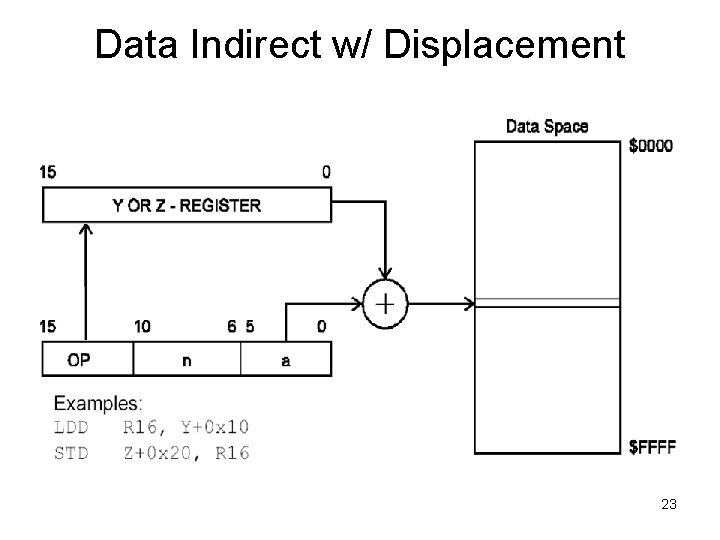

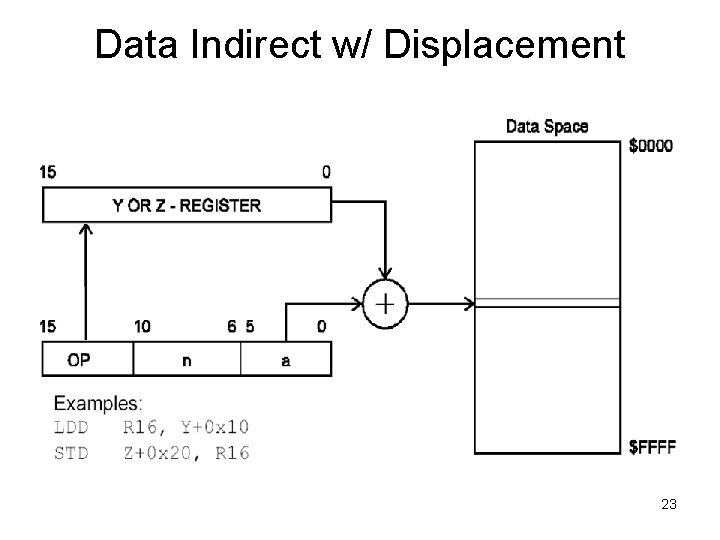

Data Indirect w/ Displacement 23

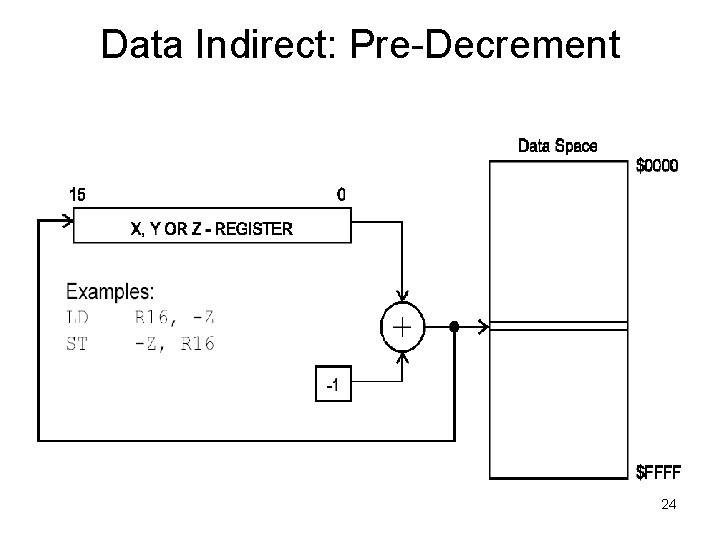

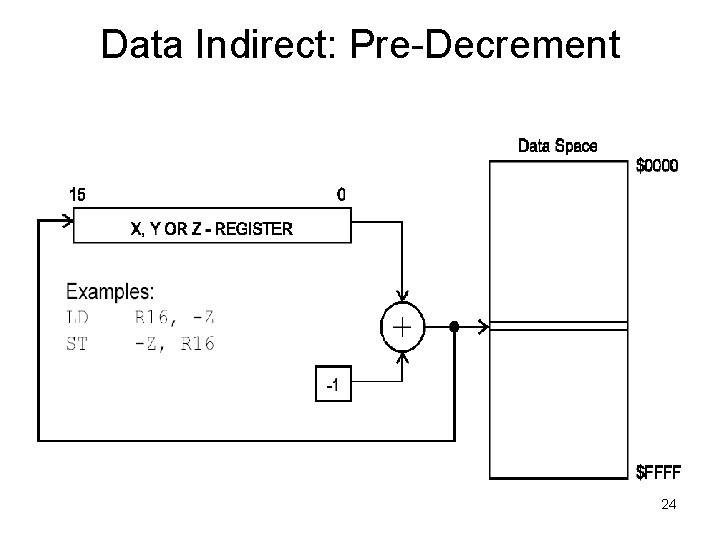

Data Indirect: Pre-Decrement 24

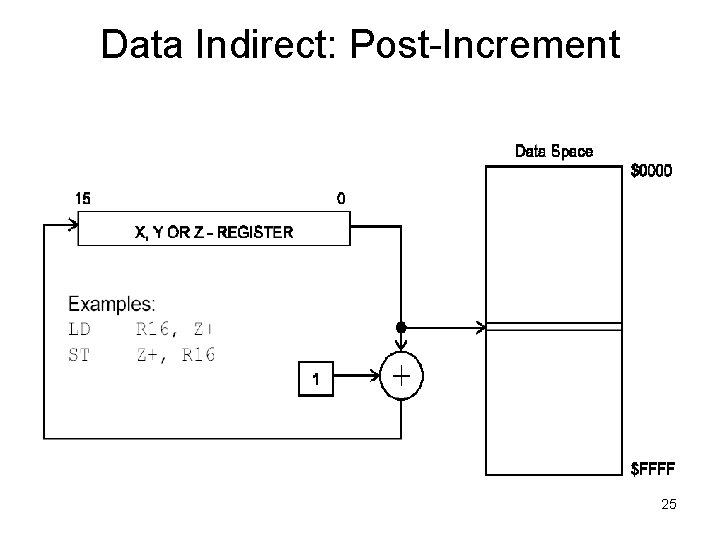

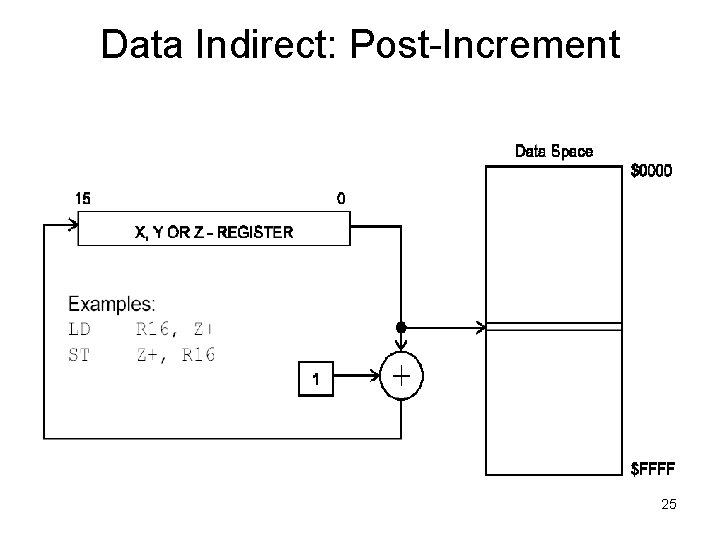

Data Indirect: Post-Increment 25

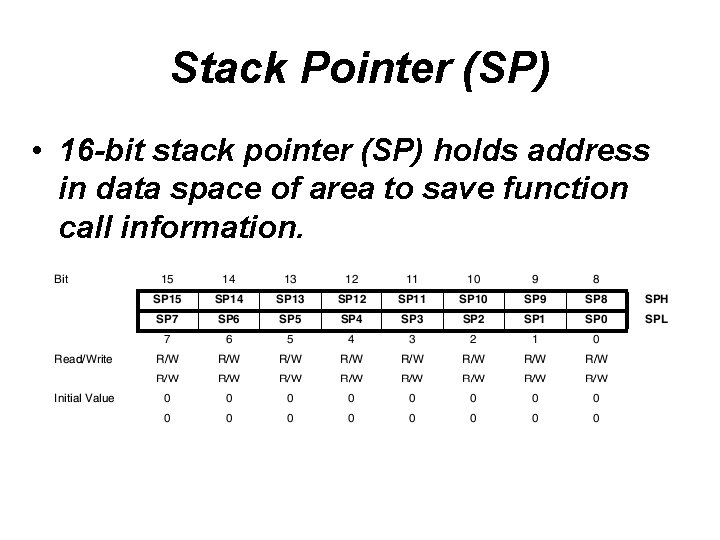

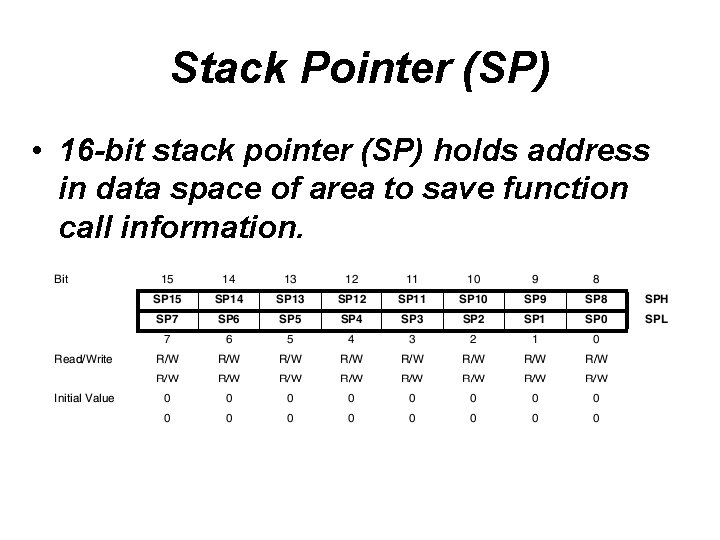

Stack Pointer (SP) • 16 -bit stack pointer (SP) holds address in data space of area to save function call information.

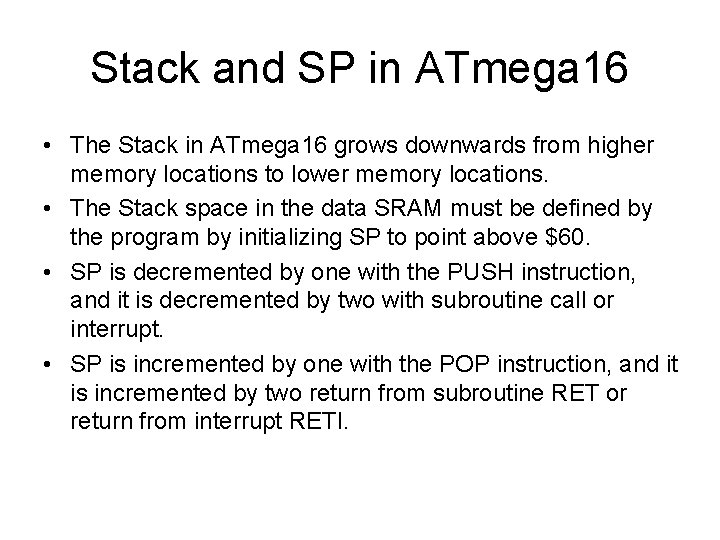

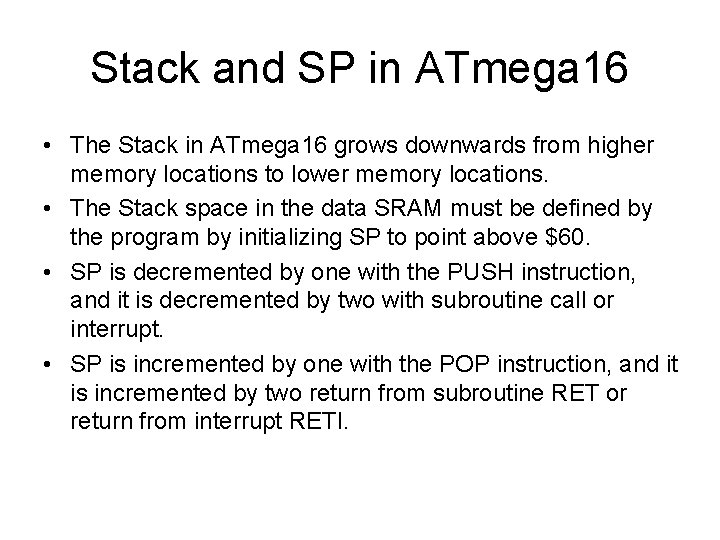

Stack and SP in ATmega 16 • The Stack in ATmega 16 grows downwards from higher memory locations to lower memory locations. • The Stack space in the data SRAM must be defined by the program by initializing SP to point above $60. • SP is decremented by one with the PUSH instruction, and it is decremented by two with subroutine call or interrupt. • SP is incremented by one with the POP instruction, and it is incremented by two return from subroutine RET or return from interrupt RETI.

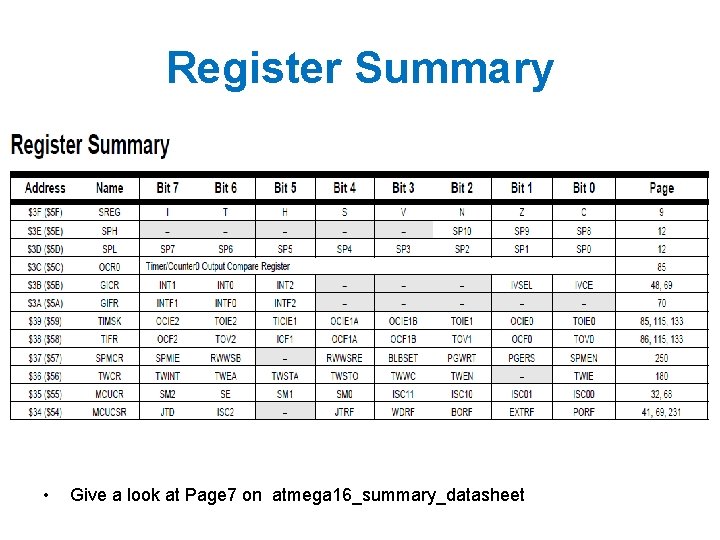

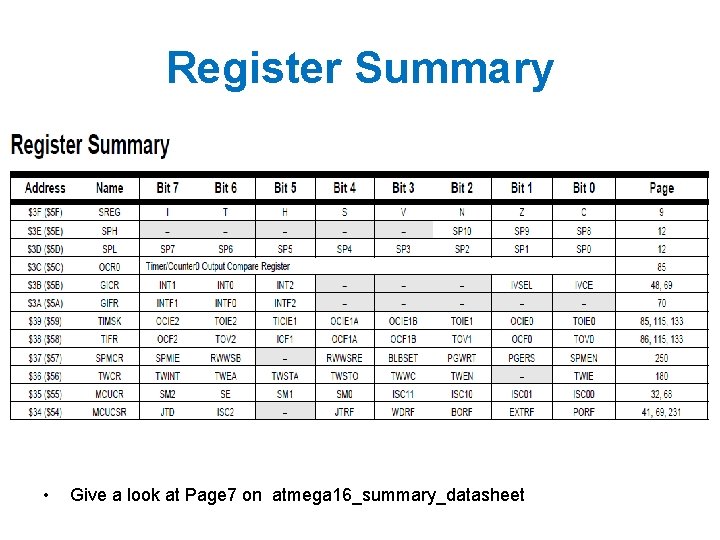

Register Summary • Give a look at Page 7 on atmega 16_summary_datasheet

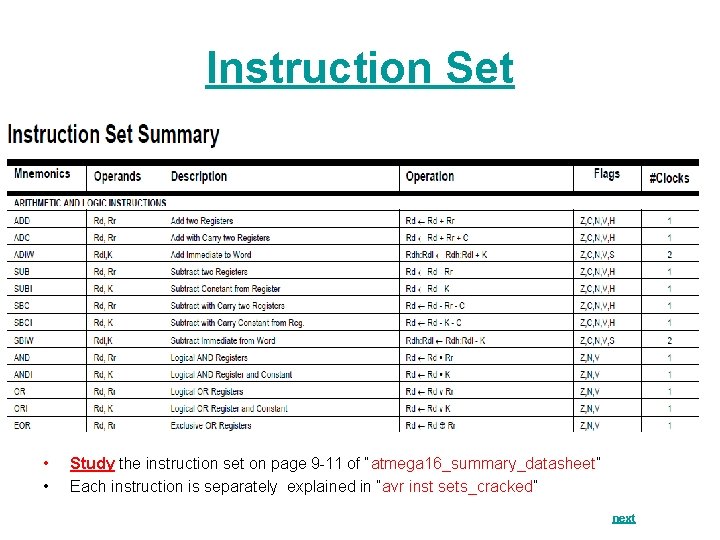

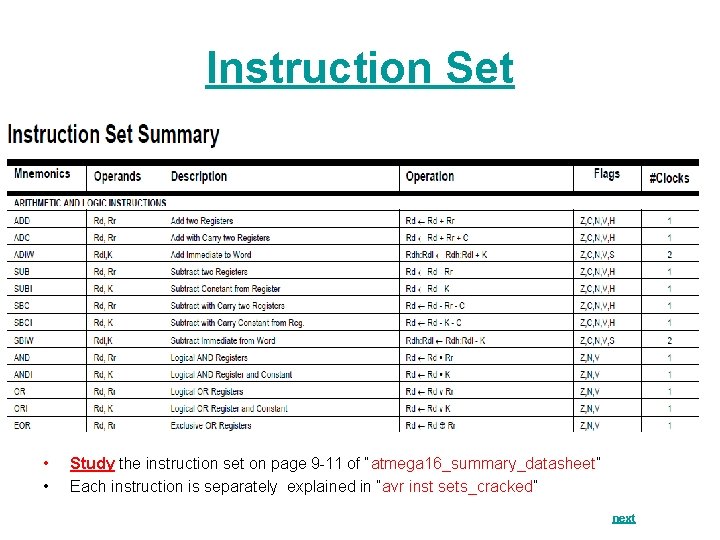

Instruction Set • • Study the instruction set on page 9 -11 of “atmega 16_summary_datasheet” Each instruction is separately explained in “avr inst sets_cracked” next

• Next slides are for self study 30

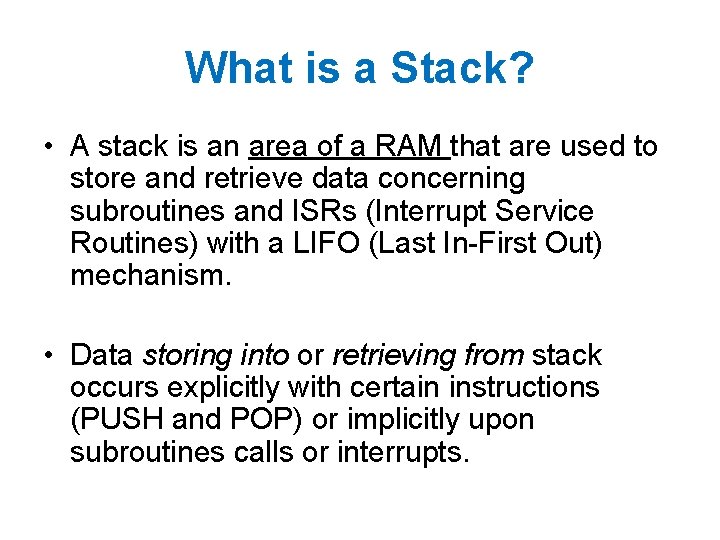

What is a Stack? • A stack is an area of a RAM that are used to store and retrieve data concerning subroutines and ISRs (Interrupt Service Routines) with a LIFO (Last In-First Out) mechanism. • Data storing into or retrieving from stack occurs explicitly with certain instructions (PUSH and POP) or implicitly upon subroutines calls or interrupts.

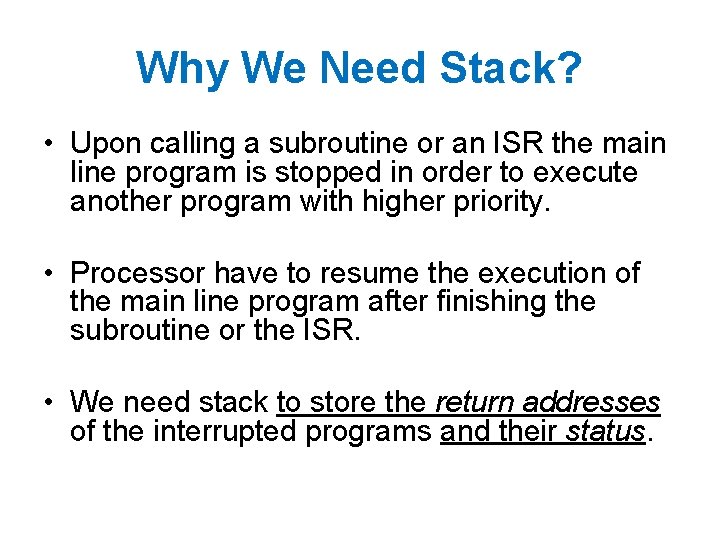

Why We Need Stack? • Upon calling a subroutine or an ISR the main line program is stopped in order to execute another program with higher priority. • Processor have to resume the execution of the main line program after finishing the subroutine or the ISR. • We need stack to store the return addresses of the interrupted programs and their status.

What happens Upon Calling a Subroutine or ISR? • Upon interrupting a program, the following actions take place: – Address of the next instruction of the interrupted program (contents of the PC register) is stored into stack. – Intermediate results (in registers and RAM) of the interrupted program are stored into stack. – Address of the subroutine or ISR (Vector address) is loaded into PC register.

How Subroutine and ISR are launched • Subroutines are launched by CALL instructions written by the programmer (software launching). • Interrupt Service Routines are often launched by signals that come from outside or inside the processor chip(hardware launching). • A programmer can launch an ISR by software with certain instructions (8086 exp. INT 21 H).

Storing and Retrieving in/from the Stack • There is a special register called stack pointer (SP) that used to address the stack when there is a store or retrieve operation. • The stack pointer SP always points to the last used location of the stack. It is updated automatically upon each stack operation so that data is stored and retrieved with a LIFO (Last In First Out) mechanism. • Storing data into stack is called a PUSHING while retrieving data from stack is called POPPING.

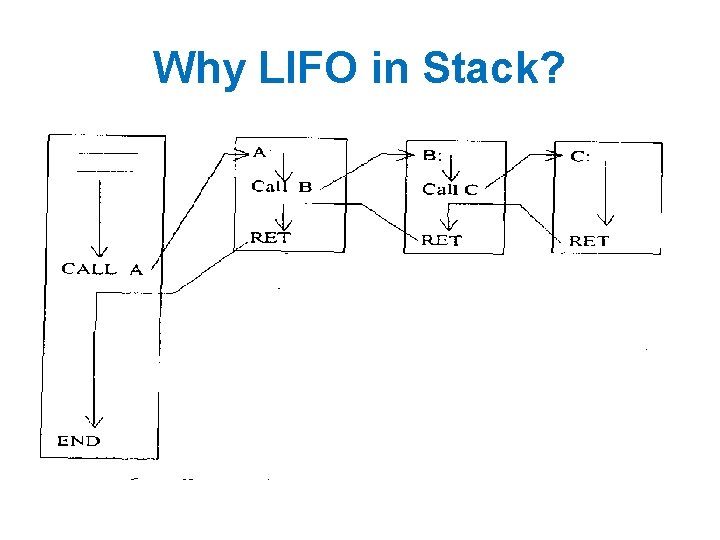

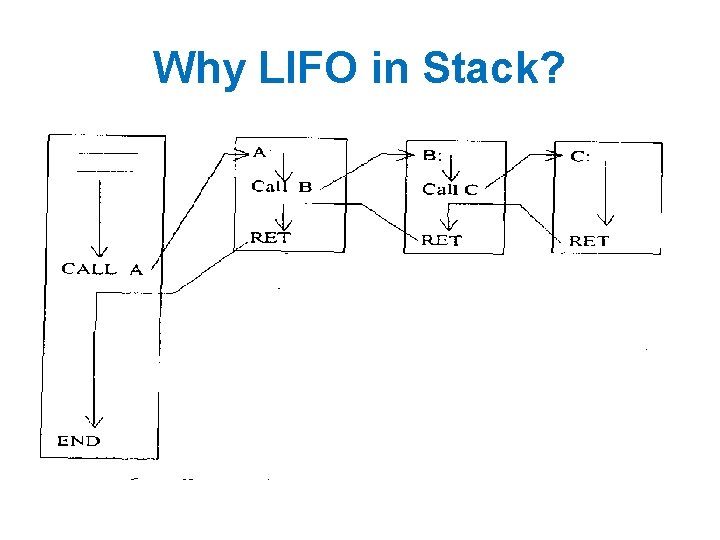

Why LIFO in Stack? • LIFO principle is used in stack because we need a LIFO mechanism to resume a nest of interrupted programs. • At the end of each subroutine or ISR there must be a special instruction (exp. RET or IRET) that load the program counter with the return address to resume execution of the interrupted program.

Why LIFO in Stack?