Lecture 19 OUTLINE Commongate stage Source follower Reading

- Slides: 15

Lecture 19 OUTLINE • Common-gate stage • Source follower Reading: Chapter 7. 3 -7. 4 EE 105 Fall 2007 Lecture 19, Slide 1 Prof. Liu, UC Berkeley

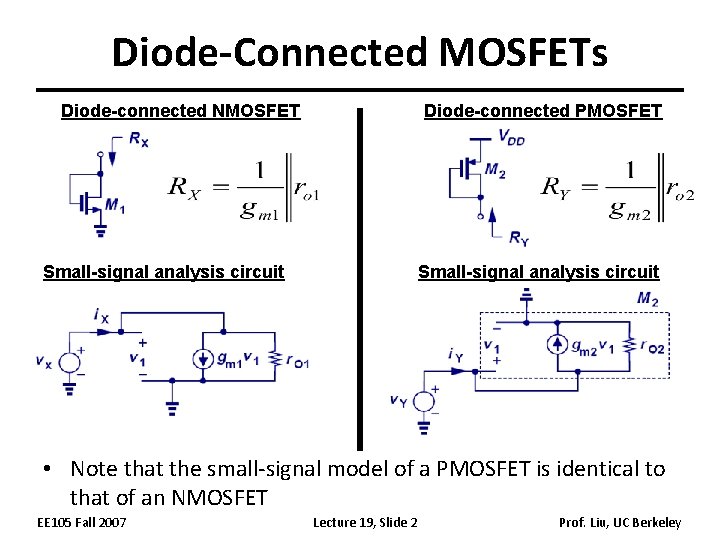

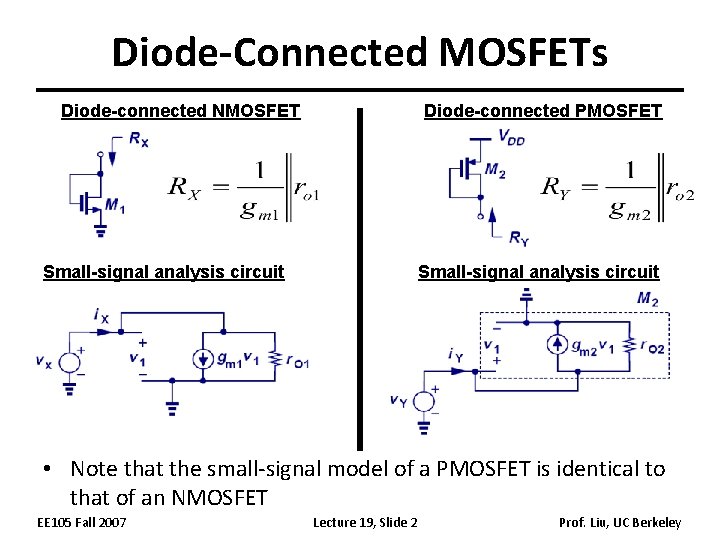

Diode-Connected MOSFETs Diode-connected NMOSFET Diode-connected PMOSFET Small-signal analysis circuit • Note that the small-signal model of a PMOSFET is identical to that of an NMOSFET EE 105 Fall 2007 Lecture 19, Slide 2 Prof. Liu, UC Berkeley

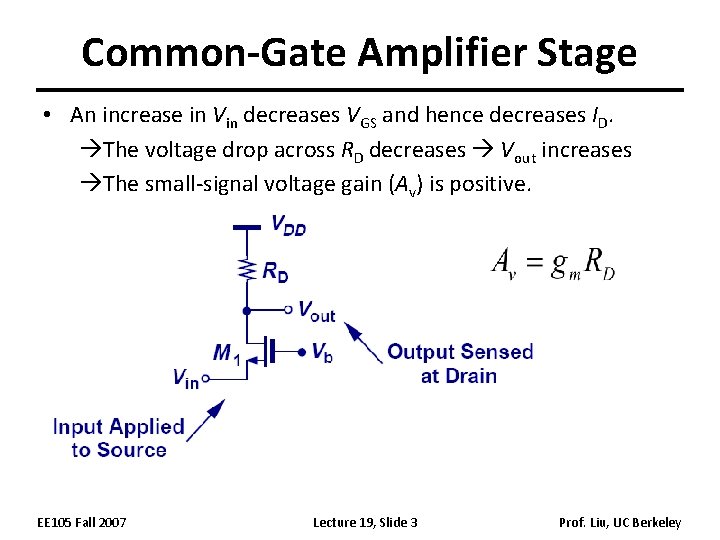

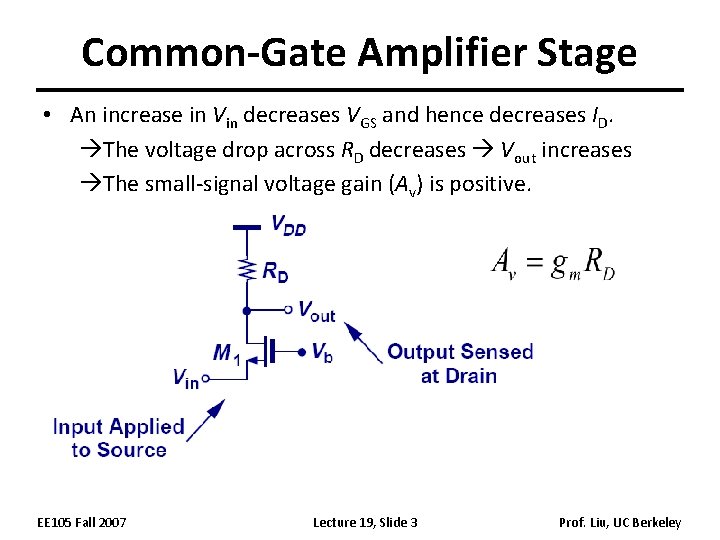

Common-Gate Amplifier Stage • An increase in Vin decreases VGS and hence decreases ID. The voltage drop across RD decreases Vout increases The small-signal voltage gain (Av) is positive. EE 105 Fall 2007 Lecture 19, Slide 3 Prof. Liu, UC Berkeley

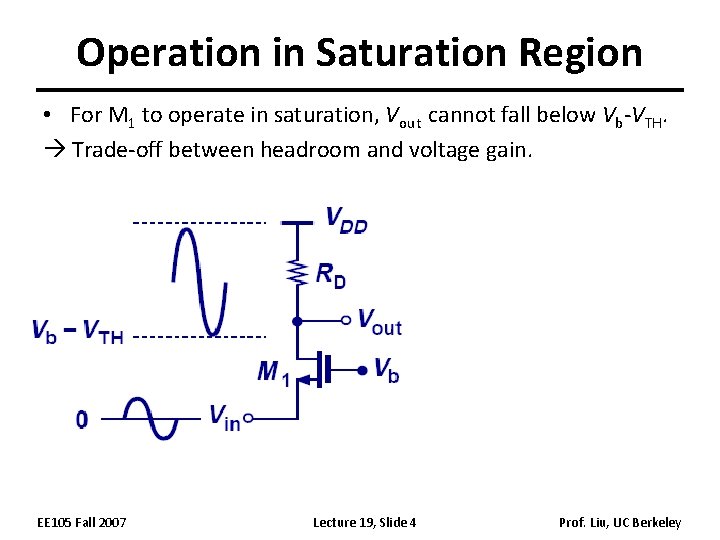

Operation in Saturation Region • For M 1 to operate in saturation, Vout cannot fall below Vb-VTH. Trade-off between headroom and voltage gain. EE 105 Fall 2007 Lecture 19, Slide 4 Prof. Liu, UC Berkeley

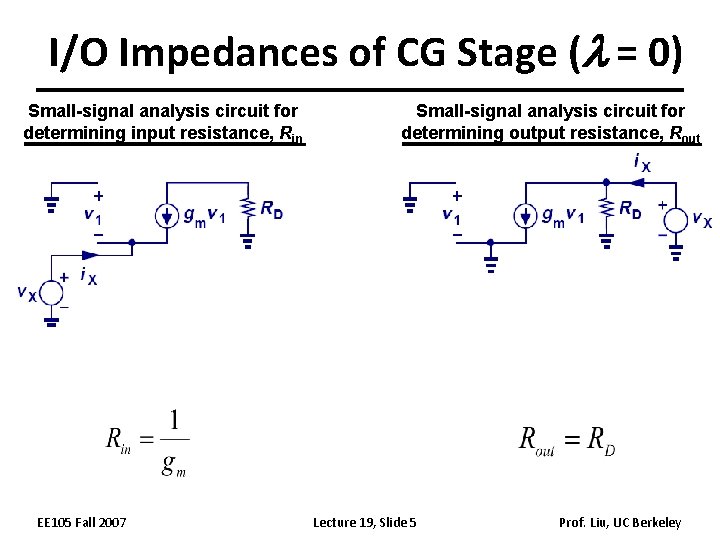

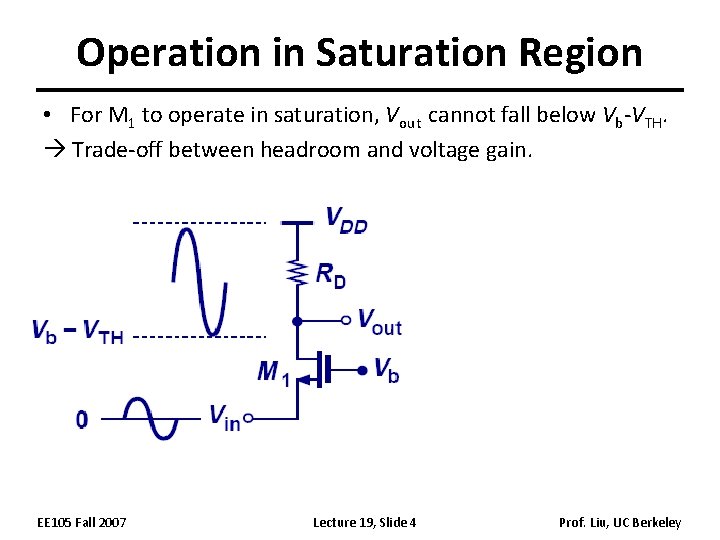

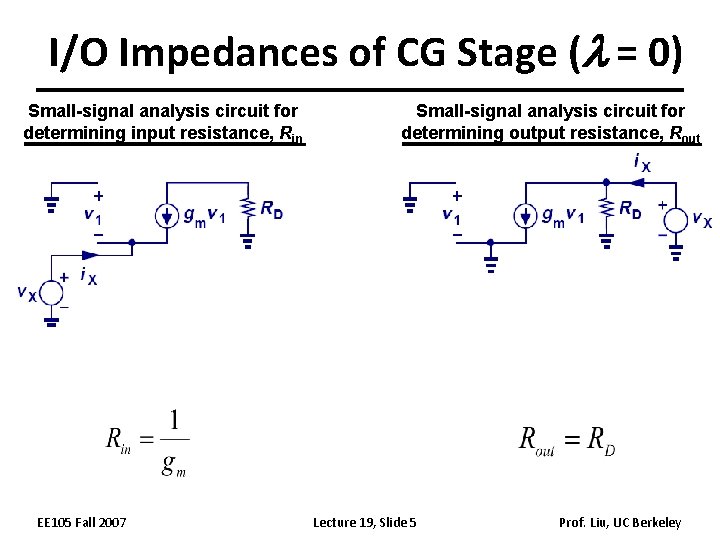

I/O Impedances of CG Stage (l = 0) Small-signal analysis circuit for determining input resistance, Rin EE 105 Fall 2007 Small-signal analysis circuit for determining output resistance, Rout Lecture 19, Slide 5 Prof. Liu, UC Berkeley

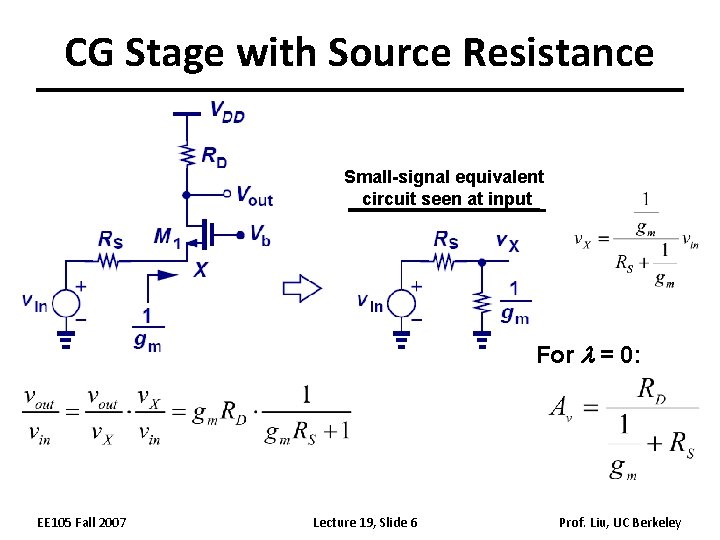

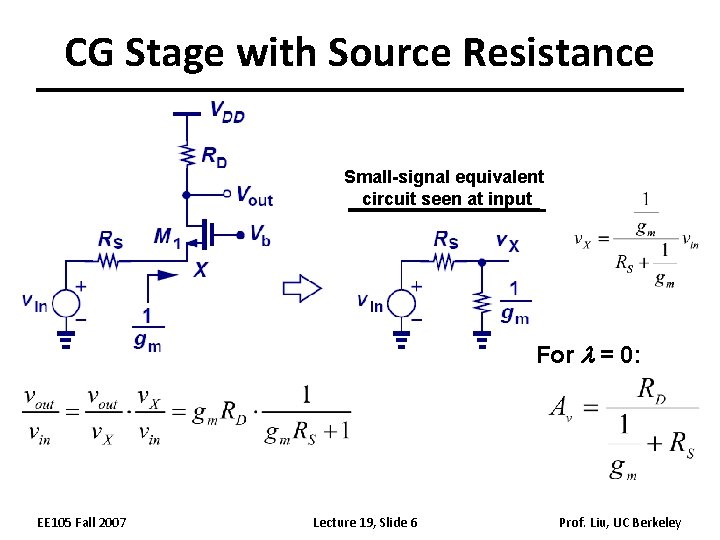

CG Stage with Source Resistance Small-signal equivalent circuit seen at input For l = 0: EE 105 Fall 2007 Lecture 19, Slide 6 Prof. Liu, UC Berkeley

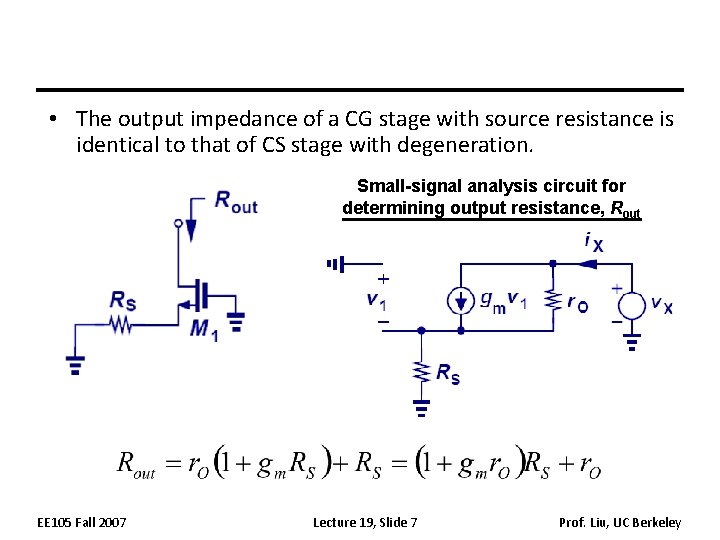

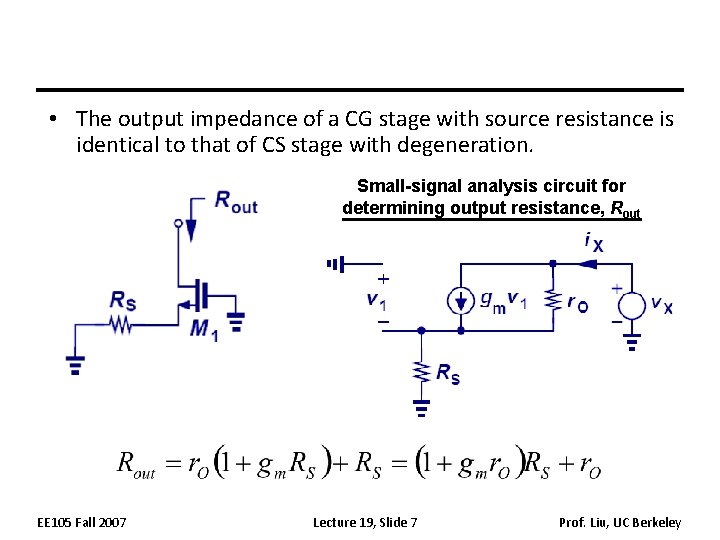

• The output impedance of a CG stage with source resistance is identical to that of CS stage with degeneration. Small-signal analysis circuit for determining output resistance, Rout EE 105 Fall 2007 Lecture 19, Slide 7 Prof. Liu, UC Berkeley

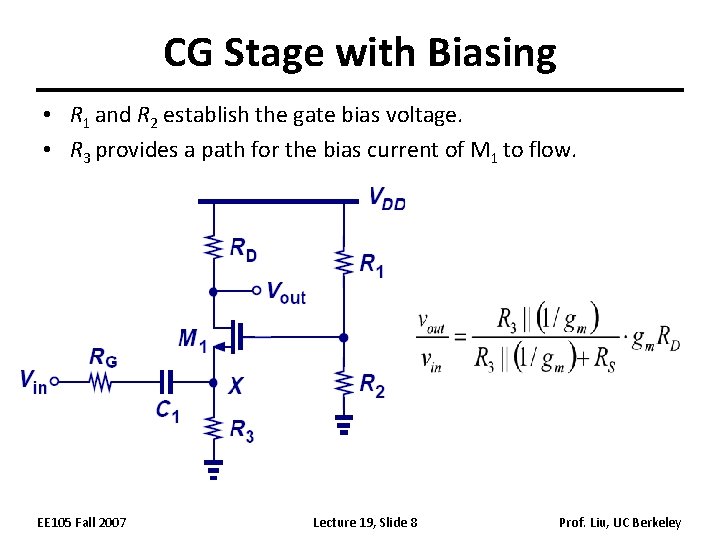

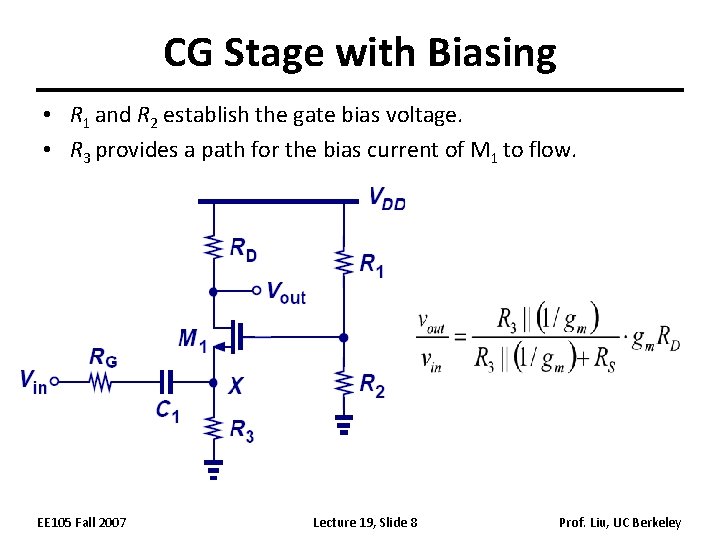

CG Stage with Biasing • R 1 and R 2 establish the gate bias voltage. • R 3 provides a path for the bias current of M 1 to flow. EE 105 Fall 2007 Lecture 19, Slide 8 Prof. Liu, UC Berkeley

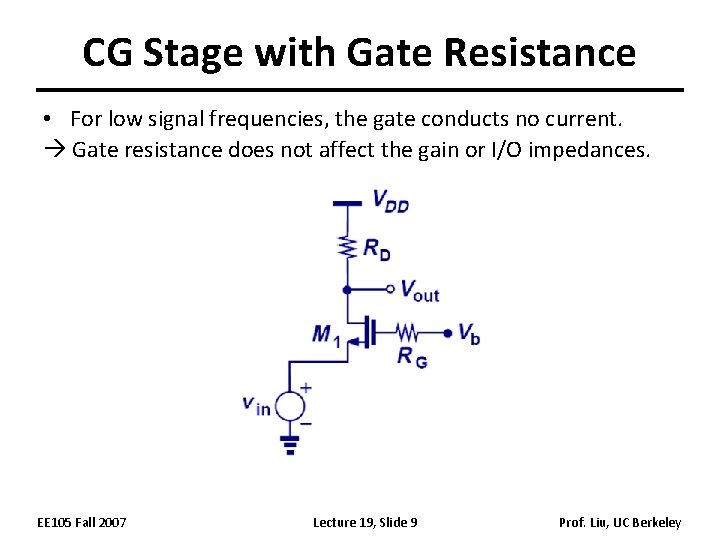

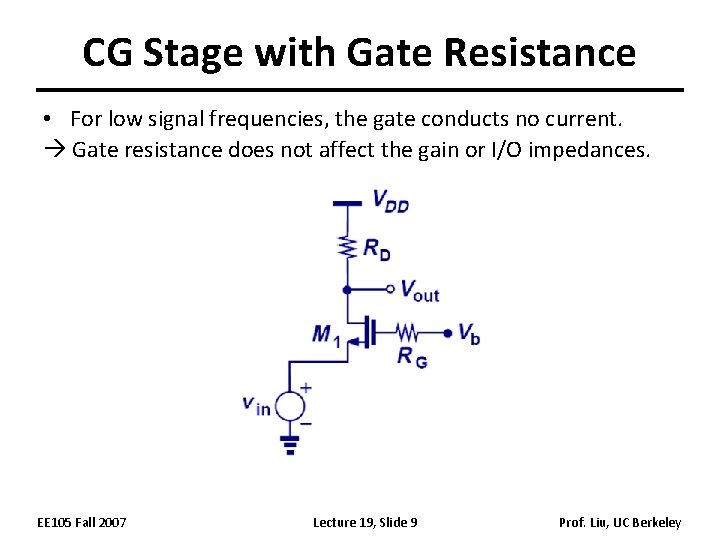

CG Stage with Gate Resistance • For low signal frequencies, the gate conducts no current. Gate resistance does not affect the gain or I/O impedances. EE 105 Fall 2007 Lecture 19, Slide 9 Prof. Liu, UC Berkeley

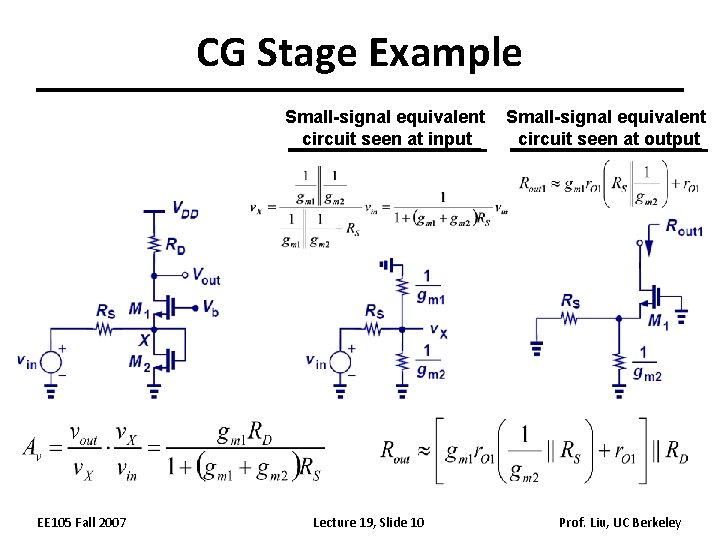

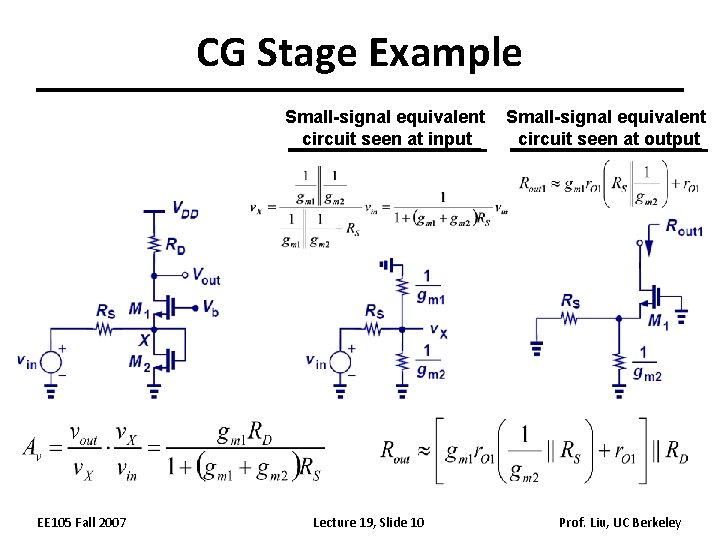

CG Stage Example Small-signal equivalent circuit seen at input EE 105 Fall 2007 Lecture 19, Slide 10 Small-signal equivalent circuit seen at output Prof. Liu, UC Berkeley

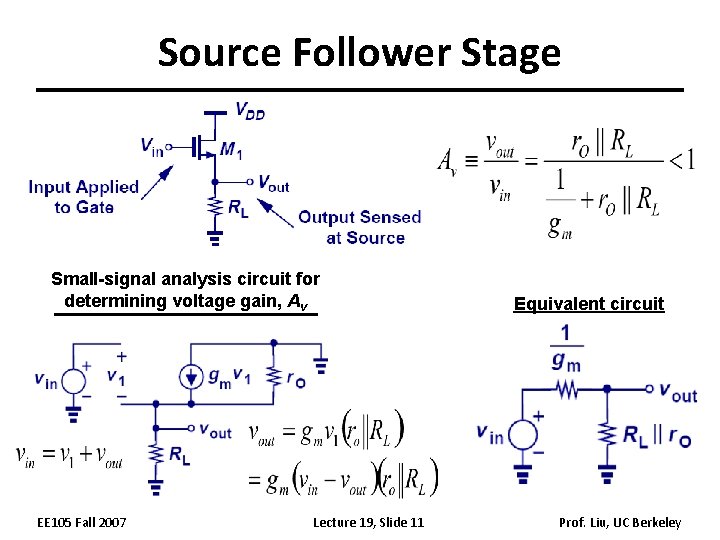

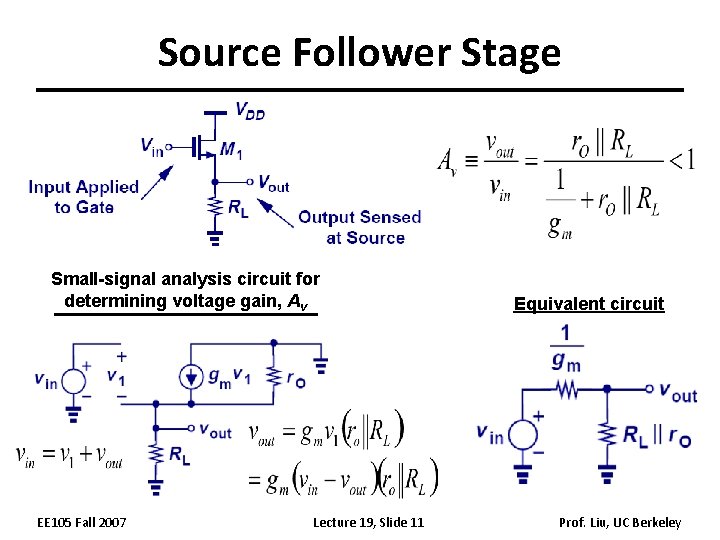

Source Follower Stage Small-signal analysis circuit for determining voltage gain, Av EE 105 Fall 2007 Lecture 19, Slide 11 Equivalent circuit Prof. Liu, UC Berkeley

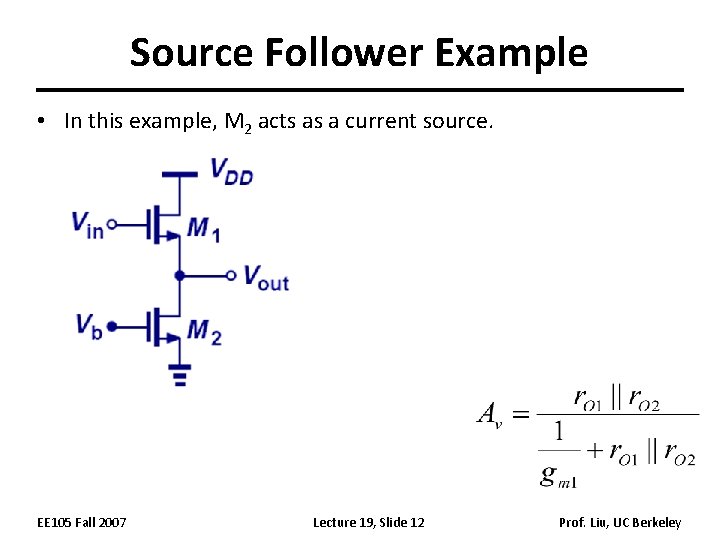

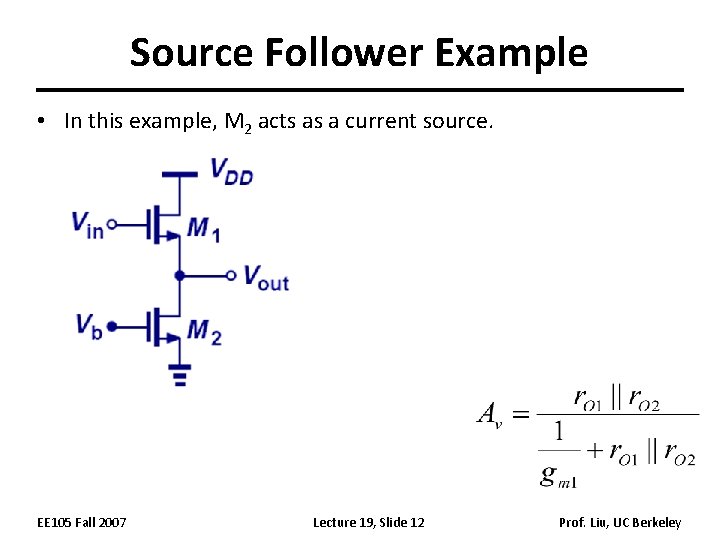

Source Follower Example • In this example, M 2 acts as a current source. EE 105 Fall 2007 Lecture 19, Slide 12 Prof. Liu, UC Berkeley

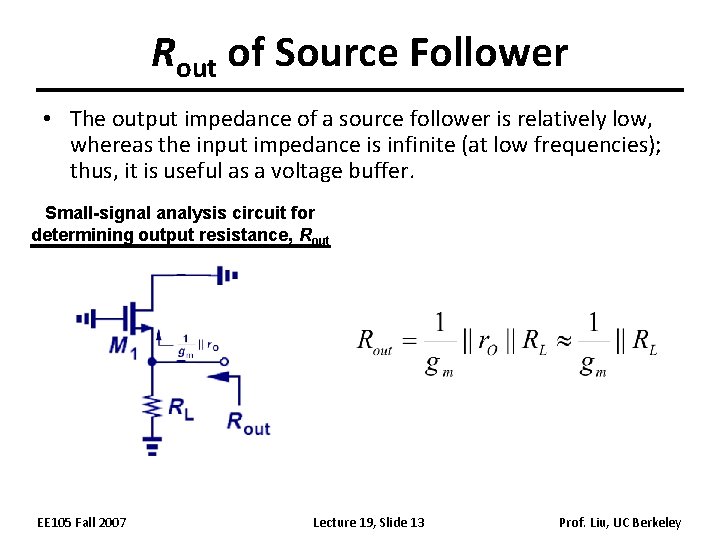

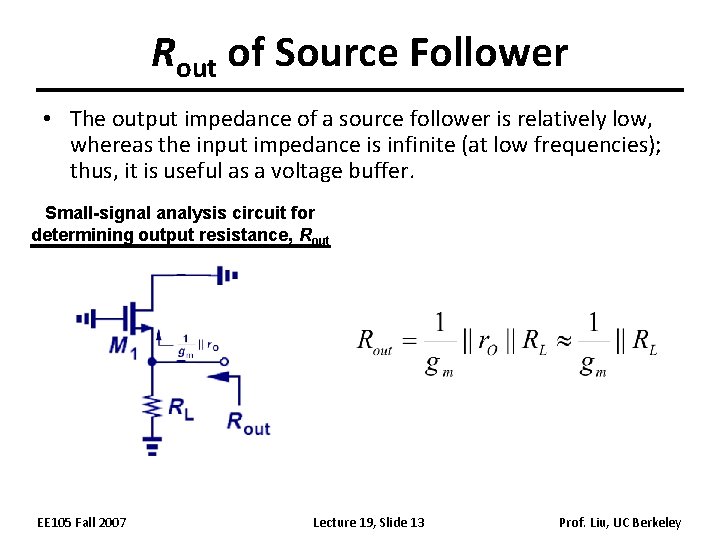

Rout of Source Follower • The output impedance of a source follower is relatively low, whereas the input impedance is infinite (at low frequencies); thus, it is useful as a voltage buffer. Small-signal analysis circuit for determining output resistance, Rout EE 105 Fall 2007 Lecture 19, Slide 13 Prof. Liu, UC Berkeley

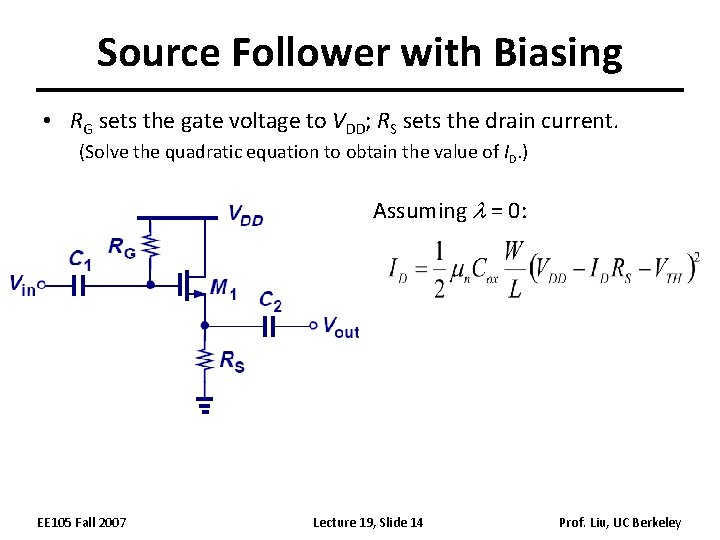

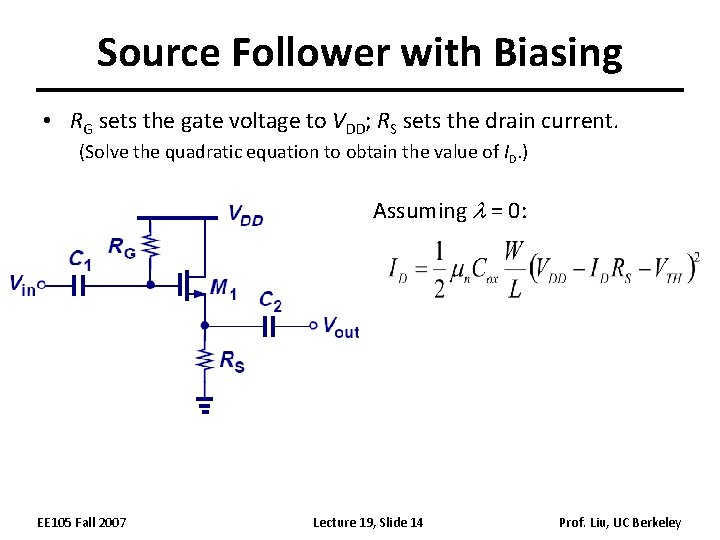

Source Follower with Biasing • RG sets the gate voltage to VDD; RS sets the drain current. (Solve the quadratic equation to obtain the value of ID. ) Assuming l = 0: EE 105 Fall 2007 Lecture 19, Slide 14 Prof. Liu, UC Berkeley

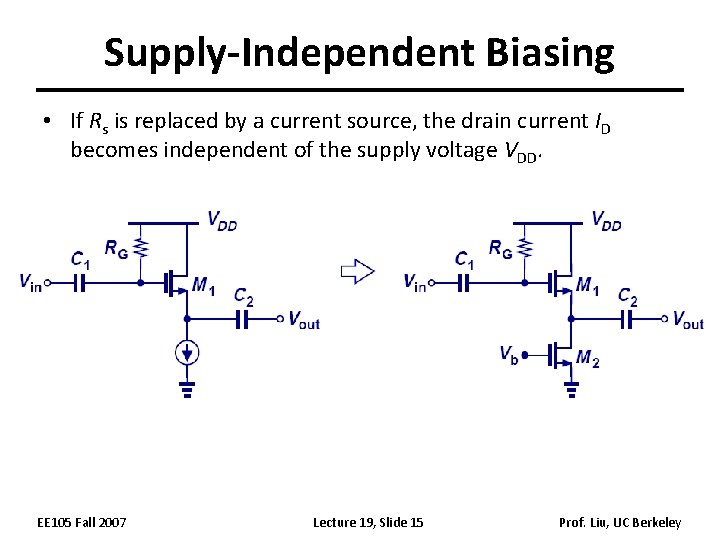

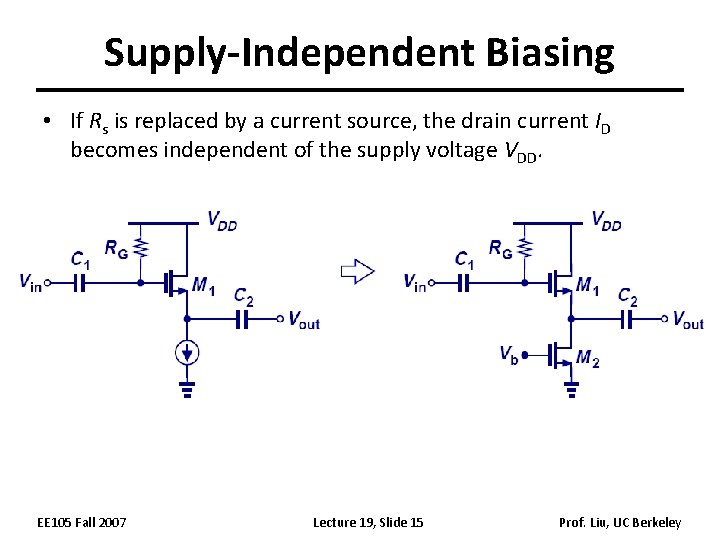

Supply-Independent Biasing • If Rs is replaced by a current source, the drain current ID becomes independent of the supply voltage VDD. EE 105 Fall 2007 Lecture 19, Slide 15 Prof. Liu, UC Berkeley