Lecture 18 OUTLINE The MOS Capacitor contd Effect

- Slides: 17

Lecture 18 OUTLINE • The MOS Capacitor (cont’d) – Effect of oxide charges – Poly-Si gate depletion effect – VT adjustment Reading: Pierret 18. 2 -18. 3; Hu 5. 7 -5. 9

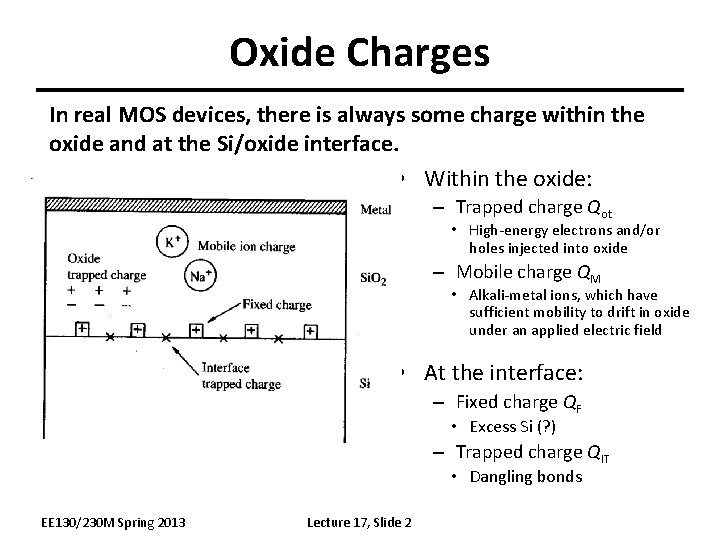

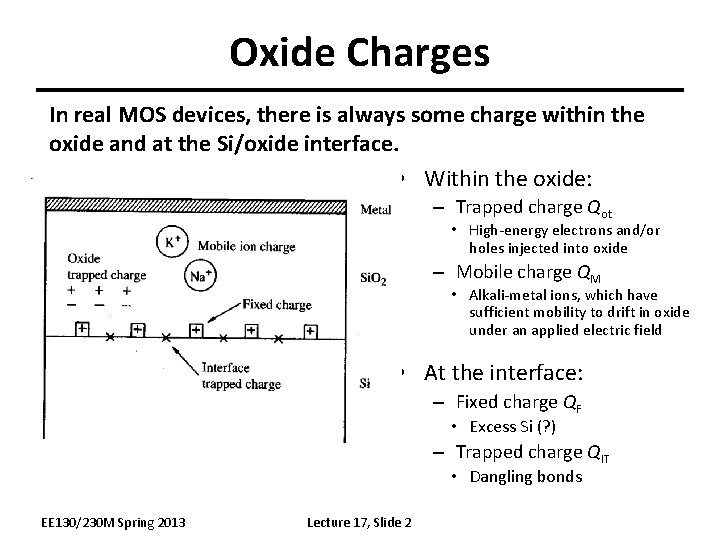

Oxide Charges In real MOS devices, there is always some charge within the oxide and at the Si/oxide interface. • Within the oxide: – Trapped charge Qot • High-energy electrons and/or holes injected into oxide – Mobile charge QM • Alkali-metal ions, which have sufficient mobility to drift in oxide under an applied electric field • At the interface: – Fixed charge QF • Excess Si (? ) – Trapped charge QIT • Dangling bonds EE 130/230 M Spring 2013 Lecture 17, Slide 2

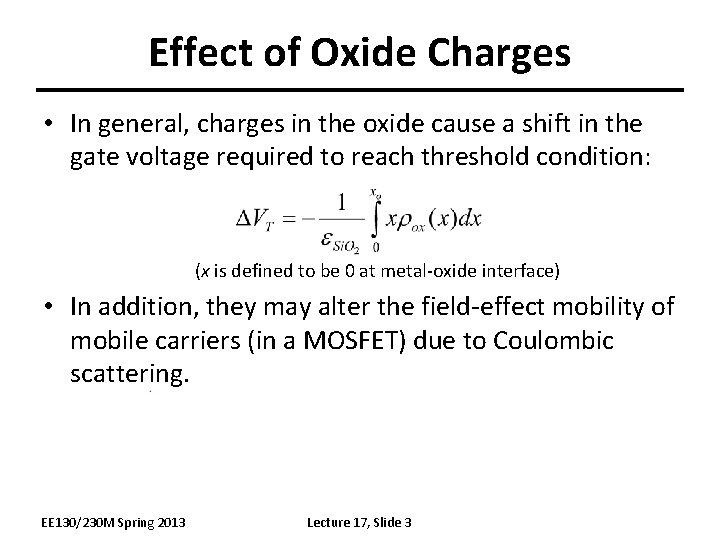

Effect of Oxide Charges • In general, charges in the oxide cause a shift in the gate voltage required to reach threshold condition: (x is defined to be 0 at metal-oxide interface) • In addition, they may alter the field-effect mobility of mobile carriers (in a MOSFET) due to Coulombic scattering. EE 130/230 M Spring 2013 Lecture 17, Slide 3

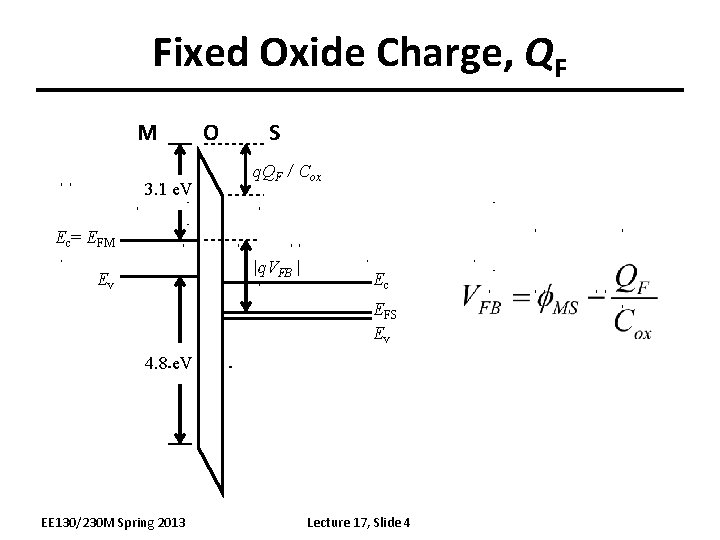

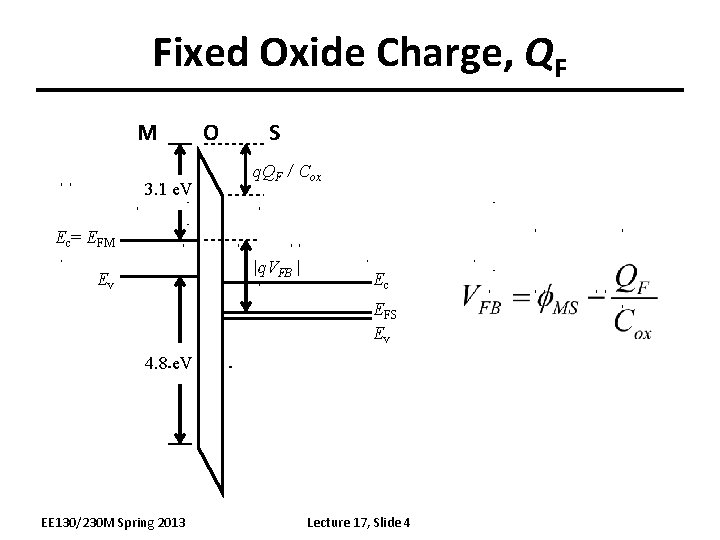

Fixed Oxide Charge, QF M 3. 1 e. V O S q. QF / Cox Ec= EFM |q. VFB | Ev Ec EFS Ev 4. 8 e. V EE 130/230 M Spring 2013 Lecture 17, Slide 4

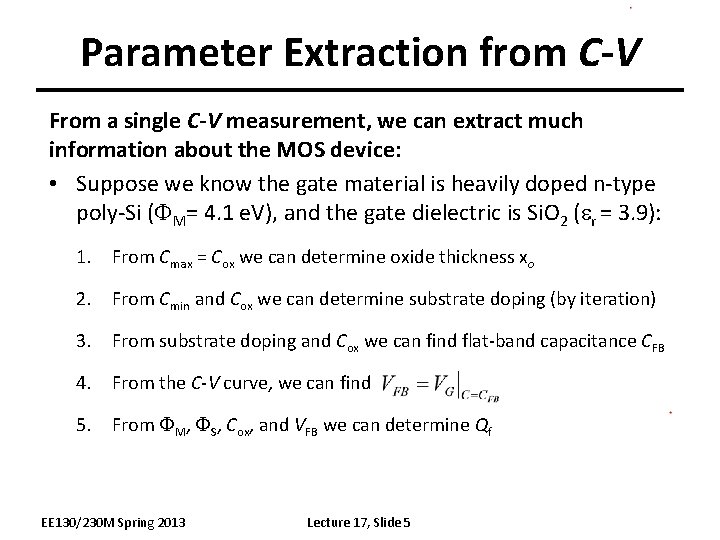

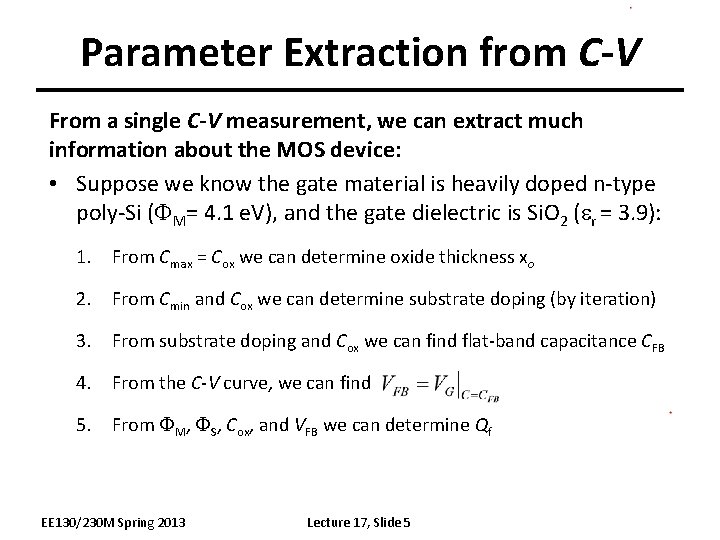

Parameter Extraction from C-V From a single C-V measurement, we can extract much information about the MOS device: • Suppose we know the gate material is heavily doped n-type poly-Si (FM= 4. 1 e. V), and the gate dielectric is Si. O 2 (er = 3. 9): 1. From Cmax = Cox we can determine oxide thickness xo 2. From Cmin and Cox we can determine substrate doping (by iteration) 3. From substrate doping and Cox we can find flat-band capacitance CFB 4. From the C-V curve, we can find 5. From FM, FS, Cox, and VFB we can determine Qf EE 130/230 M Spring 2013 Lecture 17, Slide 5

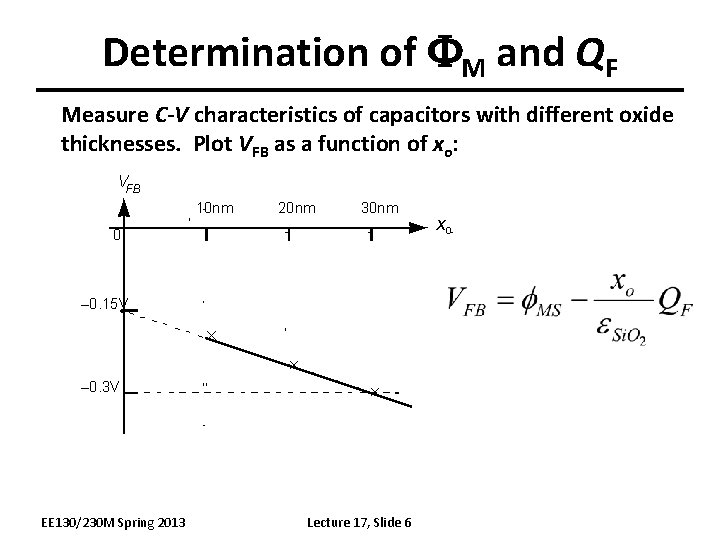

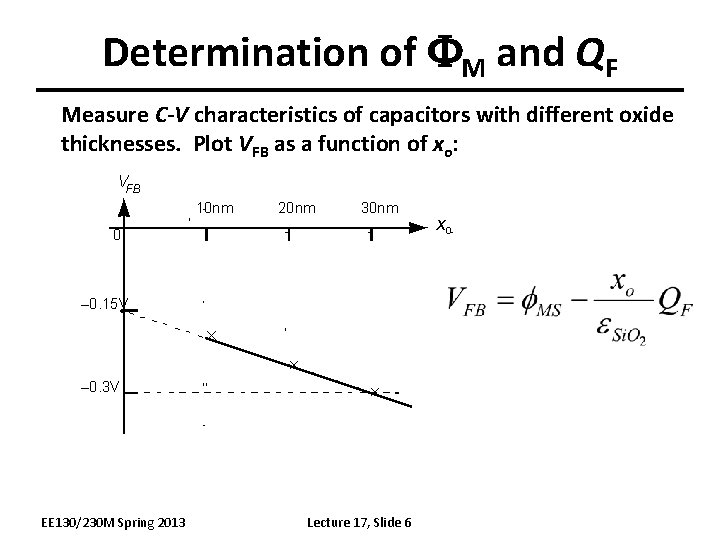

Determination of FM and QF Measure C-V characteristics of capacitors with different oxide thicknesses. Plot VFB as a function of xo: VFB 10 nm 20 nm 30 nm 0 – 0. 15 V – 0. 3 V EE 130/230 M Spring 2013 Lecture 17, Slide 6 xo

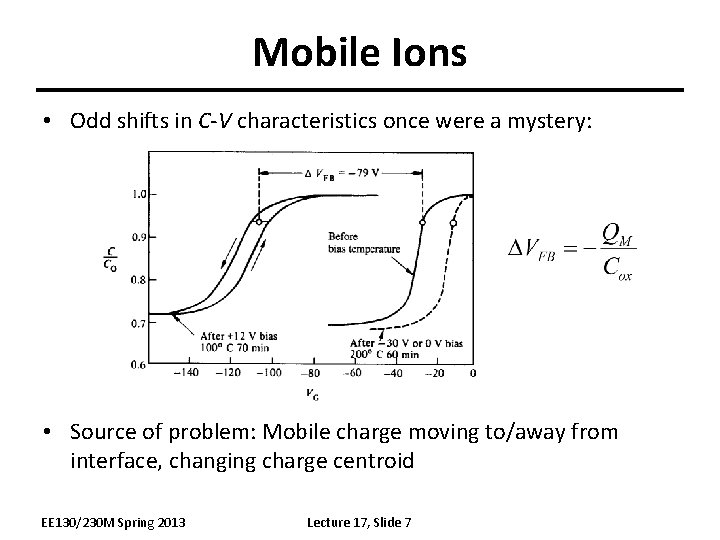

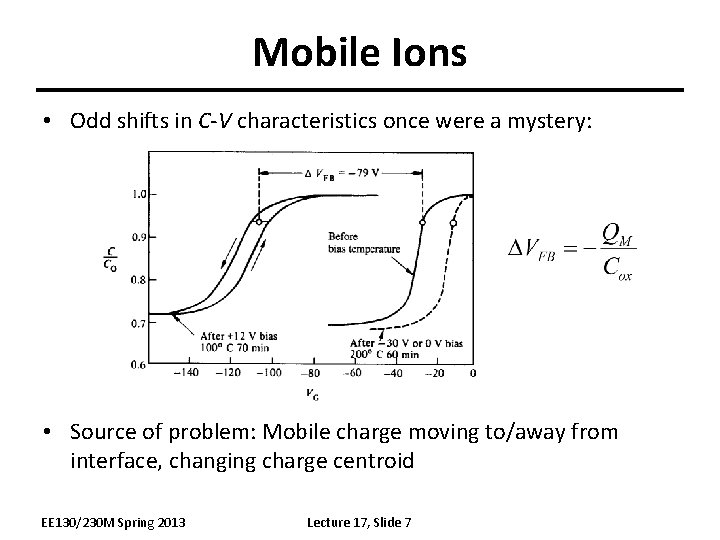

Mobile Ions • Odd shifts in C-V characteristics once were a mystery: • Source of problem: Mobile charge moving to/away from interface, changing charge centroid EE 130/230 M Spring 2013 Lecture 17, Slide 7

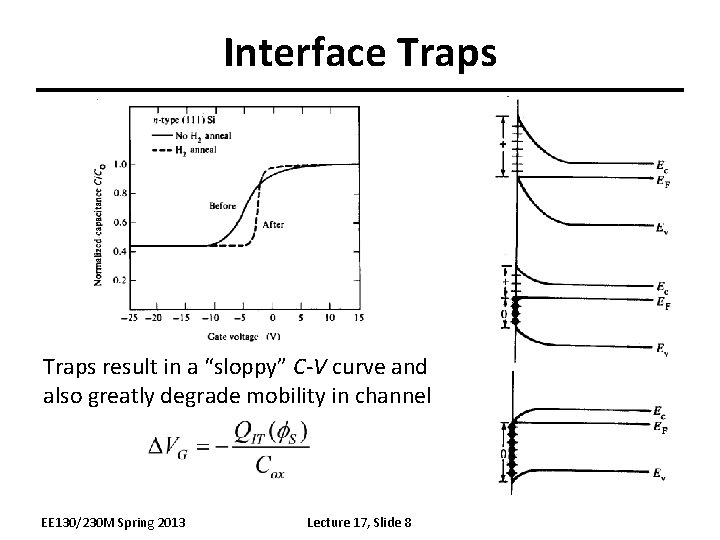

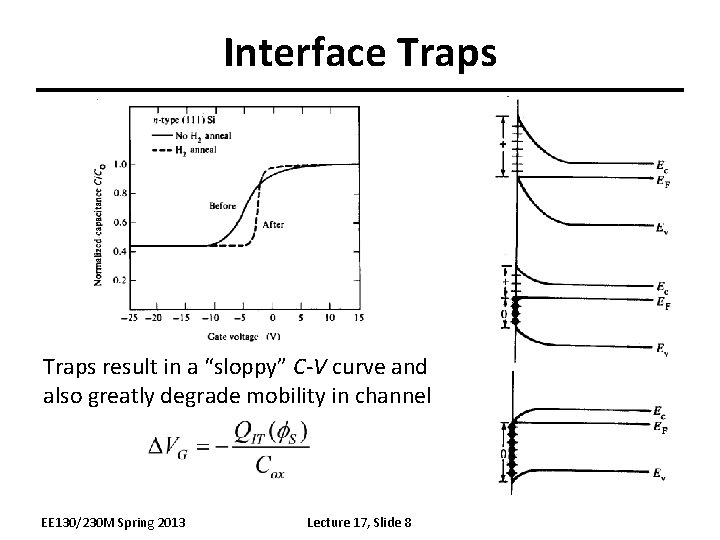

Interface Traps result in a “sloppy” C-V curve and also greatly degrade mobility in channel EE 130/230 M Spring 2013 Lecture 17, Slide 8

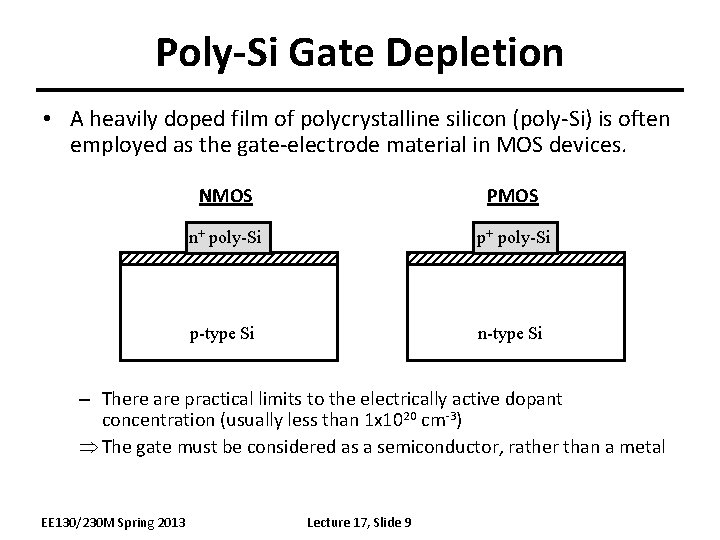

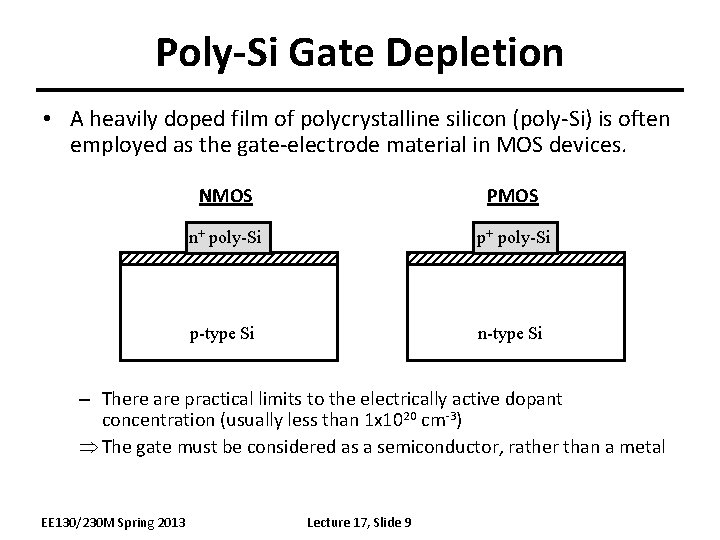

Poly-Si Gate Depletion • A heavily doped film of polycrystalline silicon (poly-Si) is often employed as the gate-electrode material in MOS devices. NMOS PMOS n+ poly-Si p-type Si n-type Si – There are practical limits to the electrically active dopant concentration (usually less than 1 x 1020 cm-3) Þ The gate must be considered as a semiconductor, rather than a metal EE 130/230 M Spring 2013 Lecture 17, Slide 9

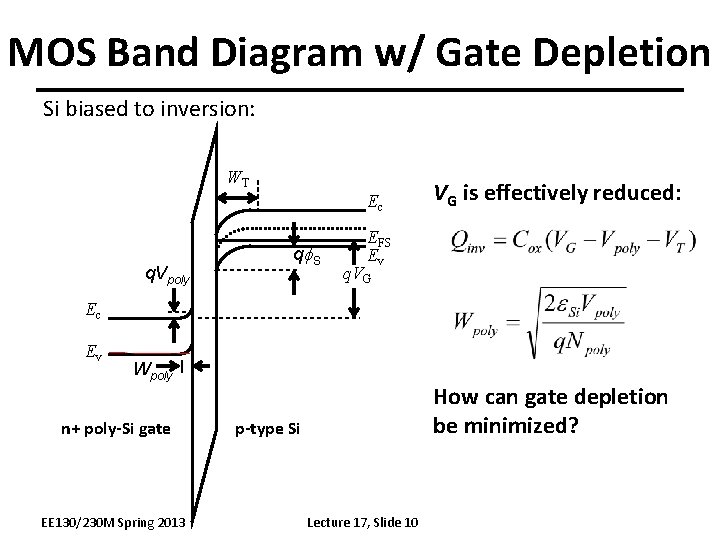

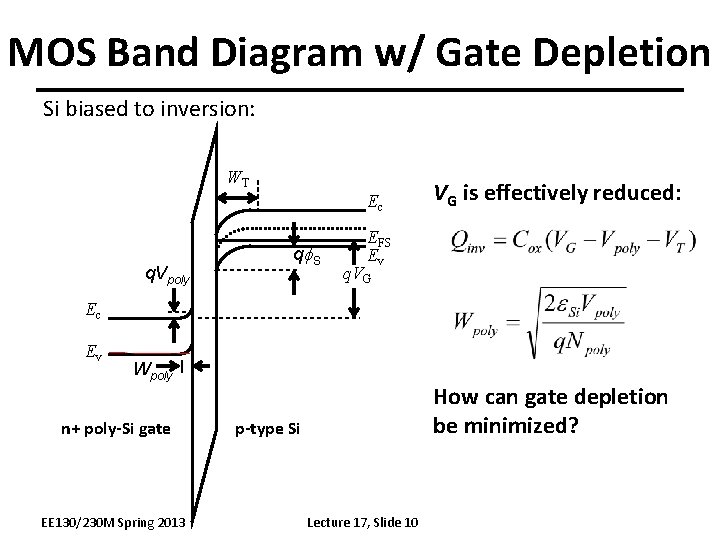

MOS Band Diagram w/ Gate Depletion Si biased to inversion: WT Ec q. Vpoly qf S VG is effectively reduced: EFS Ev q. VG Ec Ev Wpoly n+ poly-Si gate EE 130/230 M Spring 2013 How can gate depletion be minimized? p-type Si Lecture 17, Slide 10

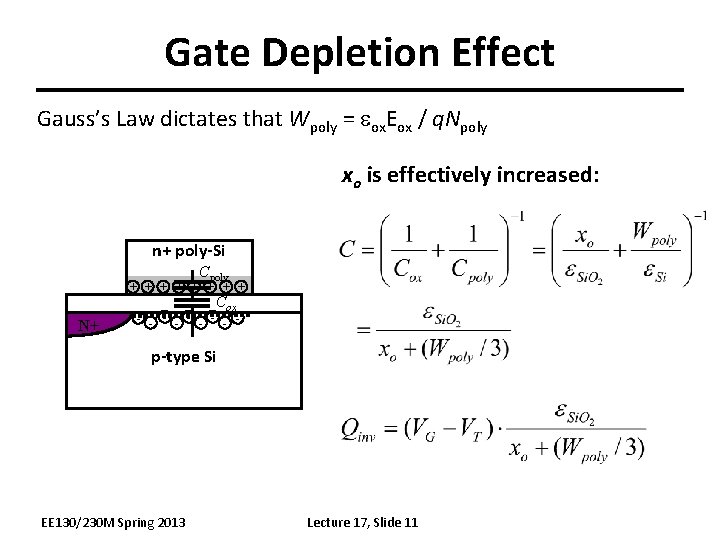

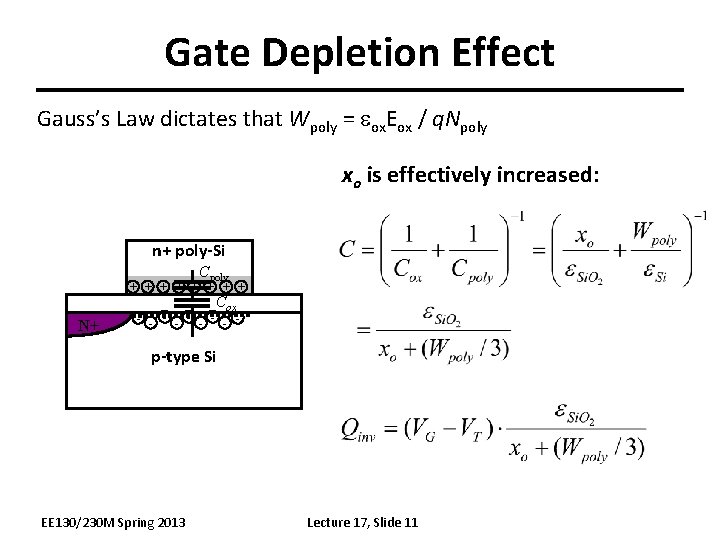

Gate Depletion Effect Gauss’s Law dictates that Wpoly = eox. Eox / q. Npoly xo is effectively increased: n+ poly-Si Cpoly + + + + Cox N+ - - - - - p-type Si EE 130/230 M Spring 2013 Lecture 17, Slide 11

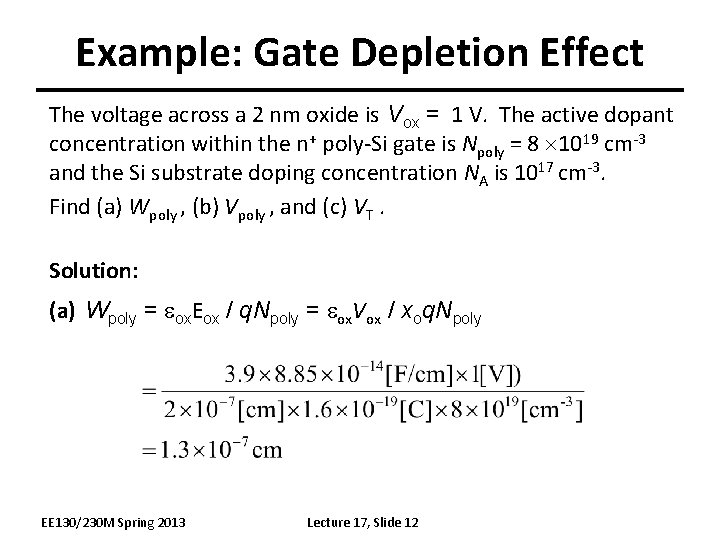

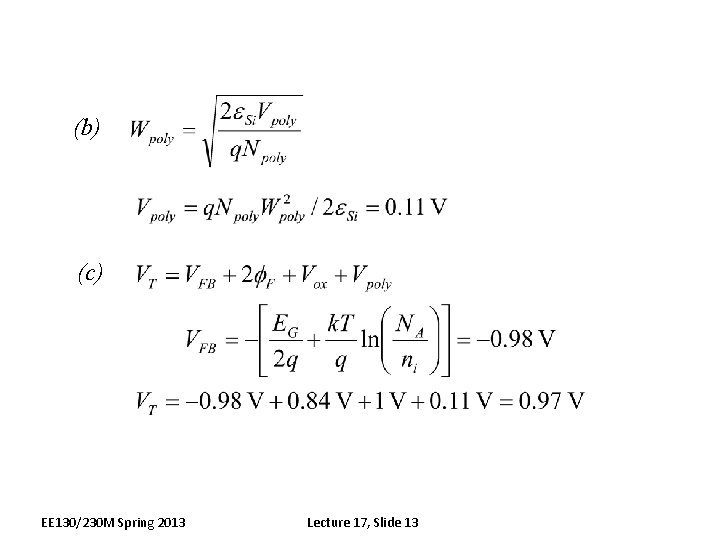

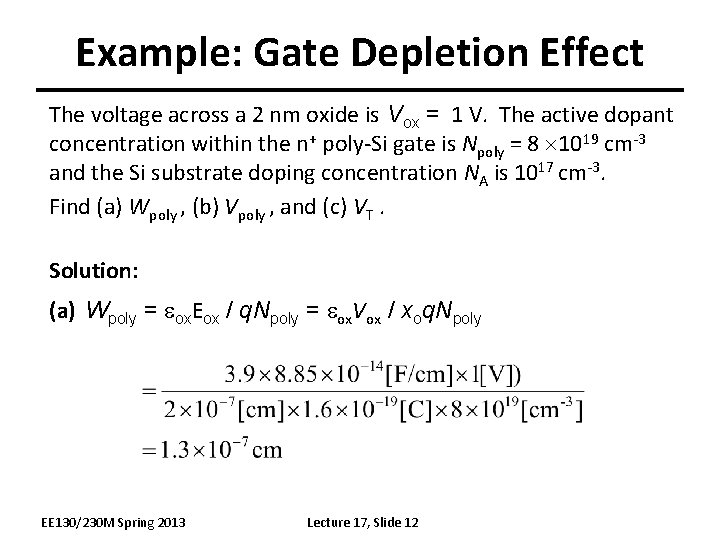

Example: Gate Depletion Effect The voltage across a 2 nm oxide is Vox = 1 V. The active dopant concentration within the n+ poly-Si gate is Npoly = 8 1019 cm-3 and the Si substrate doping concentration NA is 1017 cm-3. Find (a) Wpoly , (b) Vpoly , and (c) VT. Solution: (a) Wpoly = eox. Eox / q. Npoly = eox. Vox / xoq. Npoly EE 130/230 M Spring 2013 Lecture 17, Slide 12

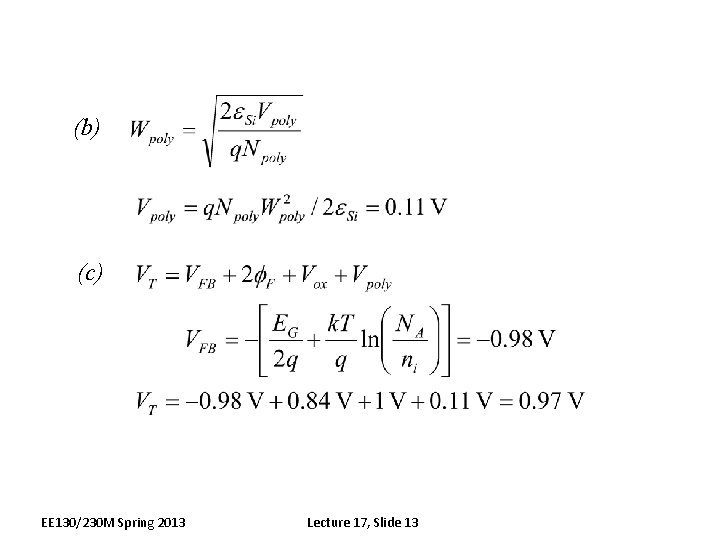

(b) (c) EE 130/230 M Spring 2013 Lecture 17, Slide 13

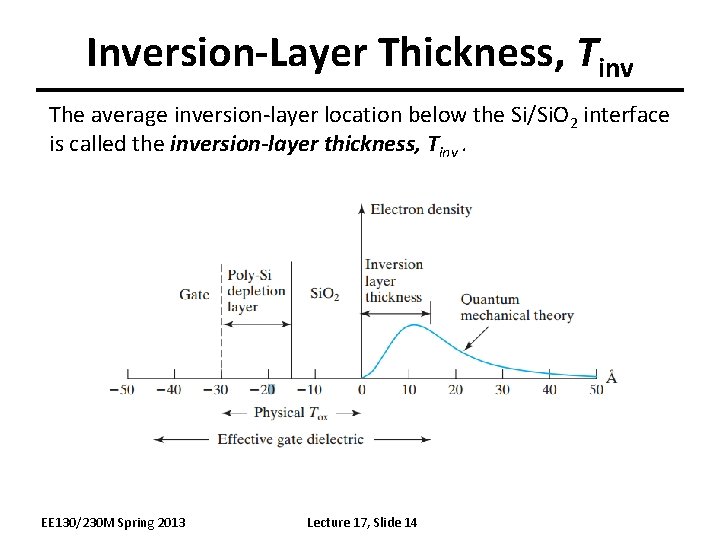

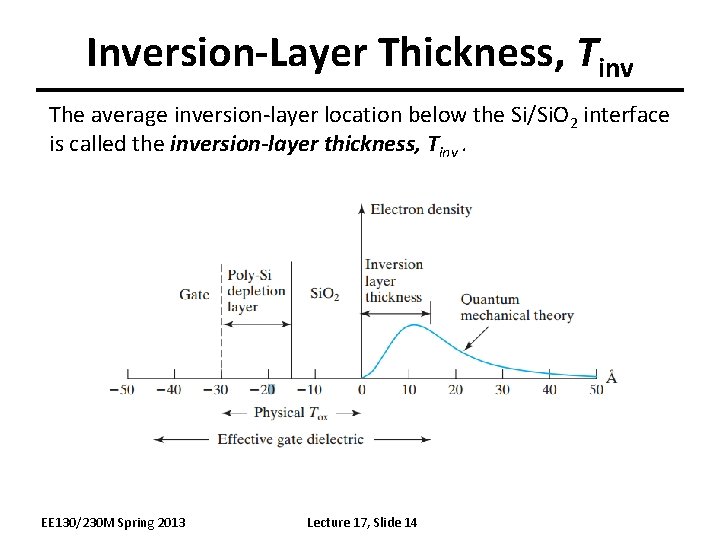

Inversion-Layer Thickness, Tinv The average inversion-layer location below the Si/Si. O 2 interface is called the inversion-layer thickness, Tinv. EE 130/230 M Spring 2013 Lecture 17, Slide 14

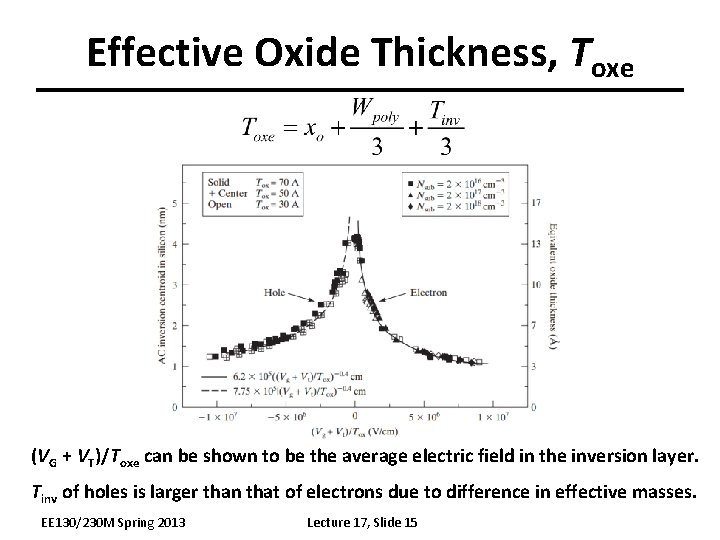

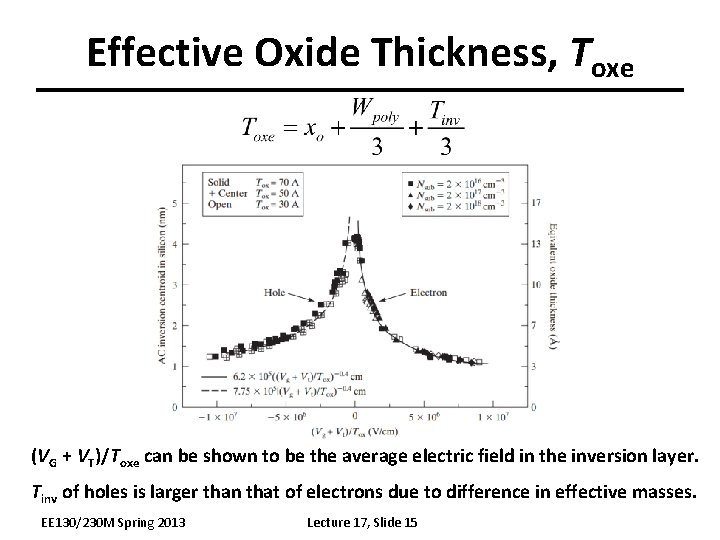

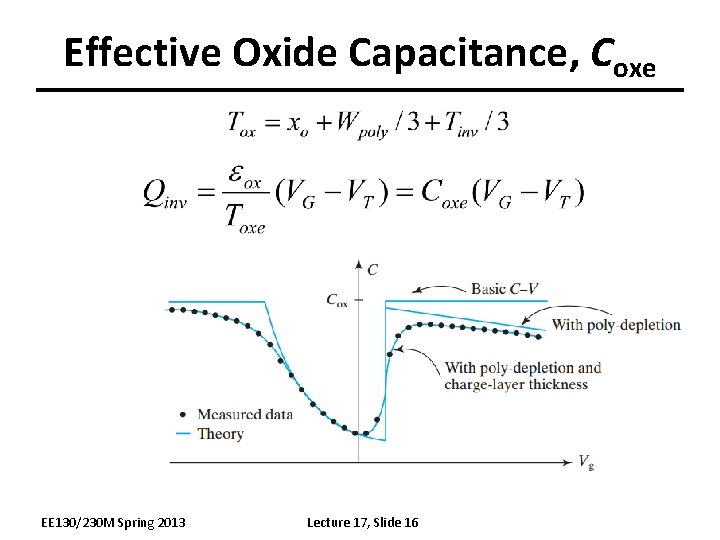

Effective Oxide Thickness, Toxe (VG + VT)/Toxe can be shown to be the average electric field in the inversion layer. Tinv of holes is larger than that of electrons due to difference in effective masses. EE 130/230 M Spring 2013 Lecture 17, Slide 15

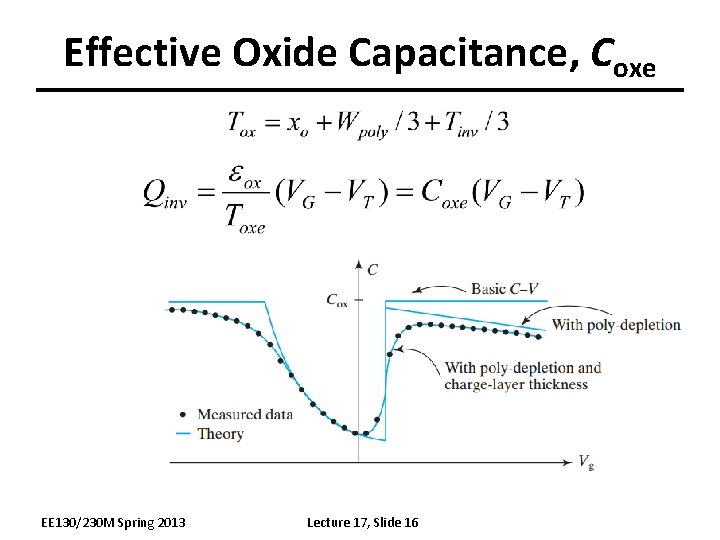

Effective Oxide Capacitance, Coxe EE 130/230 M Spring 2013 Lecture 17, Slide 16

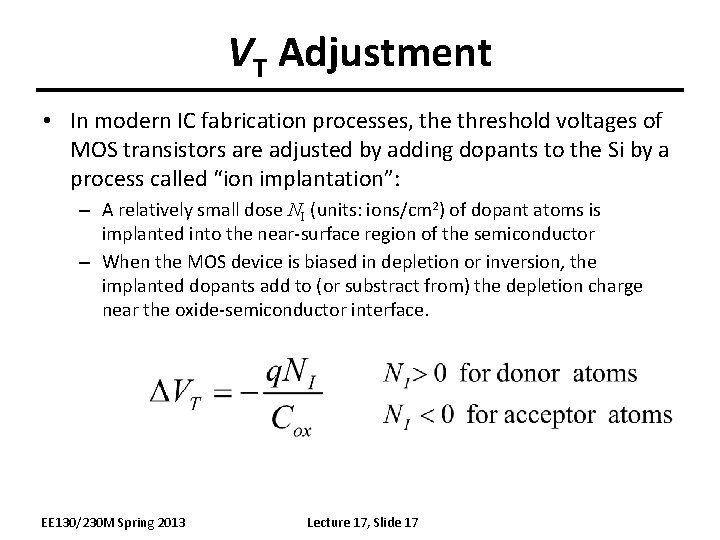

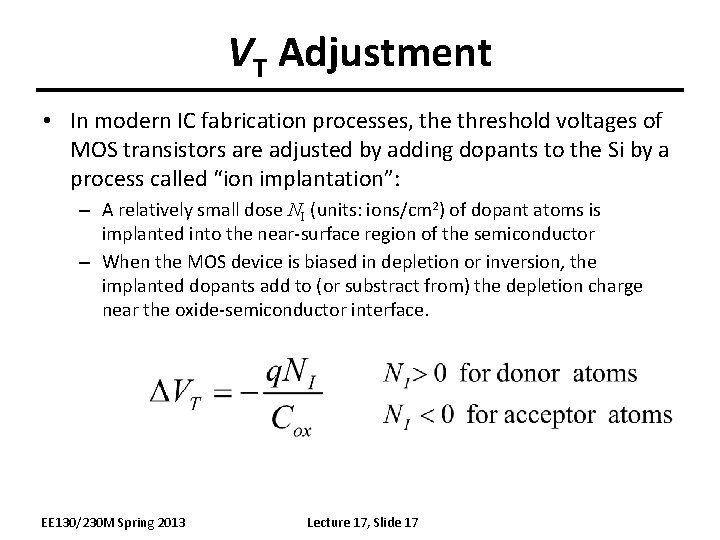

VT Adjustment • In modern IC fabrication processes, the threshold voltages of MOS transistors are adjusted by adding dopants to the Si by a process called “ion implantation”: – A relatively small dose NI (units: ions/cm 2) of dopant atoms is implanted into the near-surface region of the semiconductor – When the MOS device is biased in depletion or inversion, the implanted dopants add to (or substract from) the depletion charge near the oxide-semiconductor interface. EE 130/230 M Spring 2013 Lecture 17, Slide 17