Lecture 17 OUTLINE The MOS Capacitor contd Smallsignal

- Slides: 18

Lecture 17 OUTLINE • The MOS Capacitor (cont’d) – Small-signal capacitance (C-V characteristics) Reading: Pierret 16. 4; Hu 5. 6

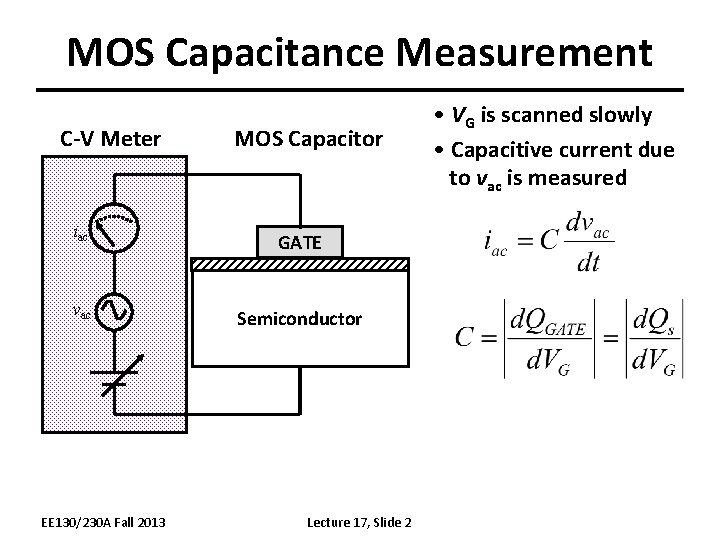

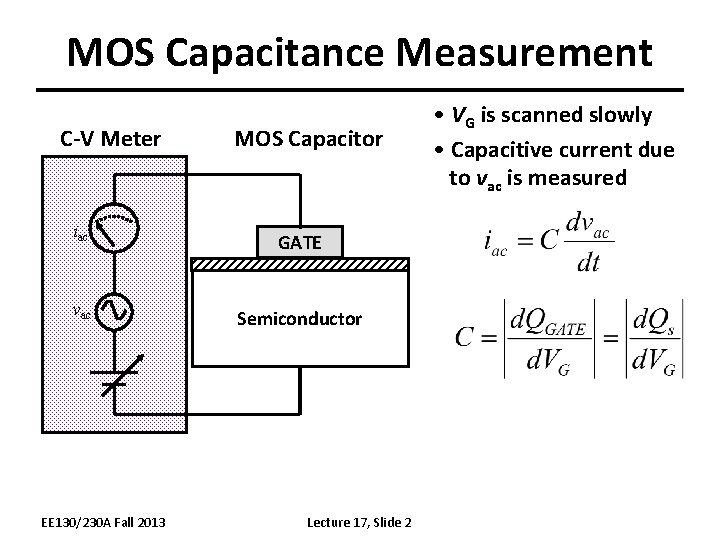

MOS Capacitance Measurement C-V Meter MOS Capacitor iac GATE vac Semiconductor EE 130/230 A Fall 2013 Lecture 17, Slide 2 • VG is scanned slowly • Capacitive current due to vac is measured

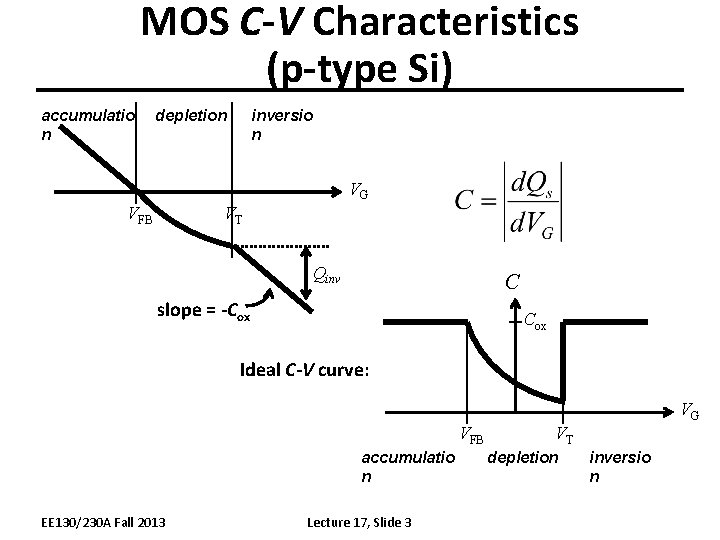

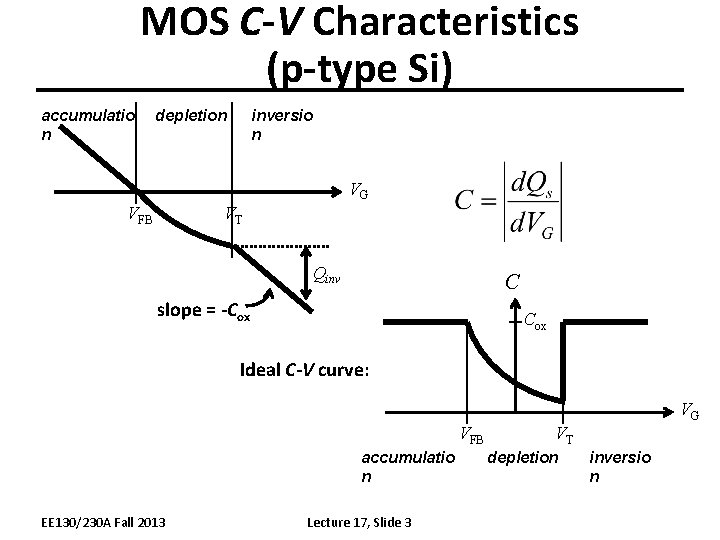

MOS C-V Characteristics (p-type Si) accumulatio n depletion inversio n VG VFB VT Qinv C slope = -Cox Ideal C-V curve: VG VFB accumulatio n EE 130/230 A Fall 2013 Lecture 17, Slide 3 VT depletion inversio n

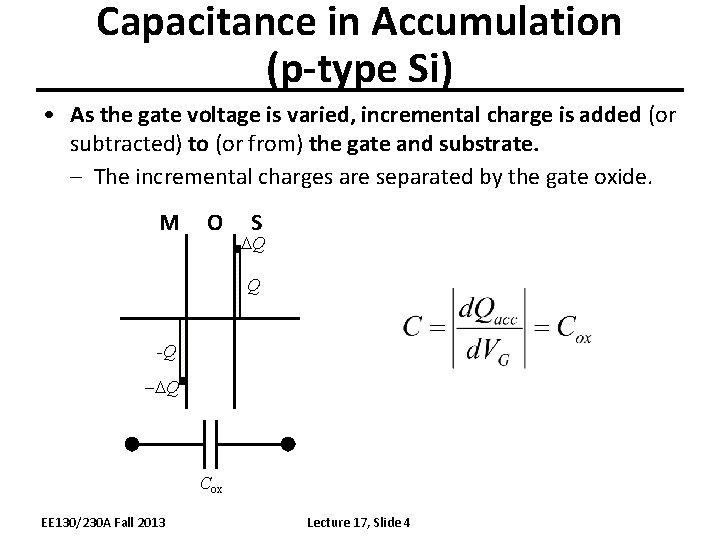

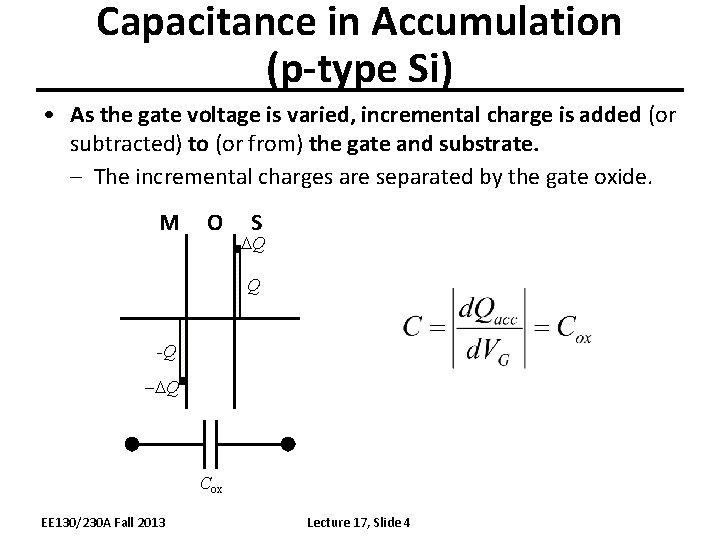

Capacitance in Accumulation (p-type Si) • As the gate voltage is varied, incremental charge is added (or subtracted) to (or from) the gate and substrate. - The incremental charges are separated by the gate oxide. M O S DQ Q -Q -DQ Cox EE 130/230 A Fall 2013 Lecture 17, Slide 4

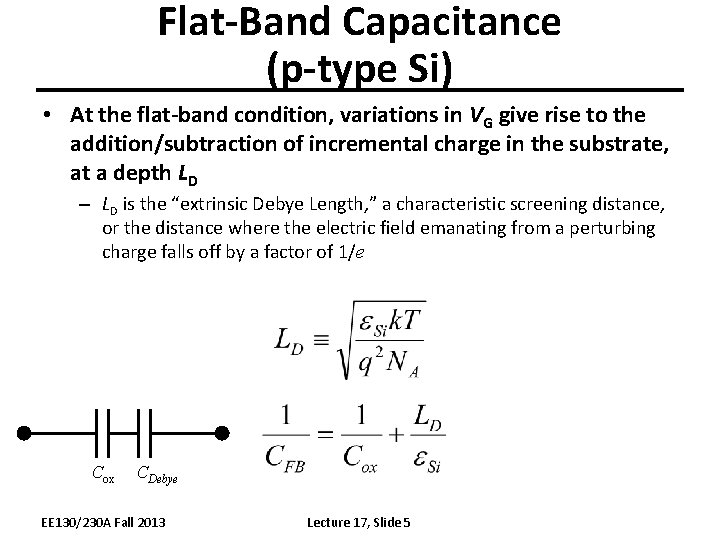

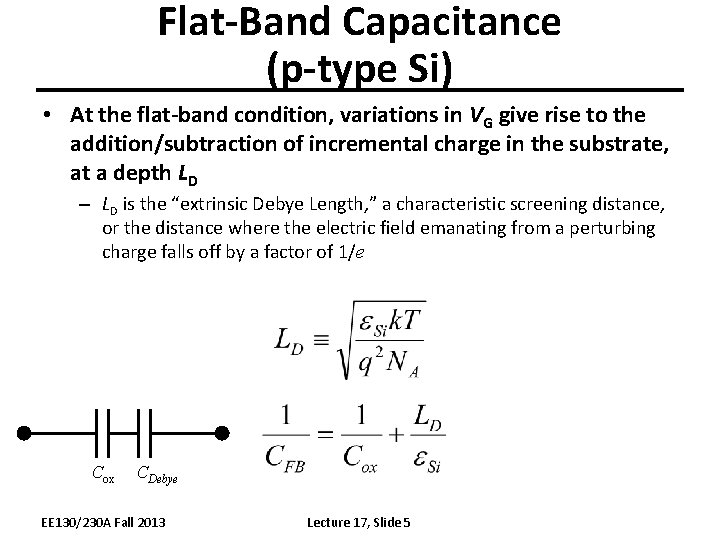

Flat-Band Capacitance (p-type Si) • At the flat-band condition, variations in VG give rise to the addition/subtraction of incremental charge in the substrate, at a depth LD – LD is the “extrinsic Debye Length, ” a characteristic screening distance, or the distance where the electric field emanating from a perturbing charge falls off by a factor of 1/e Cox CDebye EE 130/230 A Fall 2013 Lecture 17, Slide 5

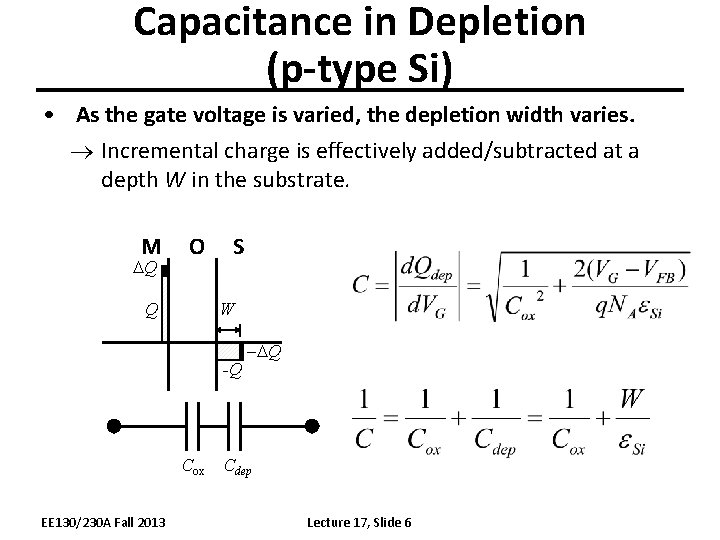

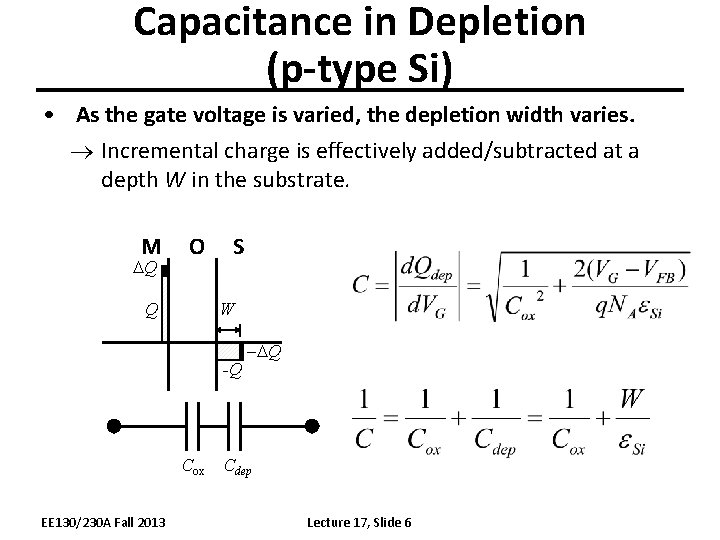

Capacitance in Depletion (p-type Si) • As the gate voltage is varied, the depletion width varies. ® Incremental charge is effectively added/subtracted at a depth W in the substrate. M DQ Q O S W -Q -DQ Cox Cdep EE 130/230 A Fall 2013 Lecture 17, Slide 6

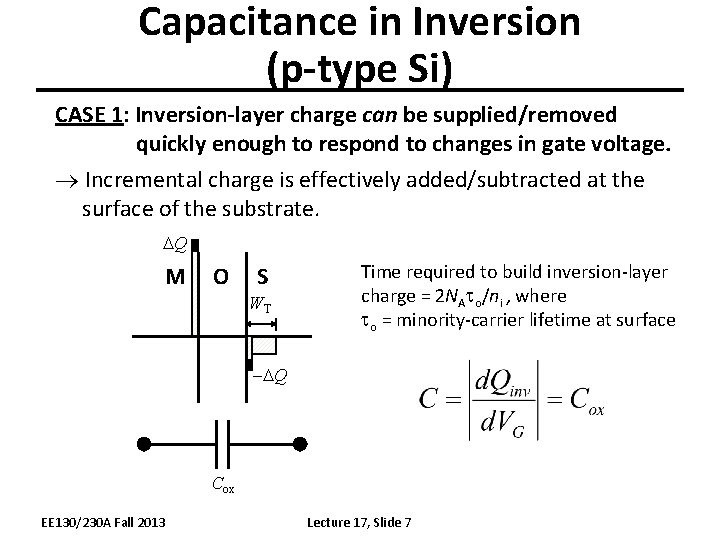

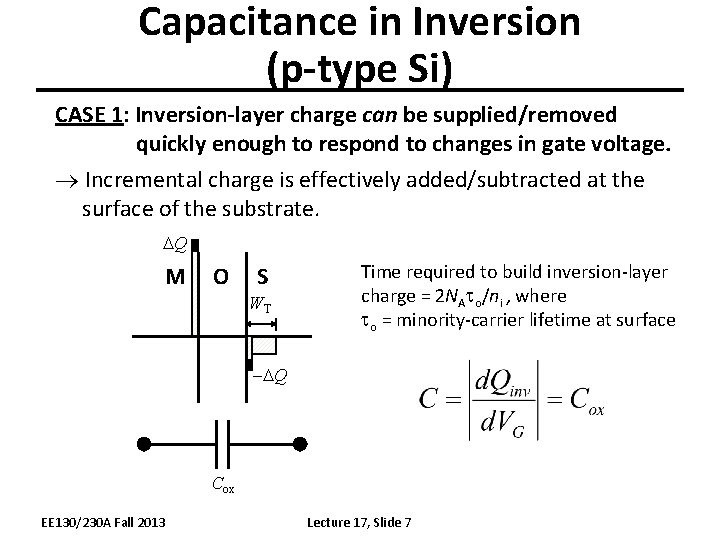

Capacitance in Inversion (p-type Si) CASE 1: Inversion-layer charge can be supplied/removed quickly enough to respond to changes in gate voltage. ® Incremental charge is effectively added/subtracted at the surface of the substrate. DQ M O S WT Time required to build inversion-layer charge = 2 NAto/ni , where to = minority-carrier lifetime at surface -DQ Cox EE 130/230 A Fall 2013 Lecture 17, Slide 7

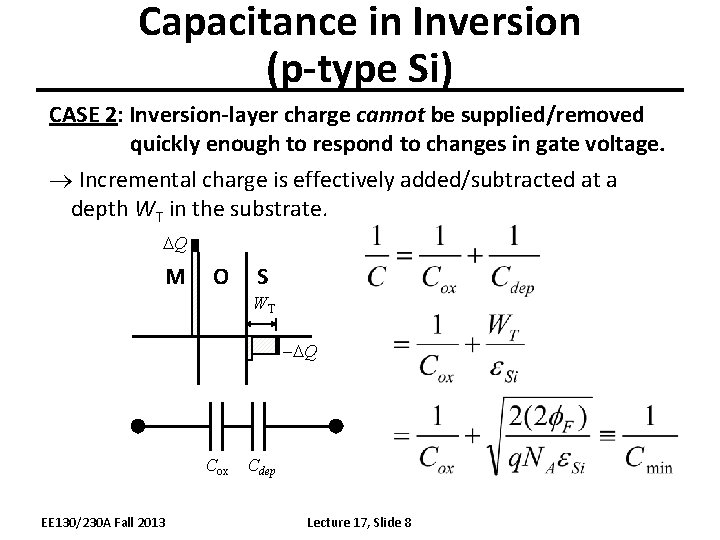

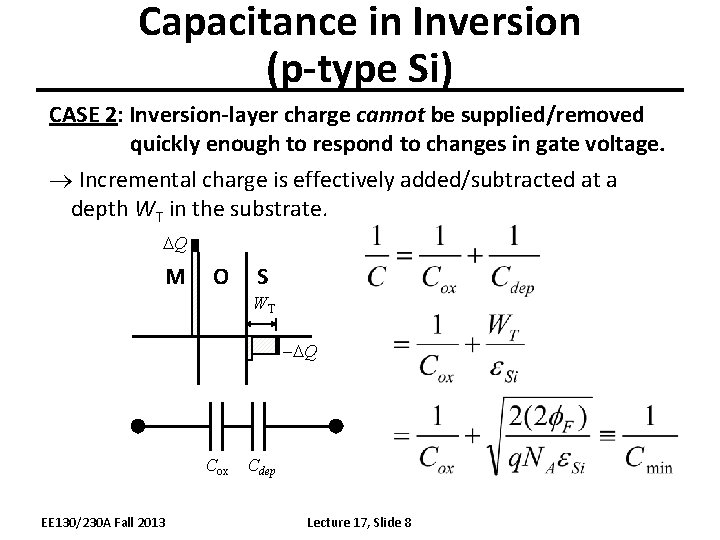

Capacitance in Inversion (p-type Si) CASE 2: Inversion-layer charge cannot be supplied/removed quickly enough to respond to changes in gate voltage. ® Incremental charge is effectively added/subtracted at a depth WT in the substrate. DQ M O S WT -DQ Cox Cdep EE 130/230 A Fall 2013 Lecture 17, Slide 8

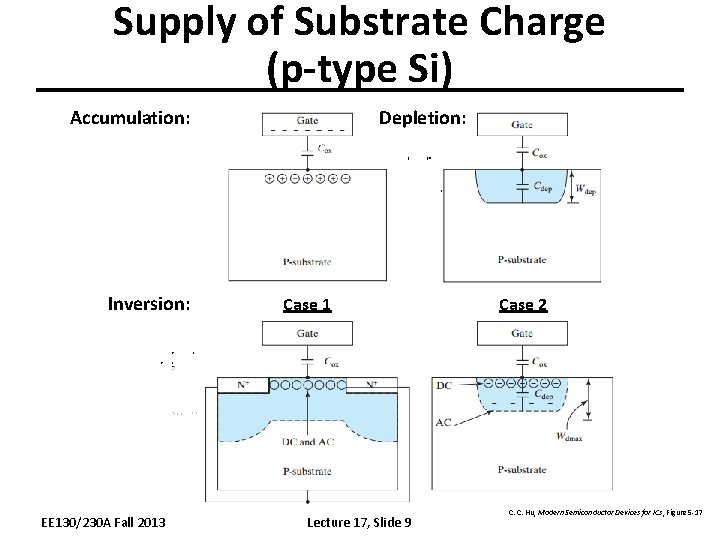

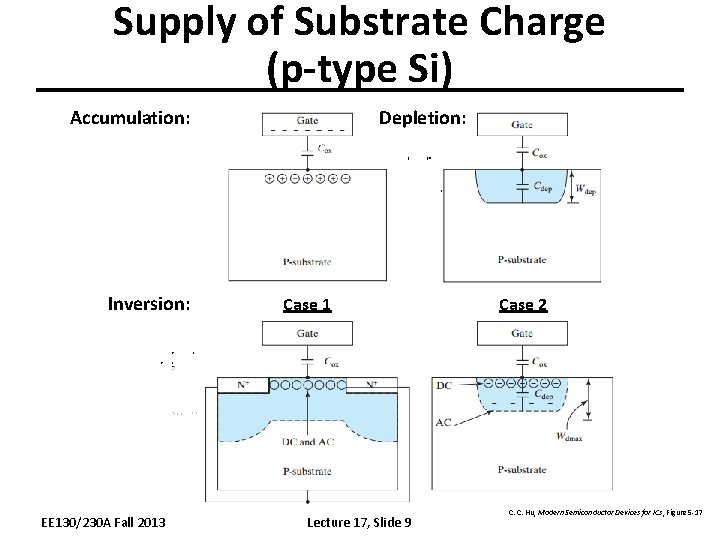

Supply of Substrate Charge (p-type Si) Accumulation: Inversion: EE 130/230 A Fall 2013 Depletion: Case 1 Lecture 17, Slide 9 Case 2 C. C. Hu, Modern Semiconductor Devices for ICs, Figure 5 -17

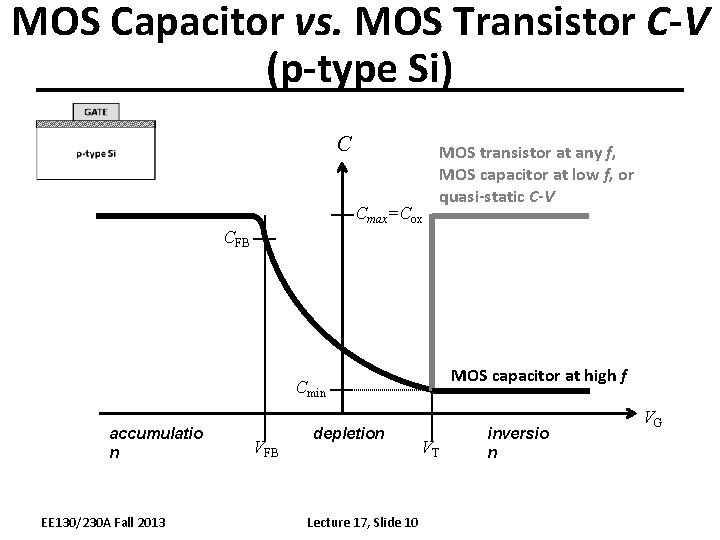

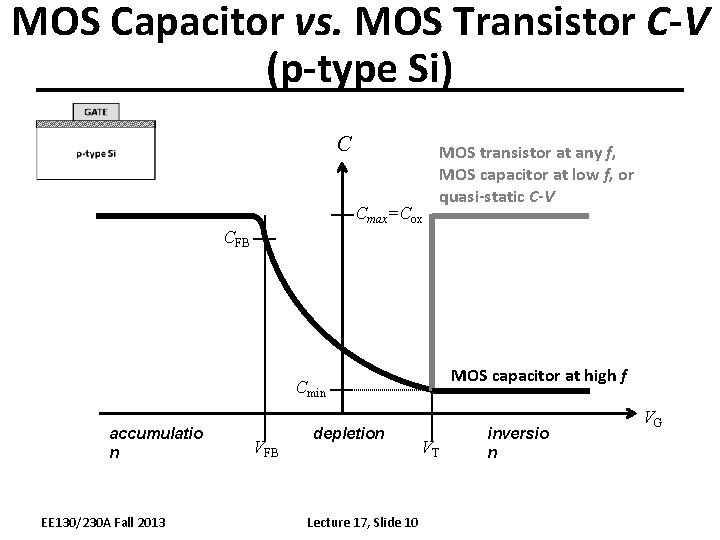

MOS Capacitor vs. MOS Transistor C-V (p-type Si) C Cmax=Cox MOS transistor at any f, MOS capacitor at low f, or quasi-static C-V CFB MOS capacitor at high f Cmin accumulatio n EE 130/230 A Fall 2013 VFB depletion Lecture 17, Slide 10 VT inversio n VG

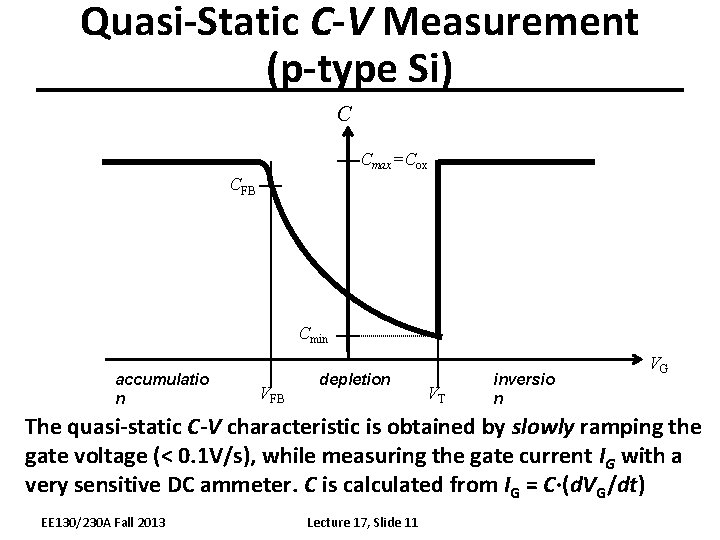

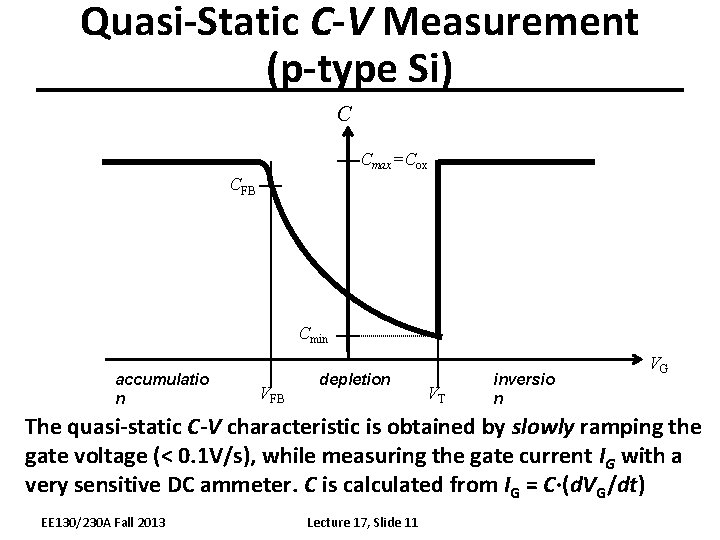

Quasi-Static C-V Measurement (p-type Si) C Cmax=Cox CFB Cmin accumulatio n VFB depletion VT inversio n VG The quasi-static C-V characteristic is obtained by slowly ramping the gate voltage (< 0. 1 V/s), while measuring the gate current IG with a very sensitive DC ammeter. C is calculated from IG = C·(d. VG/dt) EE 130/230 A Fall 2013 Lecture 17, Slide 11

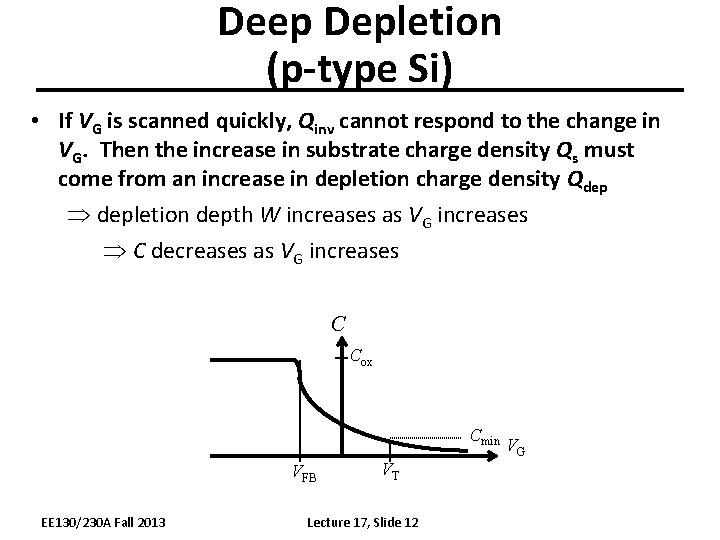

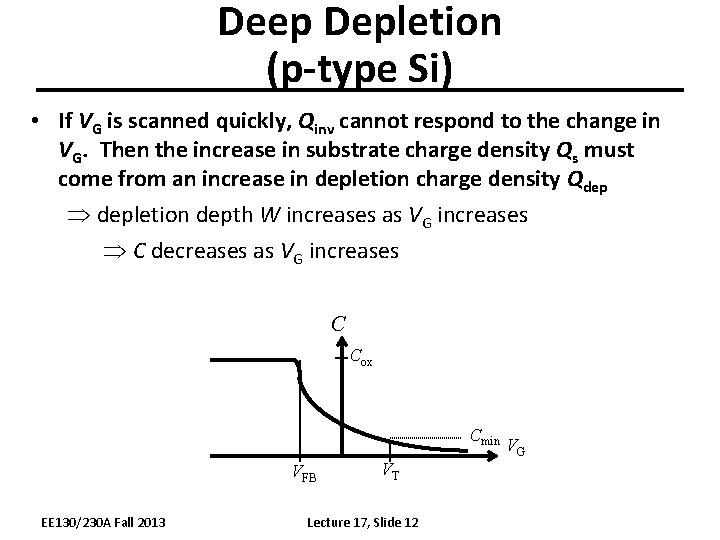

Deep Depletion (p-type Si) • If VG is scanned quickly, Qinv cannot respond to the change in VG. Then the increase in substrate charge density Qs must come from an increase in depletion charge density Qdep Þ depletion depth W increases as VG increases Þ C decreases as VG increases C Cox Cmin VFB EE 130/230 A Fall 2013 VT Lecture 17, Slide 12 VG

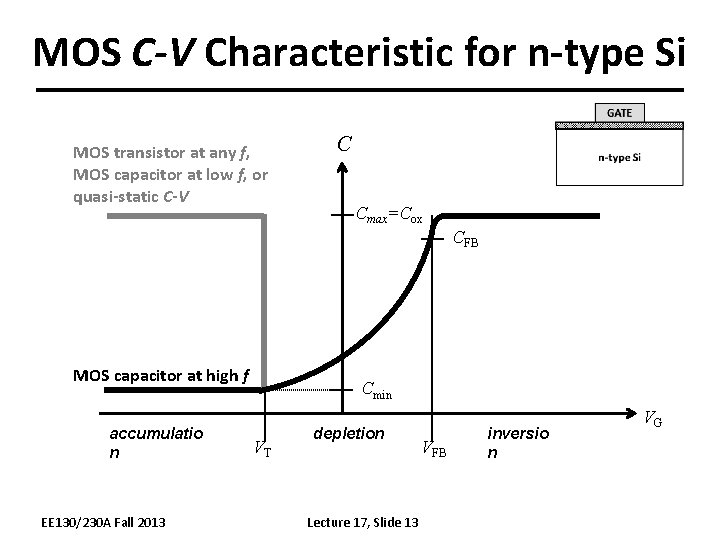

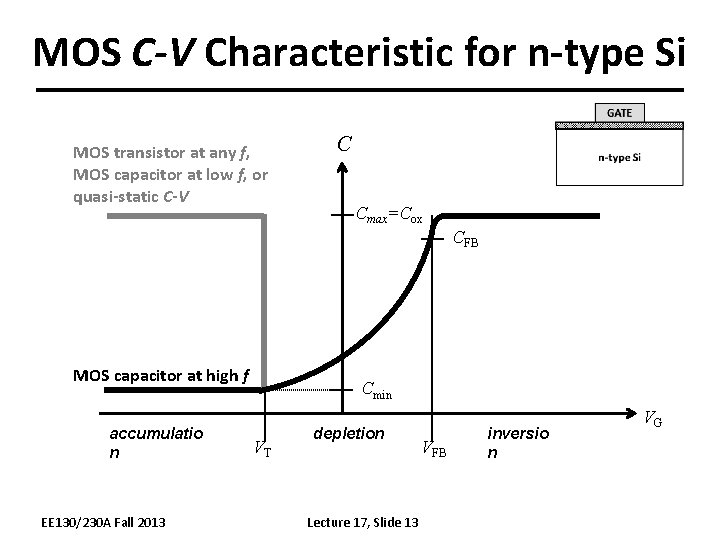

MOS C-V Characteristic for n-type Si MOS transistor at any f, MOS capacitor at low f, or quasi-static C-V C Cmax=Cox CFB MOS capacitor at high f accumulatio n EE 130/230 A Fall 2013 Cmin VT depletion Lecture 17, Slide 13 VFB inversio n VG

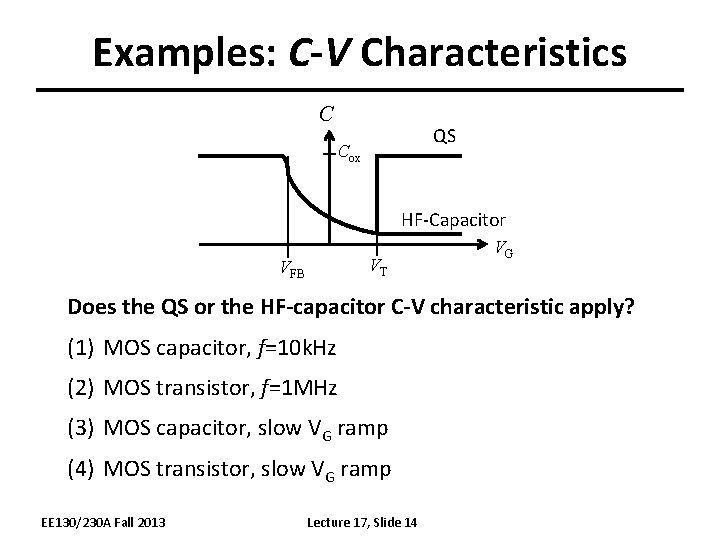

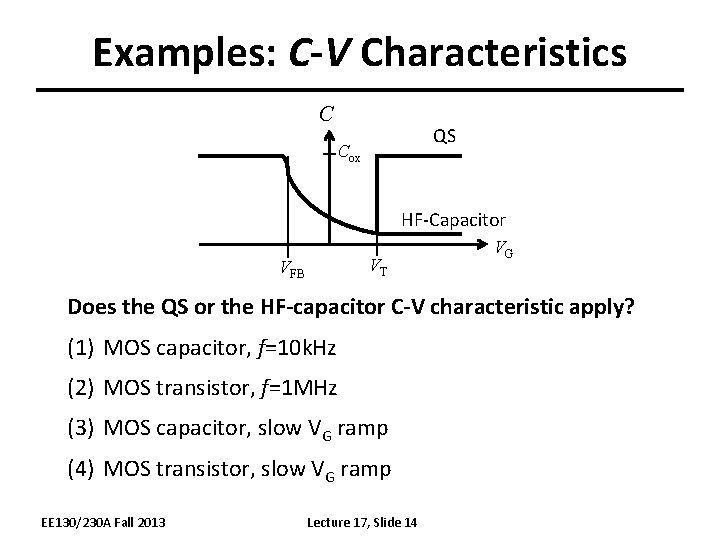

Examples: C-V Characteristics C QS Cox HF-Capacitor VT VFB VG Does the QS or the HF-capacitor C-V characteristic apply? (1) MOS capacitor, f=10 k. Hz (2) MOS transistor, f=1 MHz (3) MOS capacitor, slow VG ramp (4) MOS transistor, slow VG ramp EE 130/230 A Fall 2013 Lecture 17, Slide 14

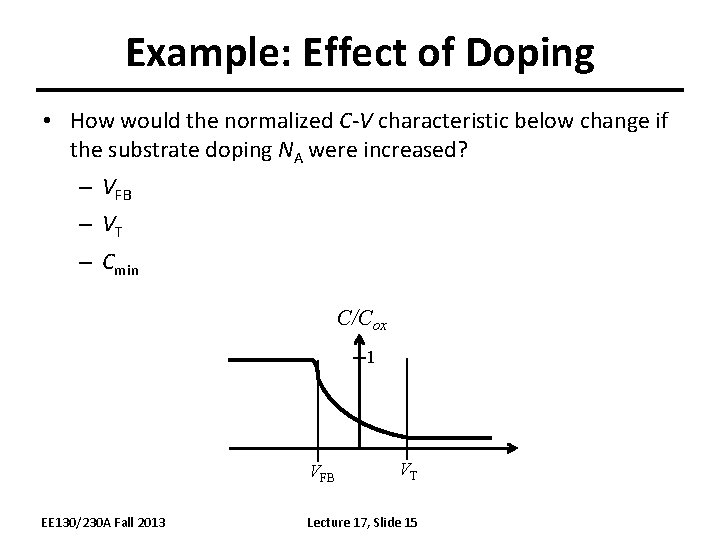

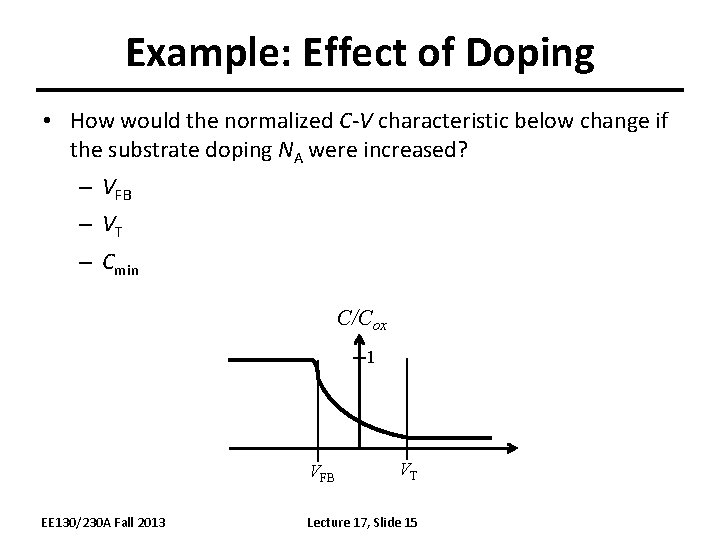

Example: Effect of Doping • How would the normalized C-V characteristic below change if the substrate doping NA were increased? – VFB – VT – Cmin C/Cox 1 VFB EE 130/230 A Fall 2013 VT Lecture 17, Slide 15

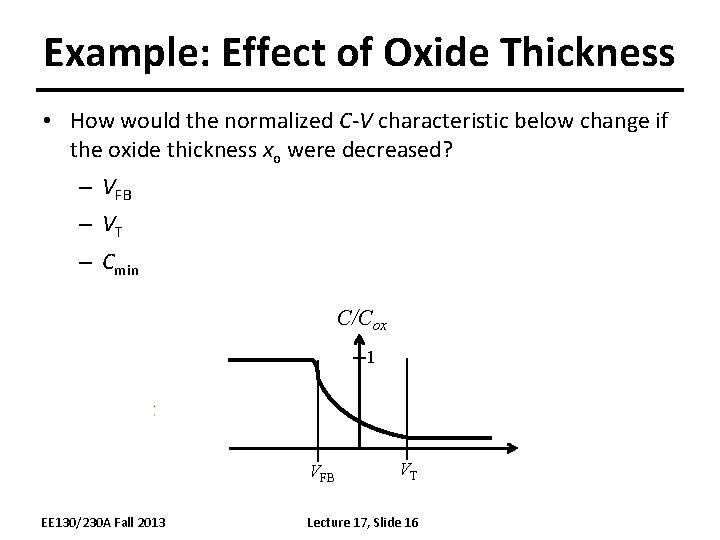

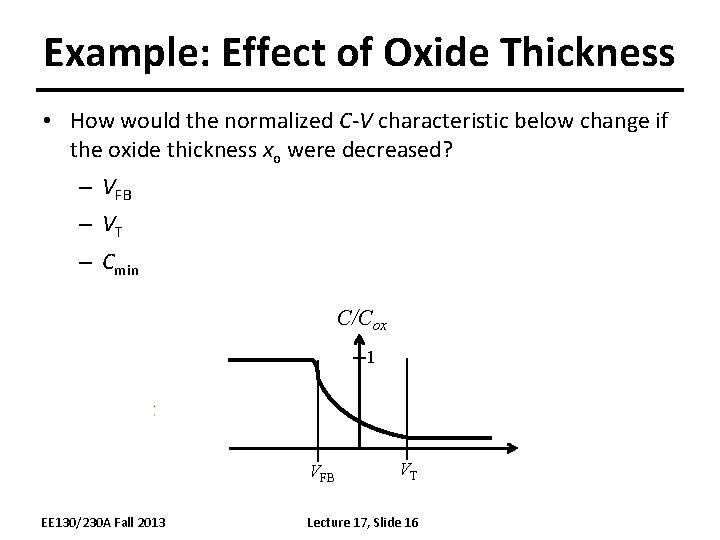

Example: Effect of Oxide Thickness • How would the normalized C-V characteristic below change if the oxide thickness xo were decreased? – VFB – VT – Cmin C/Cox 1 VFB EE 130/230 A Fall 2013 VT Lecture 17, Slide 16

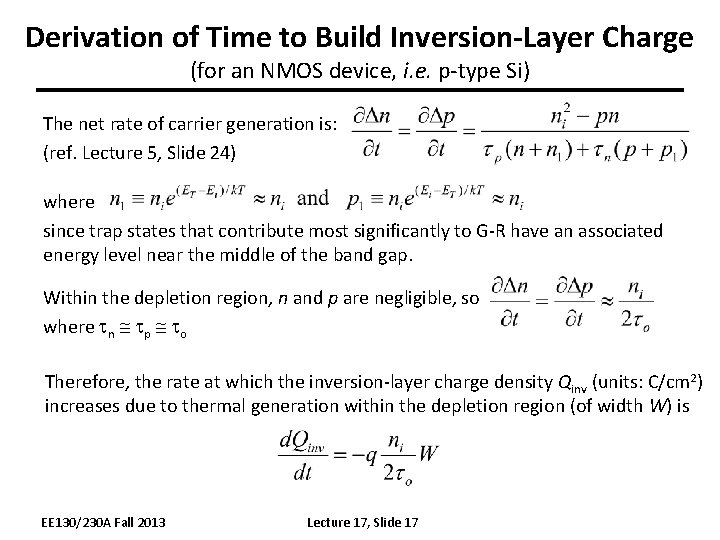

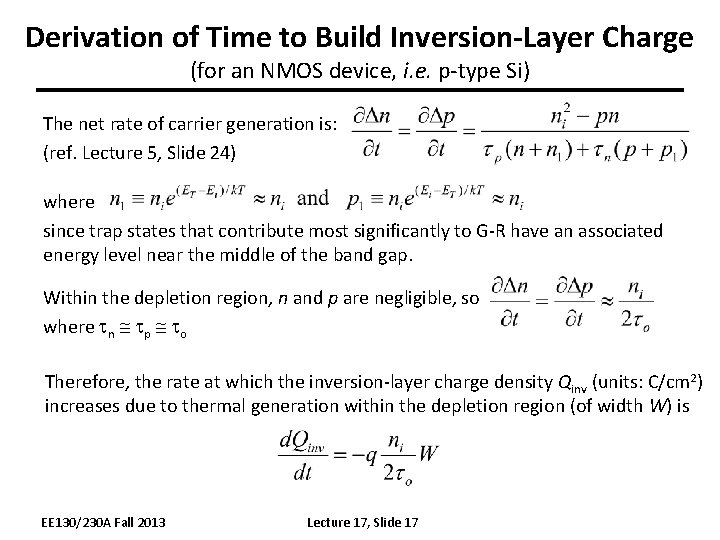

Derivation of Time to Build Inversion-Layer Charge (for an NMOS device, i. e. p-type Si) The net rate of carrier generation is: (ref. Lecture 5, Slide 24) where since trap states that contribute most significantly to G-R have an associated energy level near the middle of the band gap. Within the depletion region, n and p are negligible, so where tn tp to Therefore, the rate at which the inversion-layer charge density Qinv (units: C/cm 2) increases due to thermal generation within the depletion region (of width W) is EE 130/230 A Fall 2013 Lecture 17, Slide 17

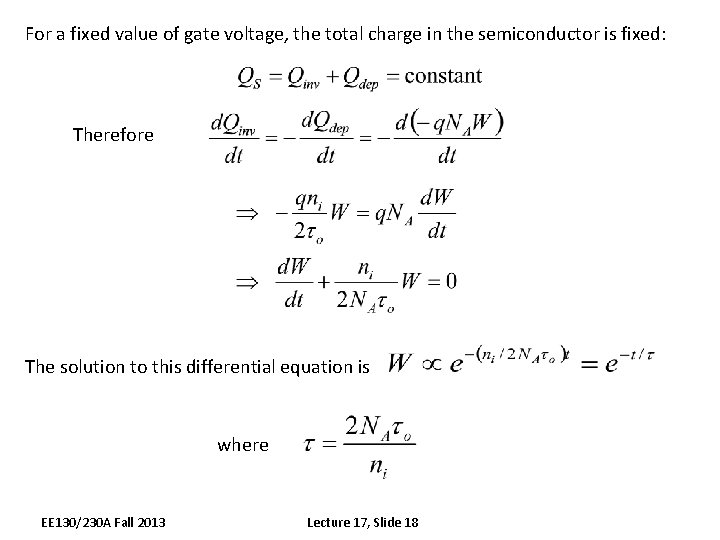

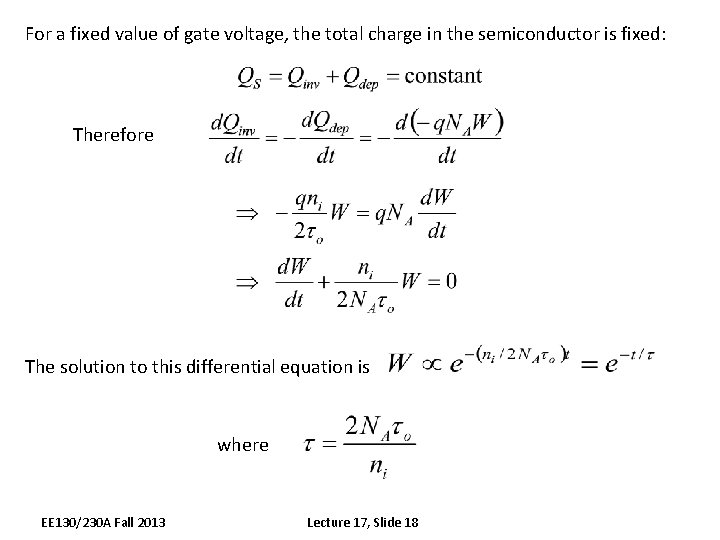

For a fixed value of gate voltage, the total charge in the semiconductor is fixed: Therefore The solution to this differential equation is where EE 130/230 A Fall 2013 Lecture 17, Slide 18