Lecture 15 Finite State Machine Implementation Prith Banerjee

Lecture 15 Finite State Machine Implementation Prith Banerjee ECE C 03 Advanced Digital Design Spring 1998 ECE C 03 Lecture 15 1

Outline • • Mapping FSM to random logic Mapping FSM to ROMS Mapping FSM to PLAs Mapping FSM to Programmable Logic Devices (Xilinx) • READING: Katz 10. 1. 1, 10. 1. 2, 10. 3, Dewey 9. 5 ECE C 03 Lecture 15 2

FSM Implementation Strategies • Discrete Gate Logic Emphasis so far • MSI Logic (e. g. , Counters) • Structured Logic (e. g. , PLA/PAL, ROM) • Field Programmable Gate Arrays (FPGAs) Function can be configured "on the fly" or in the field Flipflops/Registers plus discrete gates on the same chip ECE C 03 Lecture 15 3

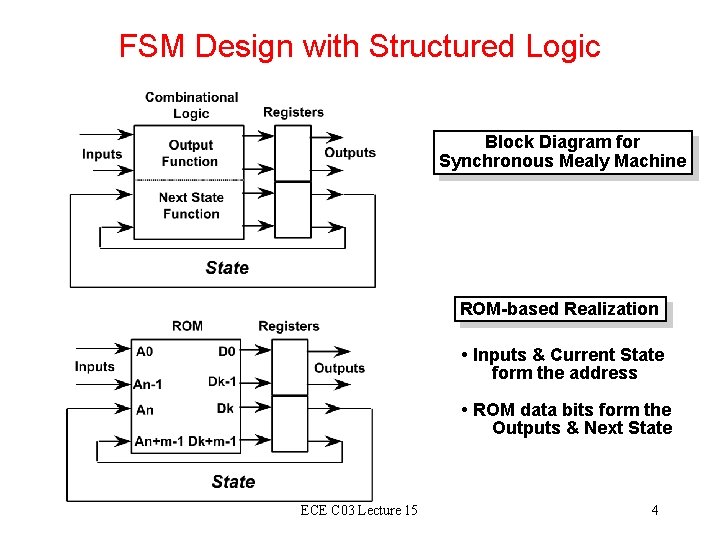

FSM Design with Structured Logic Block Diagram for Synchronous Mealy Machine ROM-based Realization • Inputs & Current State form the address • ROM data bits form the Outputs & Next State ECE C 03 Lecture 15 4

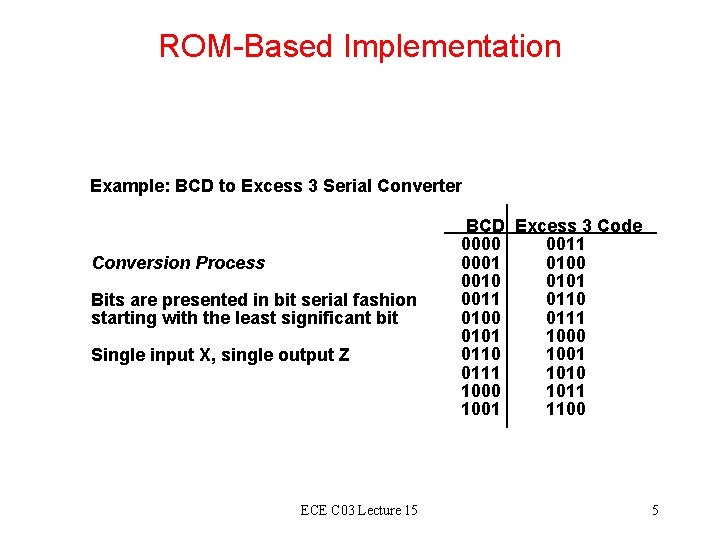

ROM-Based Implementation Example: BCD to Excess 3 Serial Converter Conversion Process Bits are presented in bit serial fashion starting with the least significant bit Single input X, single output Z ECE C 03 Lecture 15 BCD Excess 3 Code 0000 0011 0001 0100 0010 0101 0011 0110 0100 0111 0101 1000 0110 1001 0111 1010 1000 1011 1001 1100 5

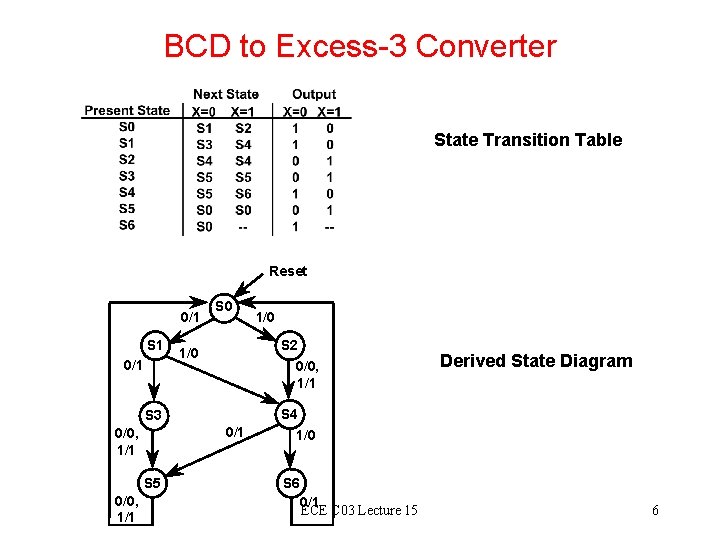

BCD to Excess-3 Converter State Transition Table Reset 0/1 S 1 0/1 S 0 S 2 0/0, 1/1 1/0 S 3 0/1 0/0, 1/1 S 5 0/0, 1/1 1/0 Derived State Diagram S 4 1/0 S 6 0/1 ECE C 03 Lecture 15 6

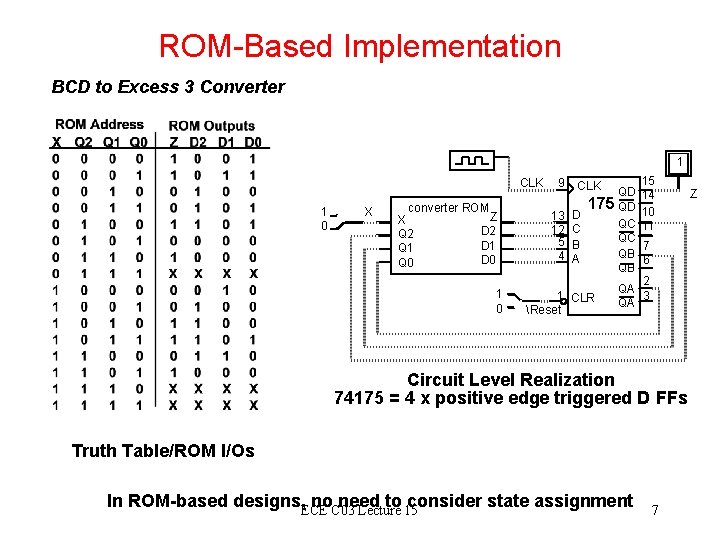

ROM-Based Implementation BCD to Excess 3 Converter 1 CLK 1 0 X converter ROM Z X D 2 Q 2 D 1 Q 1 D 0 Q 0 1 0 9 13 12 5 4 CLK D C B A QD 175 QD QC QC QB QB 1 CLR Reset 15 14 10 11 7 6 2 QA 3 QA Circuit Level Realization 74175 = 4 x positive edge triggered D FFs Truth Table/ROM I/Os In ROM-based designs, ECE no. C 03 need to consider state assignment Lecture 15 7 Z

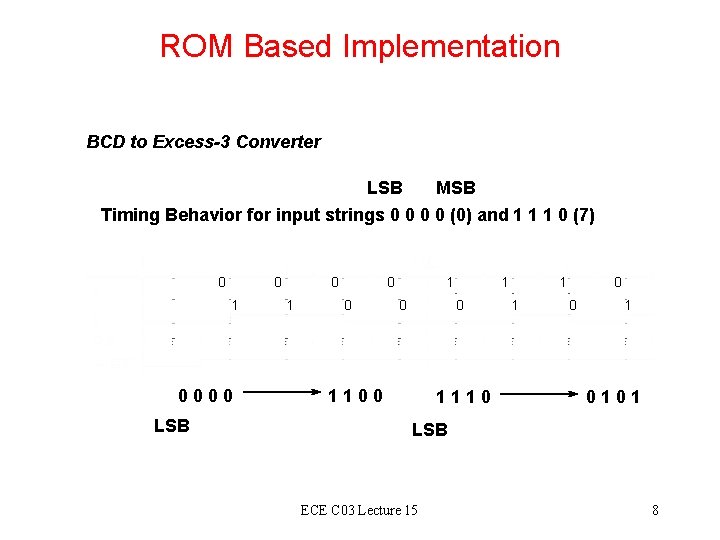

ROM Based Implementation BCD to Excess-3 Converter LSB MSB Timing Behavior for input strings 0 0 (0) and 1 1 1 0 (7) 0 0 1 0000 LSB 0 1 0 1 0 1100 1110 1 1 0 0 1 0101 LSB ECE C 03 Lecture 15 8

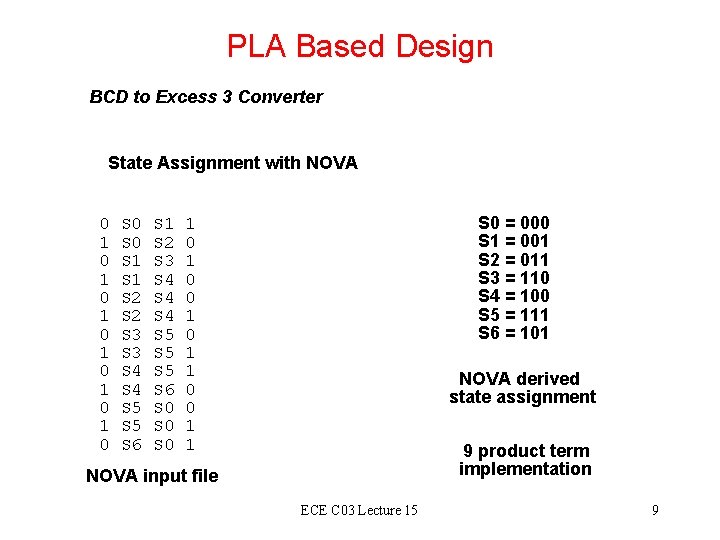

PLA Based Design BCD to Excess 3 Converter State Assignment with NOVA 0 1 0 1 0 1 0 S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 1 S 2 S 3 S 4 S 4 S 5 S 5 S 6 S 0 S 0 = 000 S 1 = 001 S 2 = 011 S 3 = 110 S 4 = 100 S 5 = 111 S 6 = 101 1 0 0 1 1 NOVA derived state assignment 9 product term implementation NOVA input file ECE C 03 Lecture 15 9

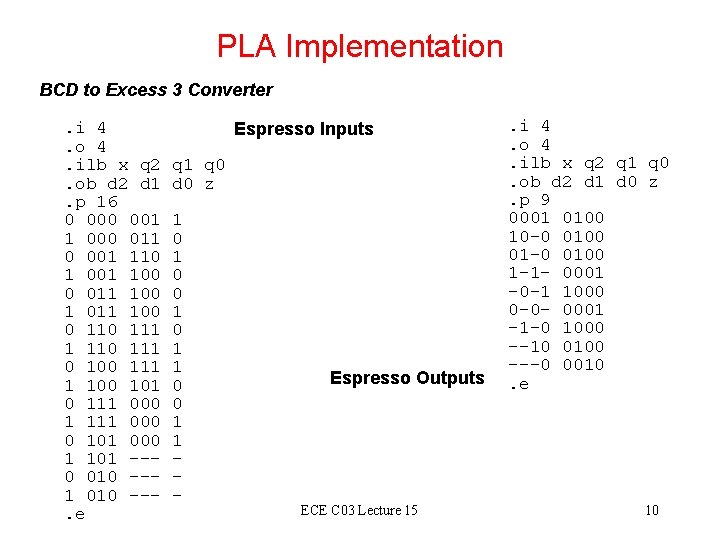

PLA Implementation BCD to Excess 3 Converter. i 4. o 4. ilb x q 2. ob d 2 d 1. p 16 0 001 1 000 011 0 001 110 1 001 100 0 011 100 1 011 100 0 111 1 110 111 0 100 111 1 100 101 0 111 000 1 111 000 0 101 000 1 101 --0 010 --1 010 --. e Espresso Inputs q 1 q 0 d 0 z 1 0 0 1 1 - Espresso Outputs ECE C 03 Lecture 15 . i 4. o 4. ilb x q 2 q 1 q 0. ob d 2 d 1 d 0 z. p 9 0001 0100 10 -0 0100 01 -0 0100 1 -1 - 0001 -0 -1 1000 0 -0 - 0001 -1 -0 1000 --10 0100 ---0 0010. e 10

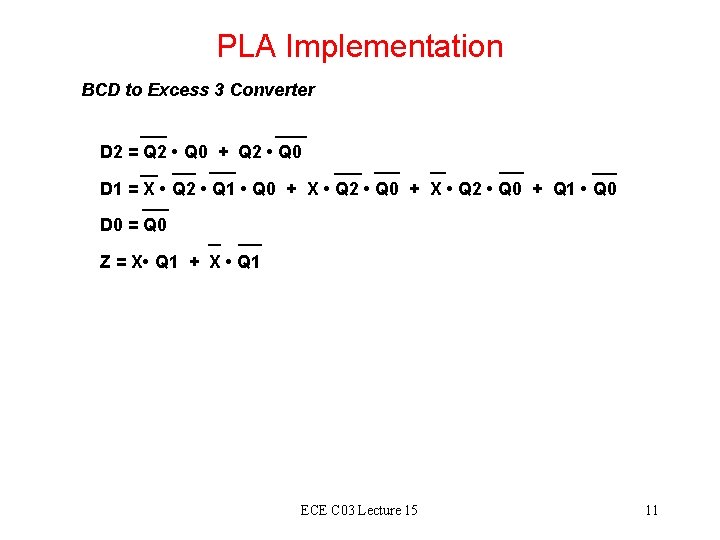

PLA Implementation BCD to Excess 3 Converter D 2 = Q 2 • Q 0 + Q 2 • Q 0 D 1 = X • Q 2 • Q 1 • Q 0 + X • Q 2 • Q 0 + Q 1 • Q 0 D 0 = Q 0 Z = X • Q 1 + X • Q 1 ECE C 03 Lecture 15 11

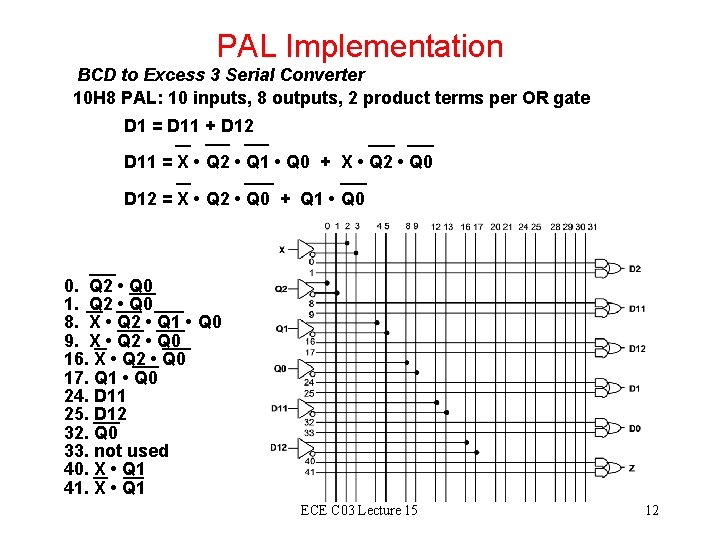

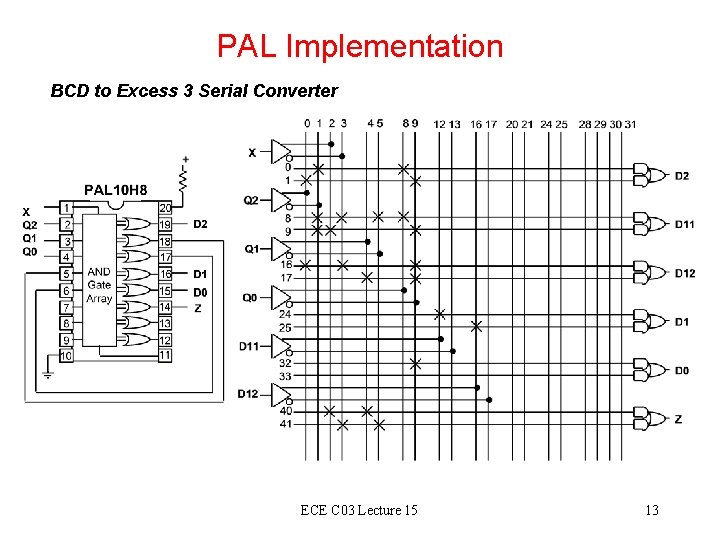

PAL Implementation BCD to Excess 3 Serial Converter 10 H 8 PAL: 10 inputs, 8 outputs, 2 product terms per OR gate D 1 = D 11 + D 12 D 11 = X • Q 2 • Q 1 • Q 0 + X • Q 2 • Q 0 D 12 = X • Q 2 • Q 0 + Q 1 • Q 0 0. Q 2 • Q 0 1. Q 2 • Q 0 8. X • Q 2 • Q 1 • Q 0 9. X • Q 2 • Q 0 16. X • Q 2 • Q 0 17. Q 1 • Q 0 24. D 11 25. D 12 32. Q 0 33. not used 40. X • Q 1 41. X • Q 1 ECE C 03 Lecture 15 12

PAL Implementation BCD to Excess 3 Serial Converter ECE C 03 Lecture 15 13

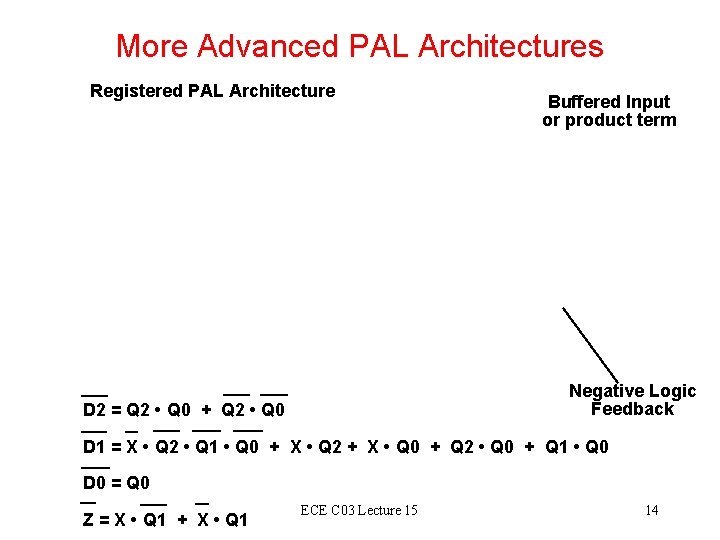

More Advanced PAL Architectures Registered PAL Architecture Buffered Input or product term Negative Logic Feedback D 2 = Q 2 • Q 0 + Q 2 • Q 0 D 1 = X • Q 2 • Q 1 • Q 0 + X • Q 2 + X • Q 0 + Q 2 • Q 0 + Q 1 • Q 0 D 0 = Q 0 Z = X • Q 1 + X • Q 1 ECE C 03 Lecture 15 14

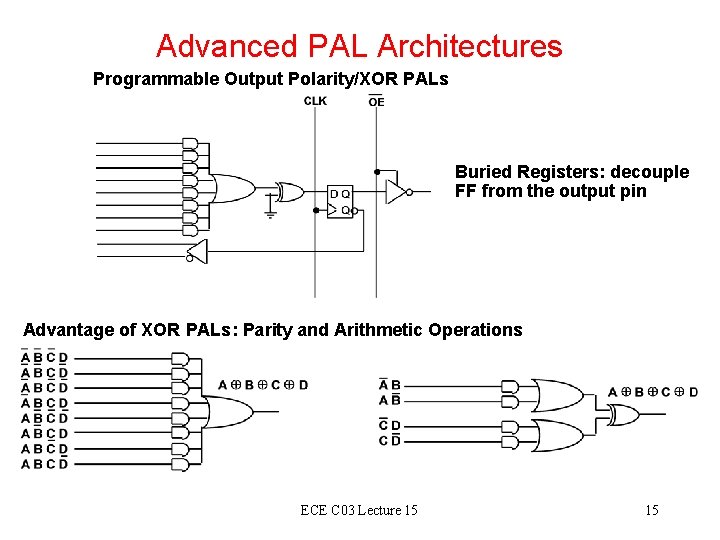

Advanced PAL Architectures Programmable Output Polarity/XOR PALs Buried Registers: decouple FF from the output pin Advantage of XOR PALs: Parity and Arithmetic Operations ECE C 03 Lecture 15 15

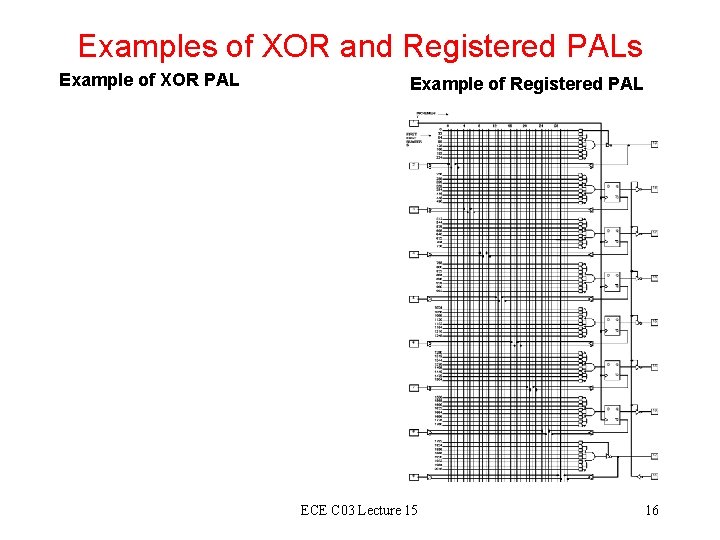

Examples of XOR and Registered PALs Example of XOR PAL Example of Registered PAL ECE C 03 Lecture 15 16

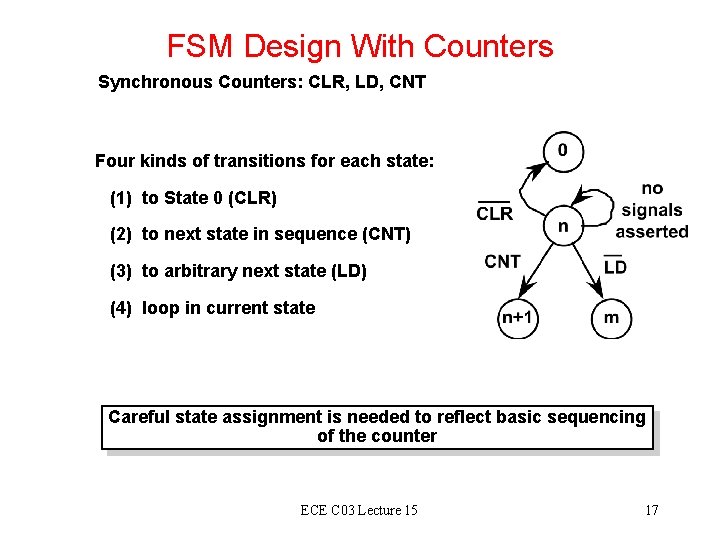

FSM Design With Counters Synchronous Counters: CLR, LD, CNT Four kinds of transitions for each state: (1) to State 0 (CLR) (2) to next state in sequence (CNT) (3) to arbitrary next state (LD) (4) loop in current state Careful state assignment is needed to reflect basic sequencing of the counter ECE C 03 Lecture 15 17

Implementation Strategies FSM Design with Counters Excess 3 Converter Revisited Note the sequential nature of the state assignments ECE C 03 Lecture 15 18

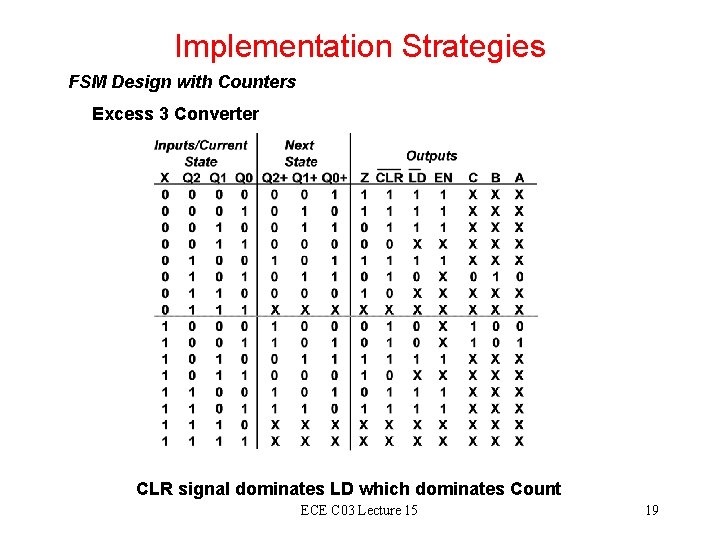

Implementation Strategies FSM Design with Counters Excess 3 Converter CLR signal dominates LD which dominates Count ECE C 03 Lecture 15 19

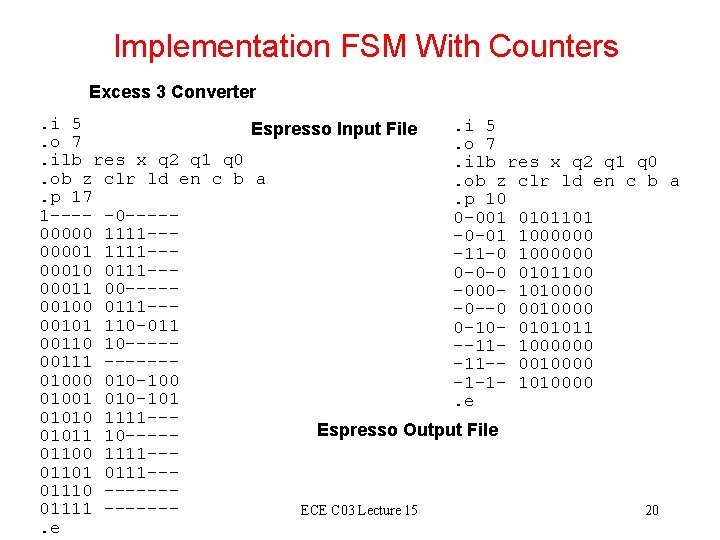

Implementation FSM With Counters Excess 3 Converter. i 5 Espresso Input File. o 7. ilb res x q 2 q 1 q 0. ob z clr ld en c b a. p 17. p 10 1 ---- -0 ----0 -001 0101101 00000 1111 ---0 -01 10000001 1111 ---11 -0 1000000 00010 0111 --0 -0 -0 0101100 00011 00 -----000 - 1010000 00100 0111 ---0 --0 0010000 00101 110 -011 0 -10 - 0101011 00110 10 ------11 - 1000000 00111 -------11 -- 0010000 010 -100 -1 -1 - 1010000 01001 010 -101. e 01010 1111 --Espresso Output File 01011 10 ----01100 1111 --01101 0111 --01110 ------01111 ------ECE C 03 Lecture 15 20. e

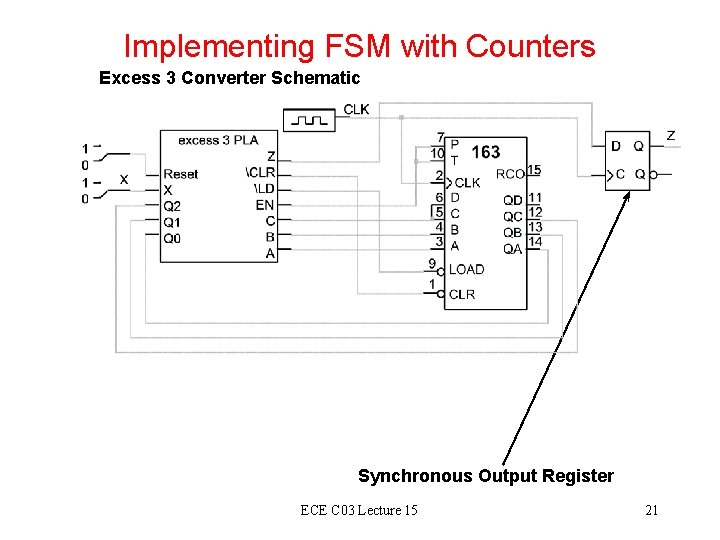

Implementing FSM with Counters Excess 3 Converter Schematic Synchronous Output Register ECE C 03 Lecture 15 21

FSM Design with FPGAs Programmable Logic Devices = PLD PALs, PLAs = 10 - 100 Gate Equivalents Field Programmable Gate Arrays = FPGAs • Altera MAX Family • Actel Programmable Gate Array • Xilinx Logical Cell Array 100 - 1000(s) of Gate Equivalents! ECE C 03 Lecture 15 22

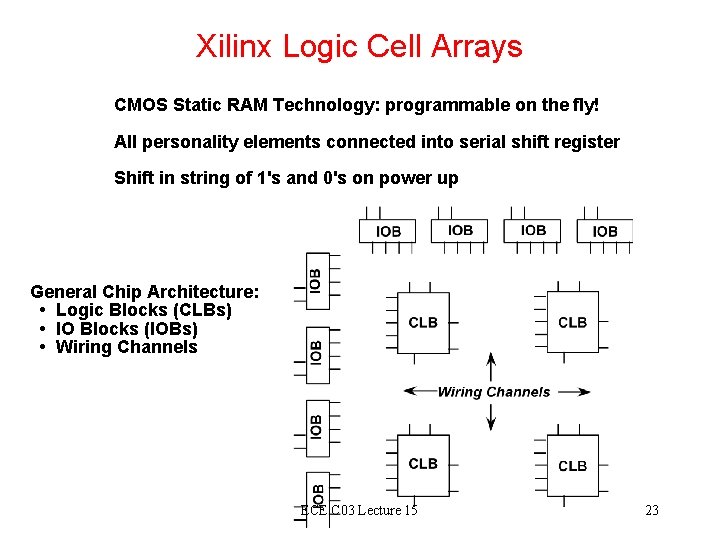

Xilinx Logic Cell Arrays CMOS Static RAM Technology: programmable on the fly! All personality elements connected into serial shift register Shift in string of 1's and 0's on power up General Chip Architecture: • Logic Blocks (CLBs) • IO Blocks (IOBs) • Wiring Channels ECE C 03 Lecture 15 23

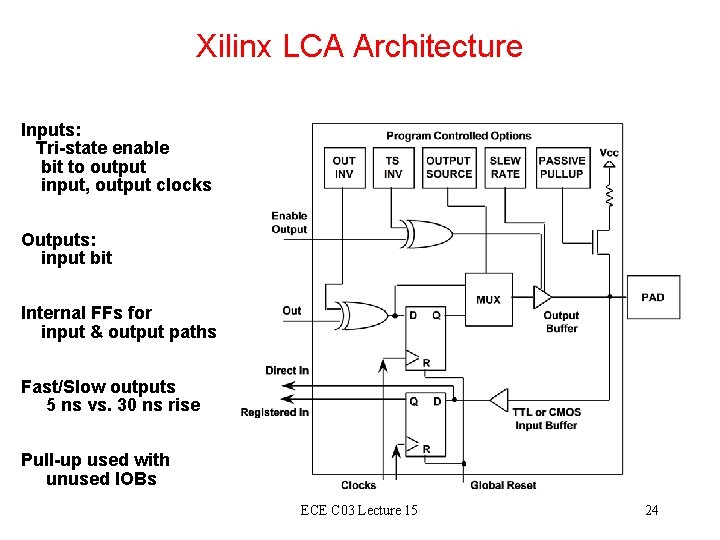

Xilinx LCA Architecture Inputs: Tri-state enable bit to output input, output clocks Outputs: input bit Internal FFs for input & output paths Fast/Slow outputs 5 ns vs. 30 ns rise Pull-up used with unused IOBs ECE C 03 Lecture 15 24

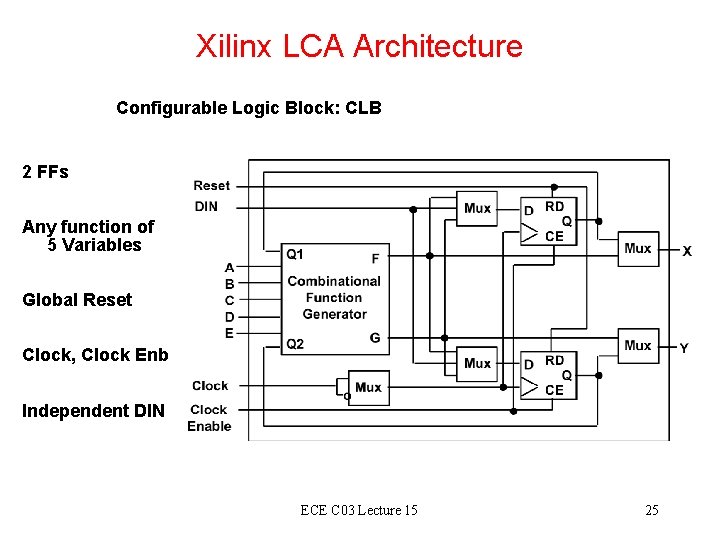

Xilinx LCA Architecture Configurable Logic Block: CLB 2 FFs Any function of 5 Variables Global Reset Clock, Clock Enb Independent DIN ECE C 03 Lecture 15 25

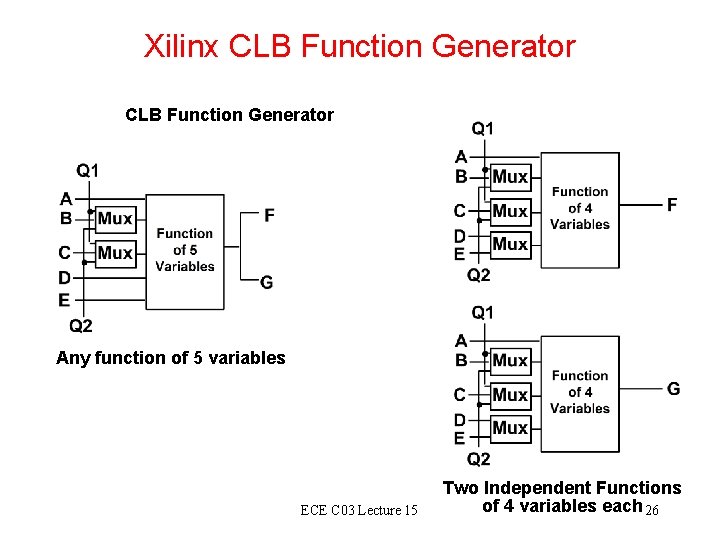

Xilinx CLB Function Generator Any function of 5 variables ECE C 03 Lecture 15 Two Independent Functions of 4 variables each 26

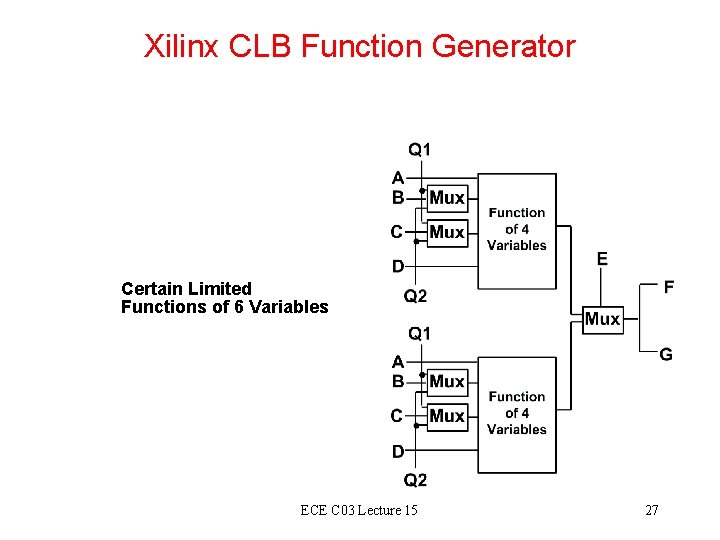

Xilinx CLB Function Generator Certain Limited Functions of 6 Variables ECE C 03 Lecture 15 27

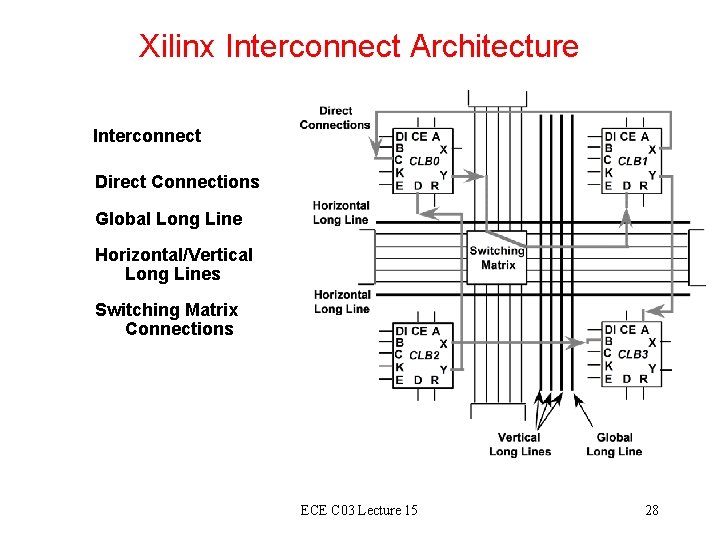

Xilinx Interconnect Architecture Interconnect Direct Connections Global Long Line Horizontal/Vertical Long Lines Switching Matrix Connections ECE C 03 Lecture 15 28

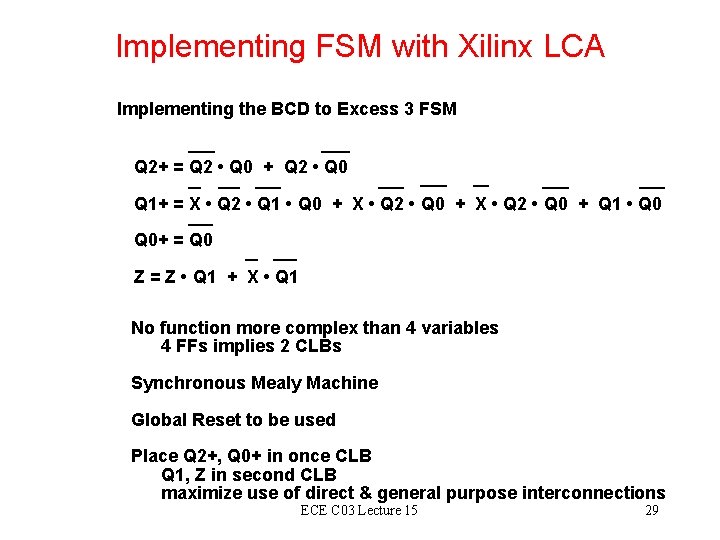

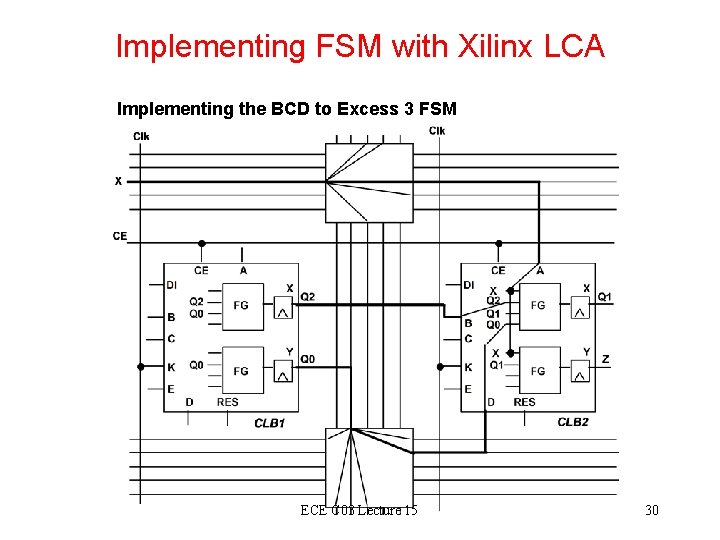

Implementing FSM with Xilinx LCA Implementing the BCD to Excess 3 FSM Q 2+ = Q 2 • Q 0 + Q 2 • Q 0 Q 1+ = X • Q 2 • Q 1 • Q 0 + X • Q 2 • Q 0 + Q 1 • Q 0+ = Q 0 Z = Z • Q 1 + X • Q 1 No function more complex than 4 variables 4 FFs implies 2 CLBs Synchronous Mealy Machine Global Reset to be used Place Q 2+, Q 0+ in once CLB Q 1, Z in second CLB maximize use of direct & general purpose interconnections ECE C 03 Lecture 15 29

Implementing FSM with Xilinx LCA Implementing the BCD to Excess 3 FSM ECE C 03 Lecture 15 30

Summary • • Mapping FSM to random logic Mapping FSM to ROMS Mapping FSM to PLAs Mapping FSM to Programmable Logic Devices (Xilinx) • NEXT LECTURE: VHDL Language • READING: Dewey 11. 2, 11. 3, 11. 4, 11. 5, 11. 6, 12. 2 ECE C 03 Lecture 15 31

- Slides: 31