Lecture 12 RTL Design Methodology Part II SORTING

![Pseudocode FOR k = 4 [load input data] wait for s=1 for i = Pseudocode FOR k = 4 [load input data] wait for s=1 for i =](https://slidetodoc.com/presentation_image_h2/7a911ffc858678574706ee0affdc76a1/image-12.jpg)

- Slides: 14

Lecture 12 RTL Design Methodology Part II: SORTING example

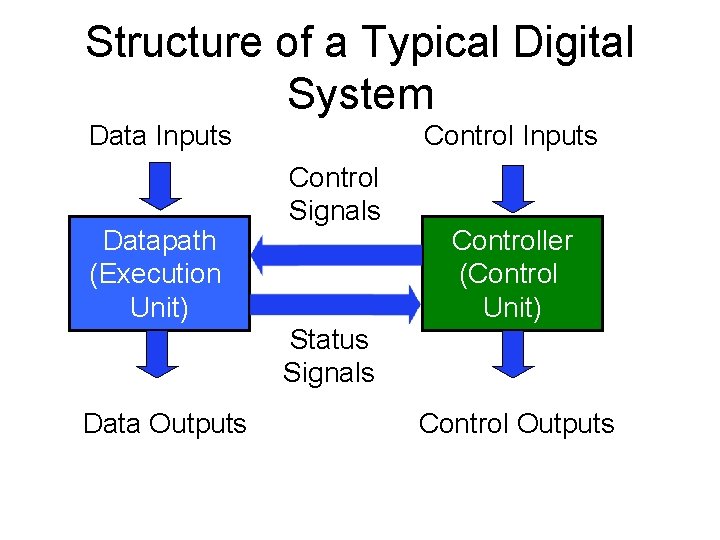

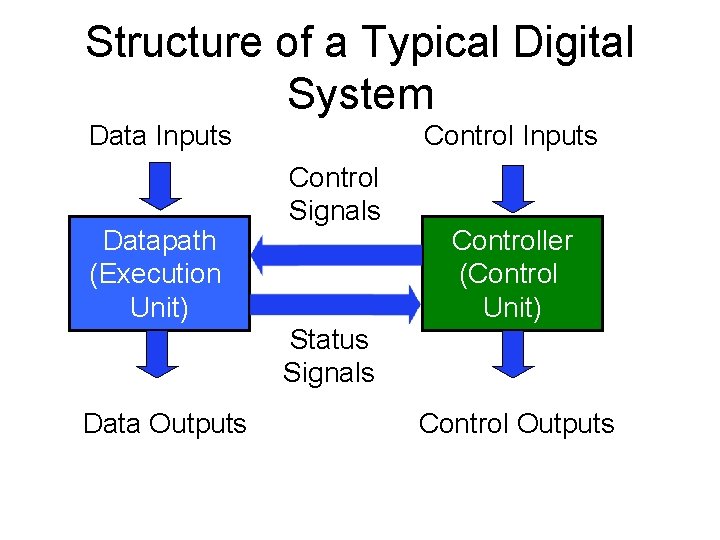

Structure of a Typical Digital System Data Inputs Datapath (Execution Unit) Control Inputs Control Signals Controller (Control Unit) Status Signals Data Outputs Control Outputs

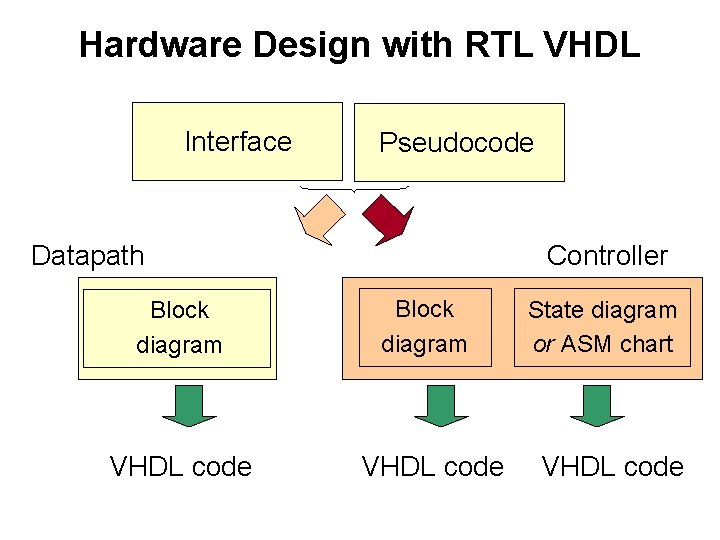

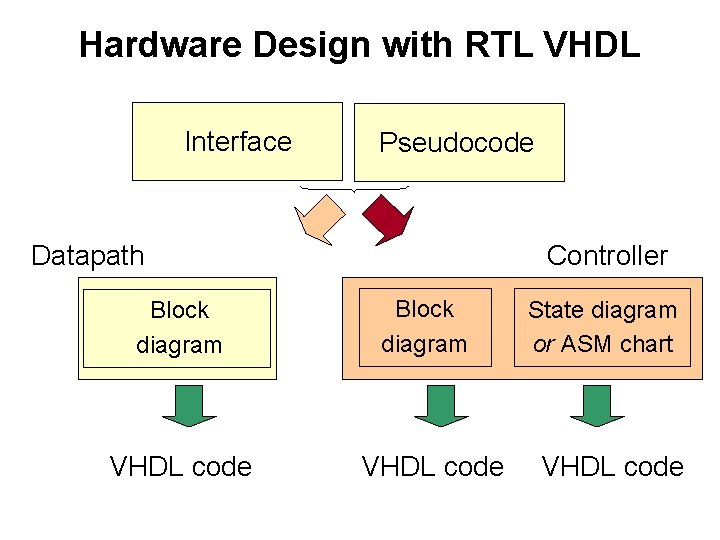

Hardware Design with RTL VHDL Interface Pseudocode Datapath Block diagram VHDL code Controller Block diagram VHDL code State diagram or ASM chart VHDL code

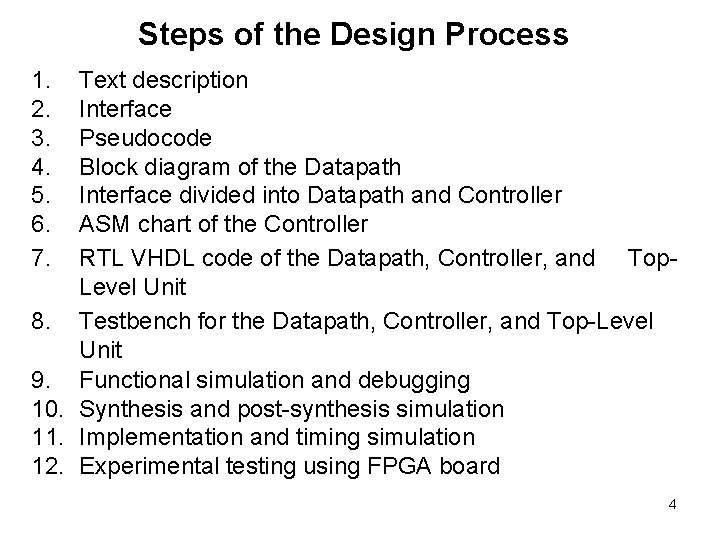

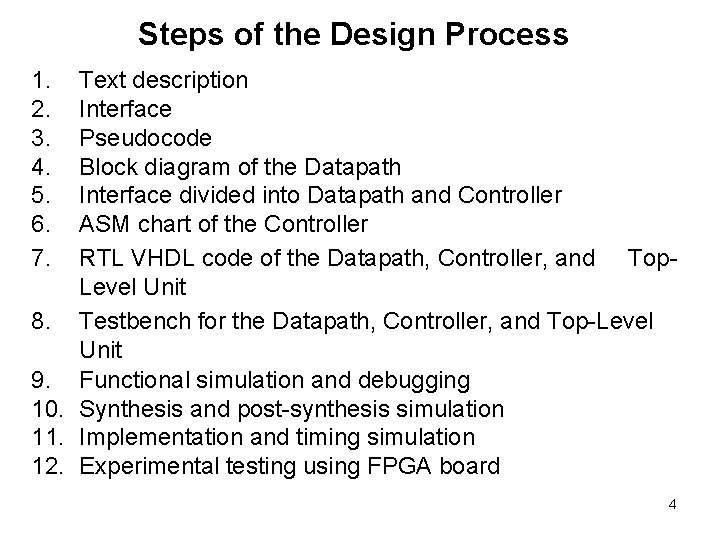

Steps of the Design Process 1. 2. 3. 4. 5. 6. 7. Text description Interface Pseudocode Block diagram of the Datapath Interface divided into Datapath and Controller ASM chart of the Controller RTL VHDL code of the Datapath, Controller, and Top. Level Unit 8. Testbench for the Datapath, Controller, and Top-Level Unit 9. Functional simulation and debugging 10. Synthesis and post-synthesis simulation 11. Implementation and timing simulation 12. Experimental testing using FPGA board 4

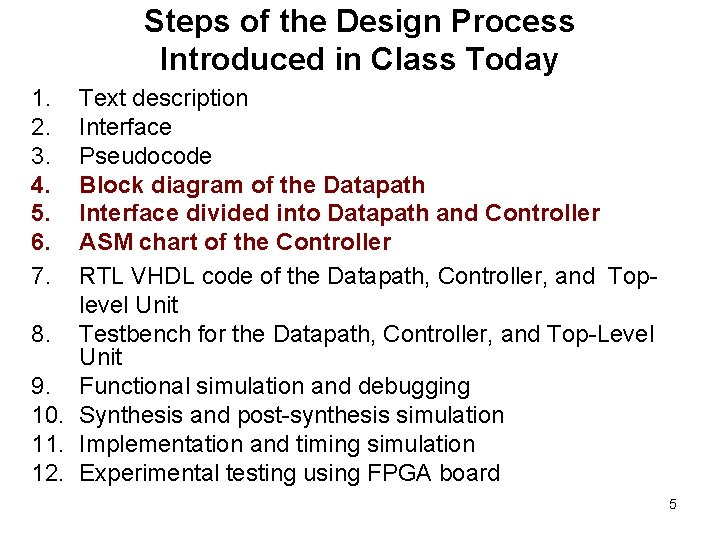

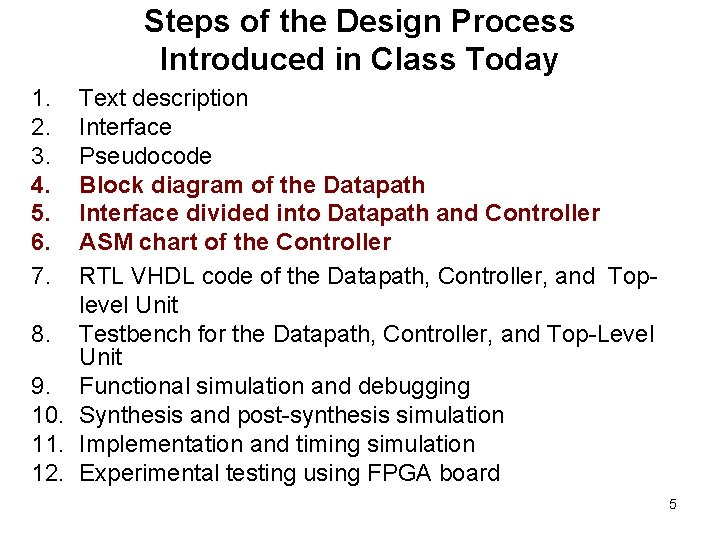

Steps of the Design Process Introduced in Class Today 1. 2. 3. 4. 5. 6. 7. Text description Interface Pseudocode Block diagram of the Datapath Interface divided into Datapath and Controller ASM chart of the Controller RTL VHDL code of the Datapath, Controller, and Toplevel Unit 8. Testbench for the Datapath, Controller, and Top-Level Unit 9. Functional simulation and debugging 10. Synthesis and post-synthesis simulation 11. Implementation and timing simulation 12. Experimental testing using FPGA board 5

SORTING example

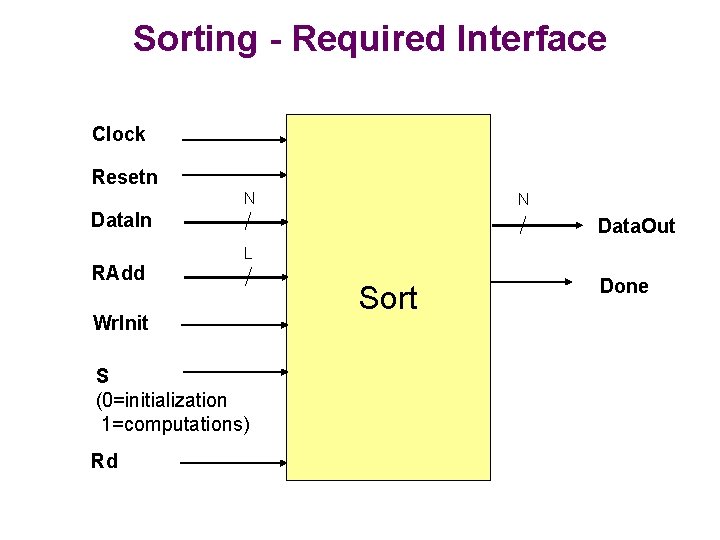

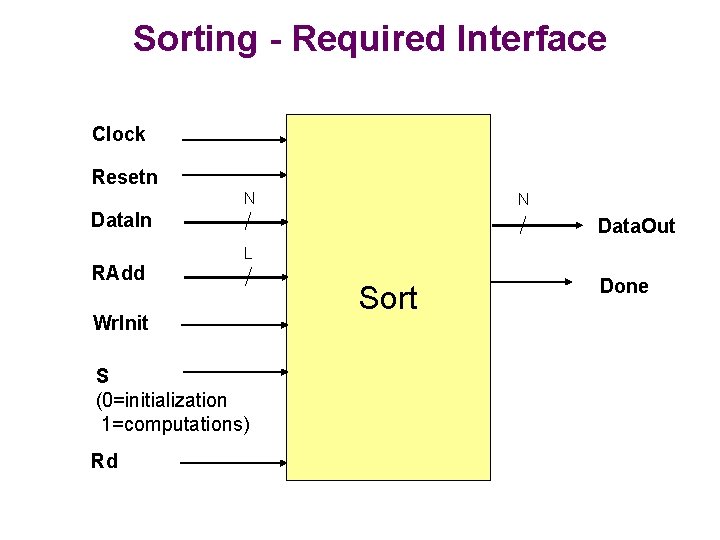

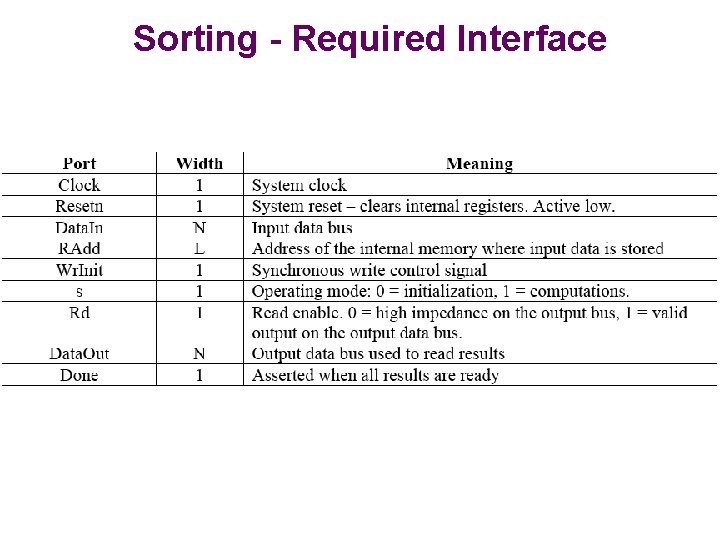

Sorting - Required Interface Clock Resetn N N Data. In RAdd Data. Out L Wr. Init S (0=initialization 1=computations) Rd Sort Done

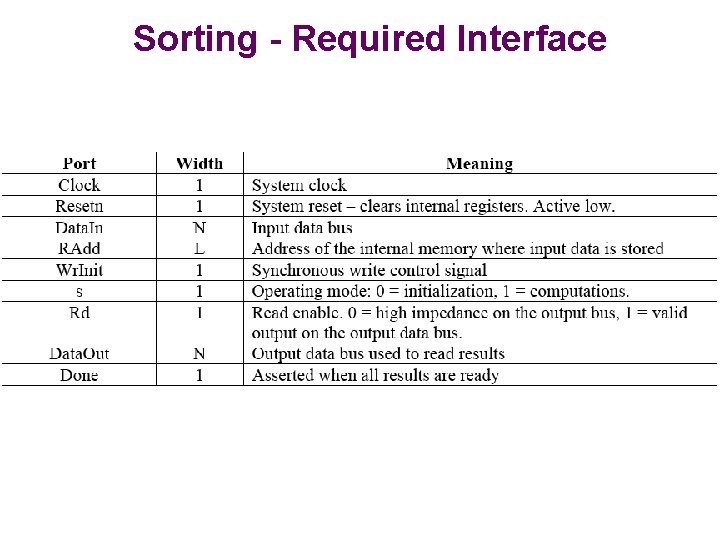

Sorting - Required Interface

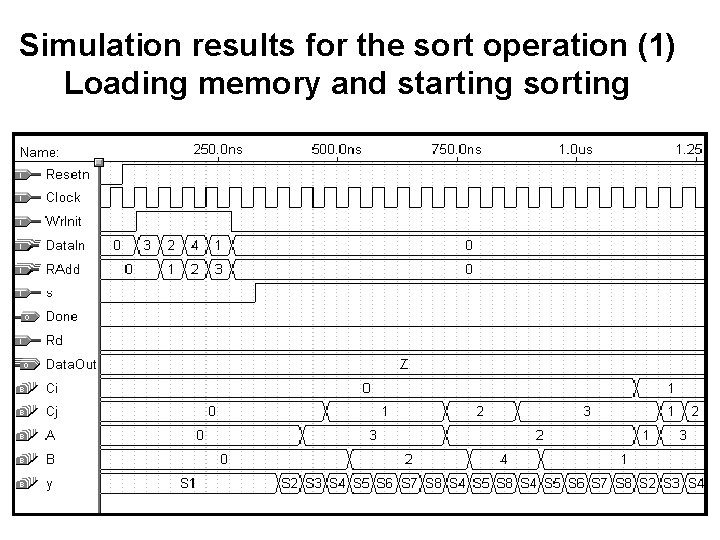

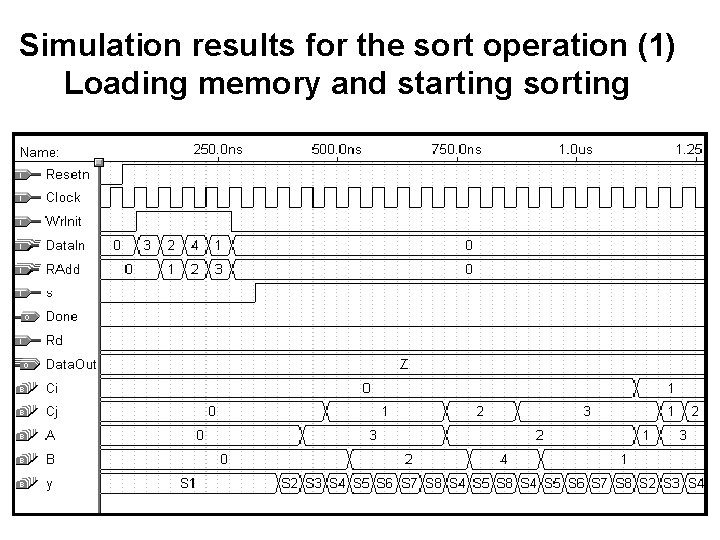

Simulation results for the sort operation (1) Loading memory and starting sorting

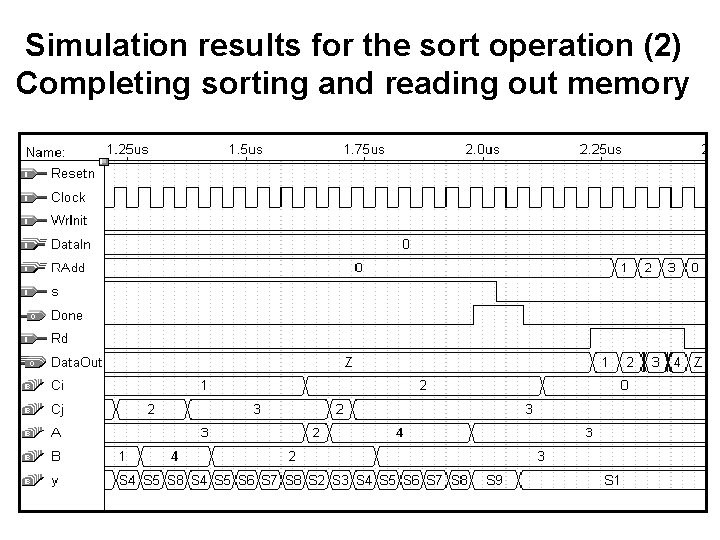

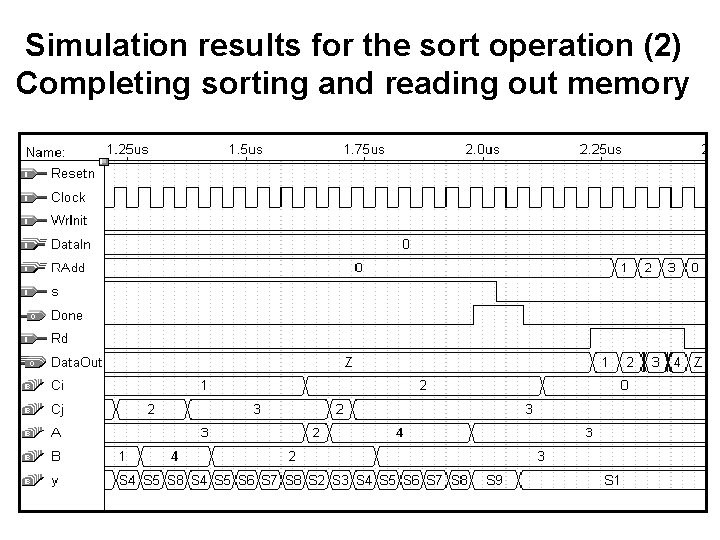

Simulation results for the sort operation (2) Completing sorting and reading out memory

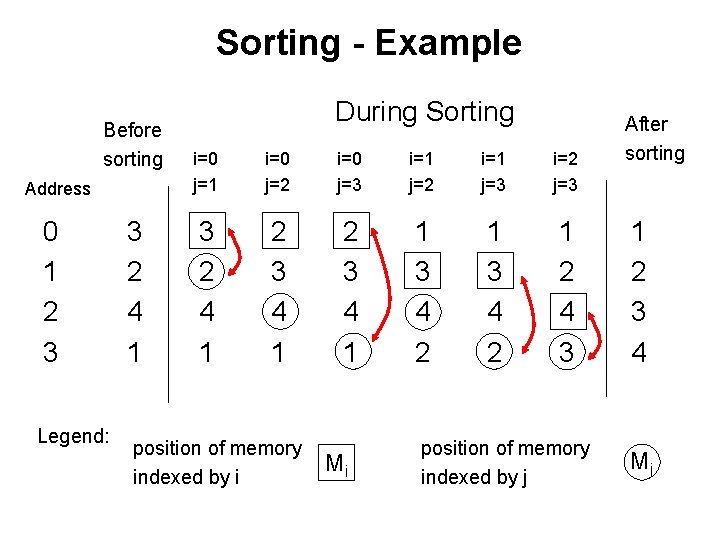

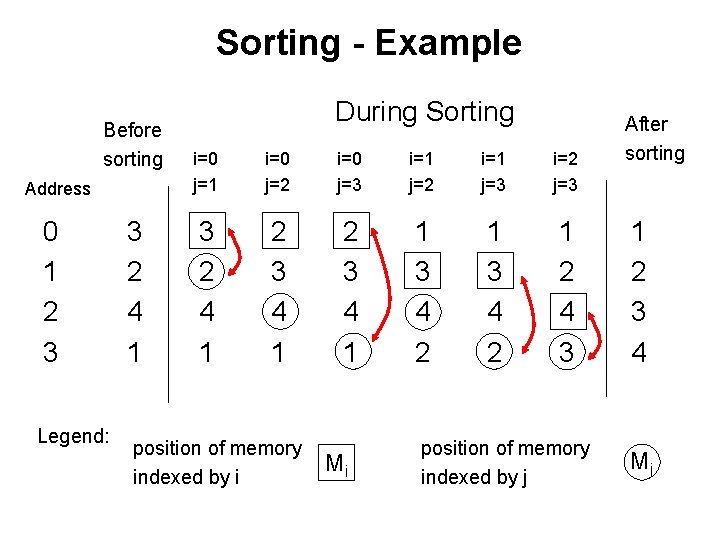

Sorting - Example Before sorting Address 0 1 2 3 Legend: 3 2 4 1 During Sorting i=0 j=1 i=0 j=2 i=0 j=3 i=1 j=2 i=1 j=3 i=2 j=3 3 2 4 1 2 3 4 1 1 3 4 2 1 2 4 3 position of memory indexed by i Mi position of memory indexed by j After sorting 1 2 3 4 Mj

![Pseudocode FOR k 4 load input data wait for s1 for i Pseudocode FOR k = 4 [load input data] wait for s=1 for i =](https://slidetodoc.com/presentation_image_h2/7a911ffc858678574706ee0affdc76a1/image-12.jpg)

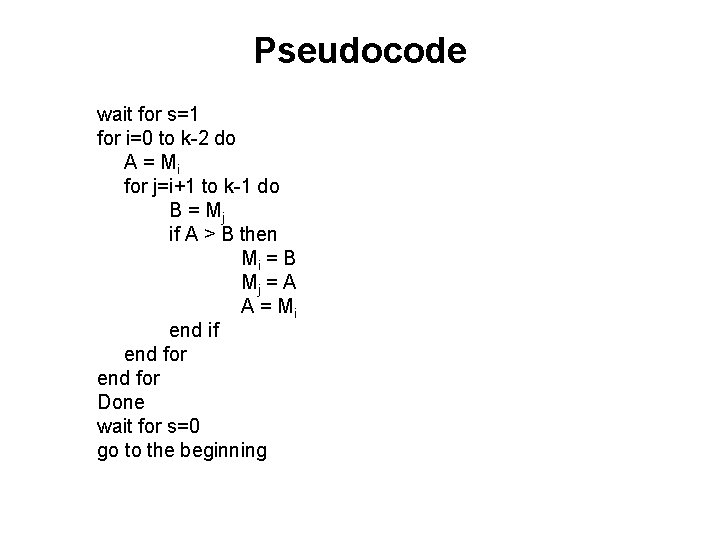

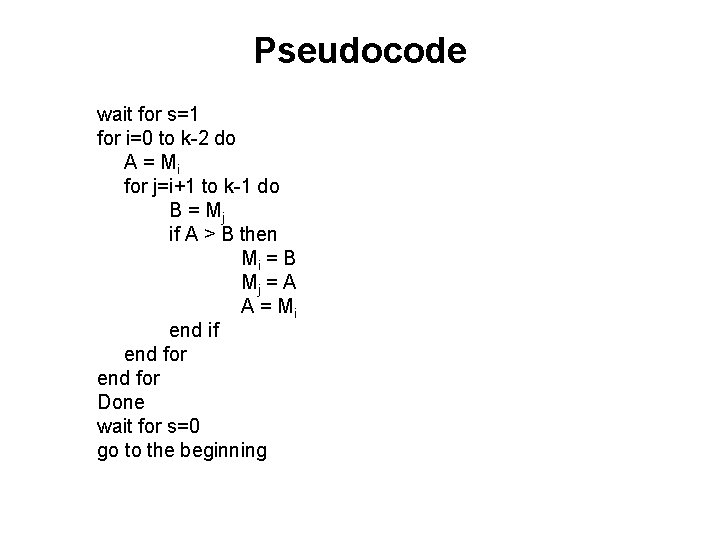

Pseudocode FOR k = 4 [load input data] wait for s=1 for i = 0 to 2 do A = Mi ; for j = i + 1 to 3 do B = Mj ; if B < A then Mi = B ; Mj = A ; A = Mi ; endif ; endfor; Done wait for s=0 [read output data] go to the beginning FOR any k ≥ 2 [load input data] wait for s=1 for i = 0 to k -2 do A = Mi ; for j = i + 1 to k – 1 do B = Mj ; if B < A then Mi = B ; Mj = A ; A = Mi ; endif ; endfor; Done wait for s=0 [read output data] go to the beginning

Pseudocode wait for s=1 for i=0 to k-2 do A = Mi for j=i+1 to k-1 do B = Mj if A > B then Mi = B Mj = A A = Mi end if end for Done wait for s=0 go to the beginning

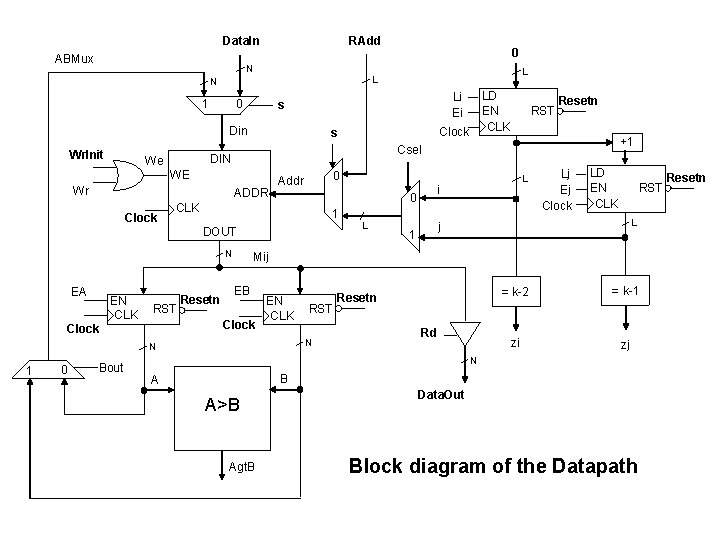

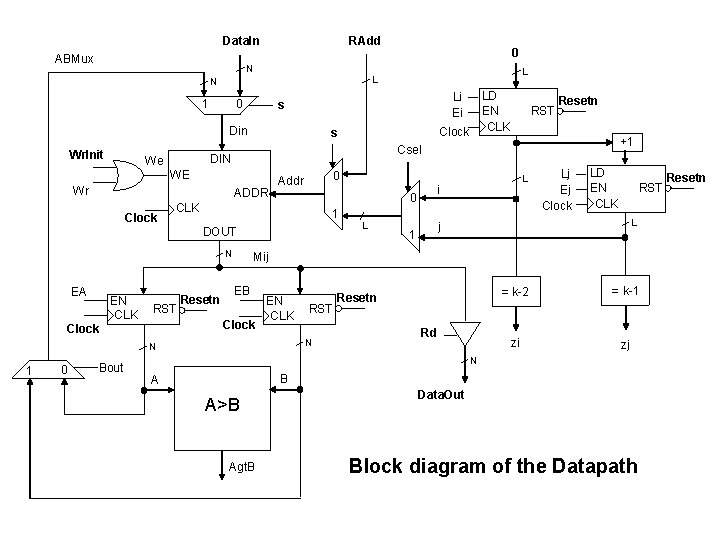

Data. In ABMux RAdd 1 0 Wr ADDR 1 RST Resetn EB EN CLK Bout RST N N 0 Lj Ej Clock LD EN CLK RST L j 1 Mij Clock L L i 0 CLK N EN CLK Resetn +1 0 Addr DOUT EA RST Csel WE Clock s DIN We LD EN CLK Li Ei s Din Wr. Init L L N 1 0 N Resetn Rd = k-2 = k-1 zi zj N B A A>B Agt. B Data. Out Block diagram of the Datapath Resetn