Lecture 10 Combinational ATPG and Logic Redundancy n

Lecture 10 Combinational ATPG and Logic Redundancy n n Redundancy identification Redundancy removal Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 1

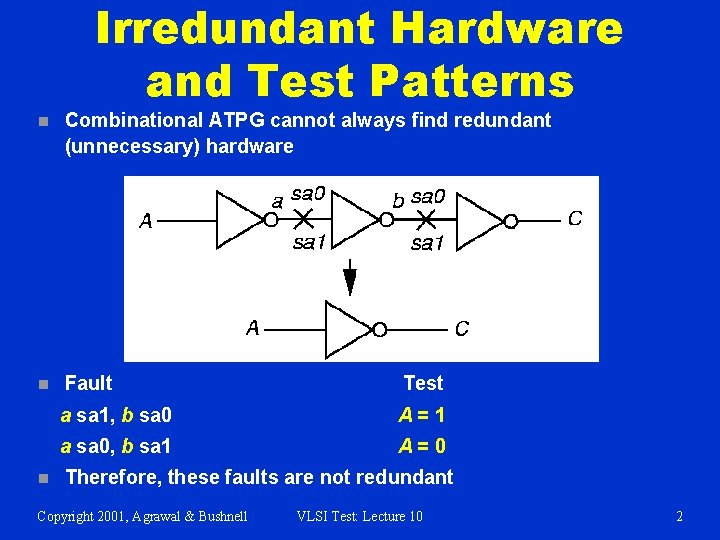

Irredundant Hardware and Test Patterns n Combinational ATPG cannot always find redundant (unnecessary) hardware n Fault Test a sa 1, b sa 0 A=1 a sa 0, b sa 1 A=0 n Therefore, these faults are not redundant Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 2

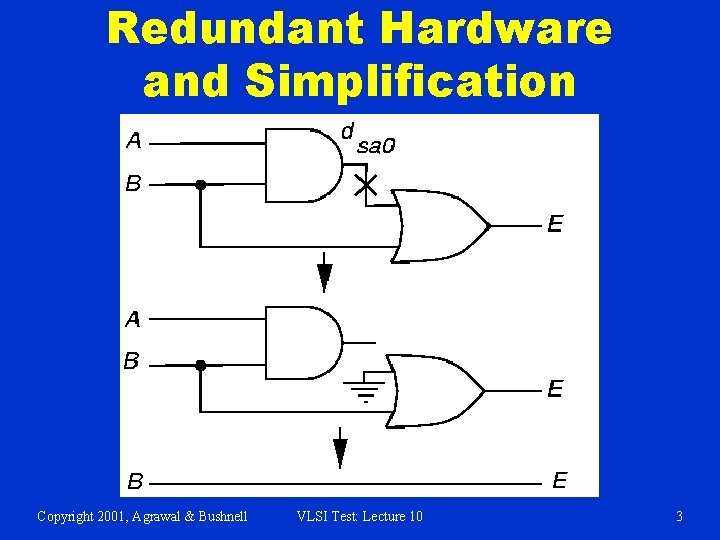

Redundant Hardware and Simplification Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 3

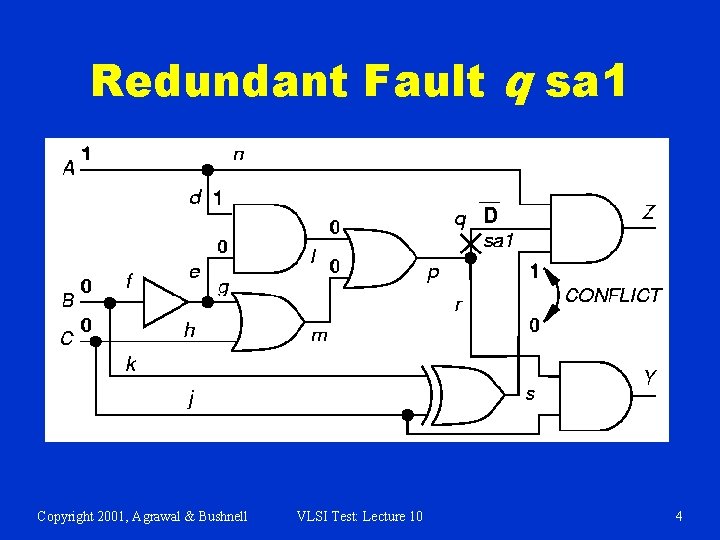

Redundant Fault q sa 1 Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 4

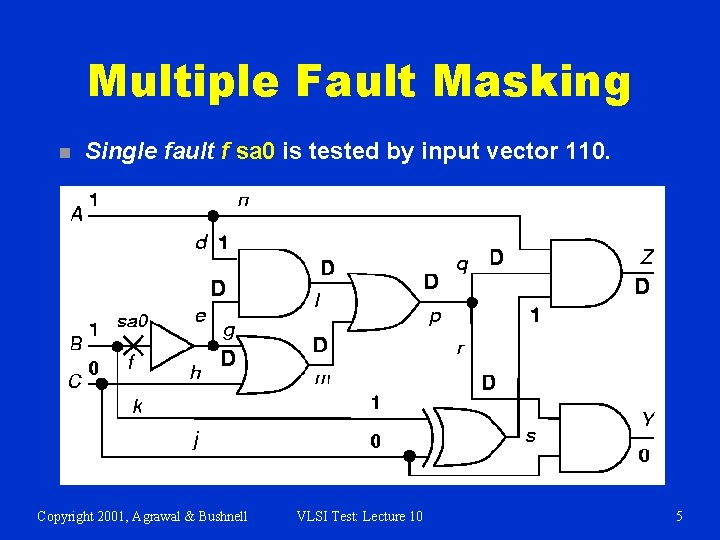

Multiple Fault Masking n Single fault f sa 0 is tested by input vector 110. Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 5

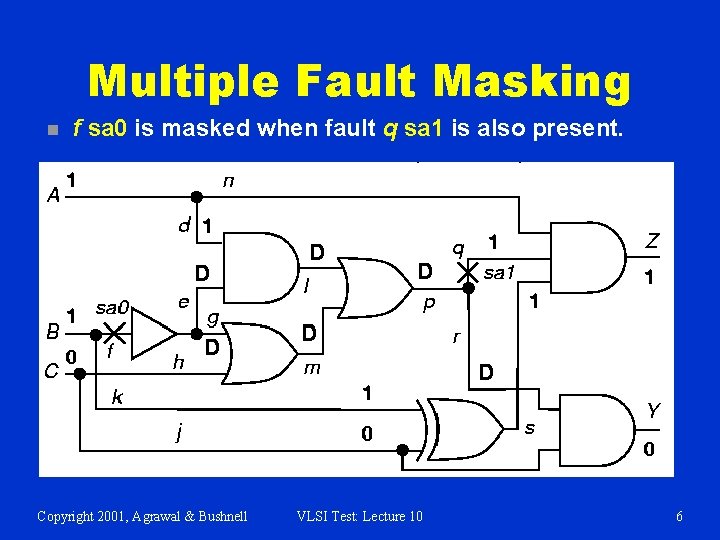

Multiple Fault Masking n f sa 0 is masked when fault q sa 1 is also present. Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 6

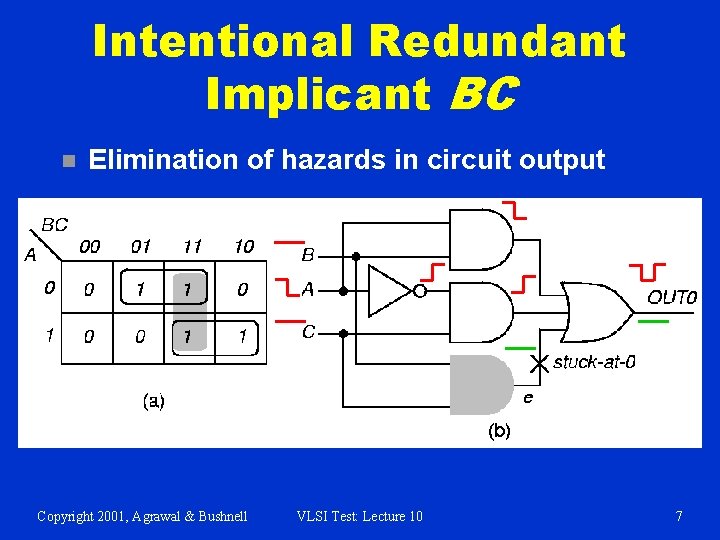

Intentional Redundant Implicant BC n Elimination of hazards in circuit output Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 7

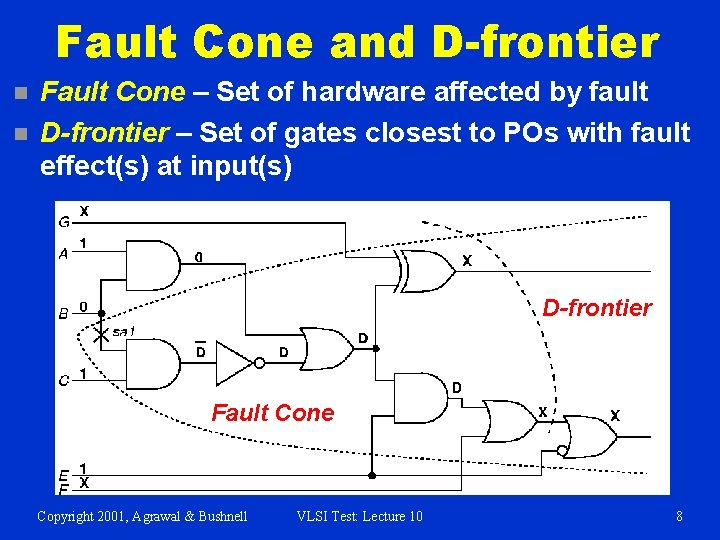

Fault Cone and D-frontier n n Fault Cone – Set of hardware affected by fault D-frontier – Set of gates closest to POs with fault effect(s) at input(s) D-frontier Fault Cone Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 8

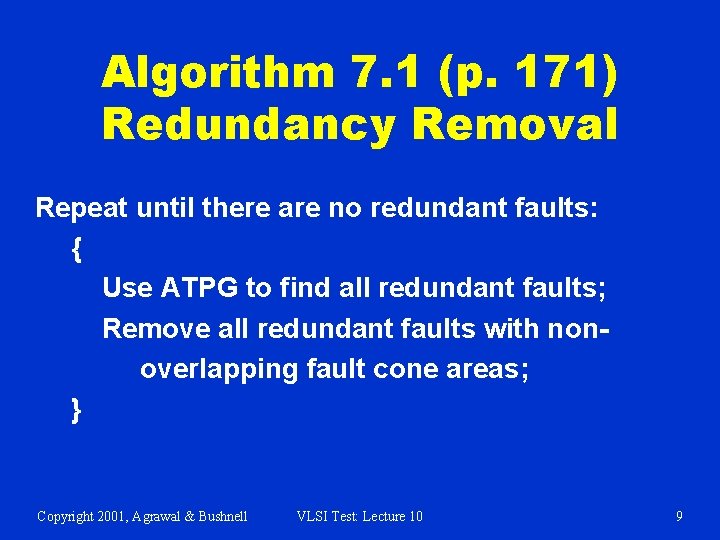

Algorithm 7. 1 (p. 171) Redundancy Removal Repeat until there are no redundant faults: { Use ATPG to find all redundant faults; Remove all redundant faults with nonoverlapping fault cone areas; } Copyright 2001, Agrawal & Bushnell VLSI Test: Lecture 10 9

- Slides: 9