Lecture 1 Introduction to Digital Logic Design CK

- Slides: 17

Lecture 1: Introduction to Digital Logic Design CK Cheng CSE Dept. UC San Diego 1

Outlines • Administration • Motivation • Scope 2

Administration Web site: http: //www. cse. ucsd. edu/classes/fa 10/cse 140/ Web. CT: http: //webct. ucsd. edu 3

Administration Instructor: CK Cheng, CSE 2130, ckcheng+140@ucsd. edu, 858 534 -6184 Teaching Assistants: • • Swathi Karunamurthy skarunam@ucsd. edu Murali Vikram m_vikram_1987@yahoo. com Shams Pirani spirani@ucsd. edu Gopi Krishna Tummala gopi. tummala@gmail. com 4

Administration Schedule • Outline (Use index to check the location of the textbooks) • Lectures: 3: 30 -4: 50 PM, TTh, Center 113. • Discussion: 4: 00 -4: 50 PM, M, Center 109. • Office hours: 1: 00 -2: 00 PM, TTh, CSE 2130. 5

Administration Textbooks • (H) Digital Design and Computer Architecture, D. M. Harris and S. L. Harris, Morgan Kaufmann, 2007. • (S) Introduction to Digital Systems, J. Palmer and D. Perlman, Schaum's ou. Tlines, 1993. Grading • Midterm 1: 25% (T 10/12) • Midterm 2: 30% (T 11/02) • Final Exam: 40% (3: 00 -6: 00 PM, M 12/06) 6

Motivation • Microelectronic technologies have revolutionized our world: cell phones, internet, rapid advances in medicine, etc. • The semiconductor industry has grown from $21 billion in 1985 to $268 billion in 2007. 7

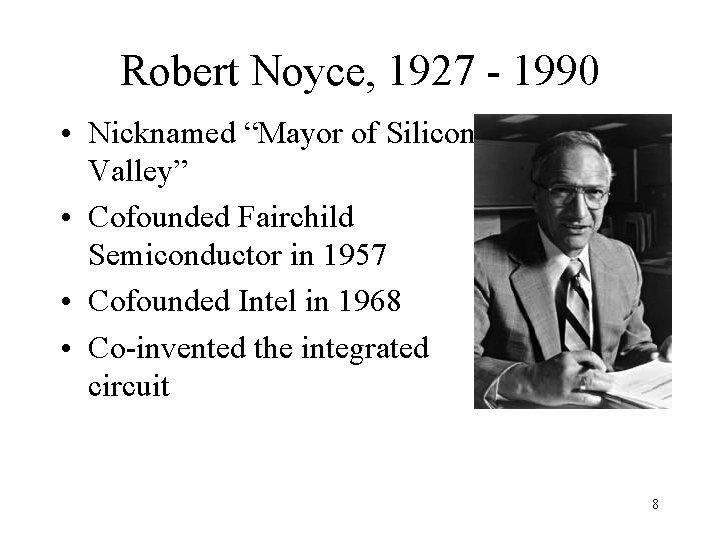

Robert Noyce, 1927 - 1990 • Nicknamed “Mayor of Silicon Valley” • Cofounded Fairchild Semiconductor in 1957 • Cofounded Intel in 1968 • Co-invented the integrated circuit 8

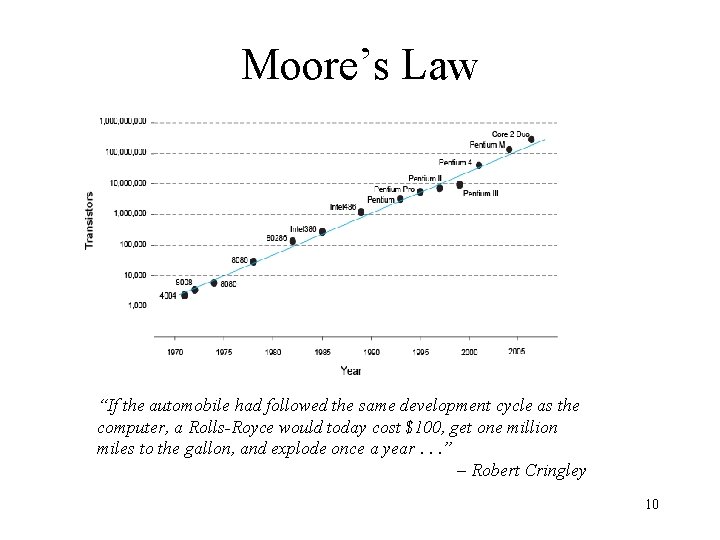

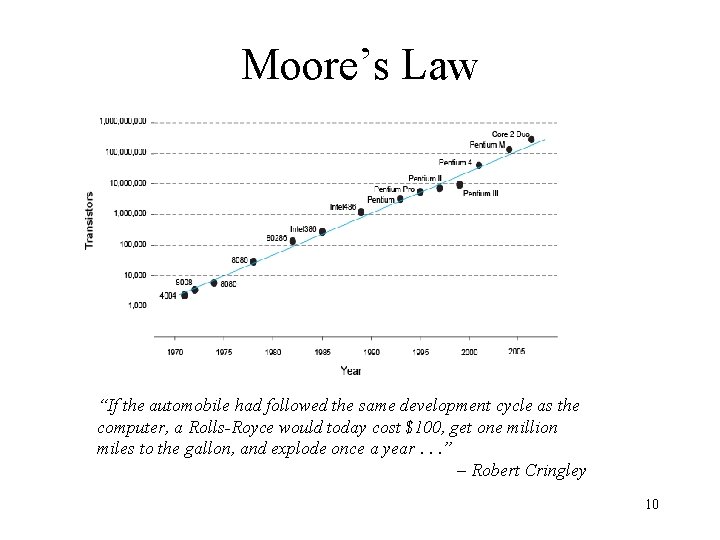

Gordon Moore, 1929 • Cofounded Intel in 1968 with Robert Noyce. • Moore’s Law: the number of transistors on a computer chip doubles every year (observed in 1965) • Since 1975, transistor counts have doubled every two years. 9

Moore’s Law “If the automobile had followed the same development cycle as the computer, a Rolls-Royce would today cost $100, get one million miles to the gallon, and explode once a year. . . ” – Robert Cringley 10

Scope • The purpose of this course is that we: – Learn what’s under the hood of an electronic component – Learn the principles of digital design – Learn to systematically debug increasingly complex designs – Design and build digital systems 11

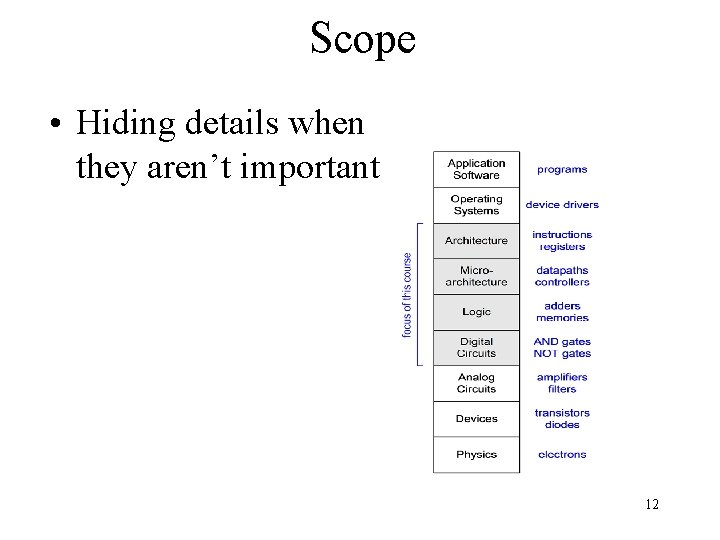

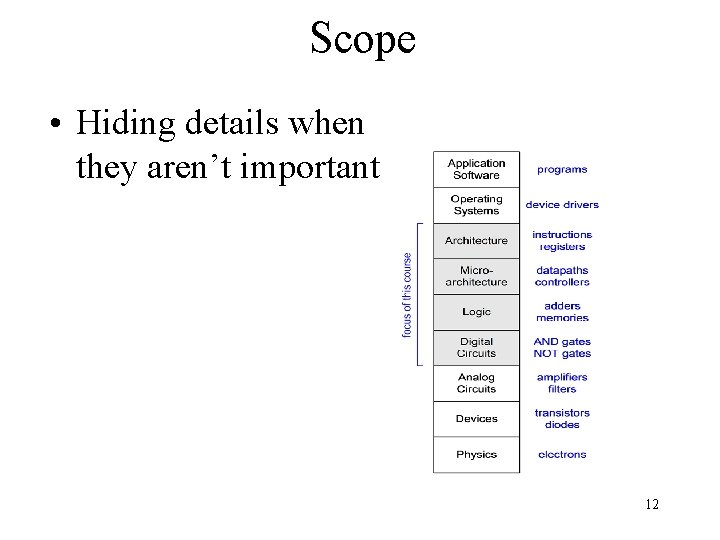

Scope • Hiding details when they aren’t important 12

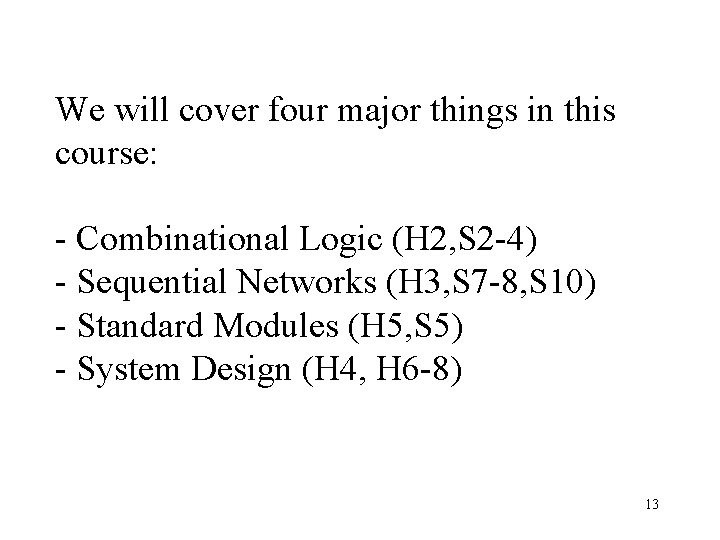

We will cover four major things in this course: - Combinational Logic (H 2, S 2 -4) - Sequential Networks (H 3, S 7 -8, S 10) - Standard Modules (H 5, S 5) - System Design (H 4, H 6 -8) 13

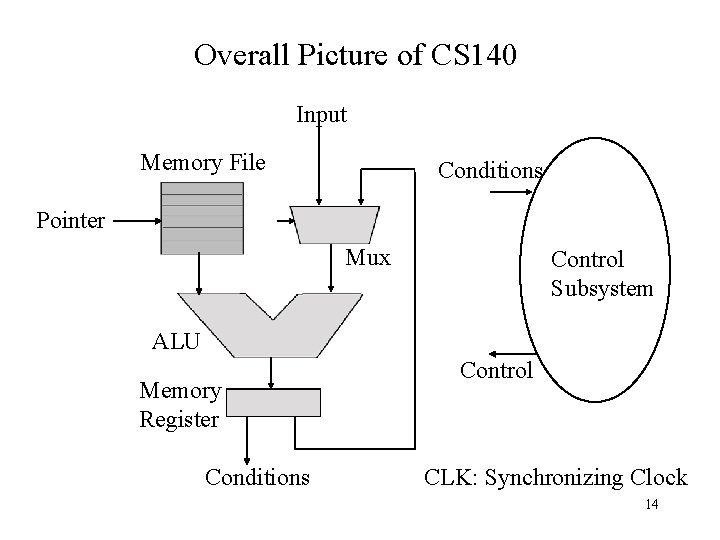

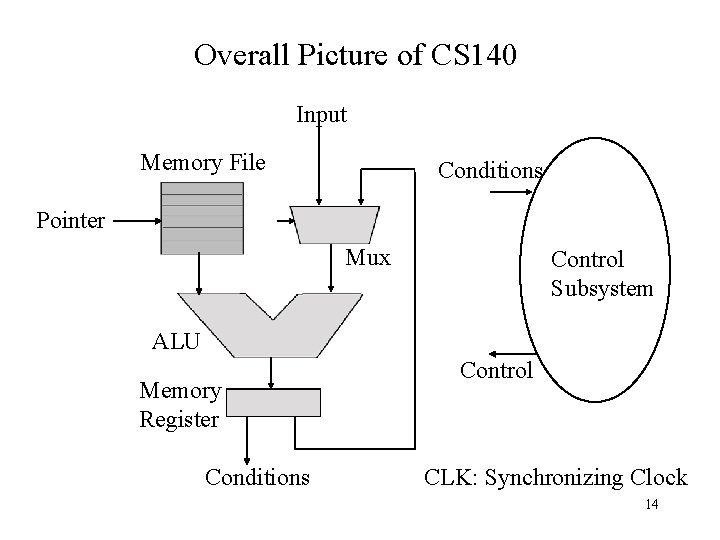

Overall Picture of CS 140 Input Memory File Conditions Pointer Mux Control Subsystem ALU Memory Register Conditions Control CLK: Synchronizing Clock 14

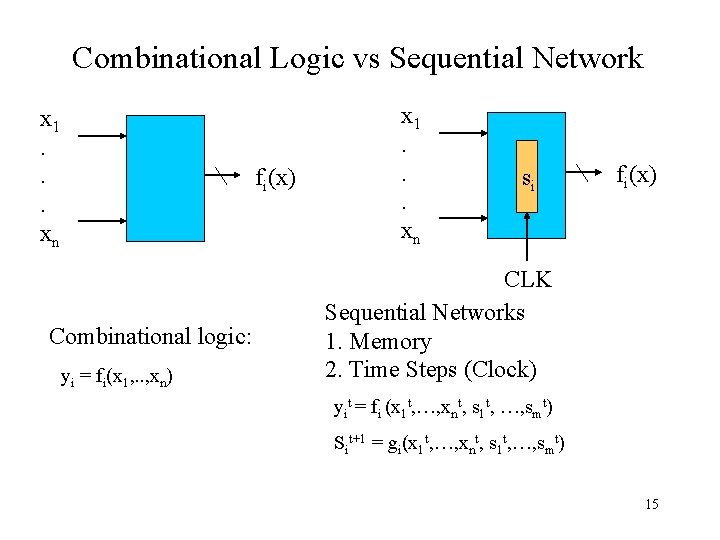

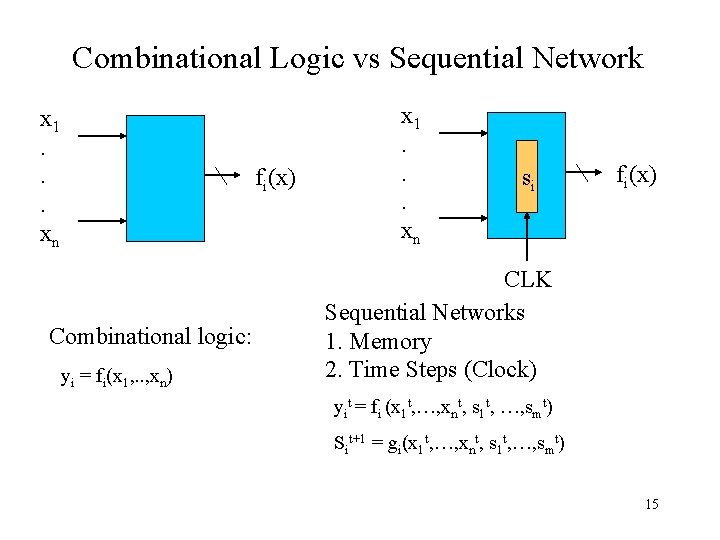

Combinational Logic vs Sequential Network x 1. . . xn fi(x) Combinational logic: yi = fi(x 1, . . , xn) x 1. . . xn si fi(x) CLK Sequential Networks 1. Memory 2. Time Steps (Clock) yit = fi (x 1 t, …, xnt, s 1 t, …, smt) Sit+1 = gi(x 1 t, …, xnt, s 1 t, …, smt) 15

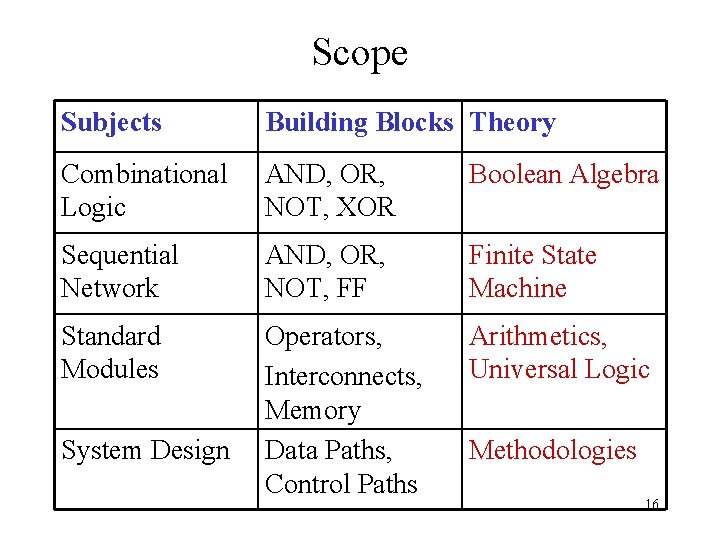

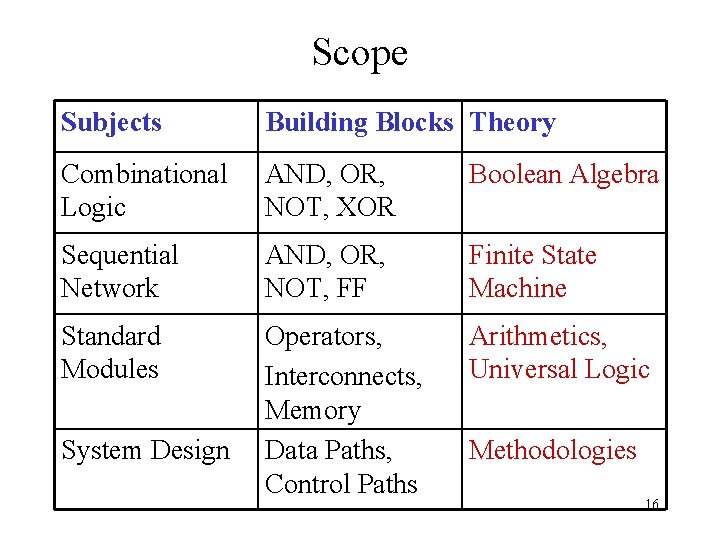

Scope Subjects Building Blocks Theory Combinational Logic AND, OR, NOT, XOR Boolean Algebra Sequential Network AND, OR, NOT, FF Finite State Machine Standard Modules Operators, Interconnects, Memory Data Paths, Control Paths Arithmetics, Universal Logic System Design Methodologies 16

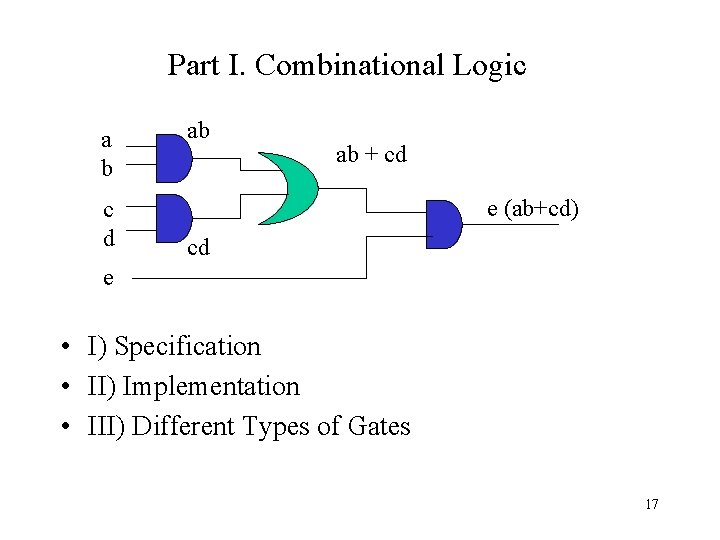

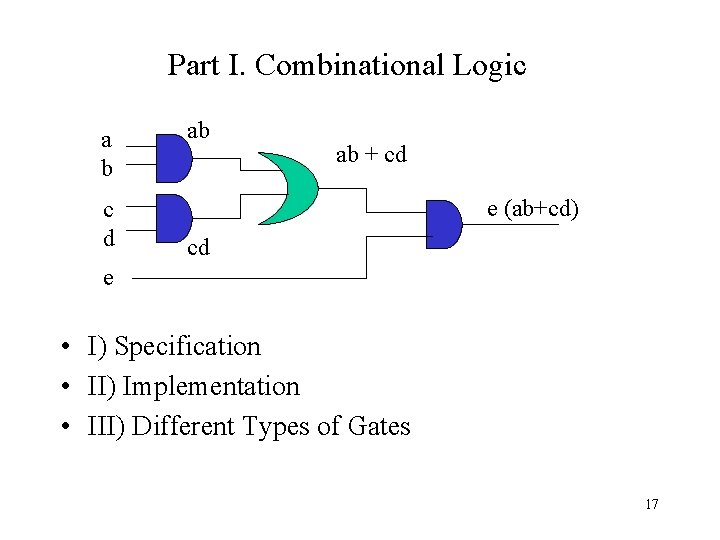

Part I. Combinational Logic a b c d ab ab + cd e (ab+cd) cd e • I) Specification • II) Implementation • III) Different Types of Gates 17