Le Microcontrleur 8051 1 Jelassi Khaled Microcontrleur Plan

- Slides: 121

Le Micro-contrôleur 8051 1 Jelassi Khaled Microcontrôleur

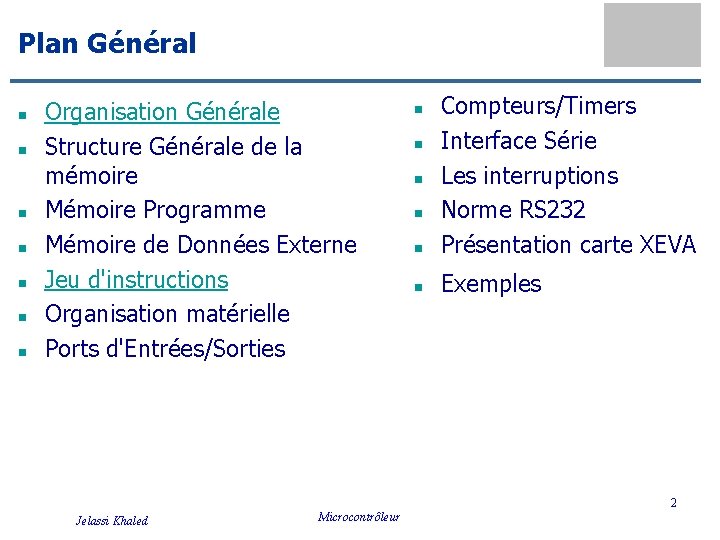

Plan Général n n n n Organisation Générale Structure Générale de la mémoire Mémoire Programme Mémoire de Données Externe Jeu d'instructions Organisation matérielle Ports d'Entrées/Sorties n Compteurs/Timers Interface Série Les interruptions Norme RS 232 Présentation carte XEVA n Exemples n n 2 Jelassi Khaled Microcontrôleur

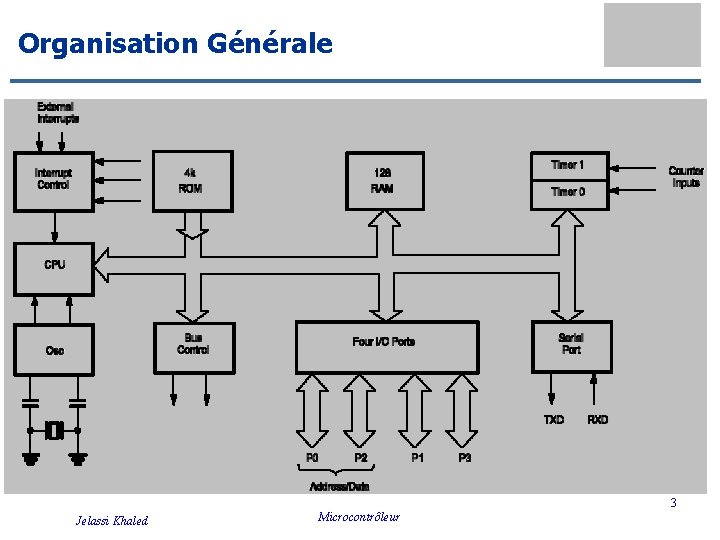

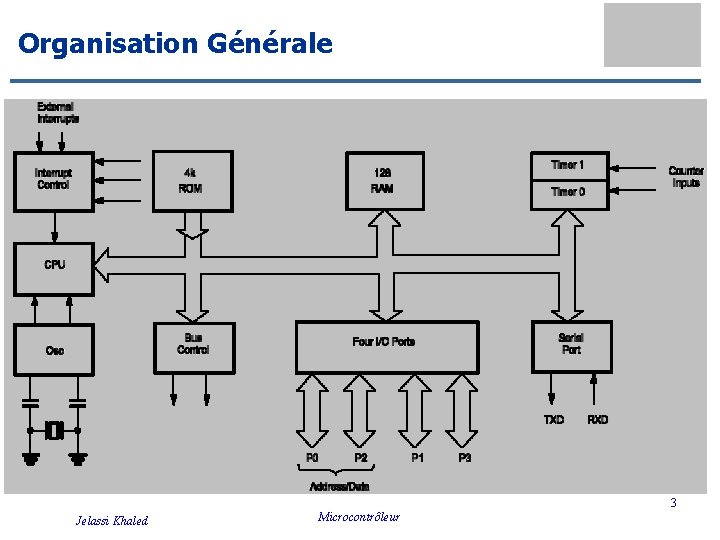

Organisation Générale Schéma Bloc 3 Jelassi Khaled Microcontrôleur

Structure Générale de la mémoire Cartographie n On appelle cartographie mémoire ou memory mapping l'organisation géographique de la mémoire 4 Jelassi Khaled Microcontrôleur

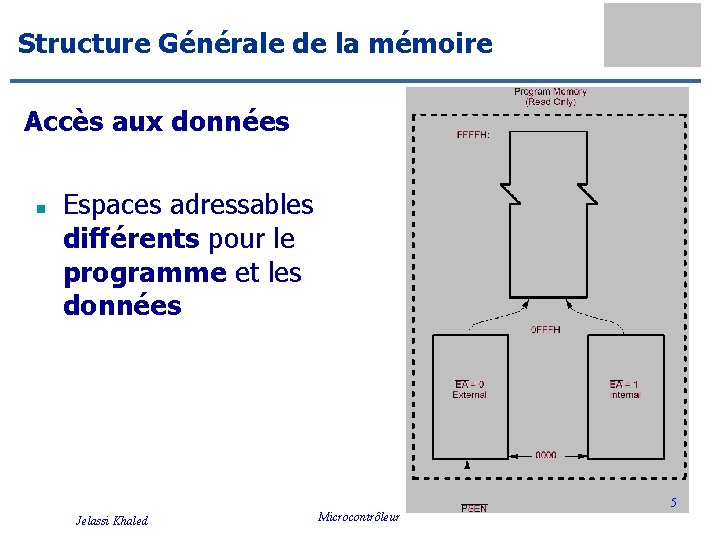

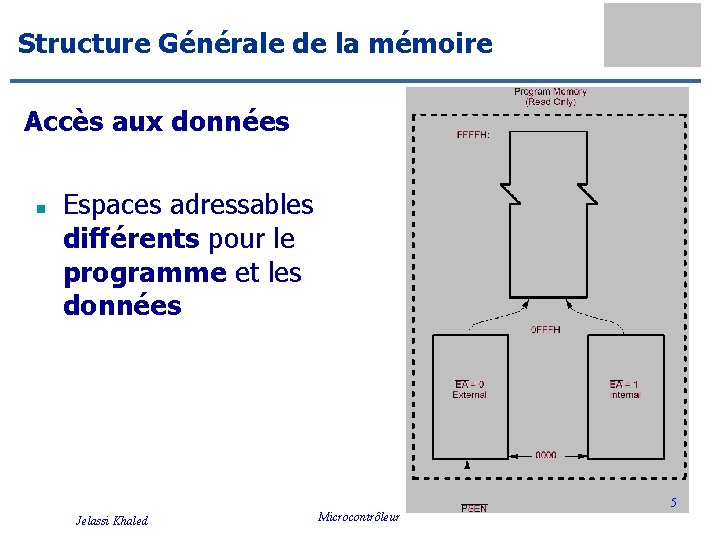

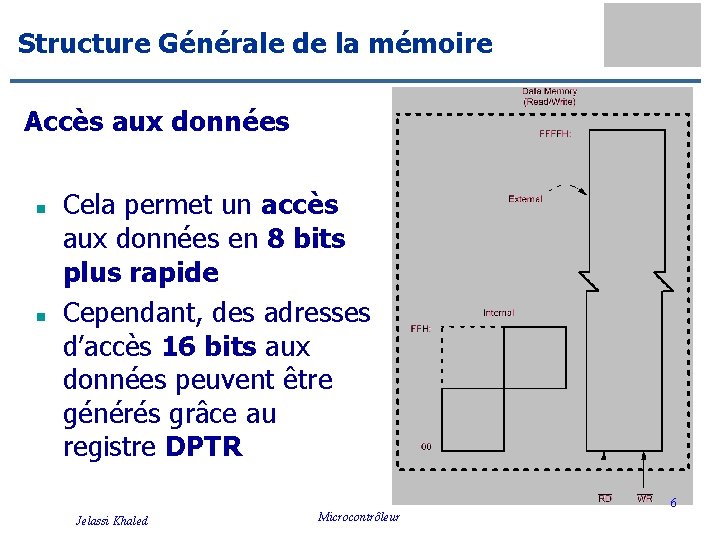

Structure Générale de la mémoire Accès aux données n Espaces adressables différents pour le programme et les données 5 Jelassi Khaled Microcontrôleur

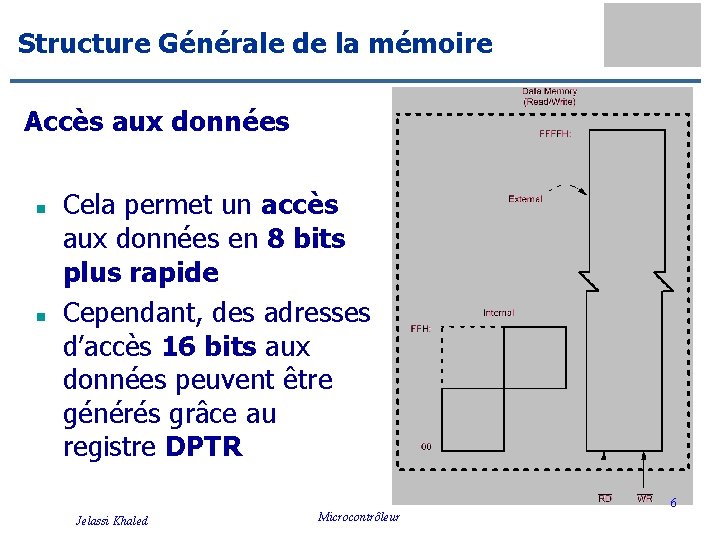

Structure Générale de la mémoire Accès aux données n n Cela permet un accès aux données en 8 bits plus rapide Cependant, des adresses d’accès 16 bits aux données peuvent être générés grâce au registre DPTR 6 Jelassi Khaled Microcontrôleur

Structure Générale de la mémoire Mémoire Programme n n Elle constituée de ROM ou d’EPROM Taille maximale : 64 k. Octets Sur le 80 C 51 : les 4 k. Octets sont sur le chip En version romless toute la mémoire est externe dans ce cas, le signal de validation de la mémoire s’appelle PSEN (Program Store Enable) 7 Jelassi Khaled Microcontrôleur

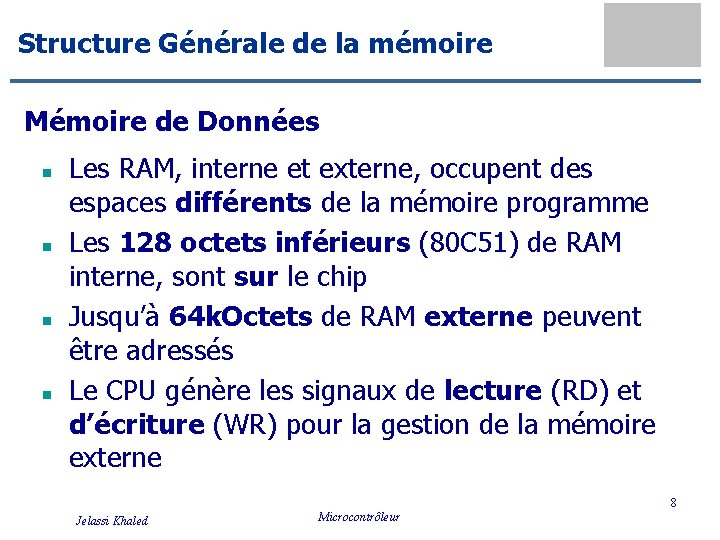

Structure Générale de la mémoire Mémoire de Données n n Les RAM, interne et externe, occupent des espaces différents de la mémoire programme Les 128 octets inférieurs (80 C 51) de RAM interne, sont sur le chip Jusqu’à 64 k. Octets de RAM externe peuvent être adressés Le CPU génère les signaux de lecture (RD) et d’écriture (WR) pour la gestion de la mémoire externe 8 Jelassi Khaled Microcontrôleur

Structure Générale de la mémoire ! n Particularité pour les systèmes de développement Sous certaines conditions, la RAM externe (mémoire de données externe) et la ROM externe (mémoire de programme externe) peuvent être combinées en appliquant RD et PSEN sur les entrées d'une fonction ET et en reliant sa sortie à l'entrée de lecture des mémoires RAM et ROM externes. 9 Jelassi Khaled Microcontrôleur

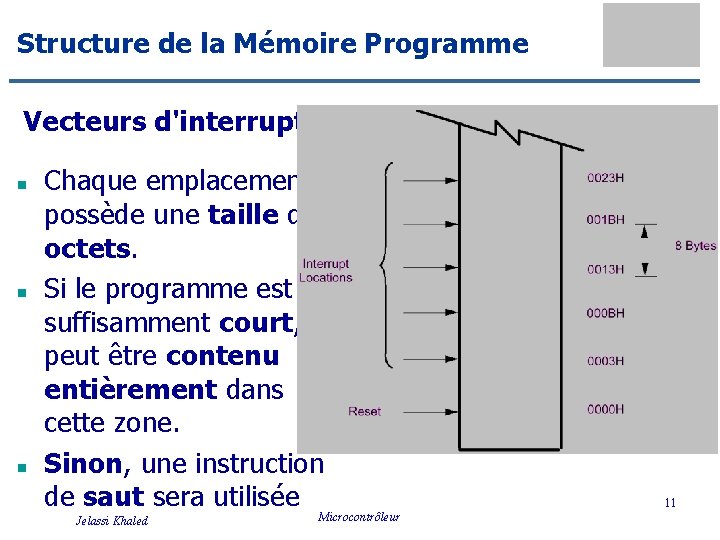

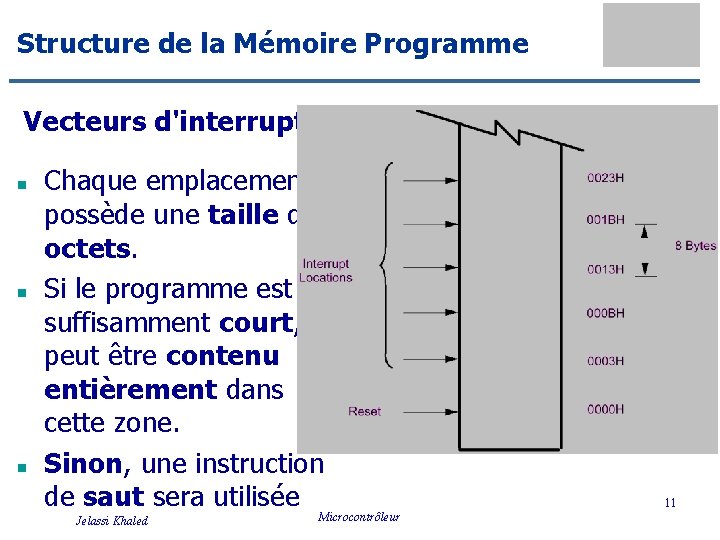

Structure de la Mémoire Programme Vecteurs d'interruptions n n Après un RESET, le 80 C 51 commence son exécution à l'adresse 0000 h Chaque interruption possède un emplacement fixe dans la mémoire programme Une interruption provoque un saut à cet emplacement qui contient une routine de service d'interruption Par exemple, l'interruption externe 0 est assignée à l'adresse 0003 h 10 Jelassi Khaled Microcontrôleur

Structure de la Mémoire Programme Vecteurs d'interruptions n n n Chaque emplacement possède une taille de 8 octets. Si le programme est suffisamment court, il peut être contenu entièrement dans cette zone. Sinon, une instruction de saut sera utilisée Jelassi Khaled Microcontrôleur 11

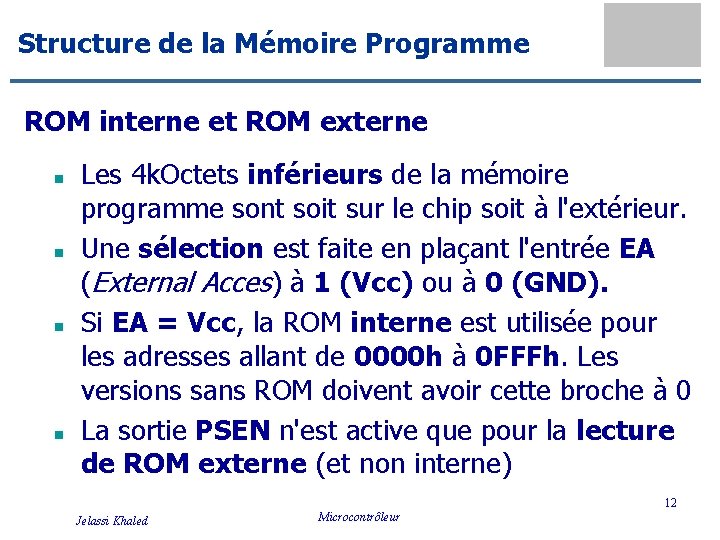

Structure de la Mémoire Programme ROM interne et ROM externe n n Les 4 k. Octets inférieurs de la mémoire programme sont soit sur le chip soit à l'extérieur. Une sélection est faite en plaçant l'entrée EA (External Acces) à 1 (Vcc) ou à 0 (GND). Si EA = Vcc, la ROM interne est utilisée pour les adresses allant de 0000 h à 0 FFFh. Les versions sans ROM doivent avoir cette broche à 0 La sortie PSEN n'est active que pour la lecture de ROM externe (et non interne) 12 Jelassi Khaled Microcontrôleur

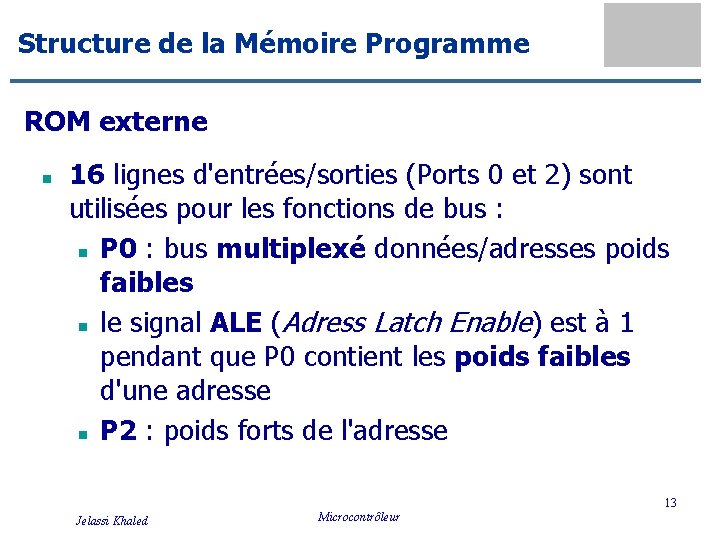

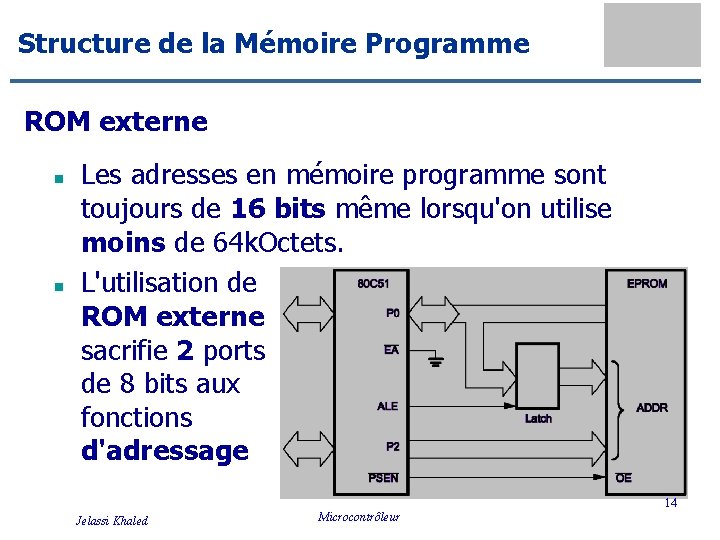

Structure de la Mémoire Programme ROM externe n 16 lignes d'entrées/sorties (Ports 0 et 2) sont utilisées pour les fonctions de bus : n P 0 : bus multiplexé données/adresses poids faibles n le signal ALE (Adress Latch Enable) est à 1 pendant que P 0 contient les poids faibles d'une adresse n P 2 : poids forts de l'adresse 13 Jelassi Khaled Microcontrôleur

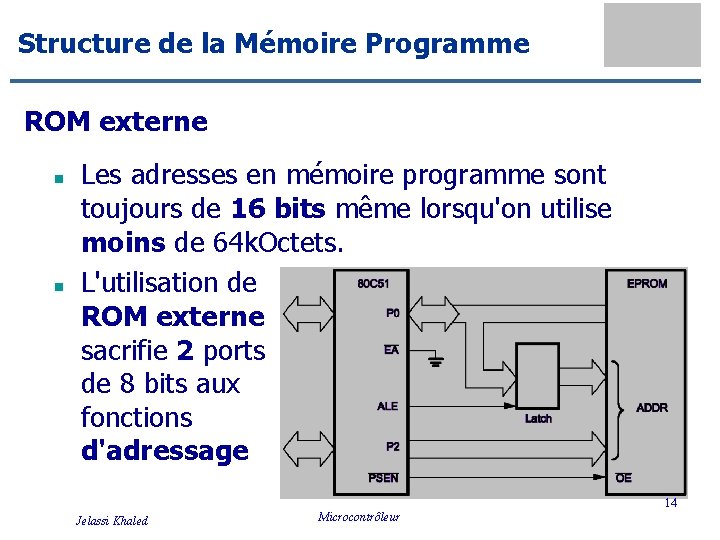

Structure de la Mémoire Programme ROM externe n n Les adresses en mémoire programme sont toujours de 16 bits même lorsqu'on utilise moins de 64 k. Octets. L'utilisation de ROM externe sacrifie 2 ports de 8 bits aux fonctions d'adressage 14 Jelassi Khaled Microcontrôleur

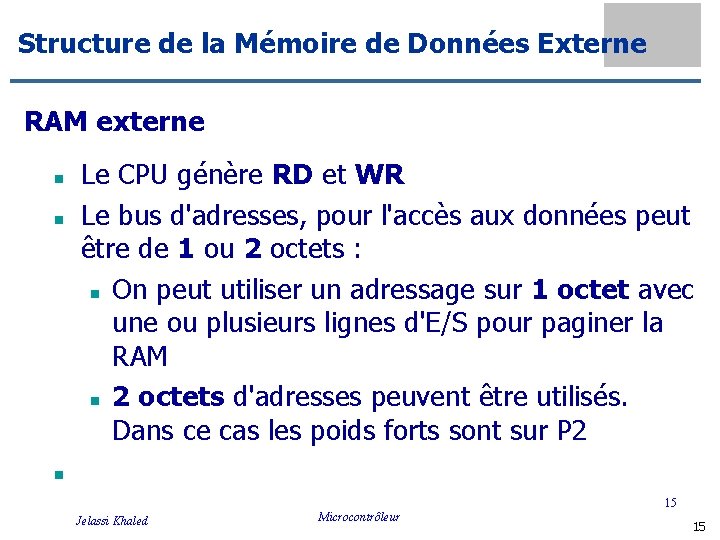

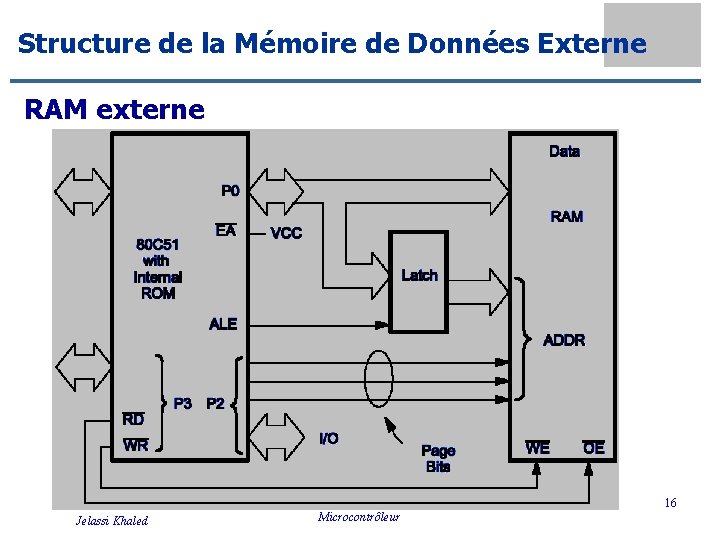

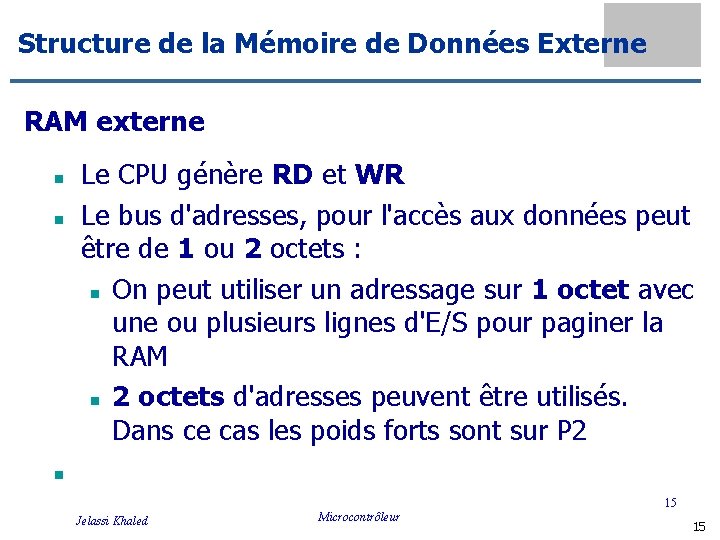

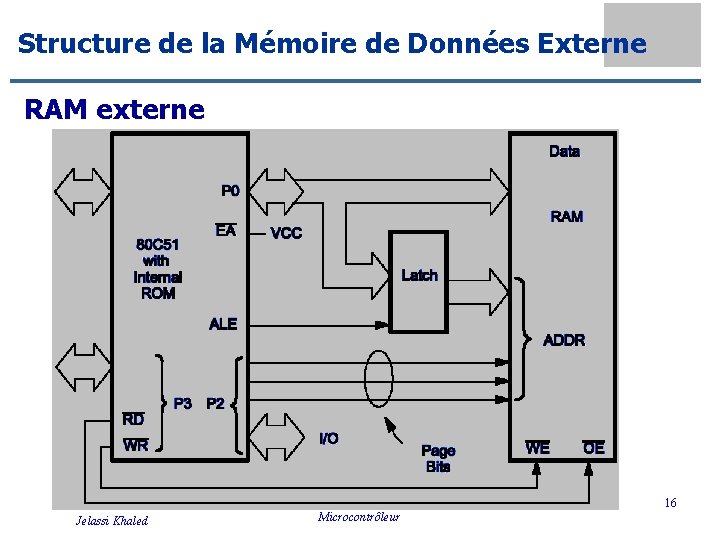

Structure de la Mémoire de Données Externe RAM externe n n n Le CPU génère RD et WR Le bus d'adresses, pour l'accès aux données peut être de 1 ou 2 octets : n On peut utiliser un adressage sur 1 octet avec une ou plusieurs lignes d'E/S pour paginer la RAM n 2 octets d'adresses peuvent être utilisés. Dans ce cas les poids forts sont sur P 2 15 Jelassi Khaled Microcontrôleur 15

Structure de la Mémoire de Données Externe RAM externe 16 Jelassi Khaled Microcontrôleur

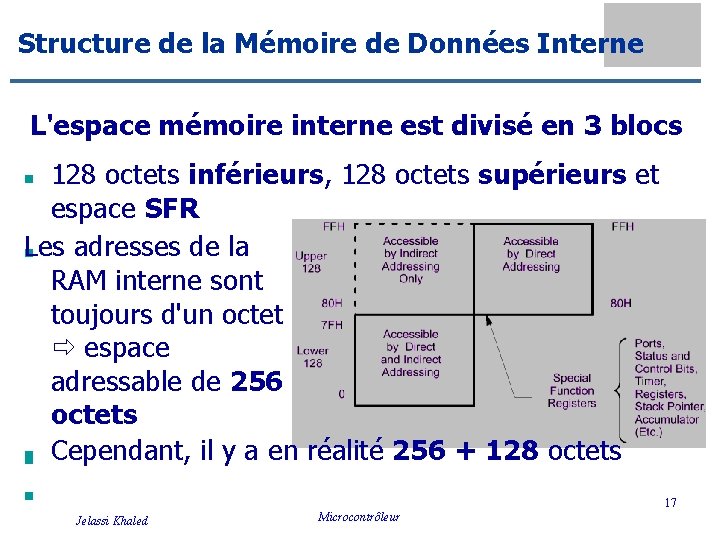

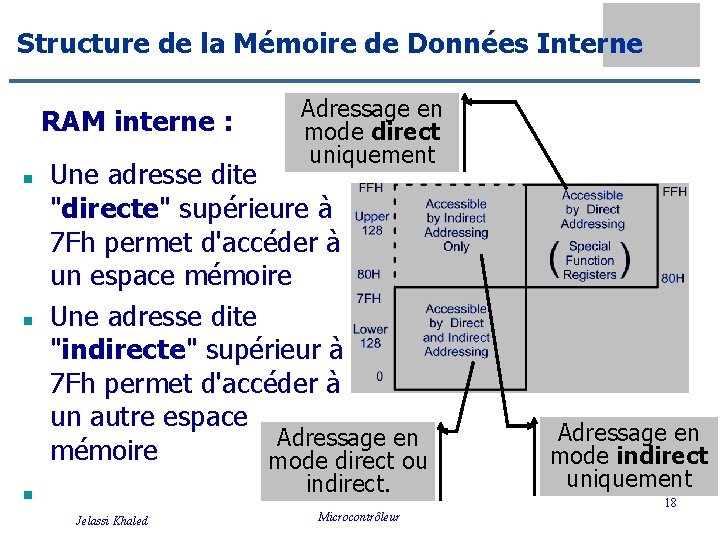

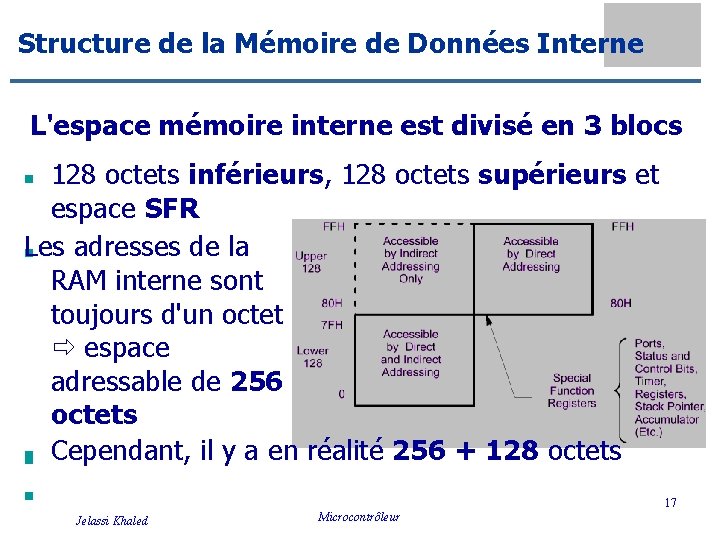

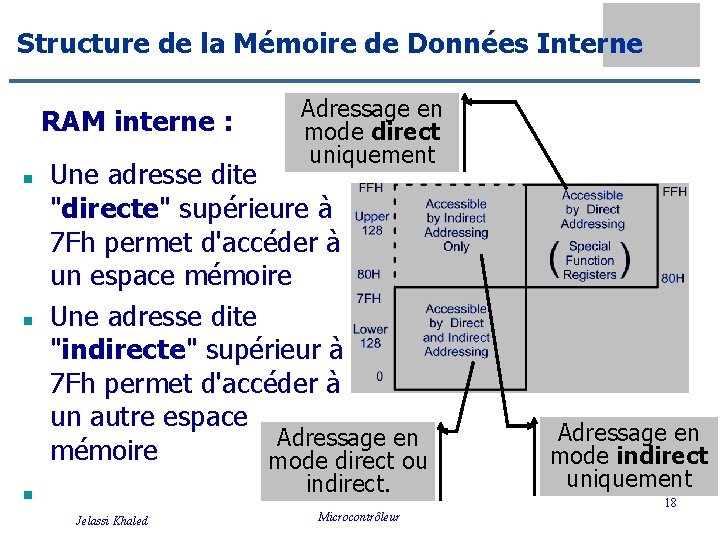

Structure de la Mémoire de Données Interne L'espace mémoire interne est divisé en 3 blocs 128 octets inférieurs, 128 octets supérieurs et espace SFR Les adresses de la n RAM interne sont toujours d'un octet espace adressable de 256 octets n + 128 octets n Cependant, il y a en réalité 256 n 17 n Jelassi Khaled Microcontrôleur

Structure de la Mémoire de Données Interne RAM interne : n n n Adressage en mode direct uniquement Une adresse dite "directe" supérieure à 7 Fh permet d'accéder à un espace mémoire Une adresse dite "indirecte" supérieur à 7 Fh permet d'accéder à un autre espace Adressage en mémoire mode direct ou indirect. Jelassi Khaled Microcontrôleur Adressage en mode indirect uniquement 18

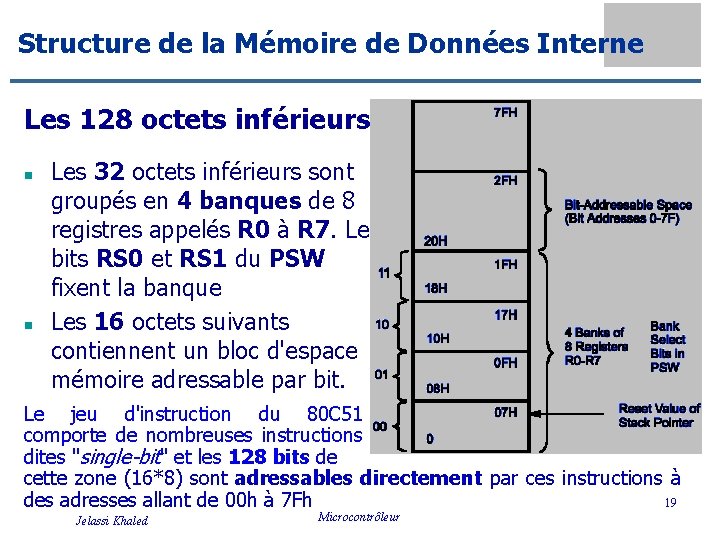

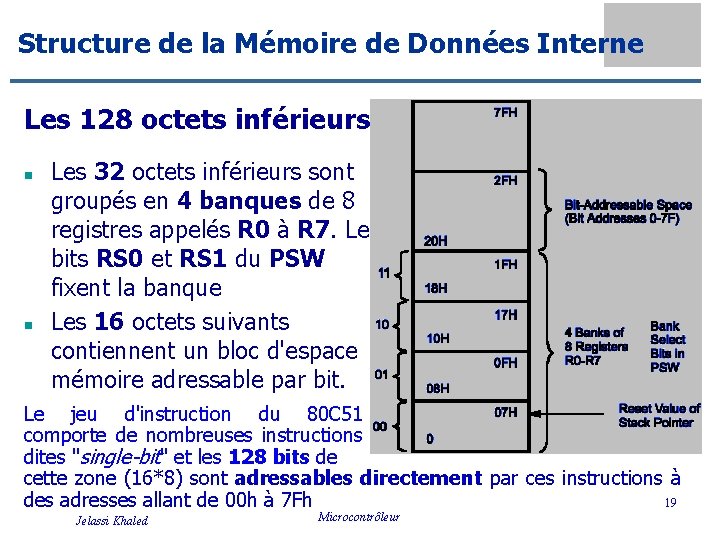

Structure de la Mémoire de Données Interne Les 128 octets inférieurs n n Les 32 octets inférieurs sont groupés en 4 banques de 8 registres appelés R 0 à R 7. Les bits RS 0 et RS 1 du PSW fixent la banque Les 16 octets suivants contiennent un bloc d'espace mémoire adressable par bit. Le jeu d'instruction du 80 C 51 comporte de nombreuses instructions dites "single-bit" et les 128 bits de cette zone (16*8) sont adressables directement par ces instructions à des adresses allant de 00 h à 7 Fh 19 Jelassi Khaled Microcontrôleur

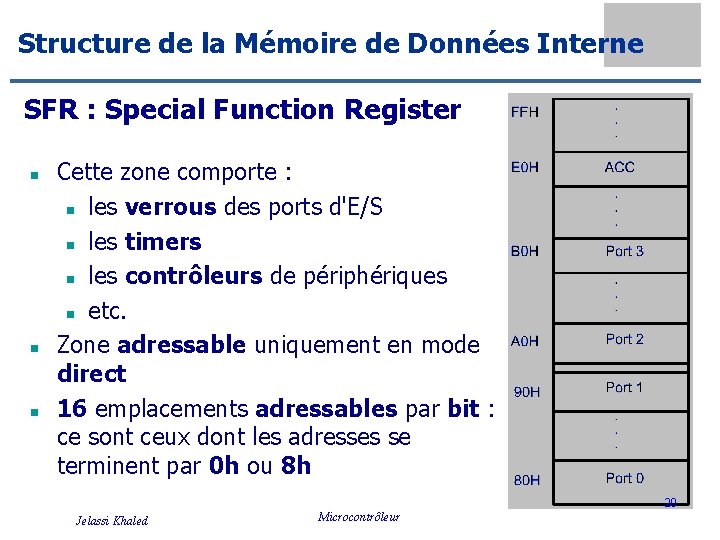

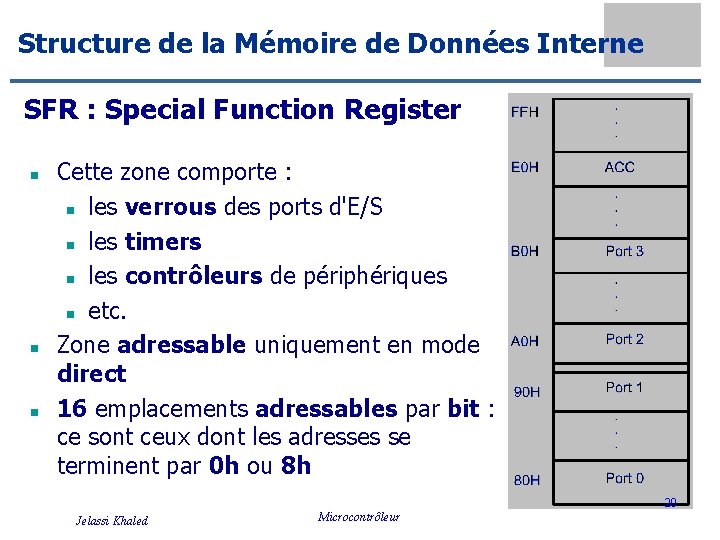

Structure de la Mémoire de Données Interne SFR : Special Function Register n n n Cette zone comporte : n les verrous des ports d'E/S n les timers n les contrôleurs de périphériques n etc. Zone adressable uniquement en mode direct 16 emplacements adressables par bit : ce sont ceux dont les adresses se terminent par 0 h ou 8 h 20 Jelassi Khaled Microcontrôleur

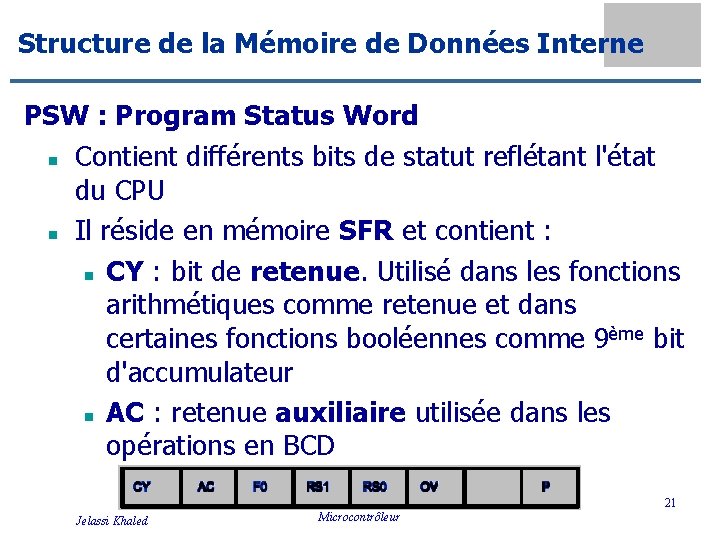

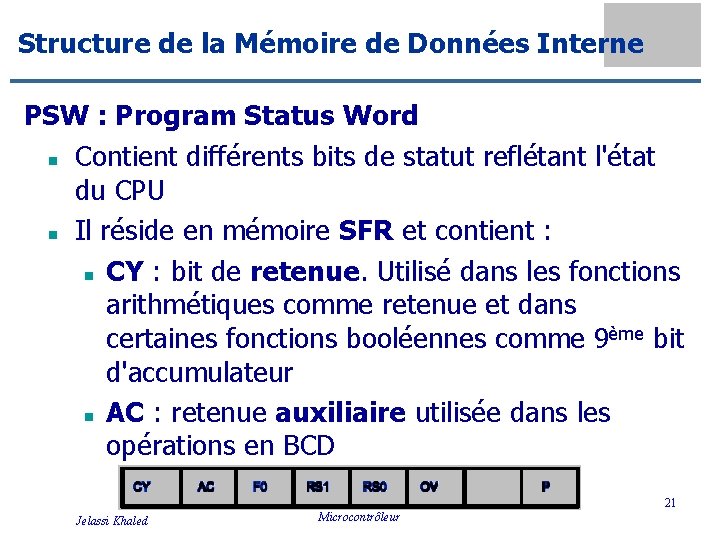

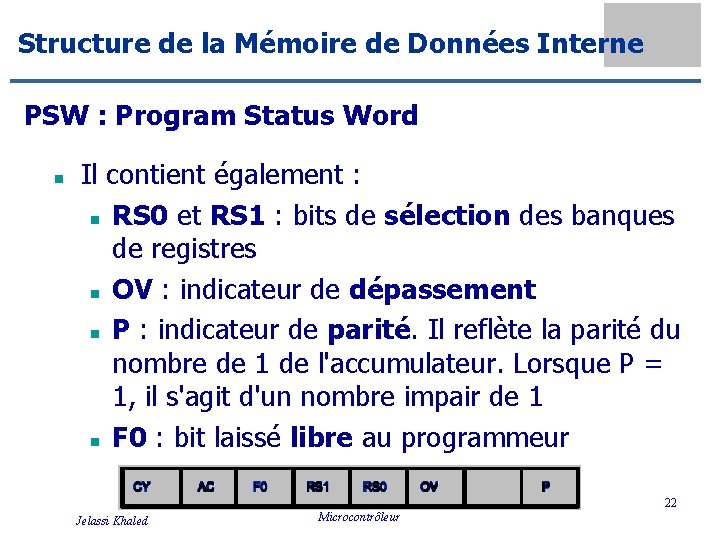

Structure de la Mémoire de Données Interne PSW : Program Status Word n Contient différents bits de statut reflétant l'état du CPU n Il réside en mémoire SFR et contient : n CY : bit de retenue. Utilisé dans les fonctions arithmétiques comme retenue et dans certaines fonctions booléennes comme 9ème bit d'accumulateur n AC : retenue auxiliaire utilisée dans les opérations en BCD 21 Jelassi Khaled Microcontrôleur

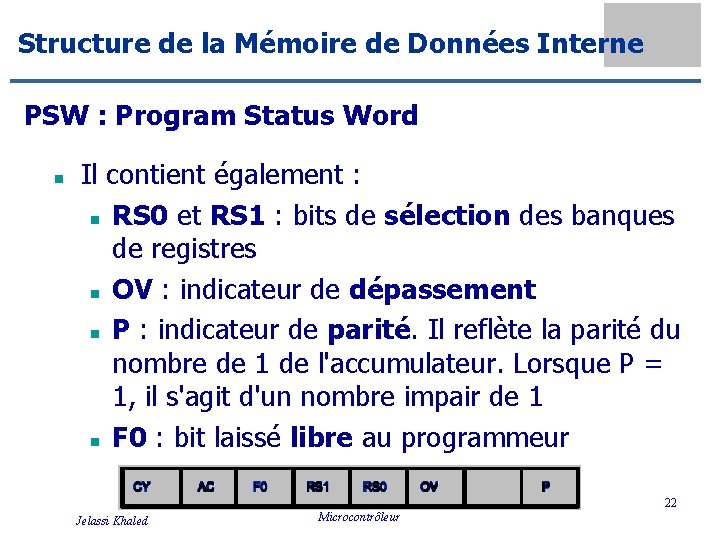

Structure de la Mémoire de Données Interne PSW : Program Status Word n Il contient également : n RS 0 et RS 1 : bits de sélection des banques de registres n OV : indicateur de dépassement n P : indicateur de parité. Il reflète la parité du nombre de 1 de l'accumulateur. Lorsque P = 1, il s'agit d'un nombre impair de 1 n F 0 : bit laissé libre au programmeur 22 Jelassi Khaled Microcontrôleur

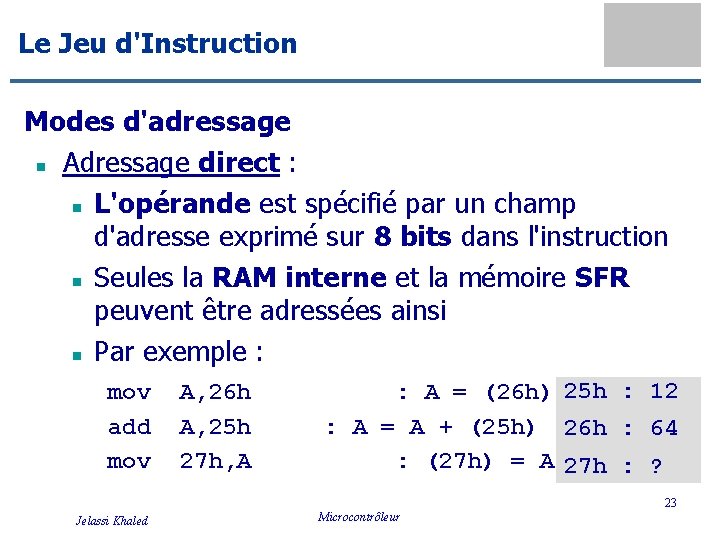

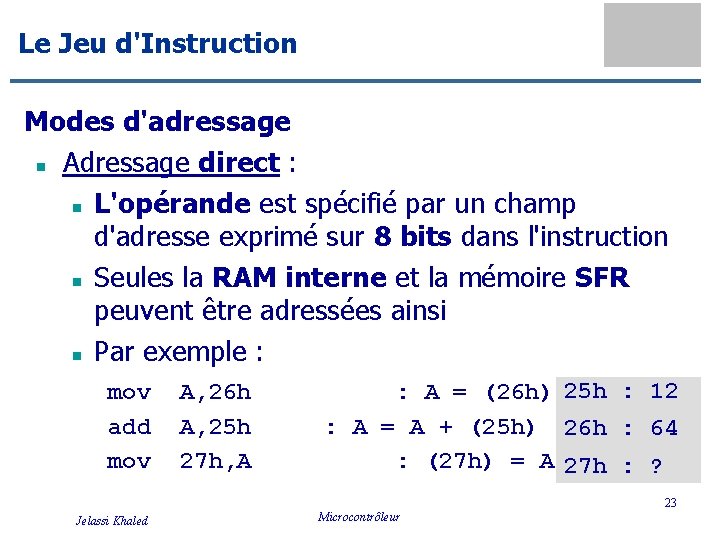

Le Jeu d'Instruction Modes d'adressage n Adressage direct : n L'opérande est spécifié par un champ d'adresse exprimé sur 8 bits dans l'instruction n Seules la RAM interne et la mémoire SFR peuvent être adressées ainsi n Par exemple : mov add mov A, 26 h A, 25 h 27 h, A : A = (26 h) 25 h : 12 : A = A + (25 h) 26 h : 64 : (27 h) = A 27 h : ? 23 Jelassi Khaled Microcontrôleur

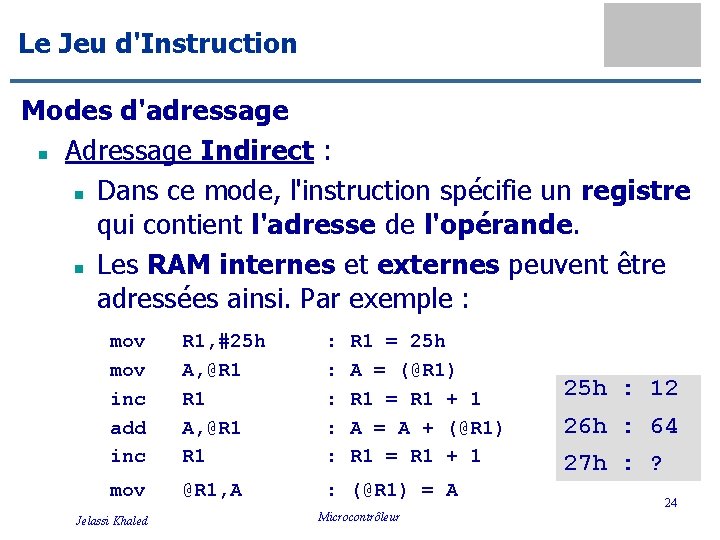

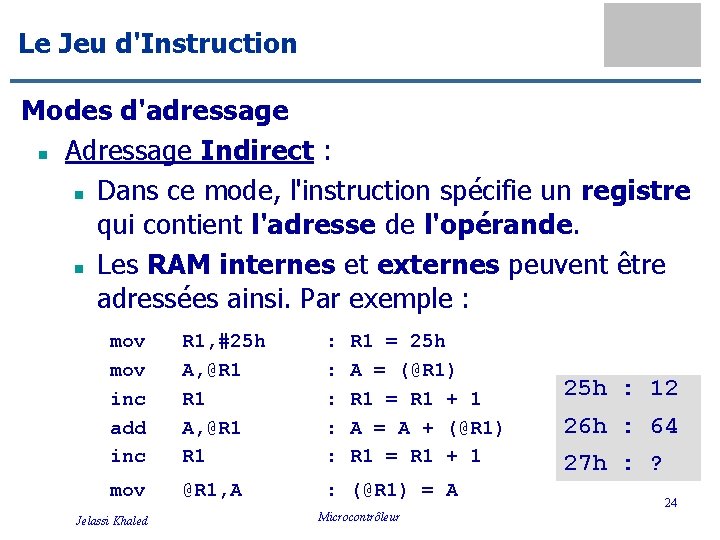

Le Jeu d'Instruction Modes d'adressage n Adressage Indirect : n Dans ce mode, l'instruction spécifie un registre qui contient l'adresse de l'opérande. n Les RAM internes et externes peuvent être adressées ainsi. Par exemple : mov inc add inc R 1, #25 h A, @R 1 R 1 : : : mov @R 1, A : (@R 1) = A Jelassi Khaled R 1 = 25 h A = (@R 1) R 1 = R 1 + 1 A = A + (@R 1) R 1 = R 1 + 1 Microcontrôleur 25 h : 12 26 h : 64 27 h : ? 24

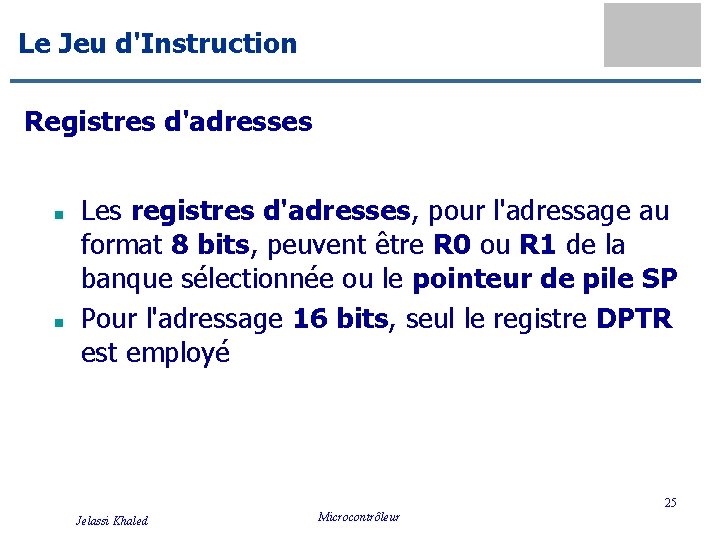

Le Jeu d'Instruction Registres d'adresses n n Les registres d'adresses, pour l'adressage au format 8 bits, peuvent être R 0 ou R 1 de la banque sélectionnée ou le pointeur de pile SP Pour l'adressage 16 bits, seul le registre DPTR est employé 25 Jelassi Khaled Microcontrôleur

Le Jeu d'Instructions de registres n n Les instructions utilisant les registres R 0 à R 7 comportent, dans leur code opératoire, 3 bits désignant le numéro du registre. Elles sont donc plus compactes que celles utilisant un adressage direct nécessitant un octet supplémentaire 26 Jelassi Khaled Microcontrôleur

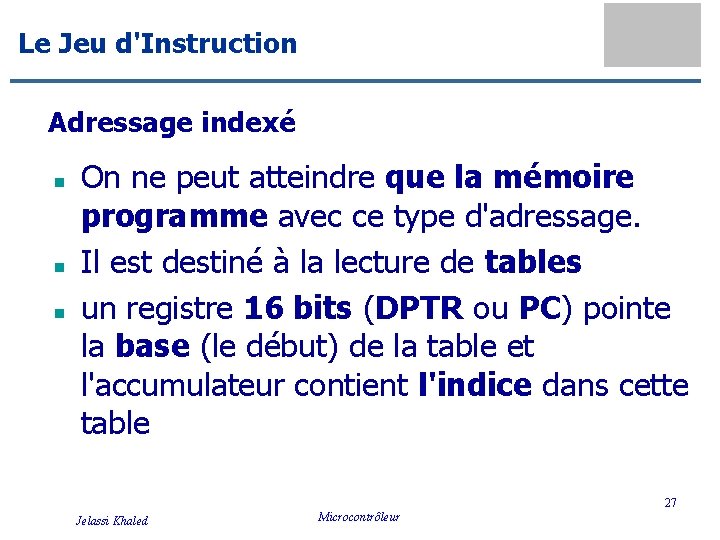

Le Jeu d'Instruction Adressage indexé n n n On ne peut atteindre que la mémoire programme avec ce type d'adressage. Il est destiné à la lecture de tables un registre 16 bits (DPTR ou PC) pointe la base (le début) de la table et l'accumulateur contient l'indice dans cette table 27 Jelassi Khaled Microcontrôleur

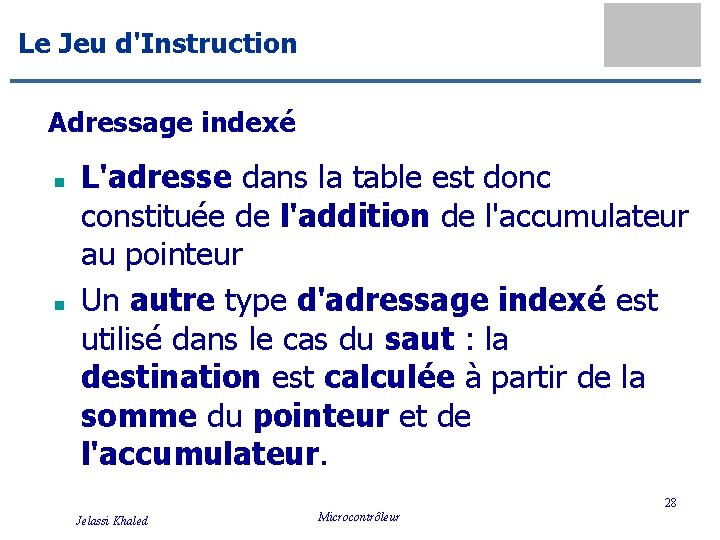

Le Jeu d'Instruction Adressage indexé n n L'adresse dans la table est donc constituée de l'addition de l'accumulateur au pointeur Un autre type d'adressage indexé est utilisé dans le cas du saut : la destination est calculée à partir de la somme du pointeur et de l'accumulateur. 28 Jelassi Khaled Microcontrôleur

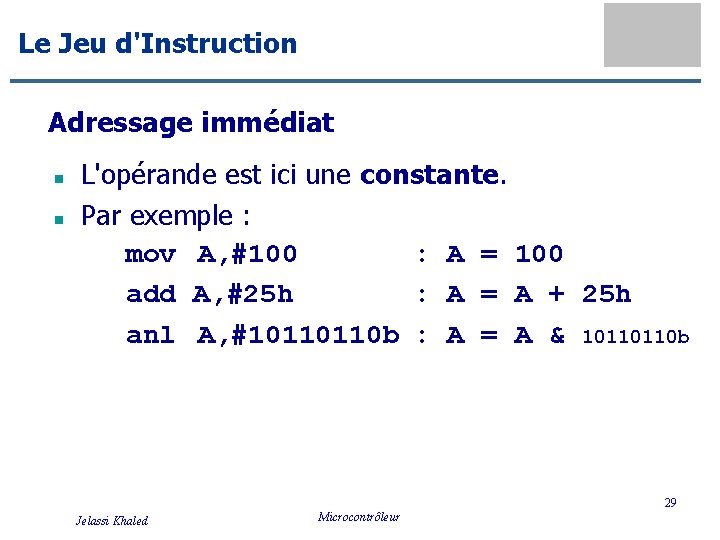

Le Jeu d'Instruction Adressage immédiat n n L'opérande est ici une constante. Par exemple : mov A, #100 : A = 100 add A, #25 h : A = A + 25 h anl A, #10110110 b : A = A & 10110110 b 29 Jelassi Khaled Microcontrôleur

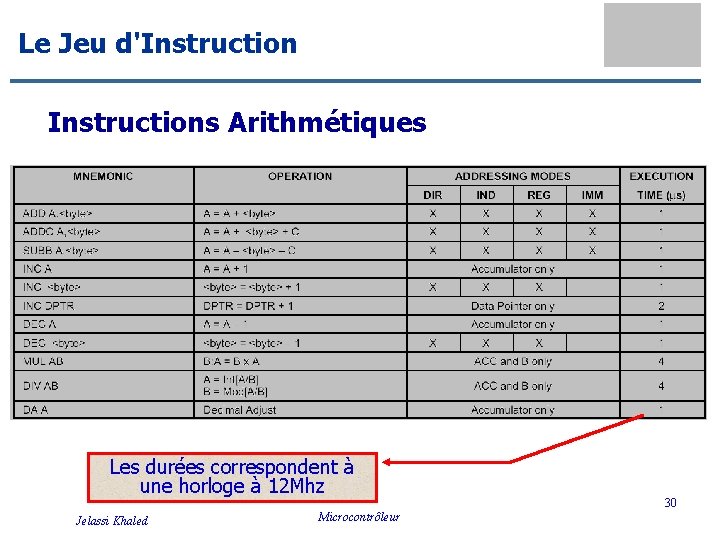

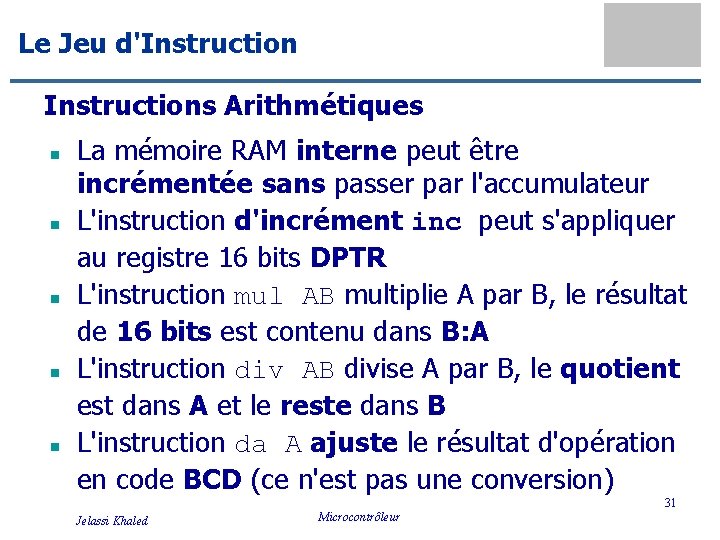

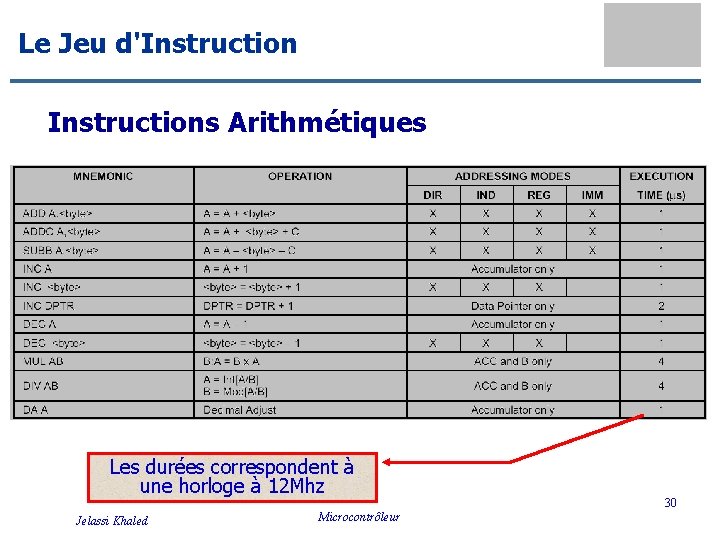

Le Jeu d'Instructions Arithmétiques Les durées correspondent à une horloge à 12 Mhz Jelassi Khaled Microcontrôleur 30

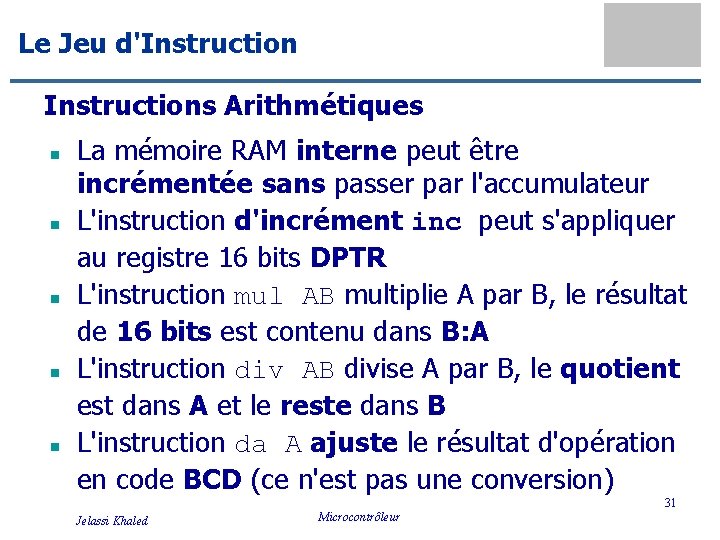

Le Jeu d'Instructions Arithmétiques n n n La mémoire RAM interne peut être incrémentée sans passer par l'accumulateur L'instruction d'incrément inc peut s'appliquer au registre 16 bits DPTR L'instruction mul AB multiplie A par B, le résultat de 16 bits est contenu dans B: A L'instruction div AB divise A par B, le quotient est dans A et le reste dans B L'instruction da A ajuste le résultat d'opération en code BCD (ce n'est pas une conversion) 31 Jelassi Khaled Microcontrôleur

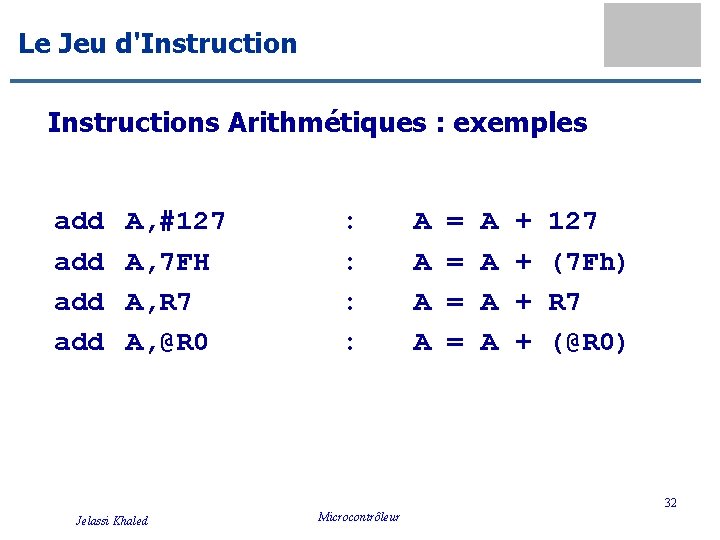

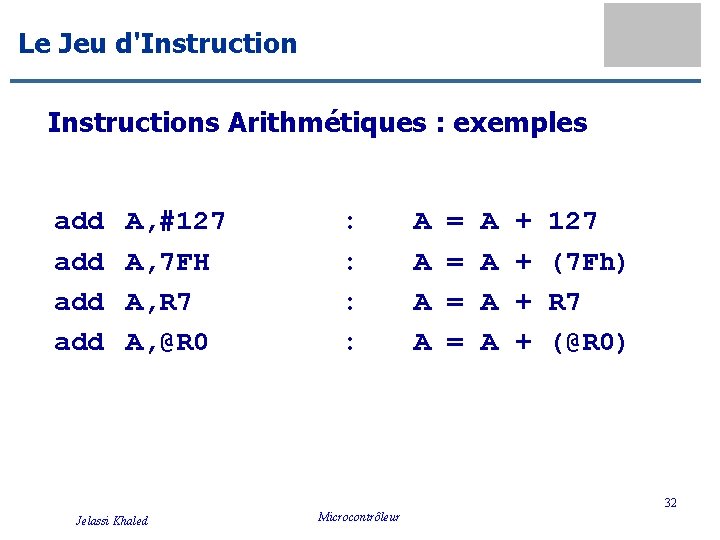

Le Jeu d'Instructions Arithmétiques : exemples add add A, #127 A, 7 FH A, R 7 A, @R 0 : : A A = = A A + + 127 (7 Fh) R 7 (@R 0) 32 Jelassi Khaled Microcontrôleur

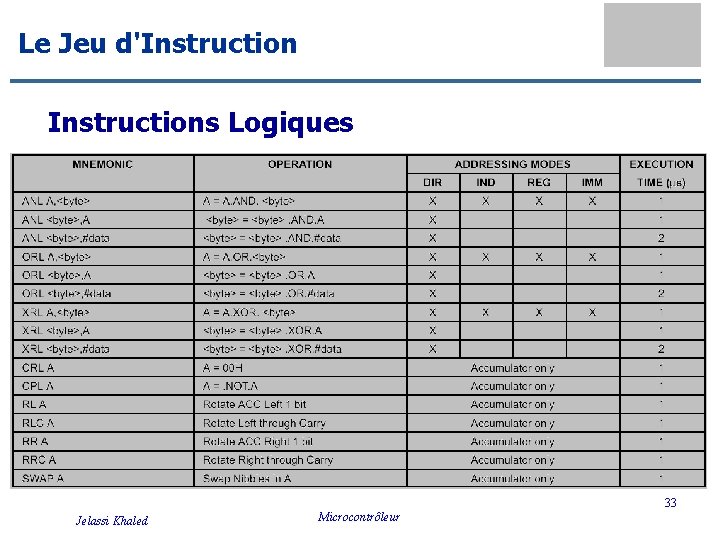

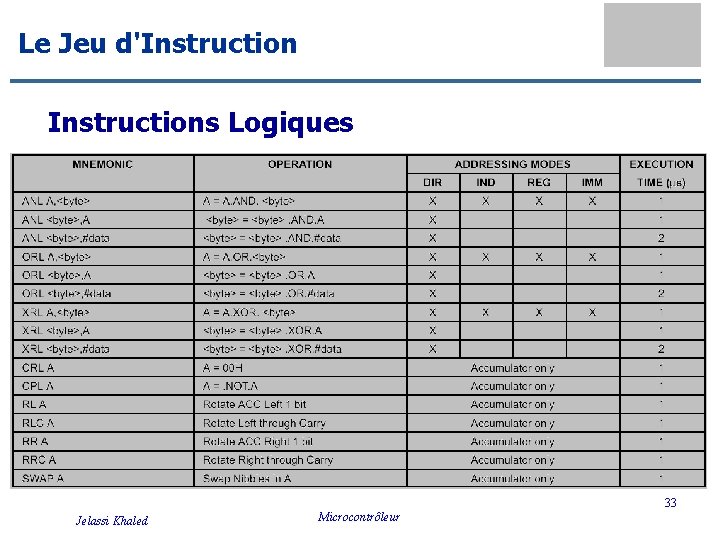

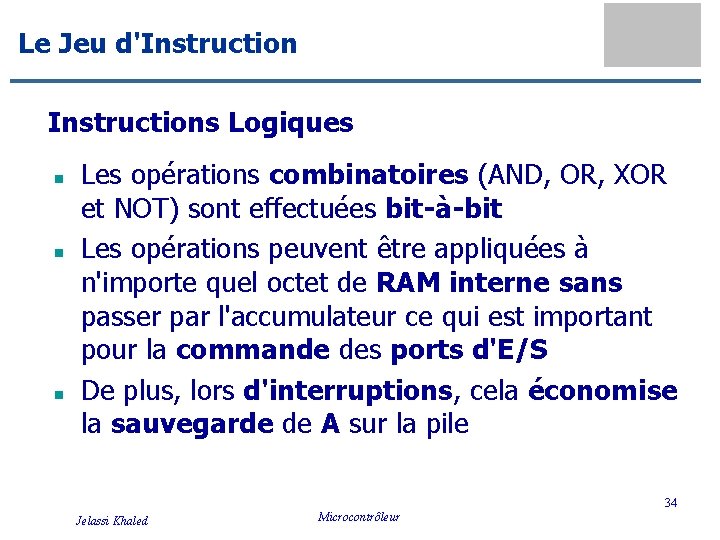

Le Jeu d'Instructions Logiques 33 Jelassi Khaled Microcontrôleur

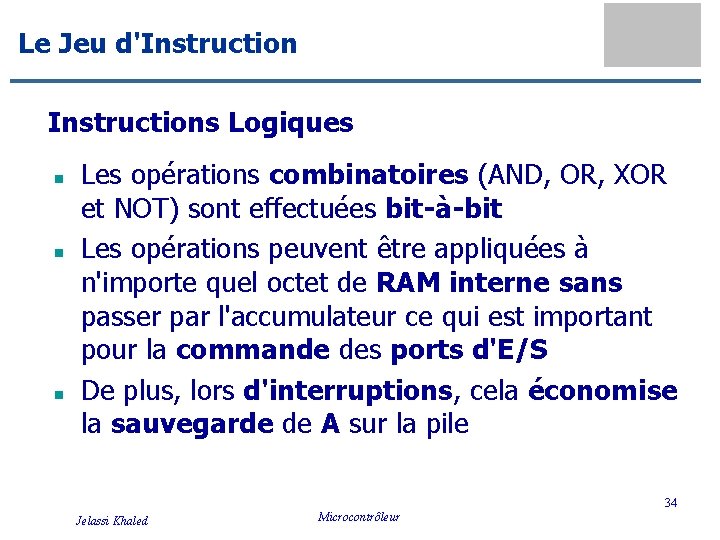

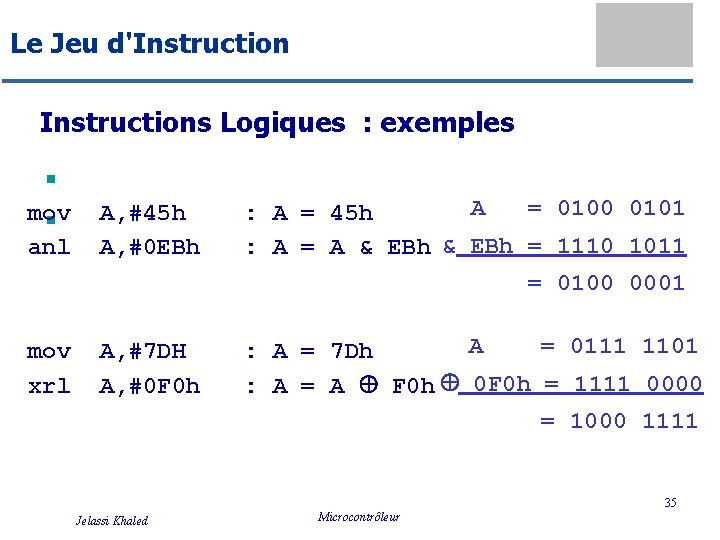

Le Jeu d'Instructions Logiques n n n Les opérations combinatoires (AND, OR, XOR et NOT) sont effectuées bit-à-bit Les opérations peuvent être appliquées à n'importe quel octet de RAM interne sans passer par l'accumulateur ce qui est important pour la commande des ports d'E/S De plus, lors d'interruptions, cela économise la sauvegarde de A sur la pile 34 Jelassi Khaled Microcontrôleur

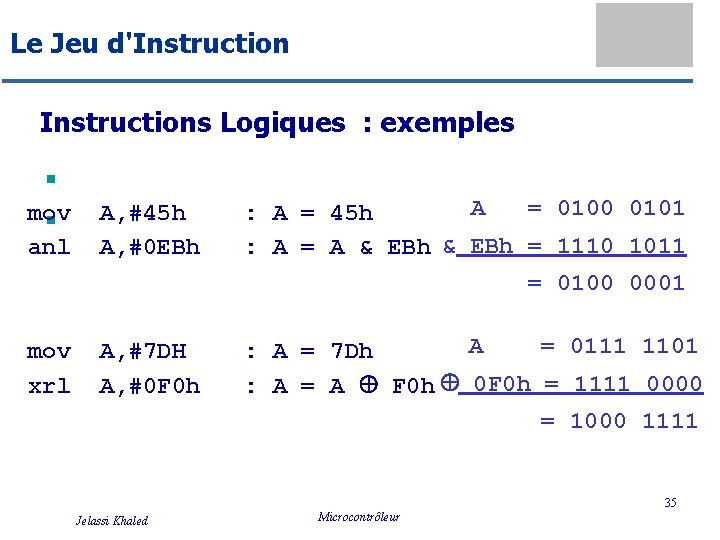

Le Jeu d'Instructions Logiques : exemples mov n A, #45 h n anl A, #0 EBh mov xrl A, #7 DH A, #0 F 0 h A = 0100 0101 : A = 45 h : A = A & EBh = 1110 1011 = 0100 0001 A = 0111 1101 : A = 7 Dh : A = A F 0 h 0 F 0 h = 1111 0000 = 1000 1111 35 Jelassi Khaled Microcontrôleur

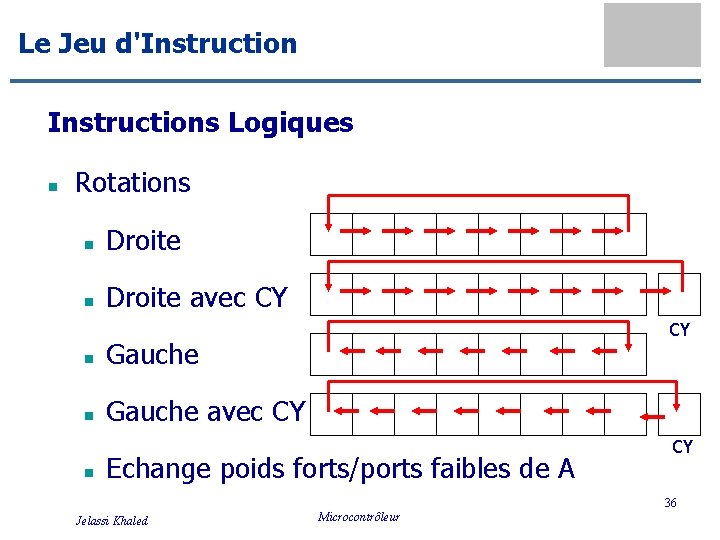

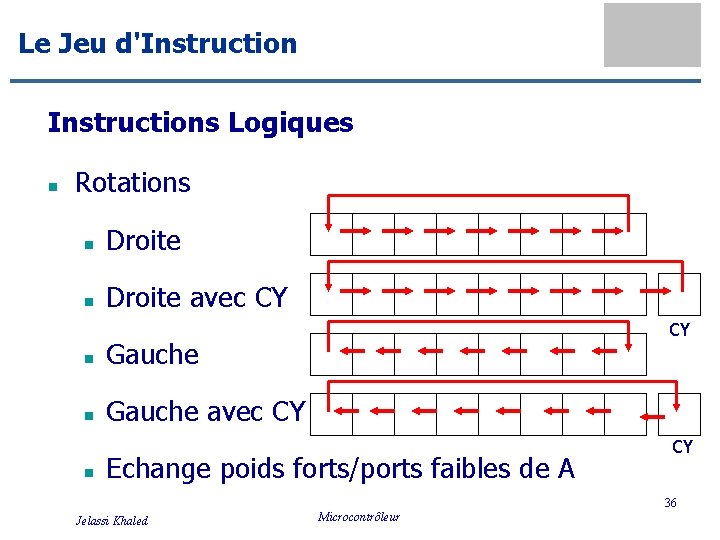

Le Jeu d'Instructions Logiques n Rotations n Droite avec CY n Gauche avec CY n CY Echange poids forts/ports faibles de A CY 36 Jelassi Khaled Microcontrôleur

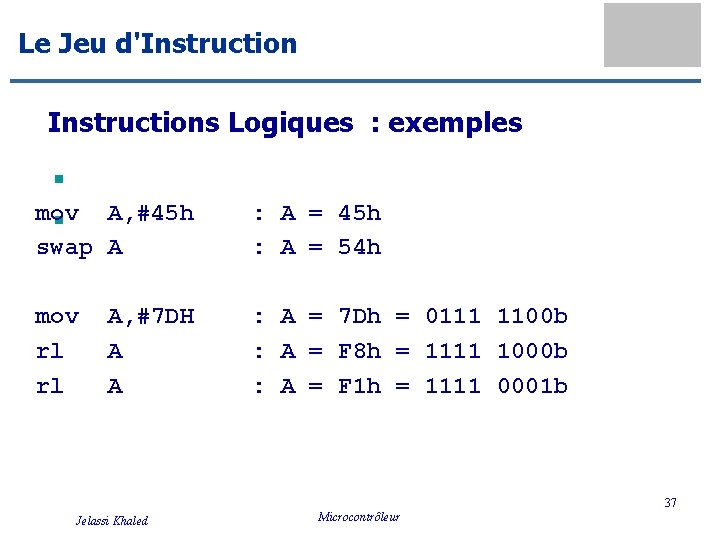

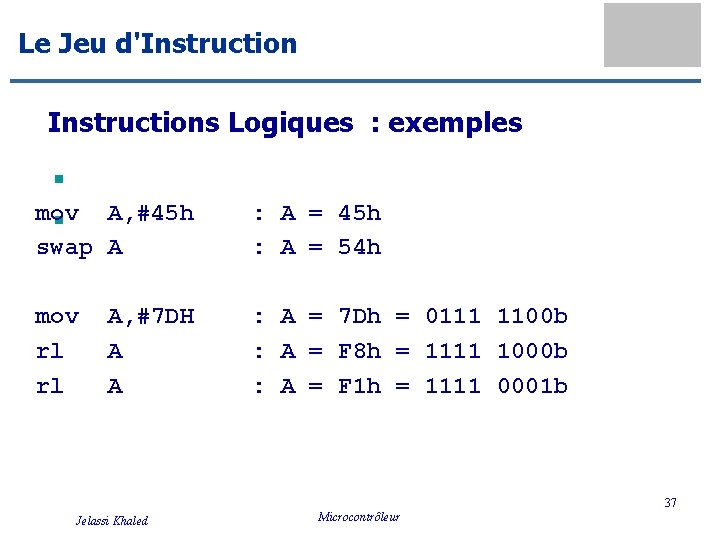

Le Jeu d'Instructions Logiques : exemples mov n A, #45 h n swap A : A = 45 h : A = 54 h mov rl rl : A = 7 Dh = 0111 1100 b : A = F 8 h = 1111 1000 b : A = F 1 h = 1111 0001 b A, #7 DH A A 37 Jelassi Khaled Microcontrôleur

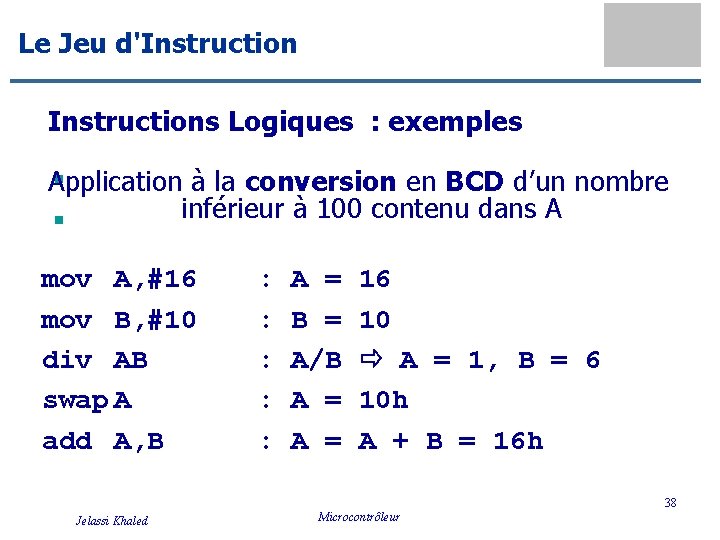

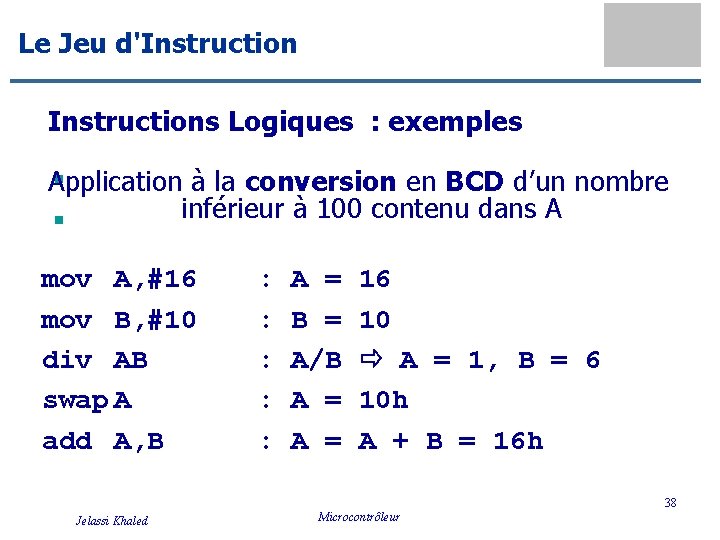

Le Jeu d'Instructions Logiques : exemples n Application à la conversion en BCD d’un nombre inférieur à 100 contenu dans A n mov A, #16 : A = 16 mov B, #10 : B = 10 div AB : A/B A = 1, B = 6 swap A : A = 10 h add A, B : A = A + B = 16 h 38 Jelassi Khaled Microcontrôleur

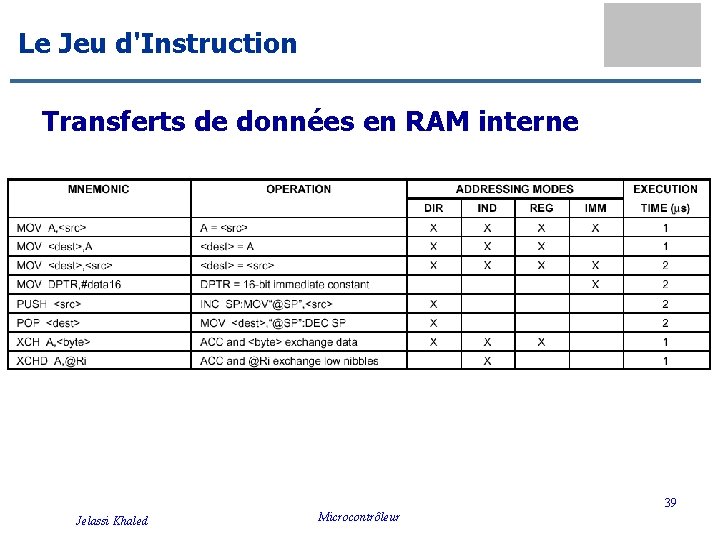

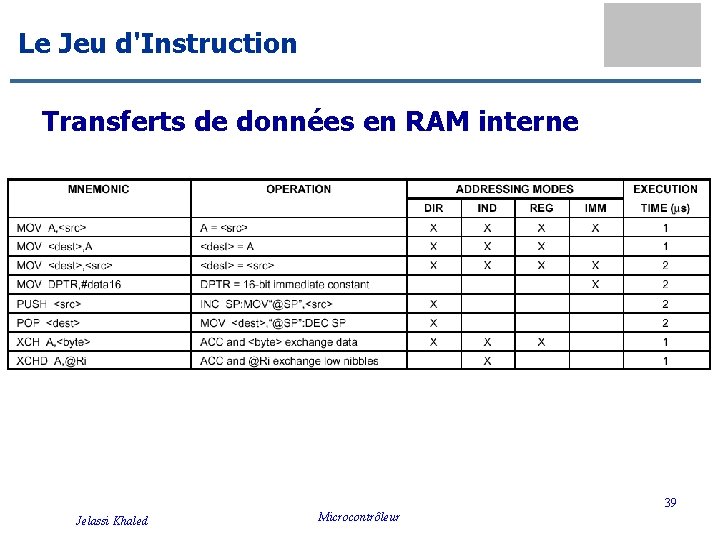

Le Jeu d'Instruction Transferts de données en RAM interne 39 Jelassi Khaled Microcontrôleur

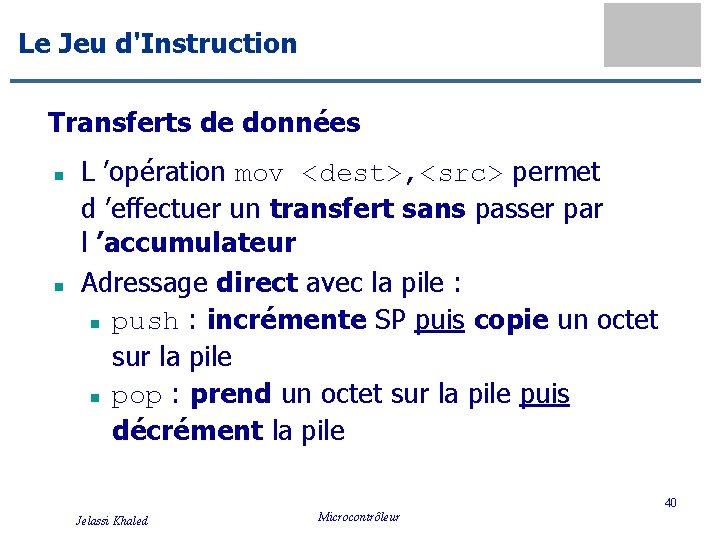

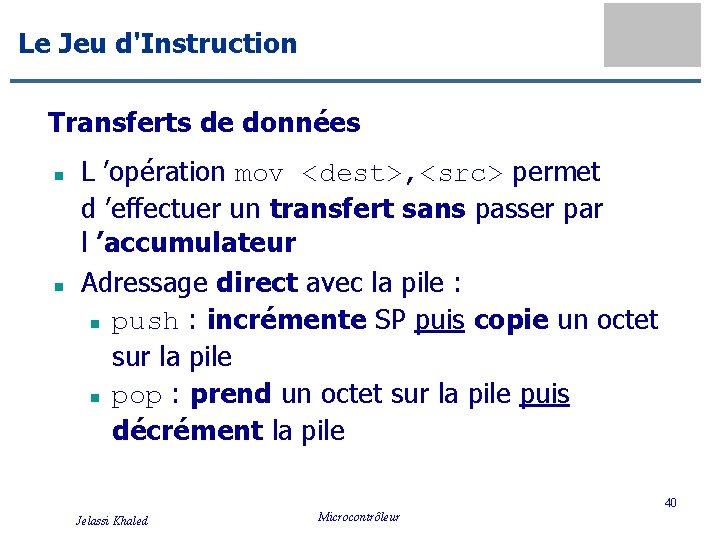

Le Jeu d'Instruction Transferts de données n n L ’opération mov <dest>, <src> permet d ’effectuer un transfert sans passer par l ’accumulateur Adressage direct avec la pile : n push : incrémente SP puis copie un octet sur la pile n pop : prend un octet sur la pile puis décrément la pile 40 Jelassi Khaled Microcontrôleur

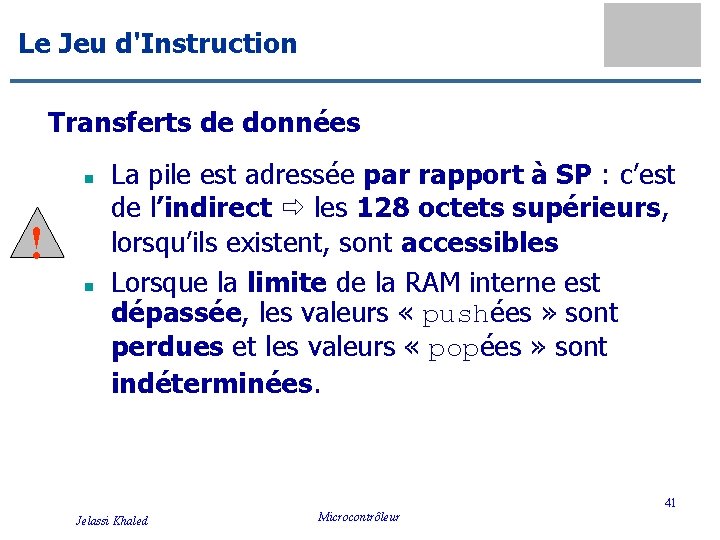

Le Jeu d'Instruction Transferts de données n ! n La pile est adressée par rapport à SP : c’est de l’indirect les 128 octets supérieurs, lorsqu’ils existent, sont accessibles Lorsque la limite de la RAM interne est dépassée, les valeurs « pushées » sont perdues et les valeurs « popées » sont indéterminées. 41 Jelassi Khaled Microcontrôleur

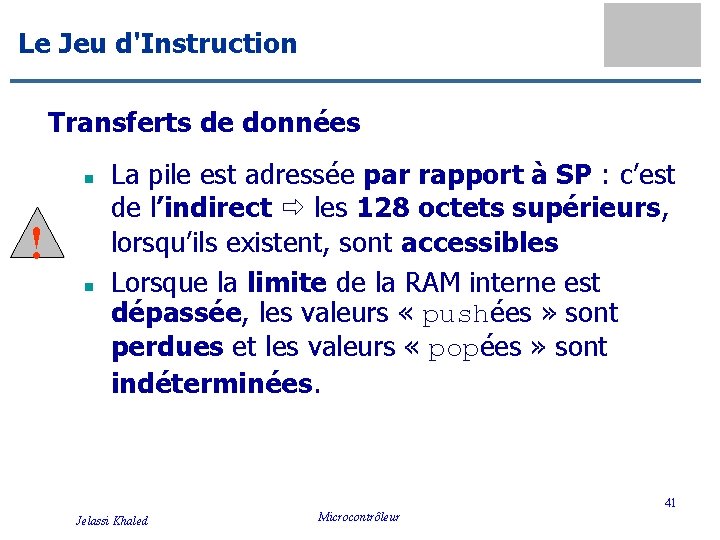

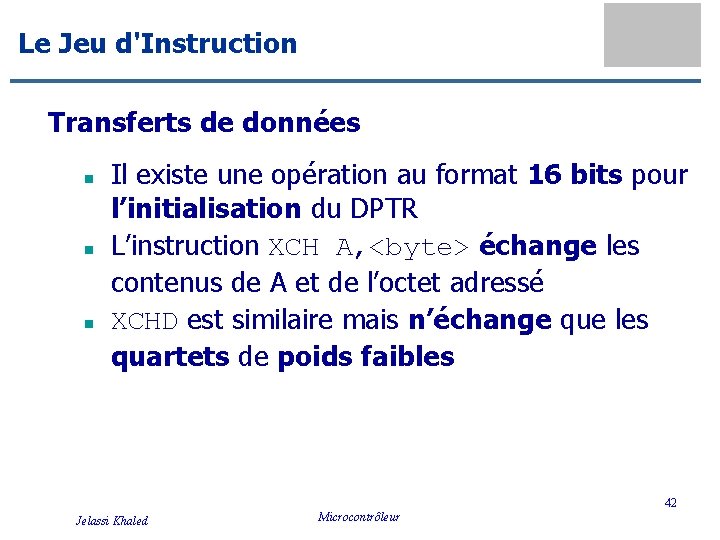

Le Jeu d'Instruction Transferts de données n n n Il existe une opération au format 16 bits pour l’initialisation du DPTR L’instruction XCH A, <byte> échange les contenus de A et de l’octet adressé XCHD est similaire mais n’échange que les quartets de poids faibles 42 Jelassi Khaled Microcontrôleur

Le Jeu d'Instruction Transferts de données : exemples Décalage d'un nombre BCD de 2 digits vers la droite Jelassi Khaled Microcontrôleur 43

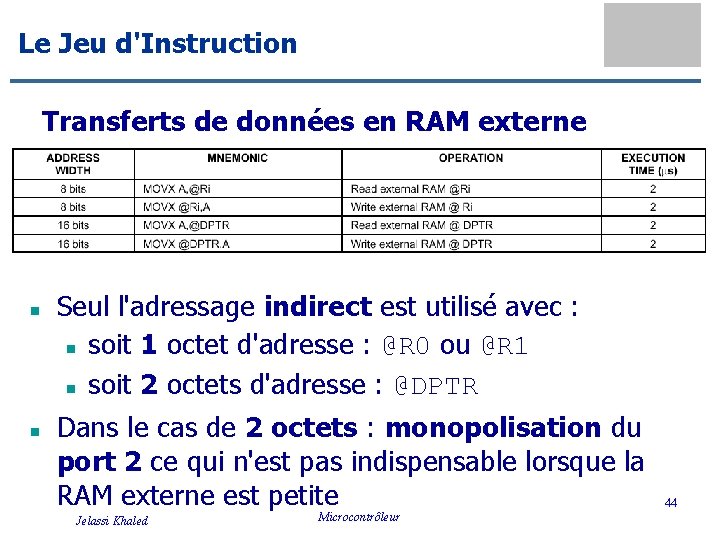

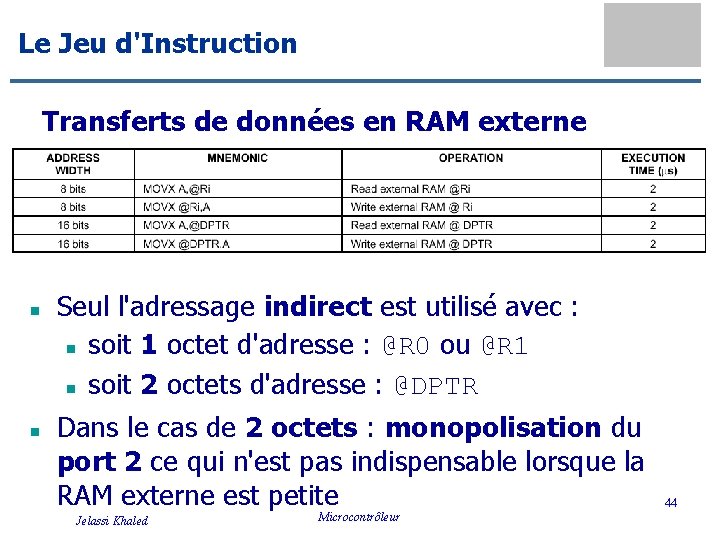

Le Jeu d'Instruction Transferts de données en RAM externe n n Seul l'adressage indirect est utilisé avec : n soit 1 octet d'adresse : @R 0 ou @R 1 n soit 2 octets d'adresse : @DPTR Dans le cas de 2 octets : monopolisation du port 2 ce qui n'est pas indispensable lorsque la RAM externe est petite Jelassi Khaled Microcontrôleur 44

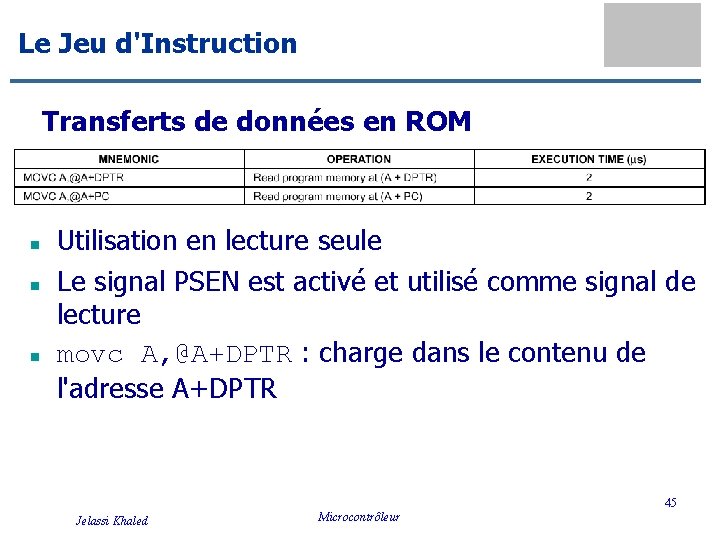

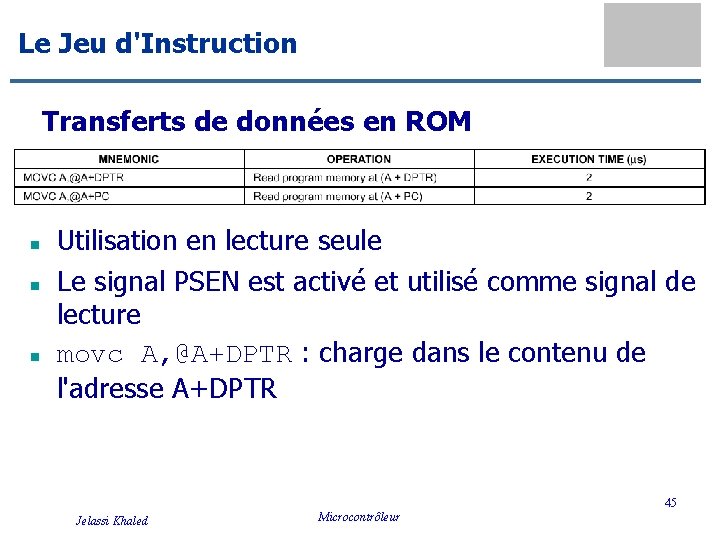

Le Jeu d'Instruction Transferts de données en ROM n n n Utilisation en lecture seule Le signal PSEN est activé et utilisé comme signal de lecture movc A, @A+DPTR : charge dans le contenu de l'adresse A+DPTR 45 Jelassi Khaled Microcontrôleur

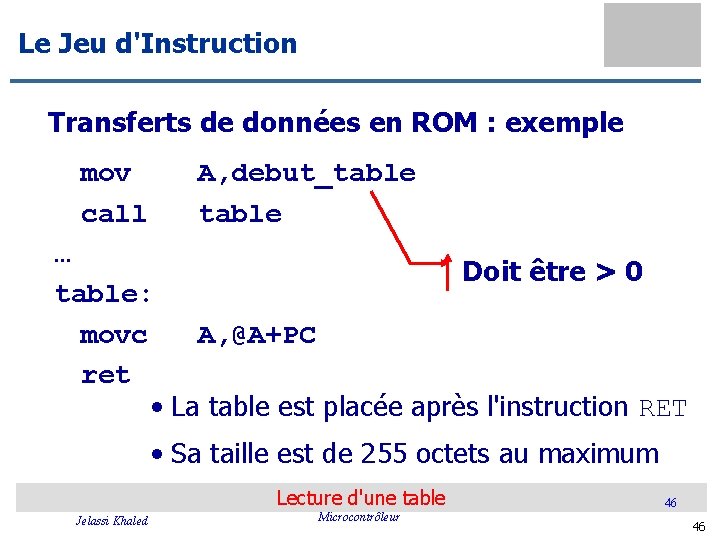

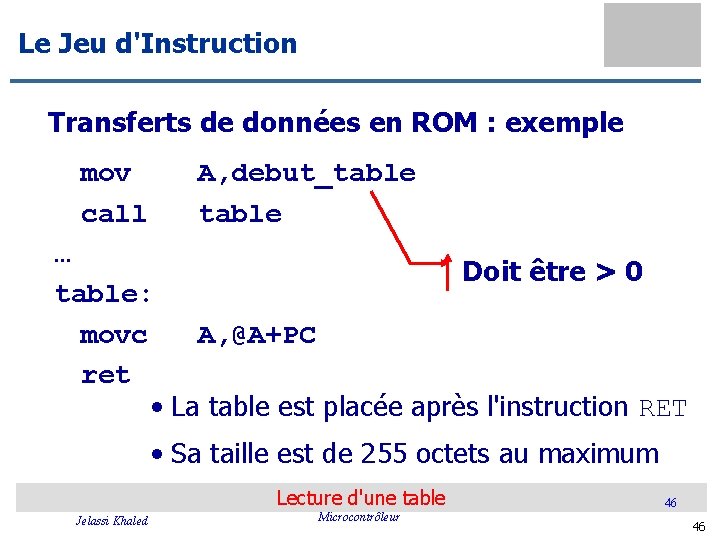

Le Jeu d'Instruction Transferts de données en ROM : exemple mov call A, debut_table … Doit être > 0 table: movc A, @A+PC ret • La table est placée après l'instruction RET • Sa taille est de 255 octets au maximum Lecture d'une table Jelassi Khaled Microcontrôleur 46 46

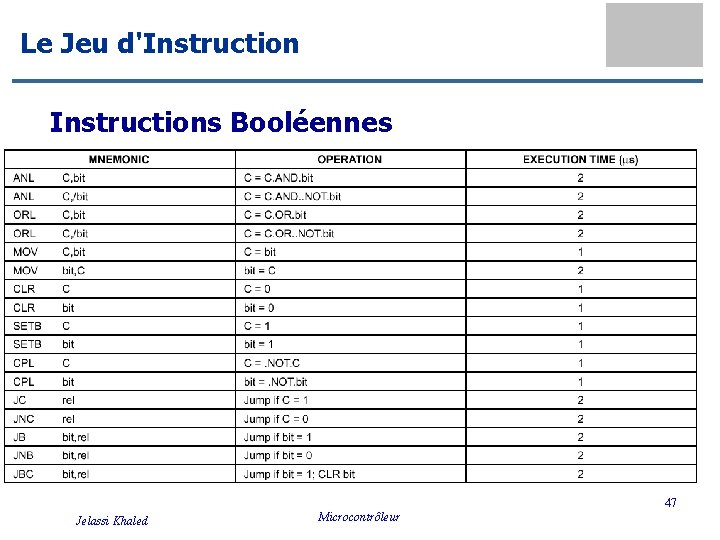

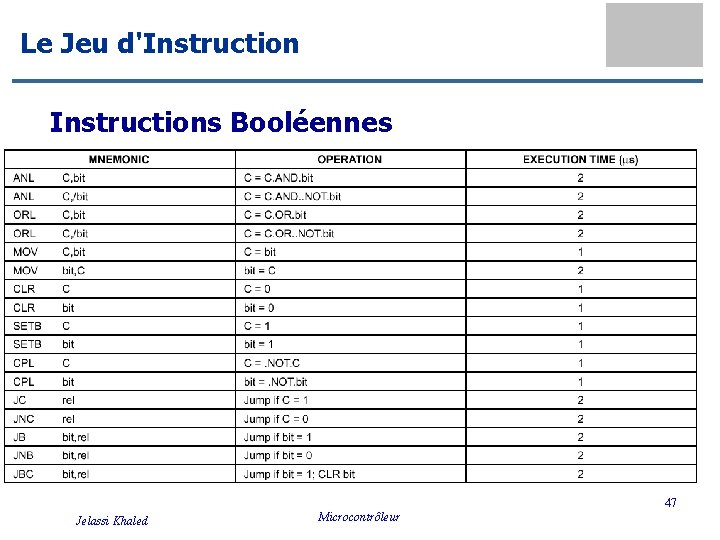

Le Jeu d'Instructions Booléennes 47 Jelassi Khaled Microcontrôleur

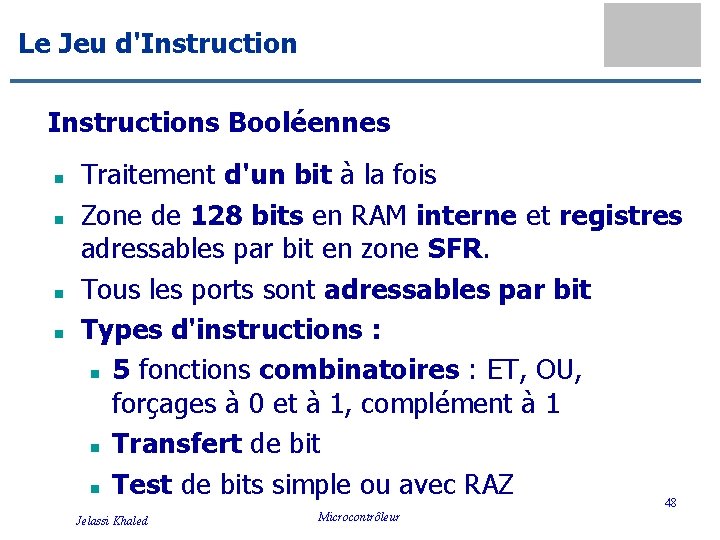

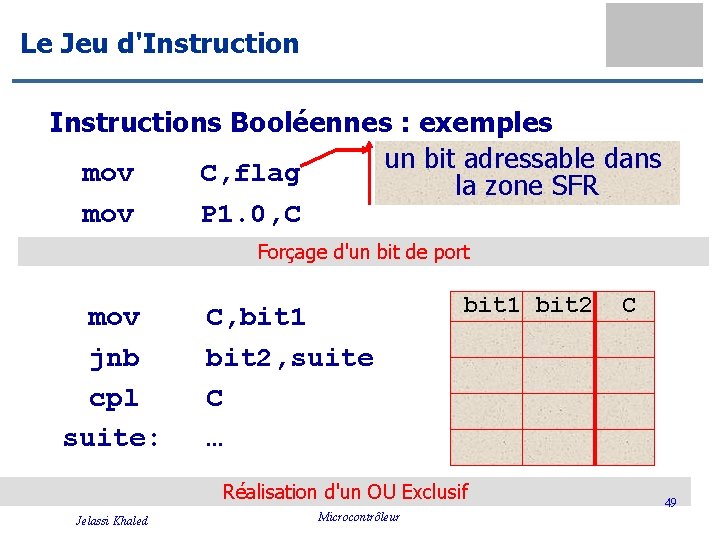

Le Jeu d'Instructions Booléennes n n Traitement d'un bit à la fois Zone de 128 bits en RAM interne et registres adressables par bit en zone SFR. Tous les ports sont adressables par bit Types d'instructions : n 5 fonctions combinatoires : ET, OU, forçages à 0 et à 1, complément à 1 n Transfert de bit n Test de bits simple ou avec RAZ 48 Jelassi Khaled Microcontrôleur

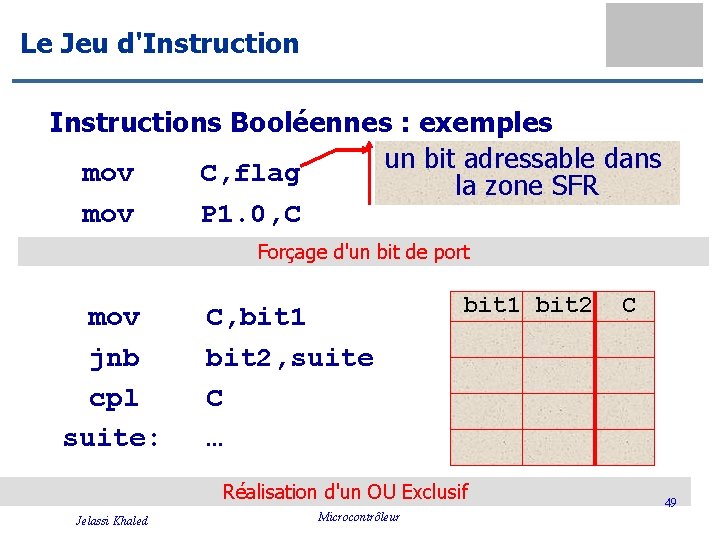

Le Jeu d'Instructions Booléennes : exemples un bit adressable dans mov C, flag la zone SFR mov P 1. 0, C Forçage d'un bit de port mov jnb cpl suite: C, bit 1 bit 2, suite C … bit 1 bit 2 Réalisation d'un OU Exclusif Jelassi Khaled Microcontrôleur C 49

Le Jeu d'Instructions Booléennes : sauts relatifs n n La destination du saut n'est pas une adresse mais un déplacement (offset) signé. Exprimé sur 1 octet, il est donc compris entre -128 et +127 50 Jelassi Khaled Microcontrôleur

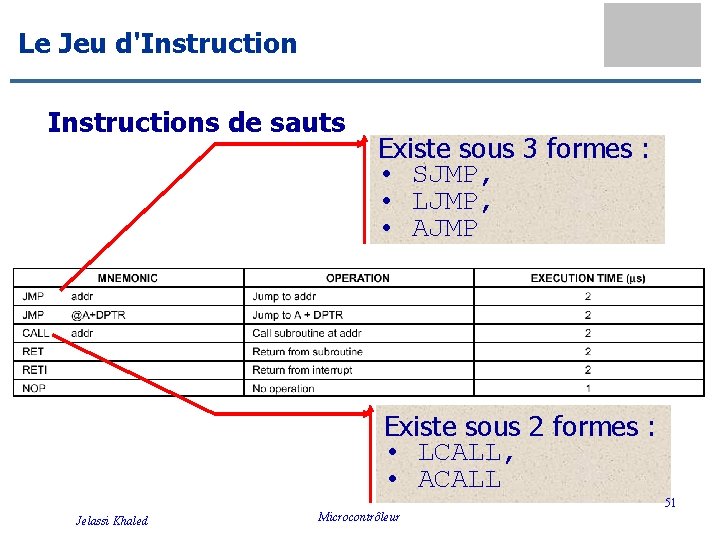

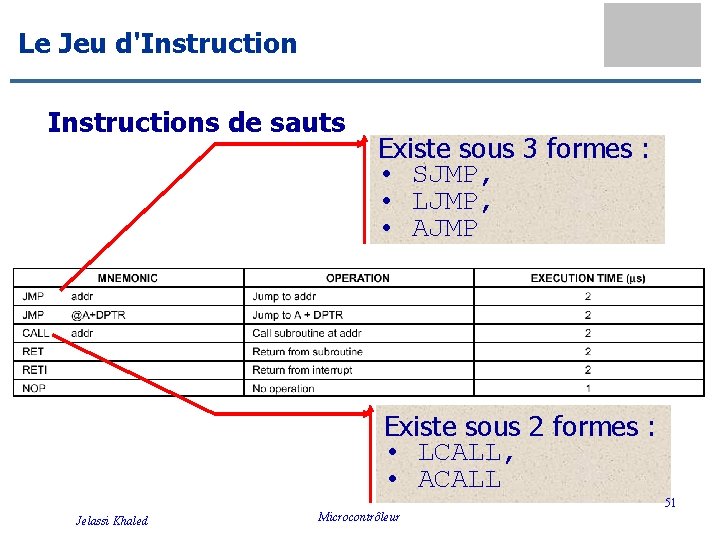

Le Jeu d'Instructions de sauts Existe sous 3 formes : • SJMP, • LJMP, • AJMP Existe sous 2 formes : • LCALL, • ACALL 51 Jelassi Khaled Microcontrôleur

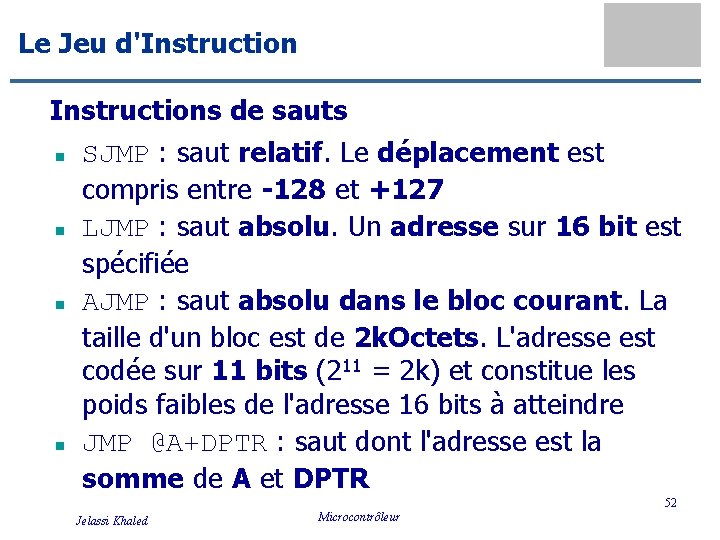

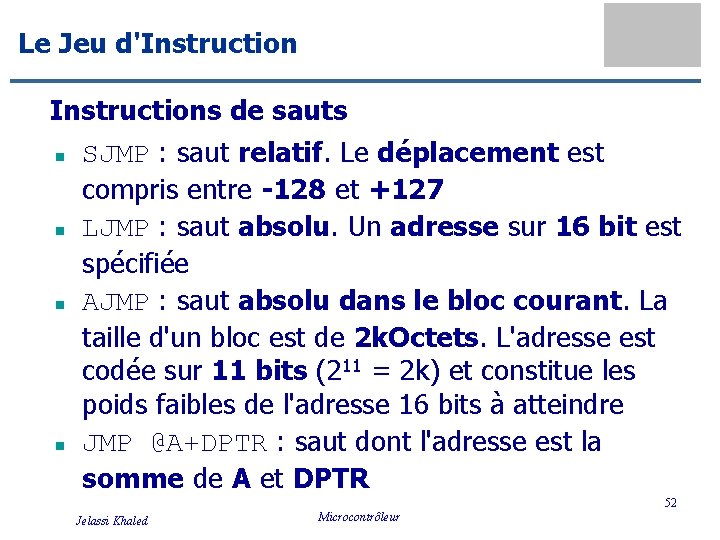

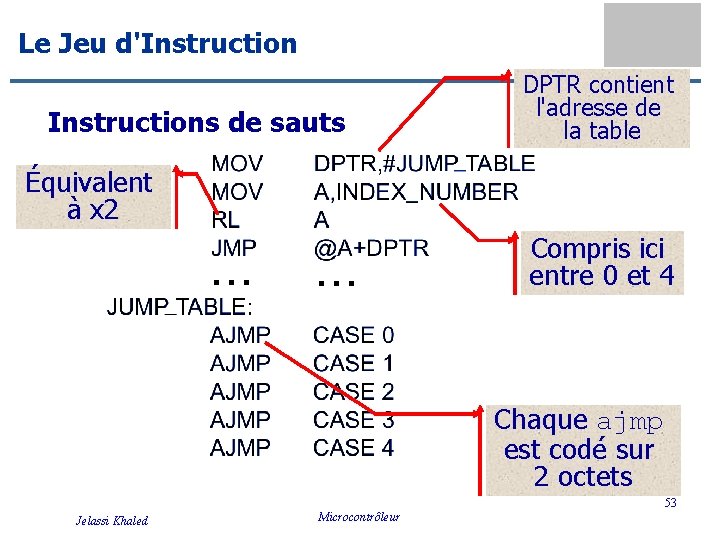

Le Jeu d'Instructions de sauts n n SJMP : saut relatif. Le déplacement est compris entre -128 et +127 LJMP : saut absolu. Un adresse sur 16 bit est spécifiée AJMP : saut absolu dans le bloc courant. La taille d'un bloc est de 2 k. Octets. L'adresse est codée sur 11 bits (211 = 2 k) et constitue les poids faibles de l'adresse 16 bits à atteindre JMP @A+DPTR : saut dont l'adresse est la somme de A et DPTR 52 Jelassi Khaled Microcontrôleur

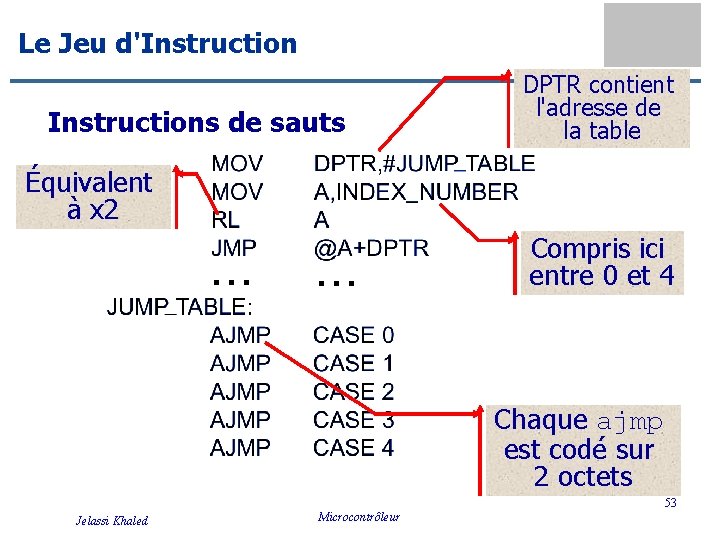

Le Jeu d'Instructions de sauts DPTR contient l'adresse de la table Équivalent à x 2 Compris ici entre 0 et 4 Chaque ajmp est codé sur 2 octets 53 Jelassi Khaled Microcontrôleur

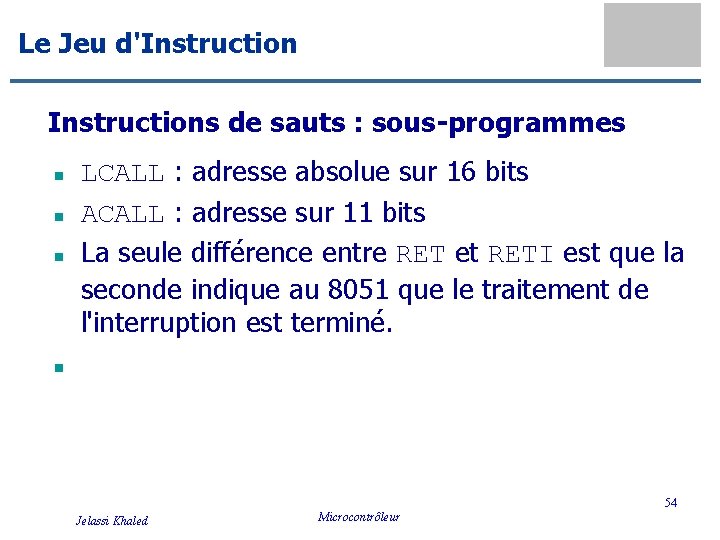

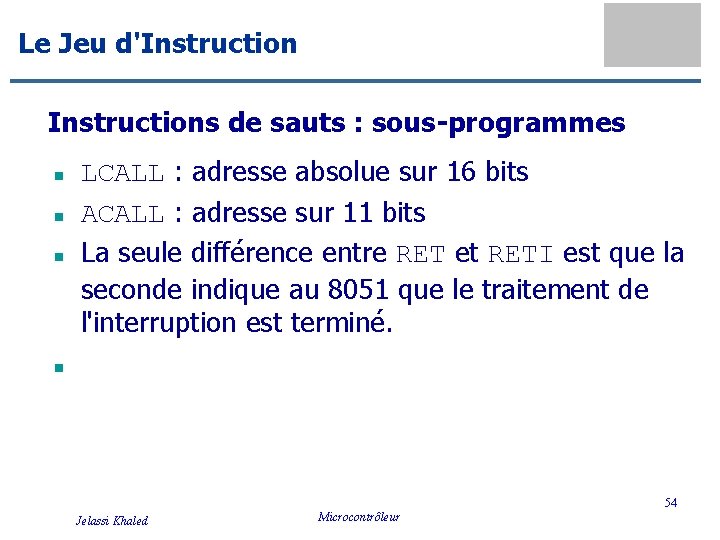

Le Jeu d'Instructions de sauts : sous-programmes n n LCALL : adresse absolue sur 16 bits ACALL : adresse sur 11 bits La seule différence entre RET et RETI est que la seconde indique au 8051 que le traitement de l'interruption est terminé. 54 Jelassi Khaled Microcontrôleur

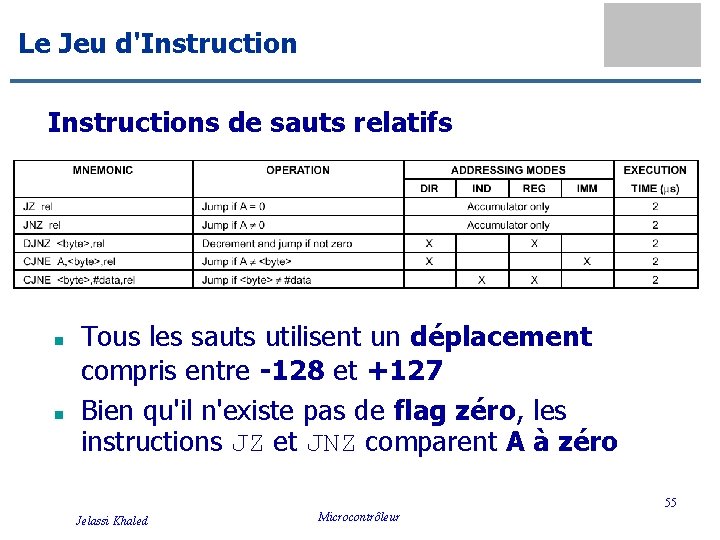

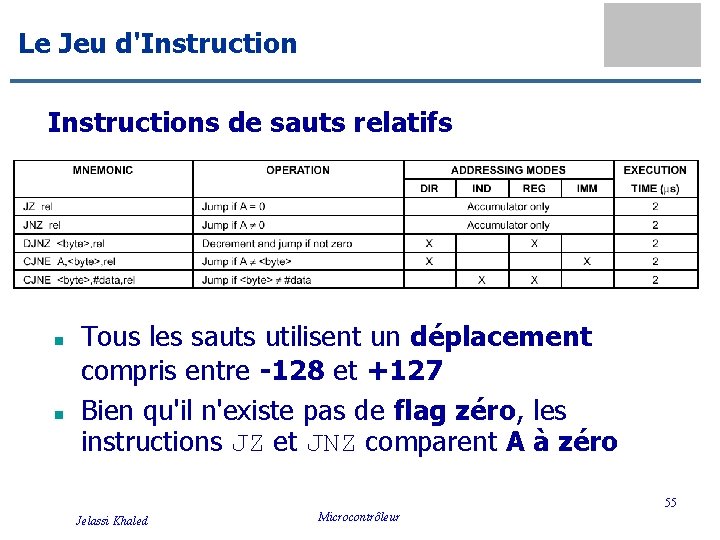

Le Jeu d'Instructions de sauts relatifs n n Tous les sauts utilisent un déplacement compris entre -128 et +127 Bien qu'il n'existe pas de flag zéro, les instructions JZ et JNZ comparent A à zéro 55 Jelassi Khaled Microcontrôleur

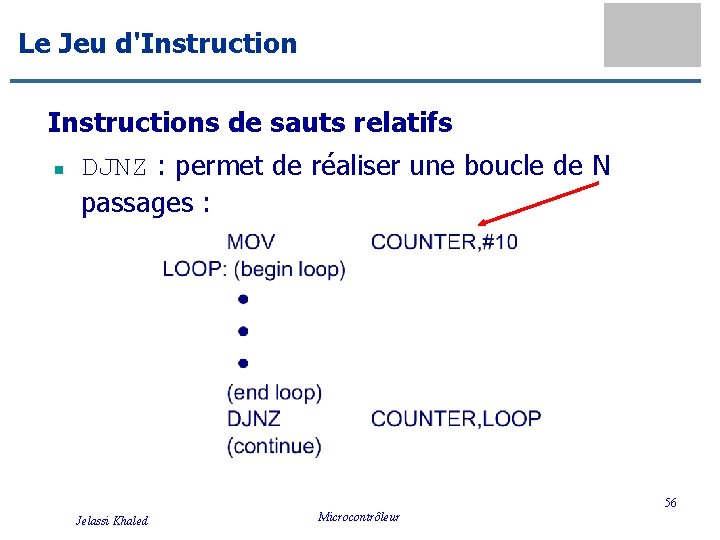

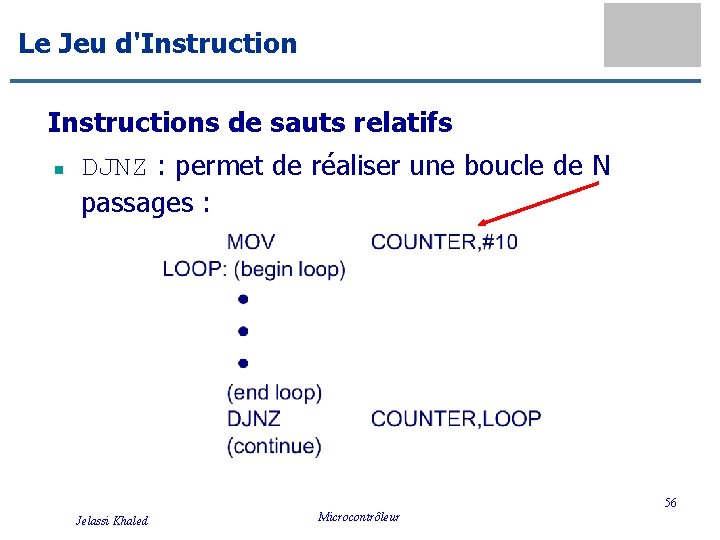

Le Jeu d'Instructions de sauts relatifs n DJNZ : permet de réaliser une boucle de N passages : 56 Jelassi Khaled Microcontrôleur

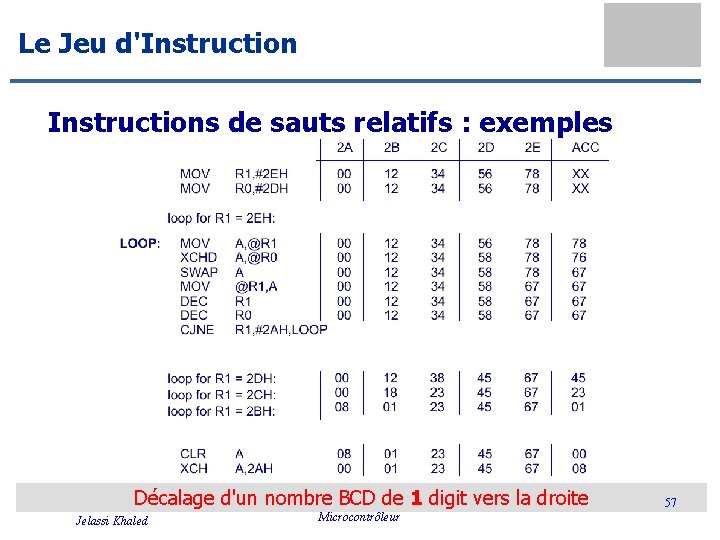

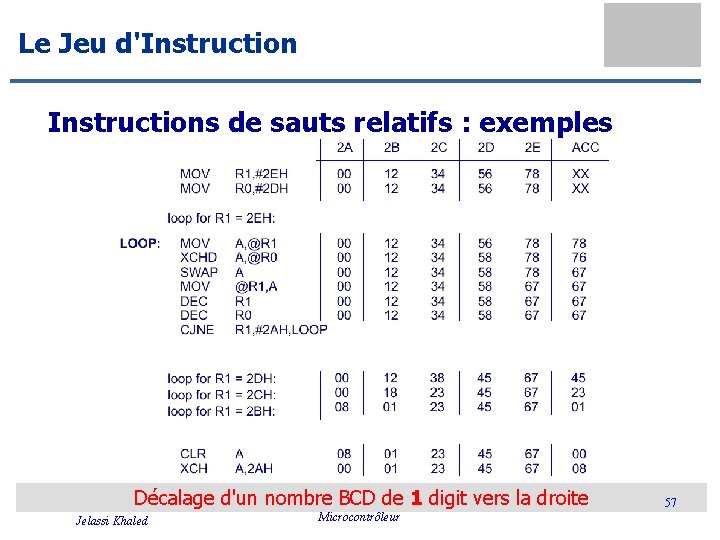

Le Jeu d'Instructions de sauts relatifs : exemples Décalage d'un nombre BCD de 1 digit vers la droite Jelassi Khaled Microcontrôleur 57

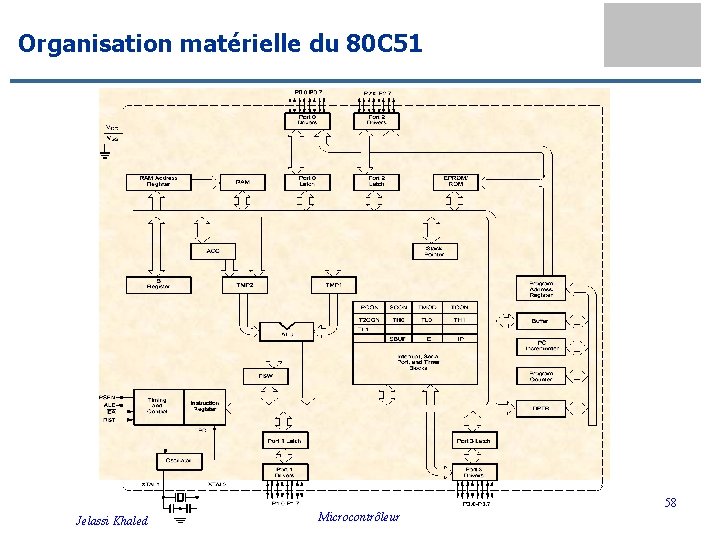

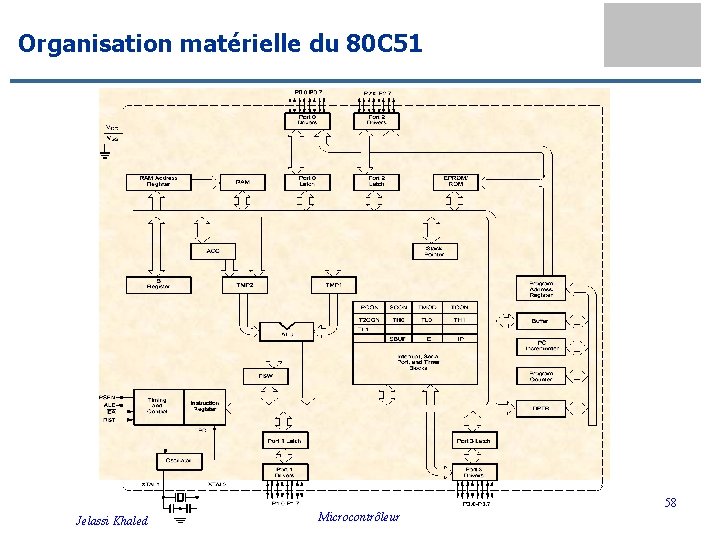

Organisation matérielle du 80 C 51 58 Jelassi Khaled Microcontrôleur

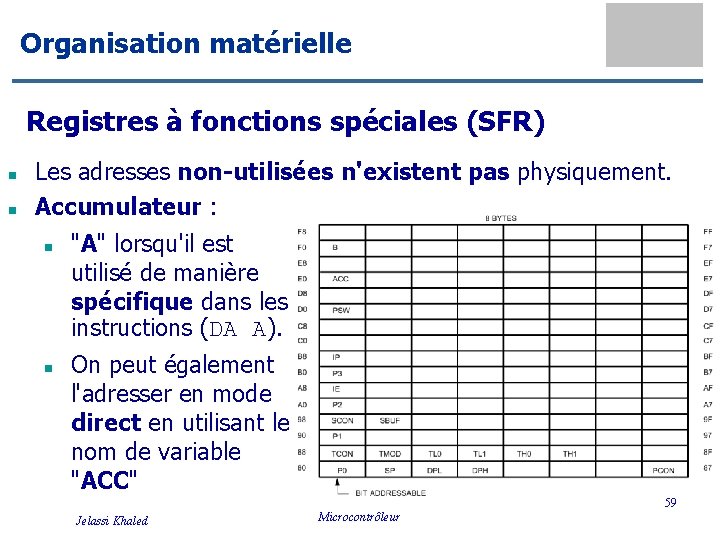

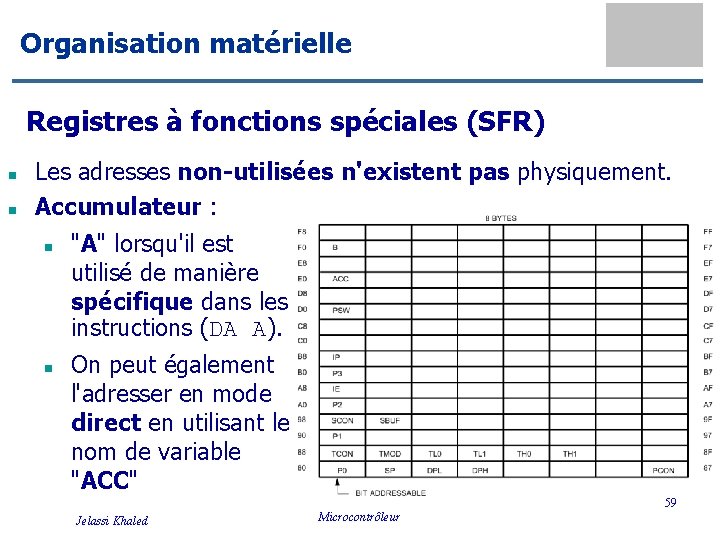

Organisation matérielle Registres à fonctions spéciales (SFR) n n Les adresses non-utilisées n'existent pas physiquement. Accumulateur : n n "A" lorsqu'il est utilisé de manière spécifique dans les instructions (DA A). On peut également l'adresser en mode direct en utilisant le nom de variable "ACC" 59 Jelassi Khaled Microcontrôleur

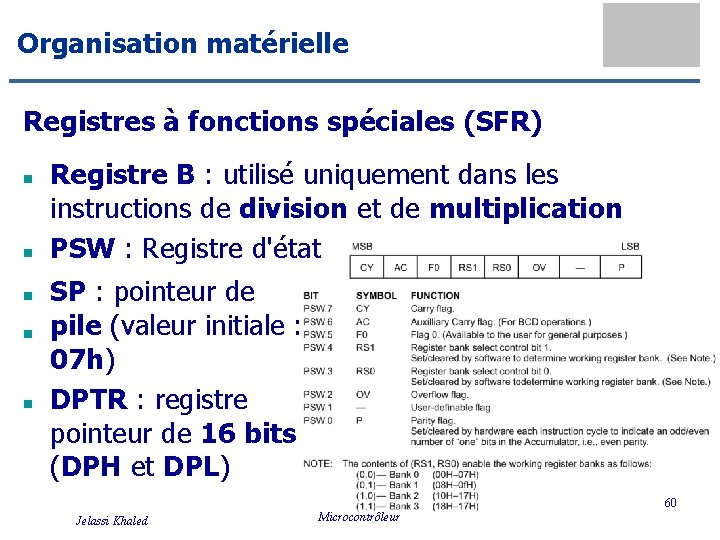

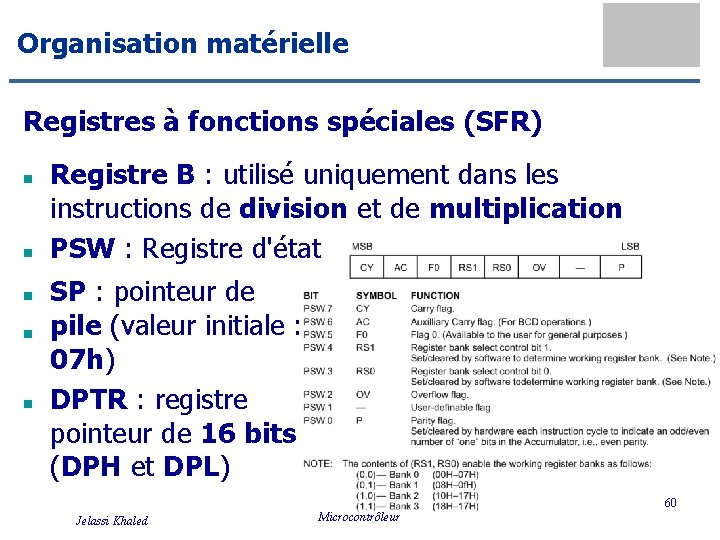

Organisation matérielle Registres à fonctions spéciales (SFR) n n Registre B : utilisé uniquement dans les instructions de division et de multiplication PSW : Registre d'état n SP : pointeur de n pile (valeur initiale : 07 h) n DPTR : registre pointeur de 16 bits (DPH et DPL) 60 Jelassi Khaled Microcontrôleur

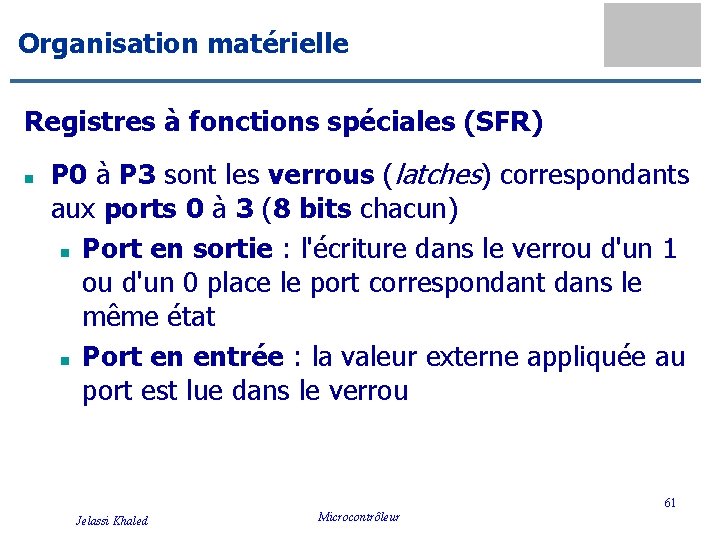

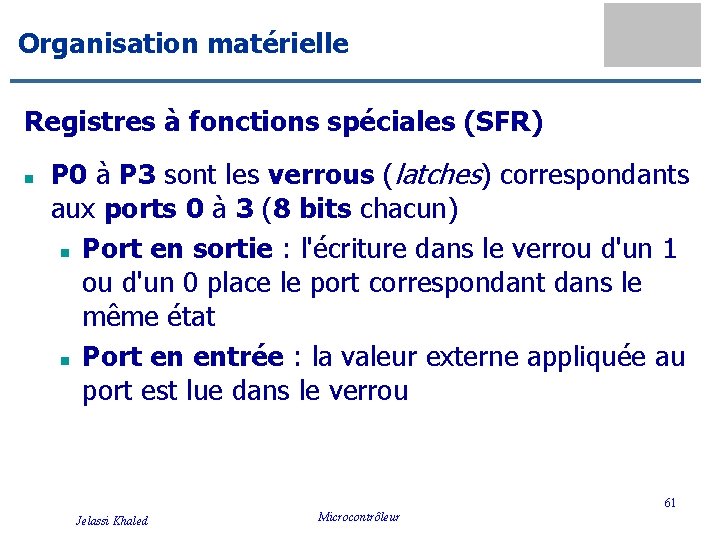

Organisation matérielle Registres à fonctions spéciales (SFR) n P 0 à P 3 sont les verrous (latches) correspondants aux ports 0 à 3 (8 bits chacun) n Port en sortie : l'écriture dans le verrou d'un 1 ou d'un 0 place le port correspondant dans le même état n Port en entrée : la valeur externe appliquée au port est lue dans le verrou 61 Jelassi Khaled Microcontrôleur

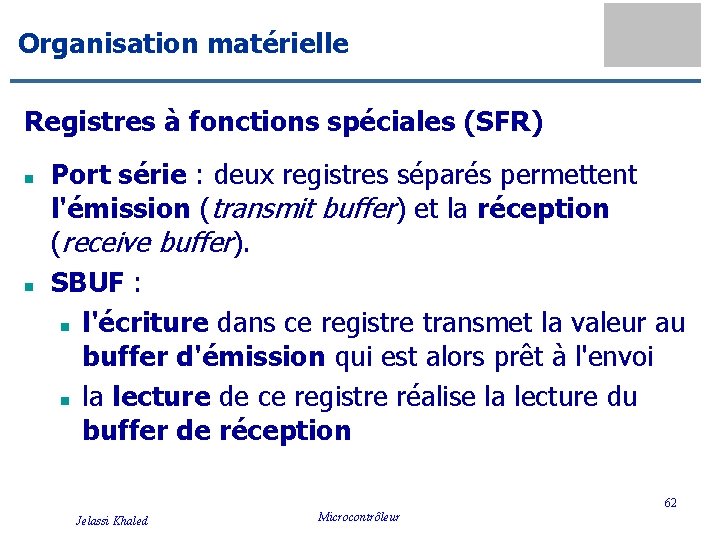

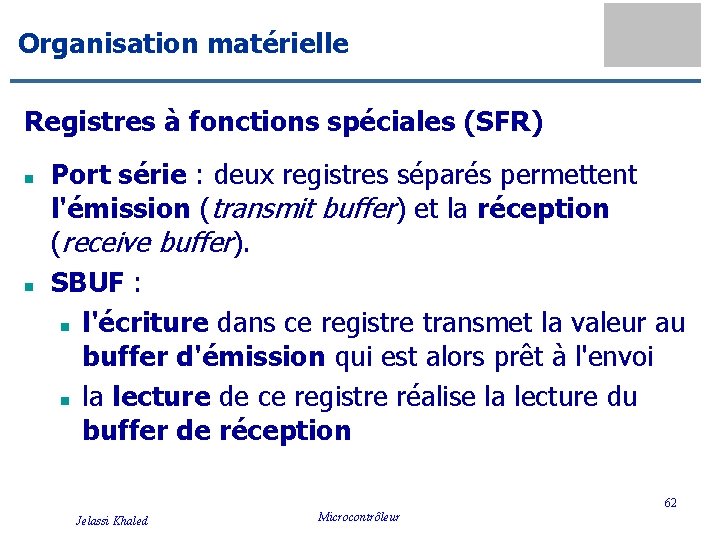

Organisation matérielle Registres à fonctions spéciales (SFR) n n Port série : deux registres séparés permettent l'émission (transmit buffer) et la réception (receive buffer). SBUF : n l'écriture dans ce registre transmet la valeur au buffer d'émission qui est alors prêt à l'envoi n la lecture de ce registre réalise la lecture du buffer de réception 62 Jelassi Khaled Microcontrôleur

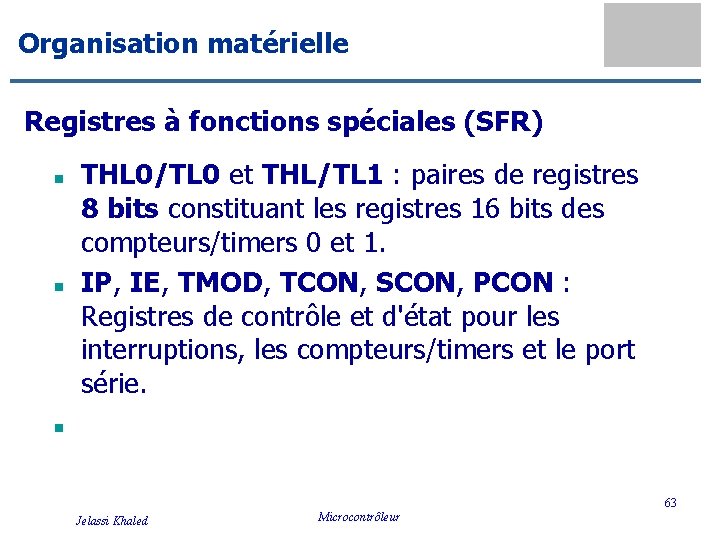

Organisation matérielle Registres à fonctions spéciales (SFR) n n n THL 0/TL 0 et THL/TL 1 : paires de registres 8 bits constituant les registres 16 bits des compteurs/timers 0 et 1. IP, IE, TMOD, TCON, SCON, PCON : Registres de contrôle et d'état pour les interruptions, les compteurs/timers et le port série. 63 Jelassi Khaled Microcontrôleur

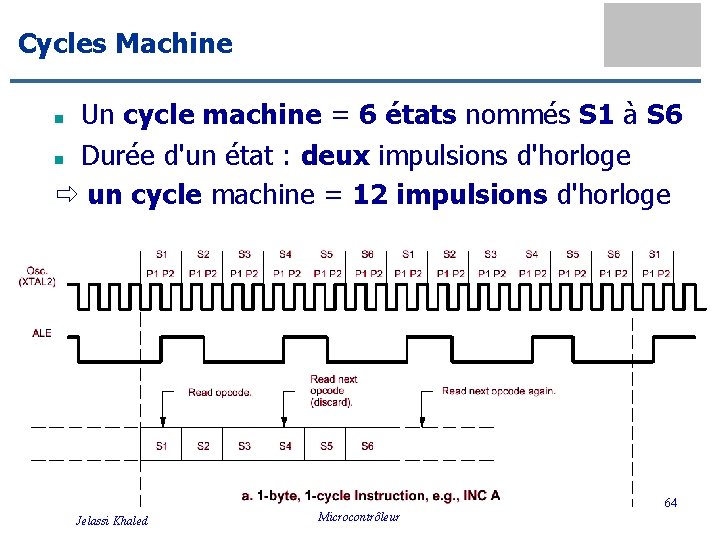

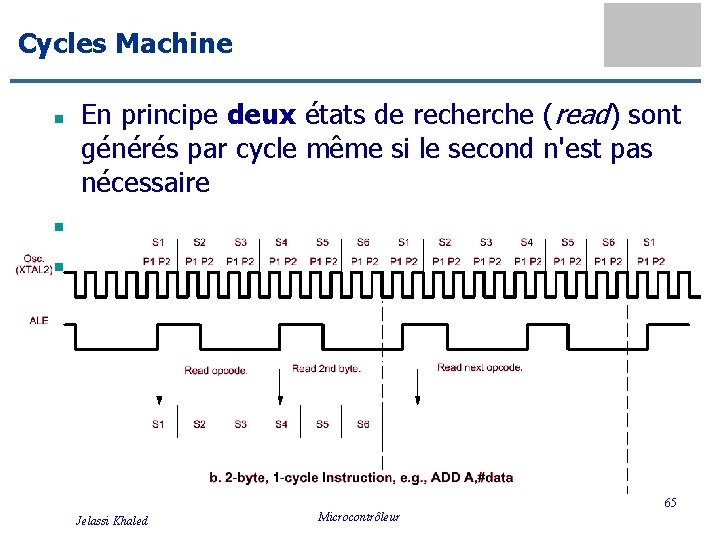

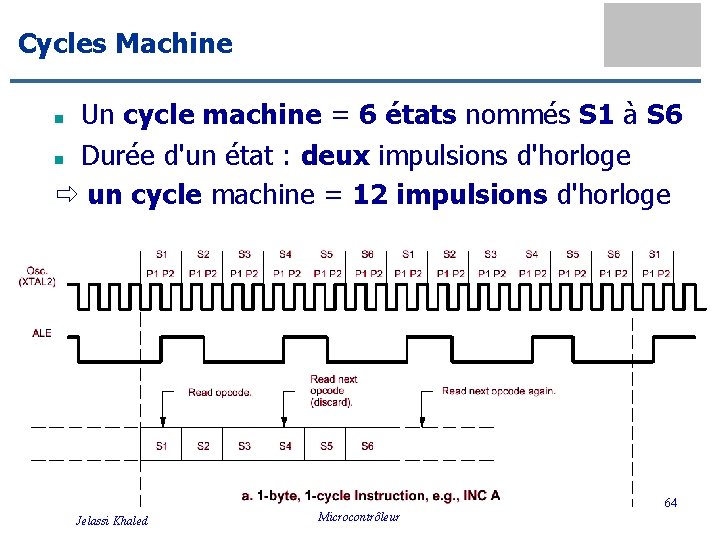

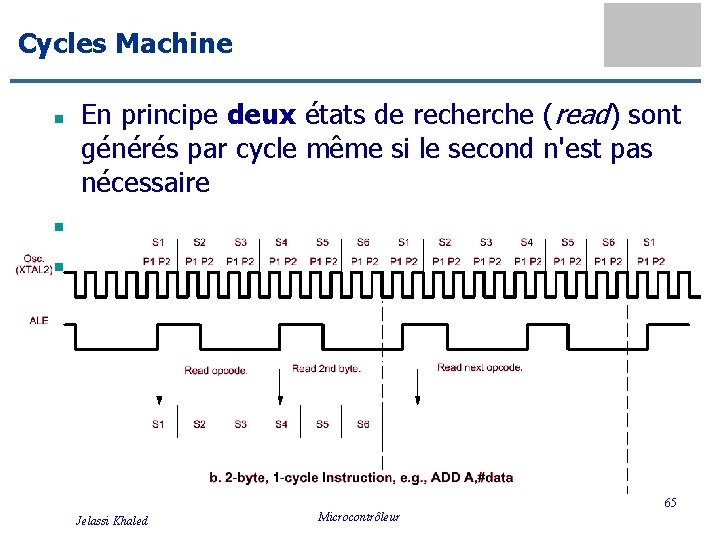

Cycles Machine Un cycle machine = 6 états nommés S 1 à S 6 n Durée d'un état : deux impulsions d'horloge un cycle machine = 12 impulsions d'horloge n 64 Jelassi Khaled Microcontrôleur

Cycles Machine n n n En principe deux états de recherche (read) sont générés par cycle même si le second n'est pas nécessaire 65 Jelassi Khaled Microcontrôleur

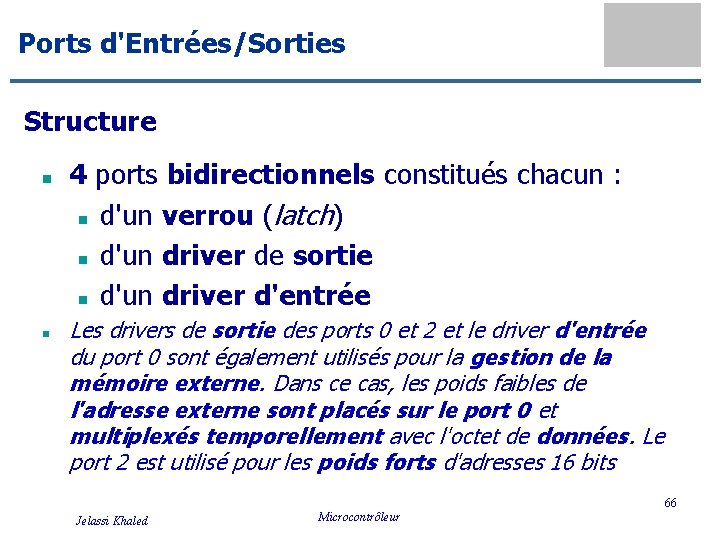

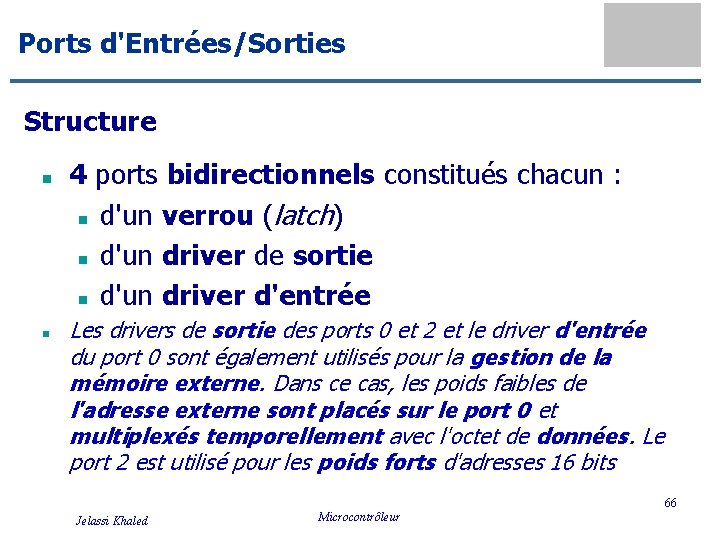

Ports d'Entrées/Sorties Structure n n 4 ports bidirectionnels constitués chacun : n d'un verrou (latch) n d'un driver de sortie n d'un driver d'entrée Les drivers de sortie des ports 0 et 2 et le driver d'entrée du port 0 sont également utilisés pour la gestion de la mémoire externe. Dans ce cas, les poids faibles de l'adresse externe sont placés sur le port 0 et multiplexés temporellement avec l'octet de données. Le port 2 est utilisé pour les poids forts d'adresses 16 bits 66 Jelassi Khaled Microcontrôleur

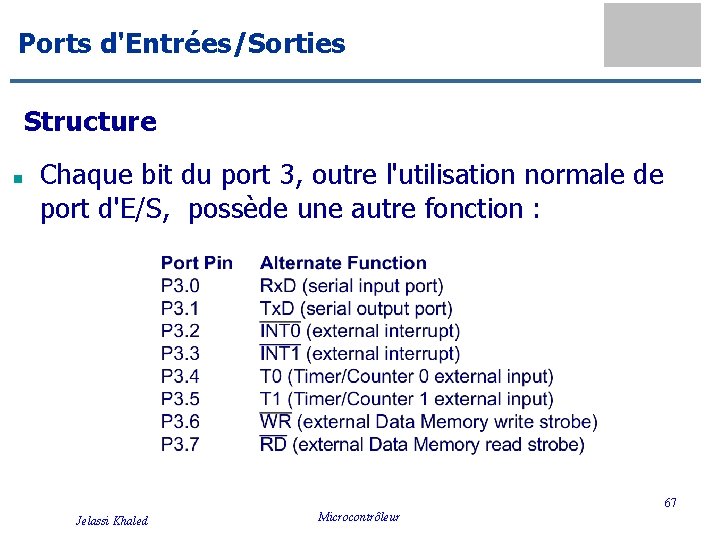

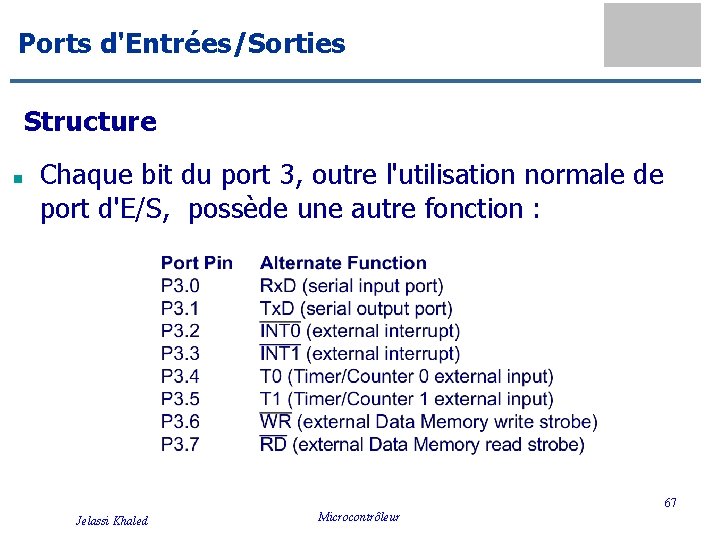

Ports d'Entrées/Sorties Structure n Chaque bit du port 3, outre l'utilisation normale de port d'E/S, possède une autre fonction : 67 Jelassi Khaled Microcontrôleur

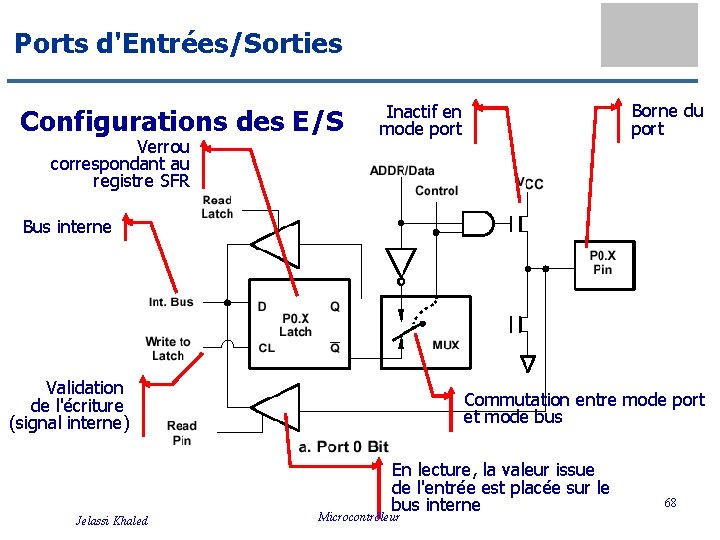

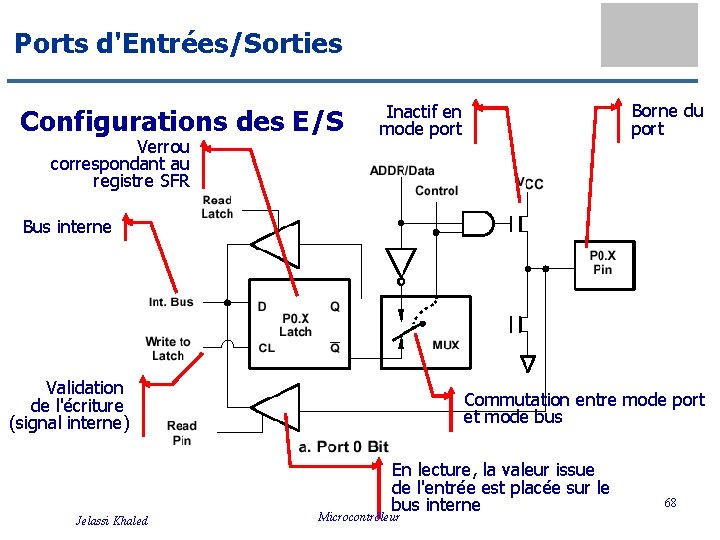

Ports d'Entrées/Sorties Configurations des E/S Verrou correspondant au registre SFR Inactif en mode port Borne du port Bus interne Validation de l'écriture (signal interne) Jelassi Khaled Commutation entre mode port et mode bus En lecture, la valeur issue de l'entrée est placée sur le bus interne Microcontrôleur 68

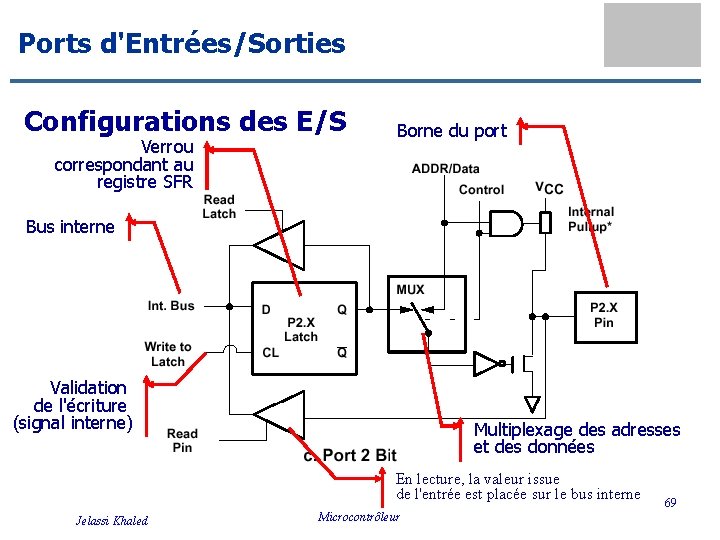

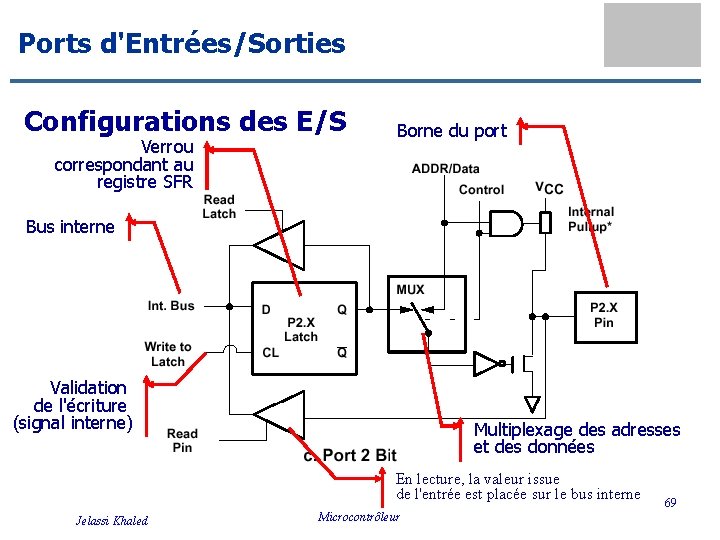

Ports d'Entrées/Sorties Configurations des E/S Verrou correspondant au registre SFR Borne du port Bus interne Validation de l'écriture (signal interne) Multiplexage des adresses et des données En lecture, la valeur issue de l'entrée est placée sur le bus interne Jelassi Khaled Microcontrôleur 69

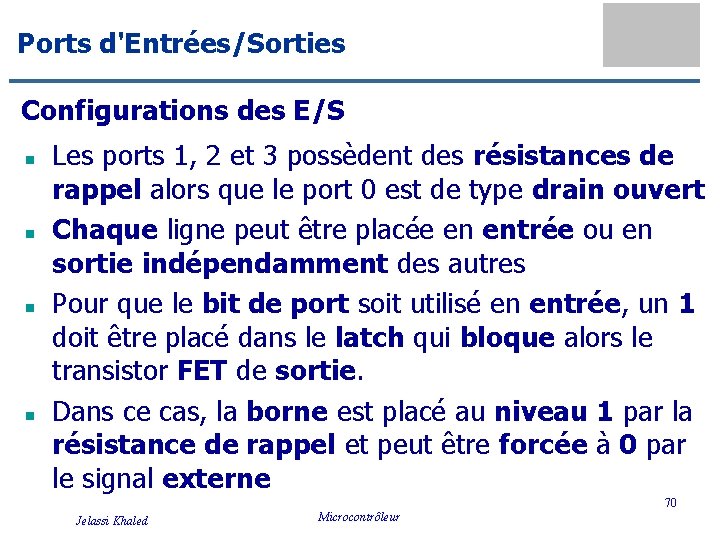

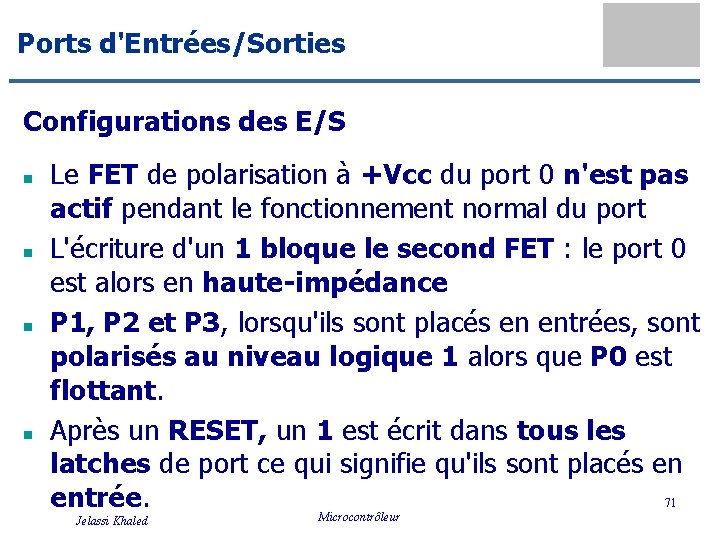

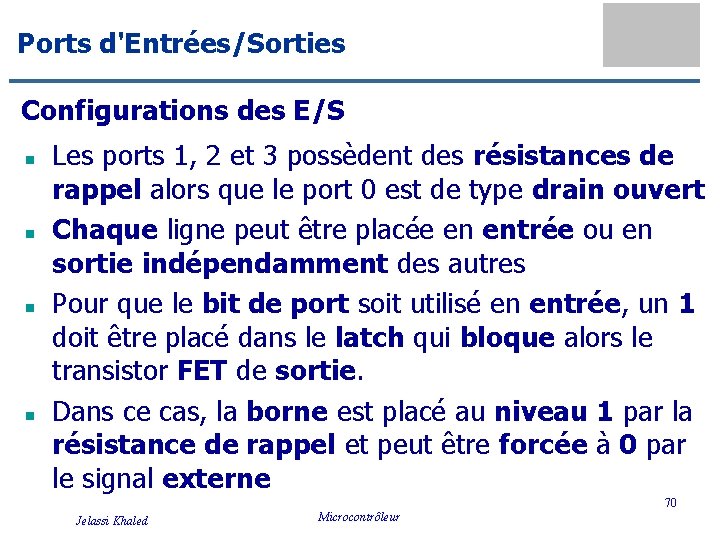

Ports d'Entrées/Sorties Configurations des E/S n n Les ports 1, 2 et 3 possèdent des résistances de rappel alors que le port 0 est de type drain ouvert Chaque ligne peut être placée en entrée ou en sortie indépendamment des autres Pour que le bit de port soit utilisé en entrée, un 1 doit être placé dans le latch qui bloque alors le transistor FET de sortie. Dans ce cas, la borne est placé au niveau 1 par la résistance de rappel et peut être forcée à 0 par le signal externe 70 Jelassi Khaled Microcontrôleur

Ports d'Entrées/Sorties Configurations des E/S n n Le FET de polarisation à +Vcc du port 0 n'est pas actif pendant le fonctionnement normal du port L'écriture d'un 1 bloque le second FET : le port 0 est alors en haute-impédance P 1, P 2 et P 3, lorsqu'ils sont placés en entrées, sont polarisés au niveau logique 1 alors que P 0 est flottant. Après un RESET, un 1 est écrit dans tous les latches de port ce qui signifie qu'ils sont placés en 71 entrée. Jelassi Khaled Microcontrôleur

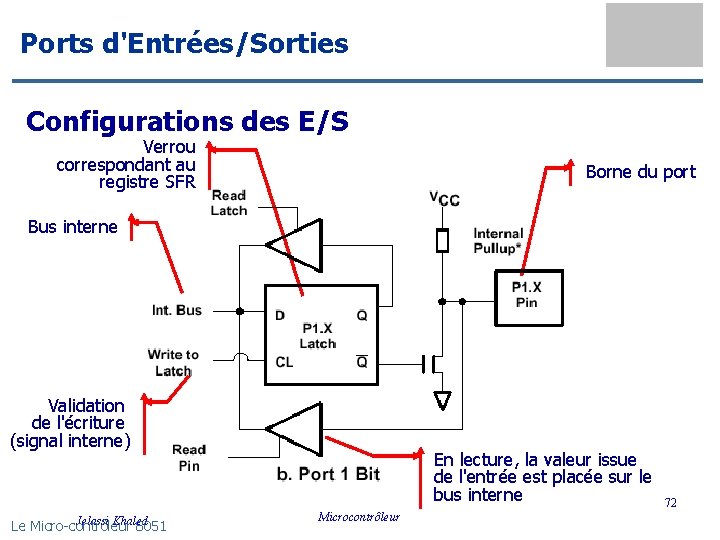

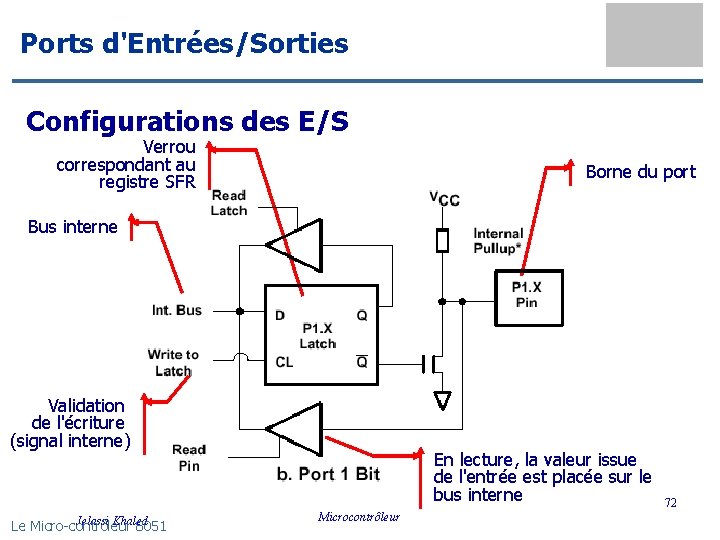

Ports d'Entrées/Sorties Configurations des E/S Verrou correspondant au registre SFR Borne du port Bus interne Validation de l'écriture (signal interne) Jelassi Khaled Le Micro-contrôleur 8051 En lecture, la valeur issue de l'entrée est placée sur le bus interne Microcontrôleur 72

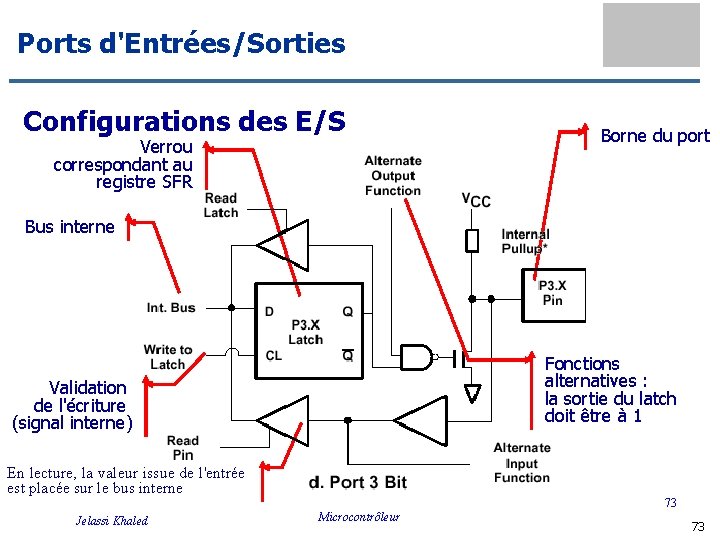

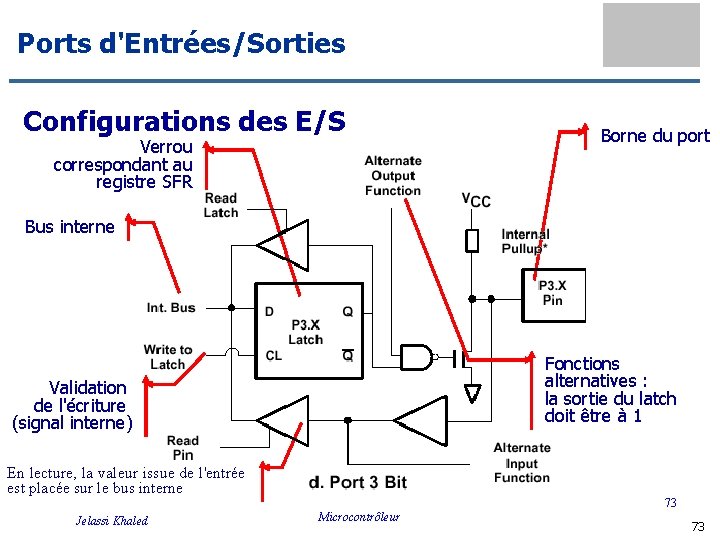

Ports d'Entrées/Sorties Configurations des E/S Verrou correspondant au registre SFR Borne du port Bus interne Fonctions alternatives : la sortie du latch doit être à 1 Validation de l'écriture (signal interne) En lecture, la valeur issue de l'entrée est placée sur le bus interne Jelassi Khaled 73 Microcontrôleur 73

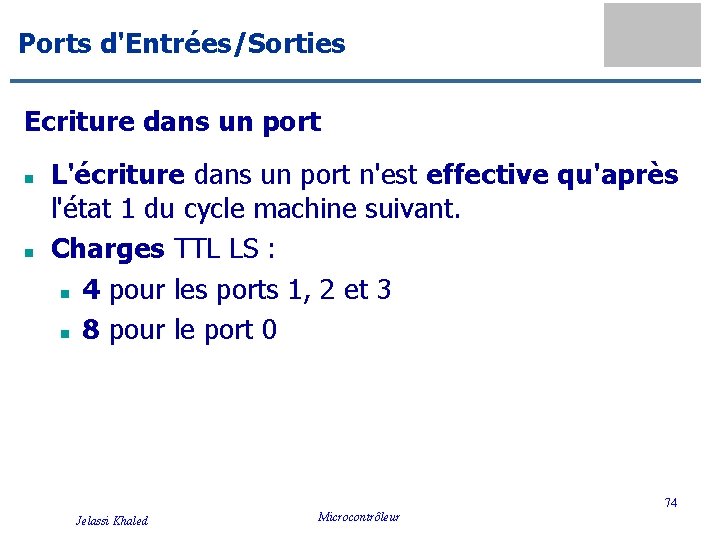

Ports d'Entrées/Sorties Ecriture dans un port n n L'écriture dans un port n'est effective qu'après l'état 1 du cycle machine suivant. Charges TTL LS : n 4 pour les ports 1, 2 et 3 n 8 pour le port 0 74 Jelassi Khaled Microcontrôleur

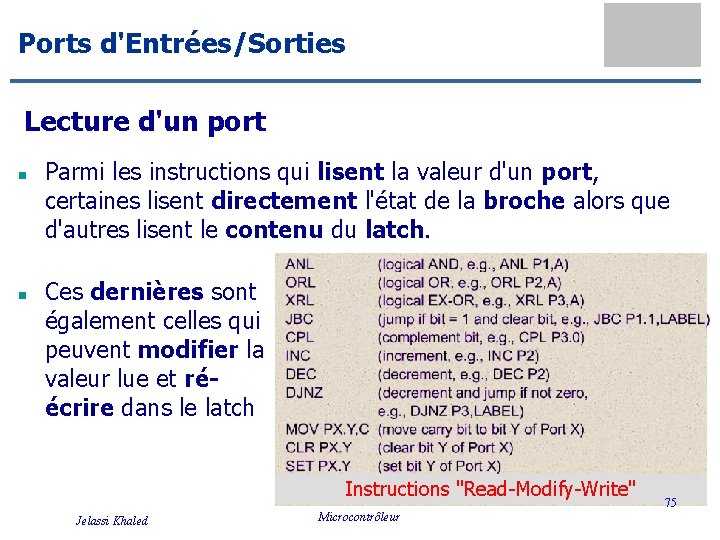

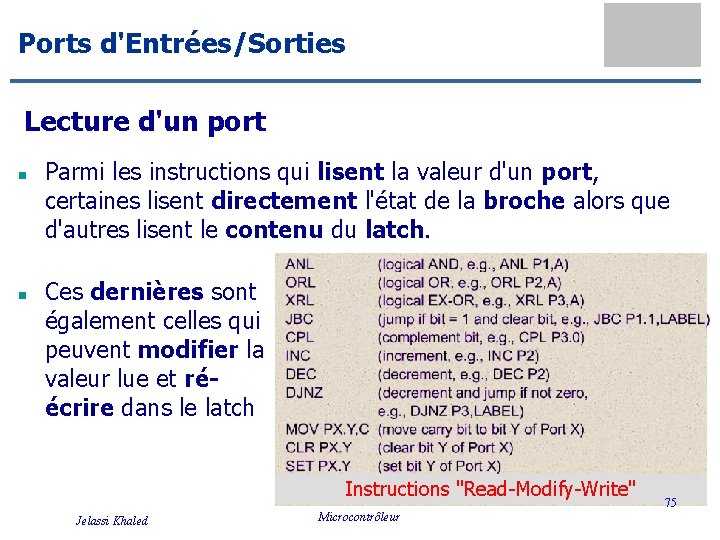

Ports d'Entrées/Sorties Lecture d'un port n n Parmi les instructions qui lisent la valeur d'un port, certaines lisent directement l'état de la broche alors que d'autres lisent le contenu du latch. Ces dernières sont également celles qui peuvent modifier la valeur lue et réécrire dans le latch Instructions "Read-Modify-Write" Jelassi Khaled Microcontrôleur 75

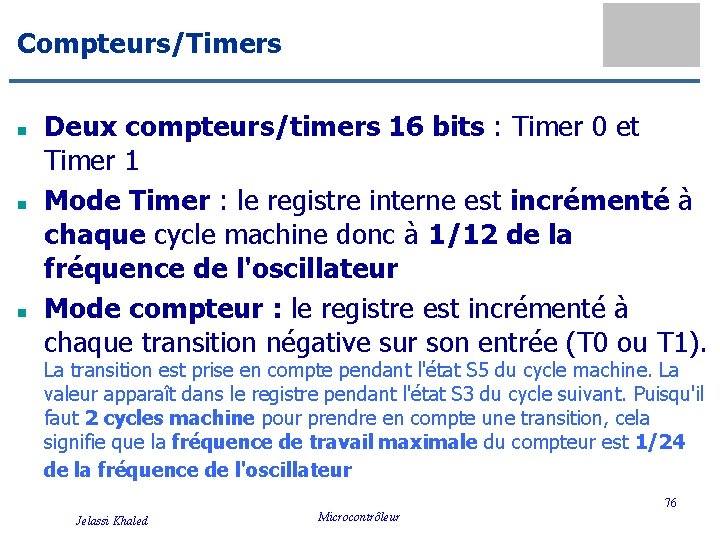

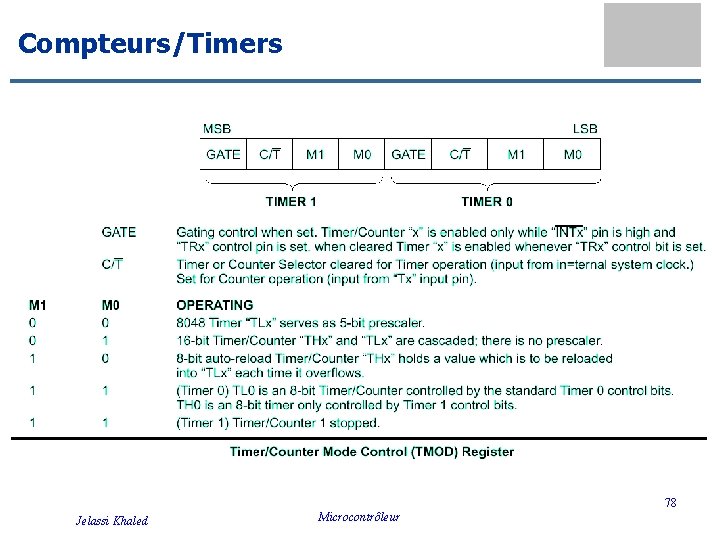

Compteurs/Timers n n n Deux compteurs/timers 16 bits : Timer 0 et Timer 1 Mode Timer : le registre interne est incrémenté à chaque cycle machine donc à 1/12 de la fréquence de l'oscillateur Mode compteur : le registre est incrémenté à chaque transition négative sur son entrée (T 0 ou T 1). La transition est prise en compte pendant l'état S 5 du cycle machine. La valeur apparaît dans le registre pendant l'état S 3 du cycle suivant. Puisqu'il faut 2 cycles machine pour prendre en compte une transition, cela signifie que la fréquence de travail maximale du compteur est 1/24 de la fréquence de l'oscillateur 76 Jelassi Khaled Microcontrôleur

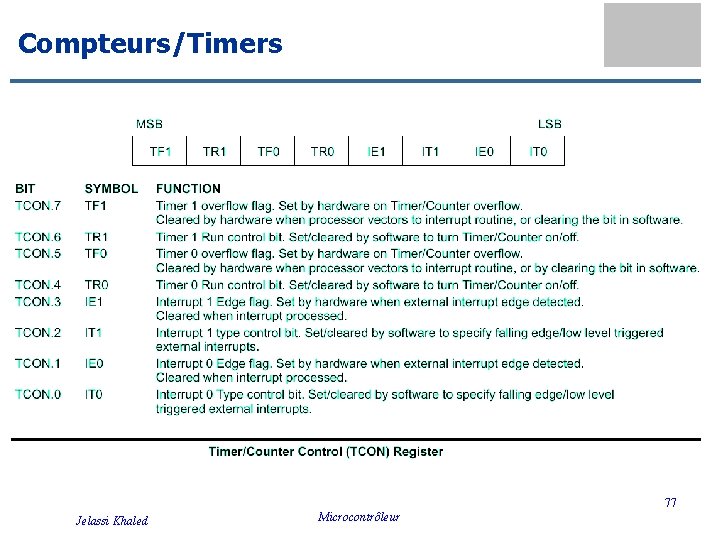

Compteurs/Timers 77 Jelassi Khaled Microcontrôleur

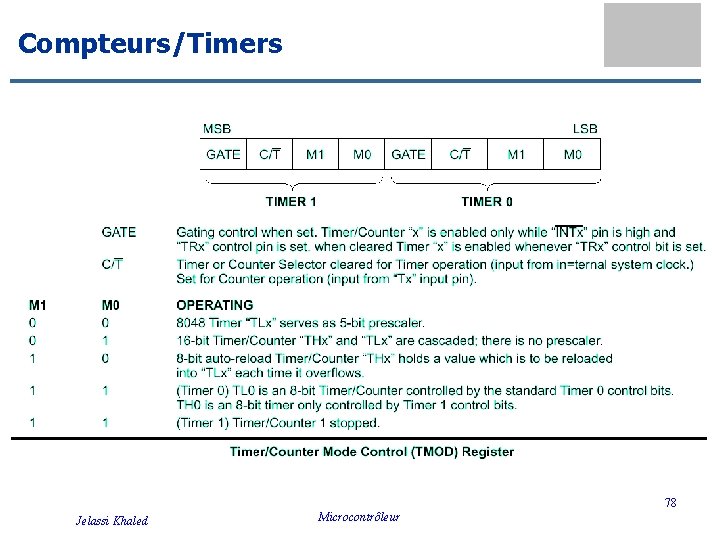

Compteurs/Timers 78 Jelassi Khaled Microcontrôleur

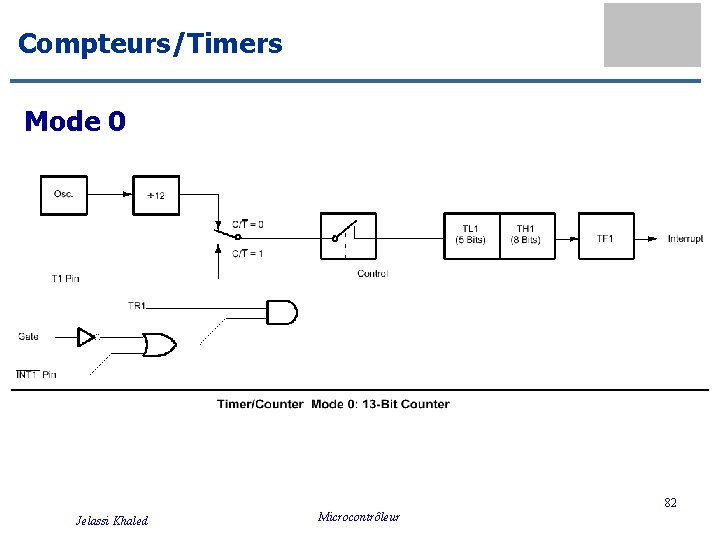

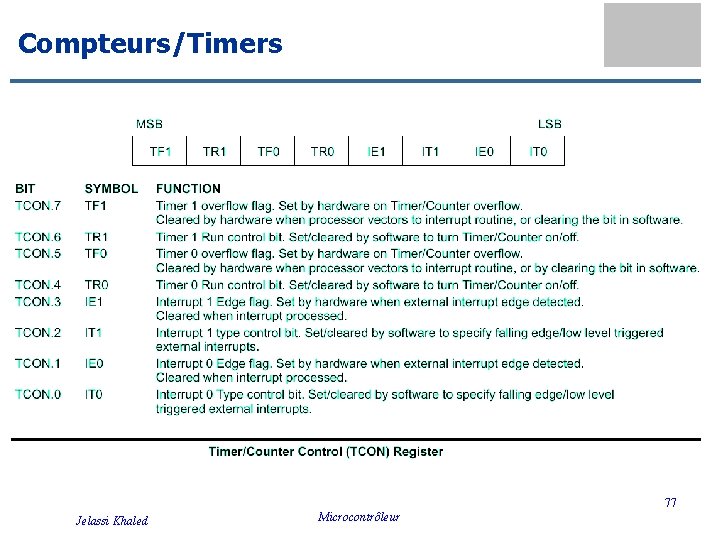

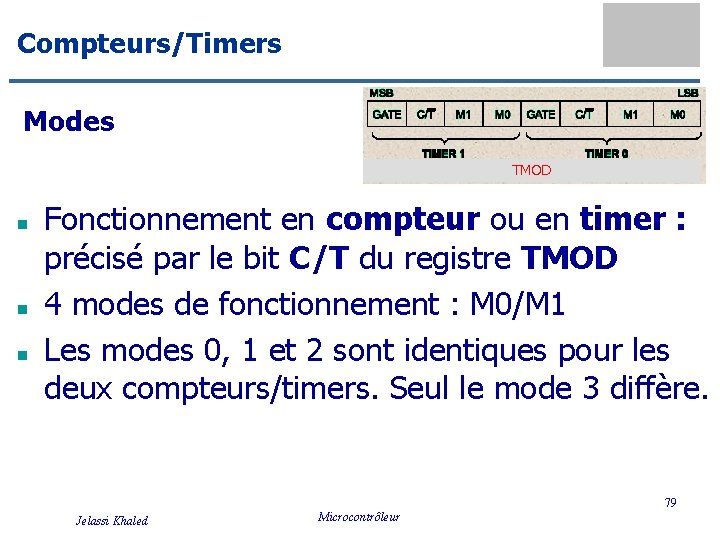

Compteurs/Timers Modes TMOD n n n Fonctionnement en compteur ou en timer : précisé par le bit C/T du registre TMOD 4 modes de fonctionnement : M 0/M 1 Les modes 0, 1 et 2 sont identiques pour les deux compteurs/timers. Seul le mode 3 diffère. 79 Jelassi Khaled Microcontrôleur

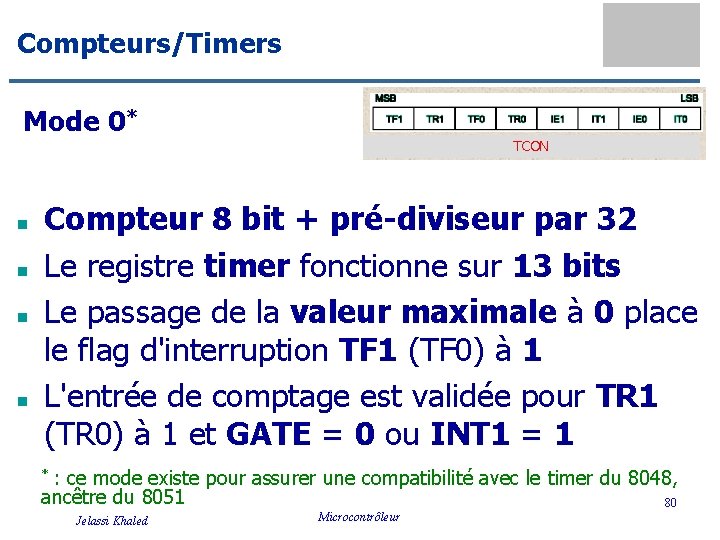

Compteurs/Timers Mode 0* TCON n n Compteur 8 bit + pré-diviseur par 32 Le registre timer fonctionne sur 13 bits Le passage de la valeur maximale à 0 place le flag d'interruption TF 1 (TF 0) à 1 L'entrée de comptage est validée pour TR 1 (TR 0) à 1 et GATE = 0 ou INT 1 = 1 * : ce mode existe pour assurer une compatibilité avec le timer du 8048, ancêtre du 8051 Jelassi Khaled 80 Microcontrôleur

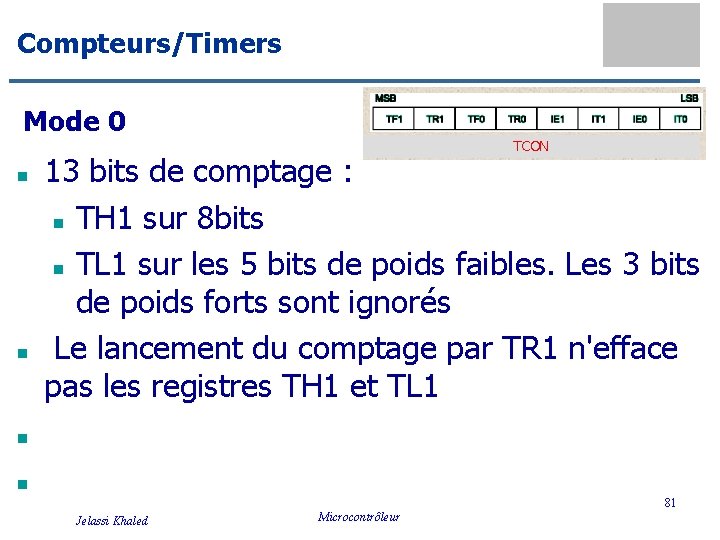

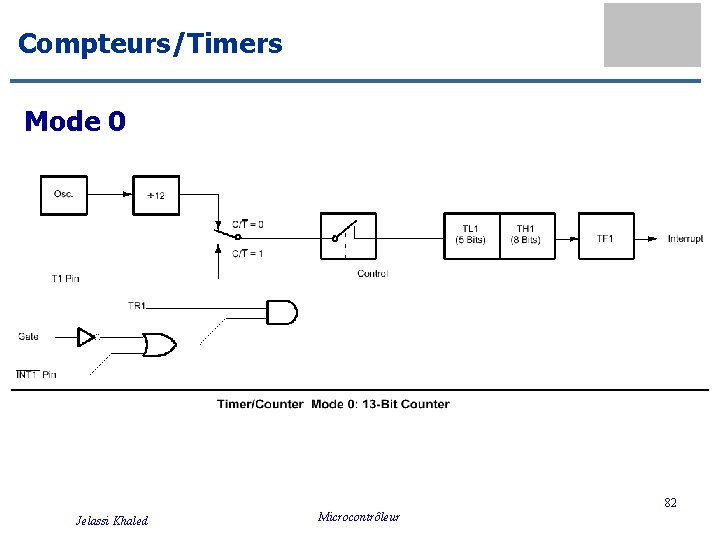

Compteurs/Timers Mode 0 TCON n n n 13 bits de comptage : n TH 1 sur 8 bits n TL 1 sur les 5 bits de poids faibles. Les 3 bits de poids forts sont ignorés Le lancement du comptage par TR 1 n'efface pas les registres TH 1 et TL 1 n 81 Jelassi Khaled Microcontrôleur

Compteurs/Timers Mode 0 82 Jelassi Khaled Microcontrôleur

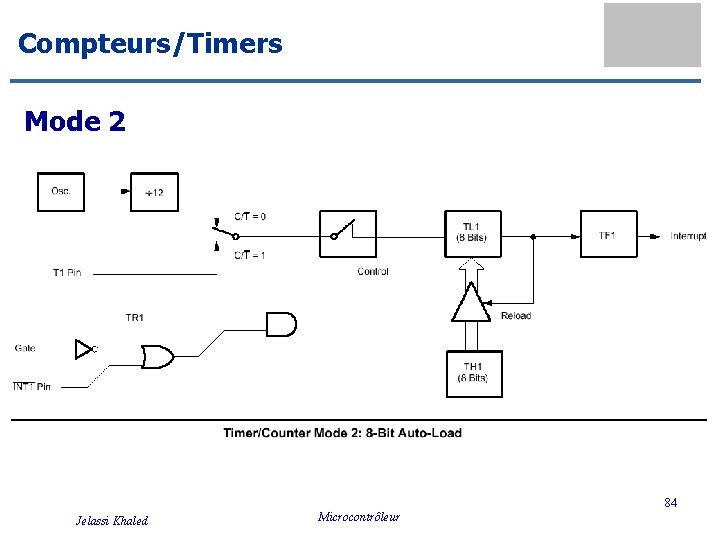

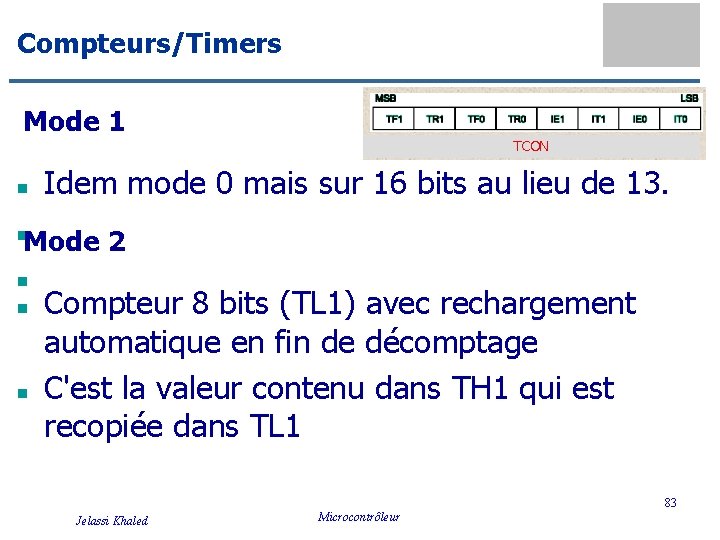

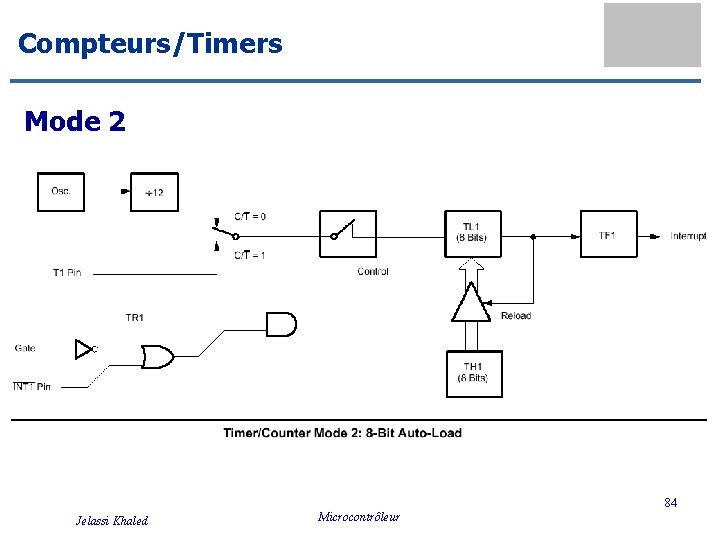

Compteurs/Timers Mode 1 TCON Idem mode 0 mais sur 16 bits au lieu de 13. n Mode 2 n n Compteur 8 bits (TL 1) avec rechargement automatique en fin de décomptage C'est la valeur contenu dans TH 1 qui est recopiée dans TL 1 83 Jelassi Khaled Microcontrôleur

Compteurs/Timers Mode 2 84 Jelassi Khaled Microcontrôleur

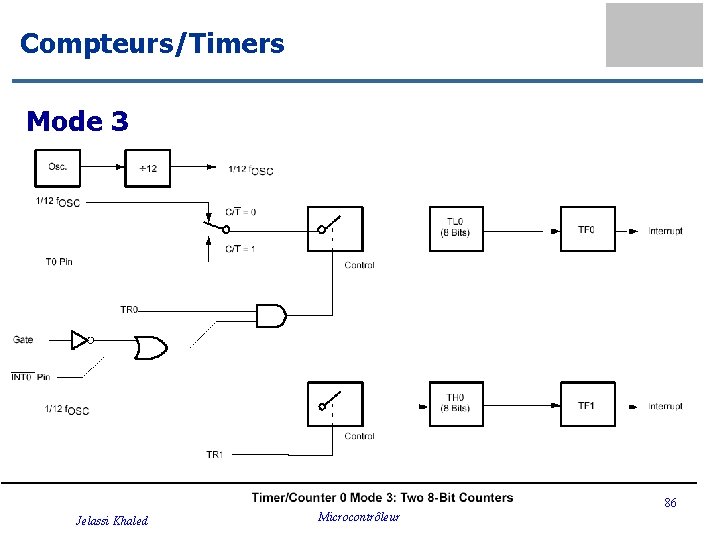

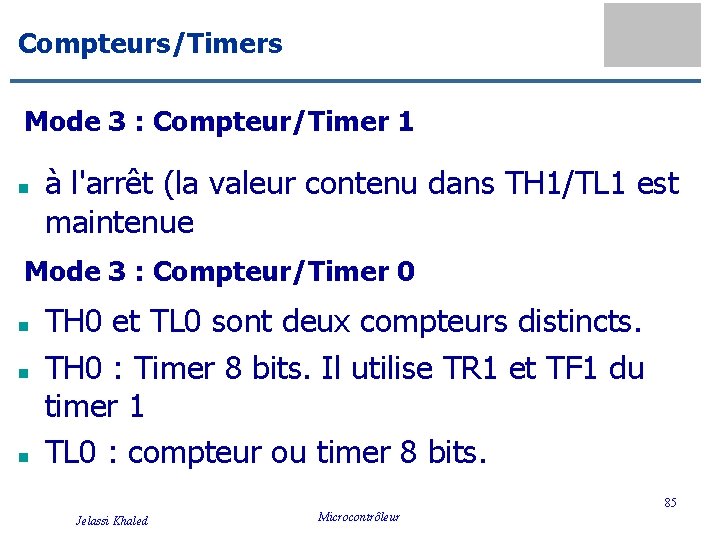

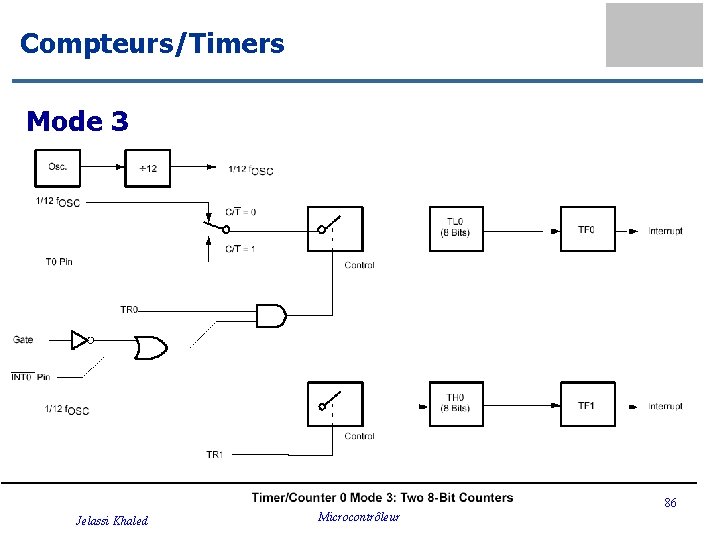

Compteurs/Timers Mode 3 : Compteur/Timer 1 n à l'arrêt (la valeur contenu dans TH 1/TL 1 est maintenue Mode 3 : Compteur/Timer 0 n n n TH 0 et TL 0 sont deux compteurs distincts. TH 0 : Timer 8 bits. Il utilise TR 1 et TF 1 du timer 1 TL 0 : compteur ou timer 8 bits. 85 Jelassi Khaled Microcontrôleur

Compteurs/Timers Mode 3 86 Jelassi Khaled Microcontrôleur

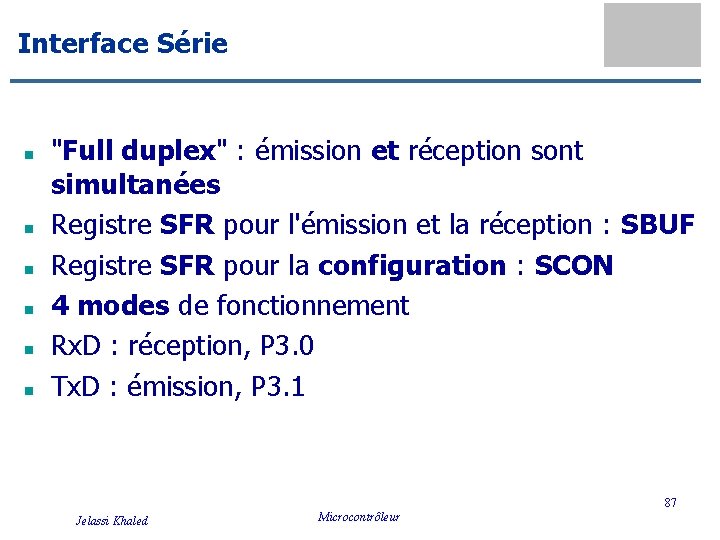

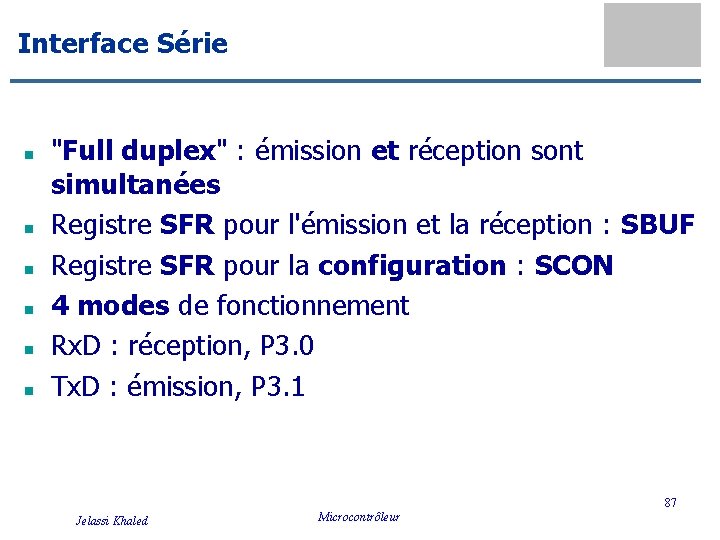

Interface Série n n n "Full duplex" : émission et réception sont simultanées Registre SFR pour l'émission et la réception : SBUF Registre SFR pour la configuration : SCON 4 modes de fonctionnement Rx. D : réception, P 3. 0 Tx. D : émission, P 3. 1 87 Jelassi Khaled Microcontrôleur

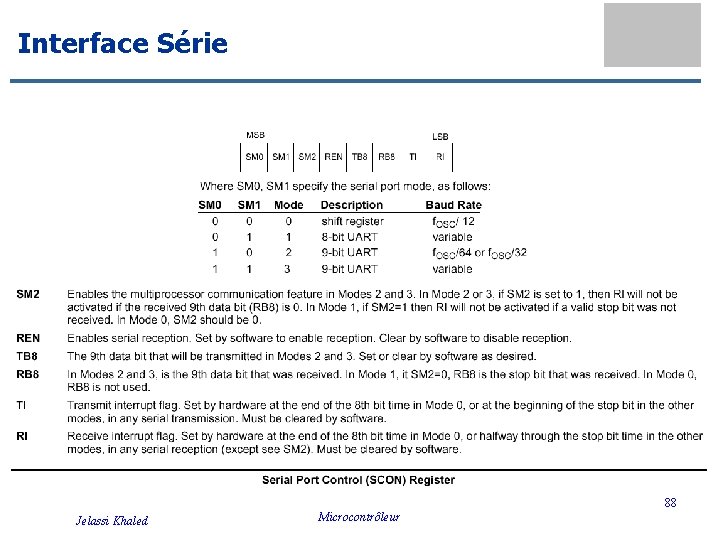

Interface Série 88 Jelassi Khaled Microcontrôleur

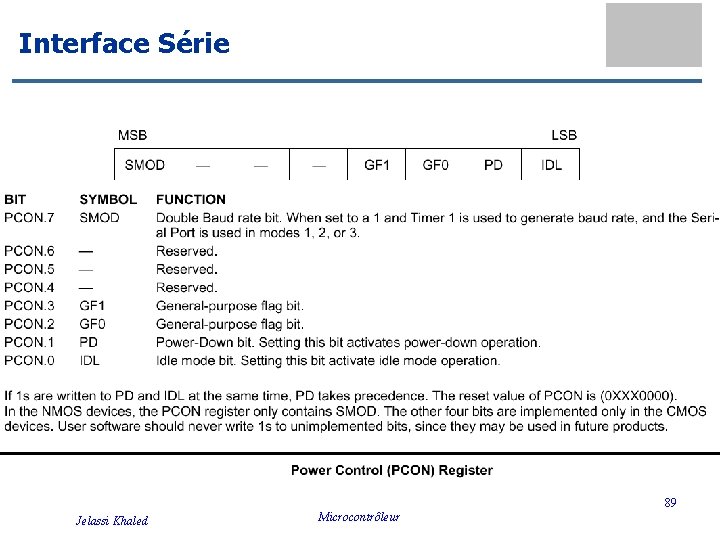

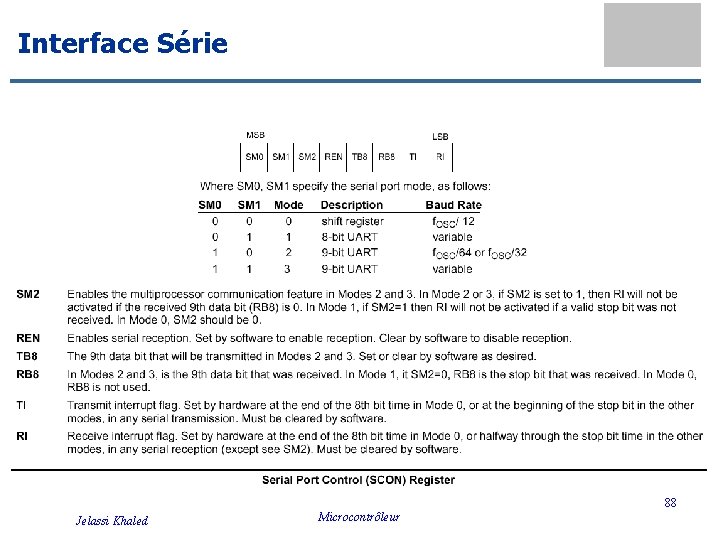

Interface Série 89 Jelassi Khaled Microcontrôleur

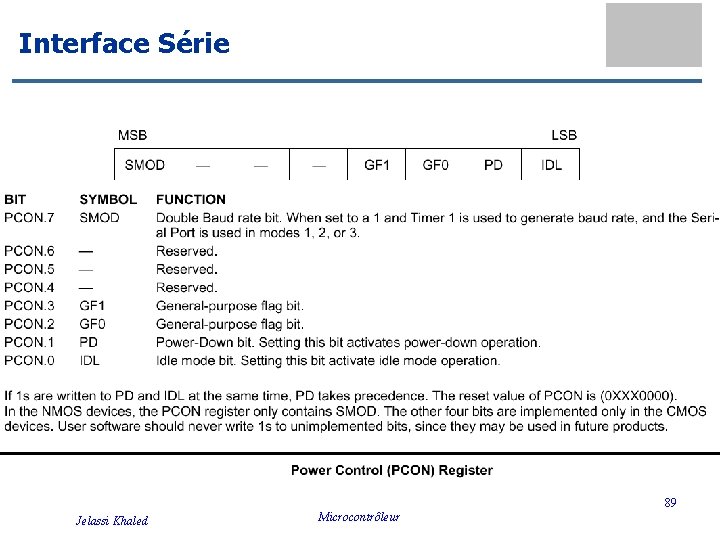

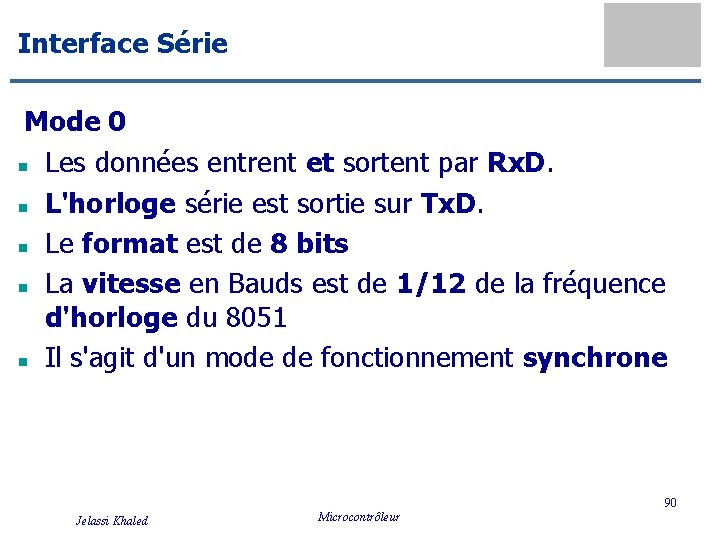

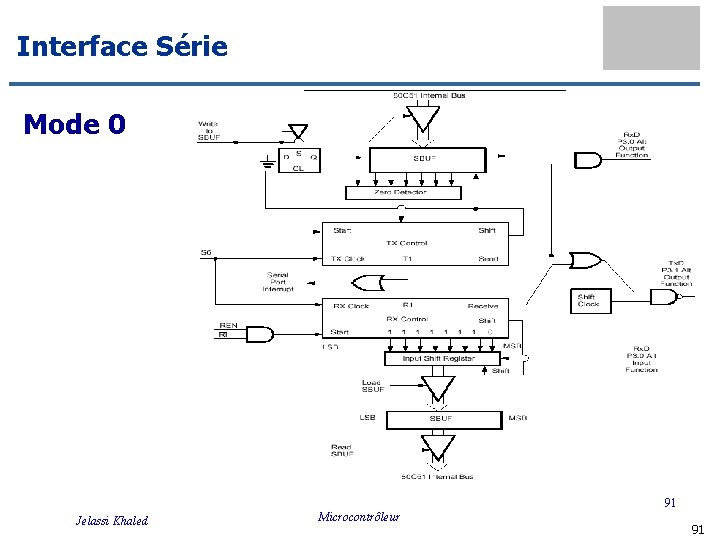

Interface Série Mode 0 n Les données entrent et sortent par Rx. D. n L'horloge série est sortie sur Tx. D. n Le format est de 8 bits n La vitesse en Bauds est de 1/12 de la fréquence d'horloge du 8051 n Il s'agit d'un mode de fonctionnement synchrone 90 Jelassi Khaled Microcontrôleur

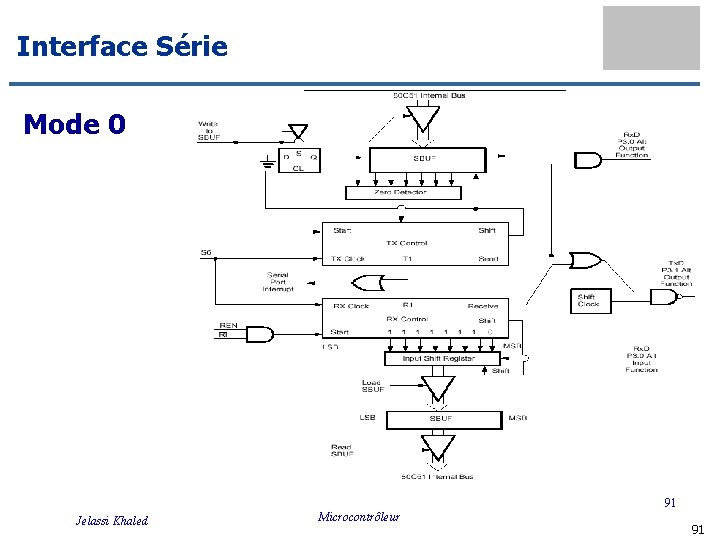

Interface Série Mode 0 91 Jelassi Khaled Microcontrôleur 91

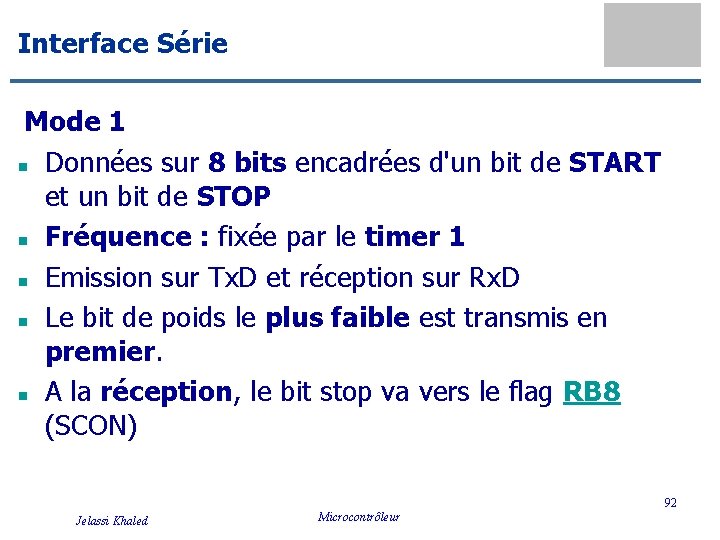

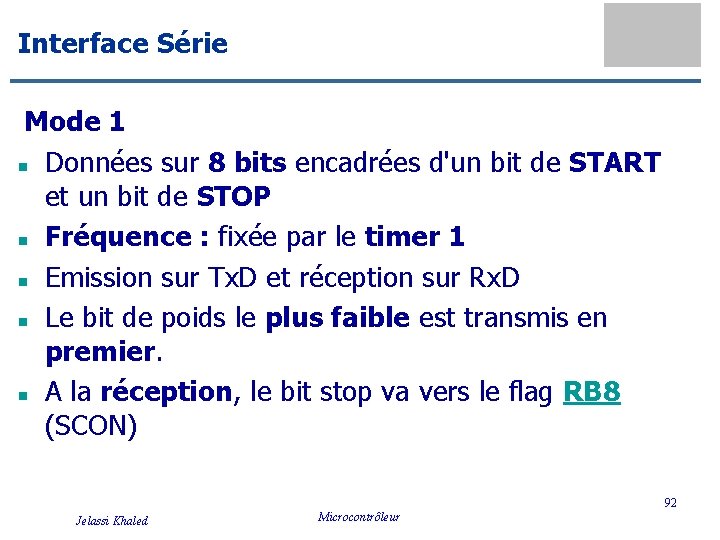

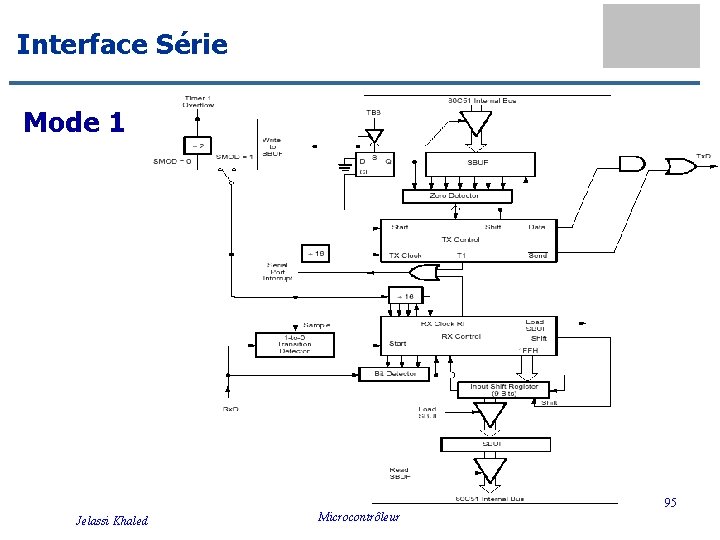

Interface Série Mode 1 n Données sur 8 bits encadrées d'un bit de START et un bit de STOP n Fréquence : fixée par le timer 1 n Emission sur Tx. D et réception sur Rx. D n Le bit de poids le plus faible est transmis en premier. n A la réception, le bit stop va vers le flag RB 8 (SCON) 92 Jelassi Khaled Microcontrôleur

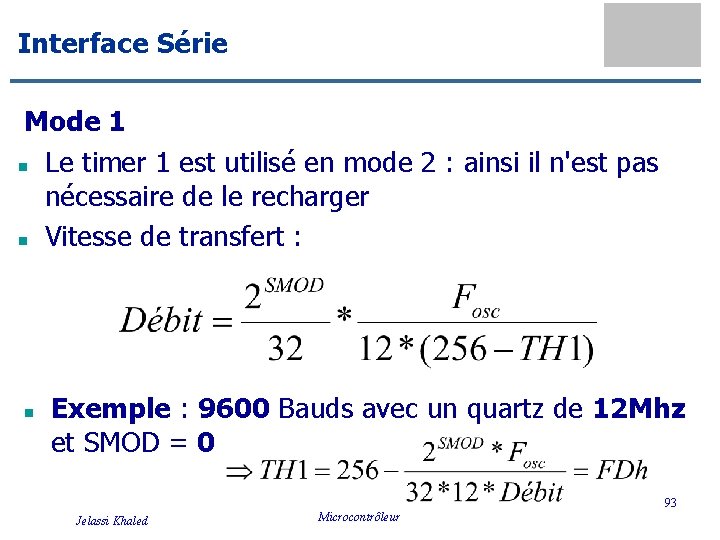

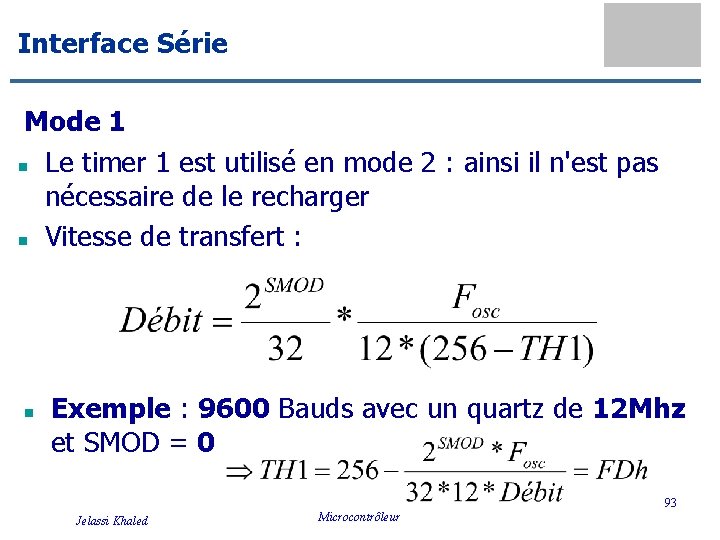

Interface Série Mode 1 n Le timer 1 est utilisé en mode 2 : ainsi il n'est pas nécessaire de le recharger n Vitesse de transfert : n Exemple : 9600 Bauds avec un quartz de 12 Mhz et SMOD = 0 93 Jelassi Khaled Microcontrôleur

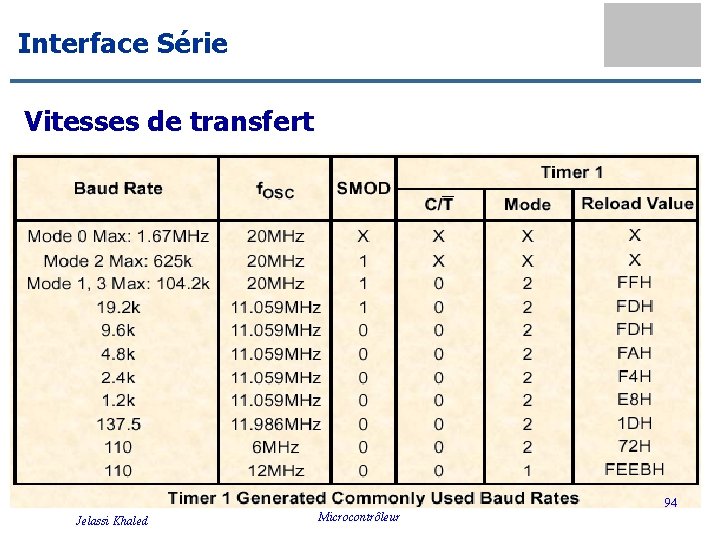

Interface Série Vitesses de transfert 94 Jelassi Khaled Microcontrôleur

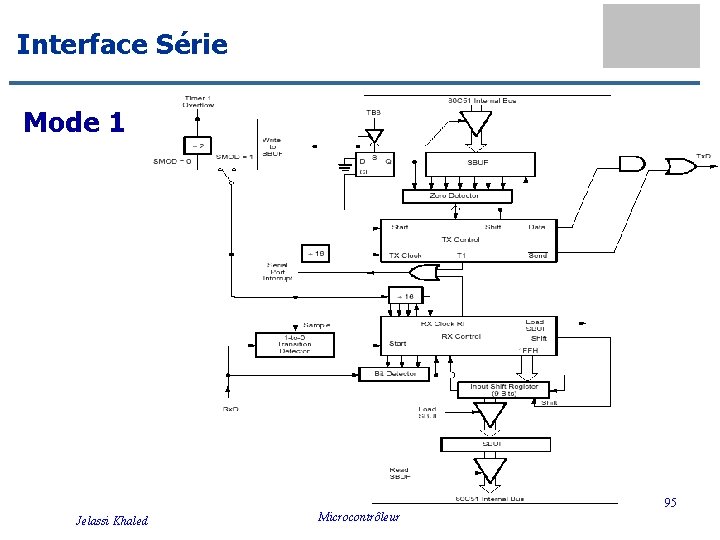

Interface Série Mode 1 95 Jelassi Khaled Microcontrôleur

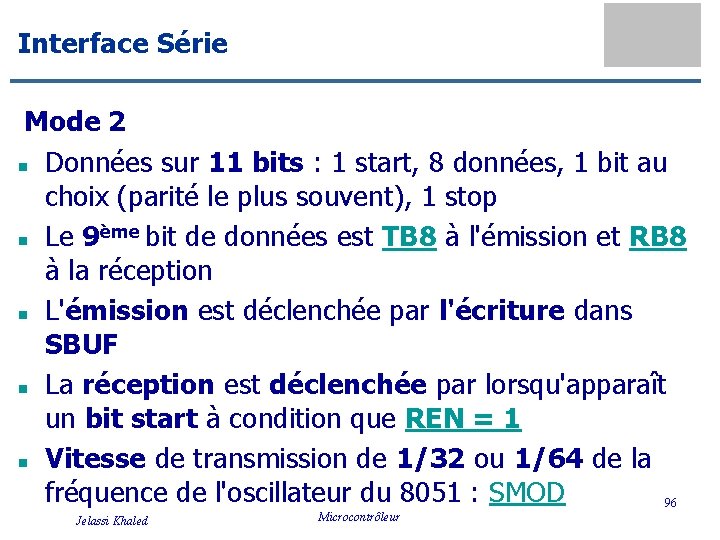

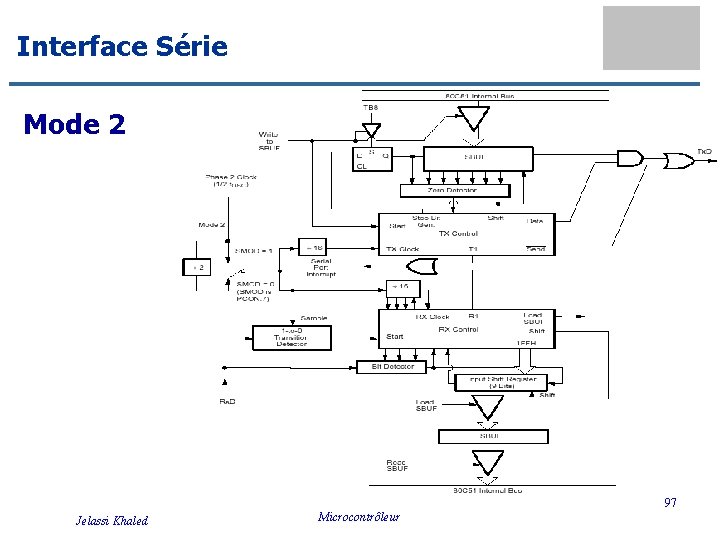

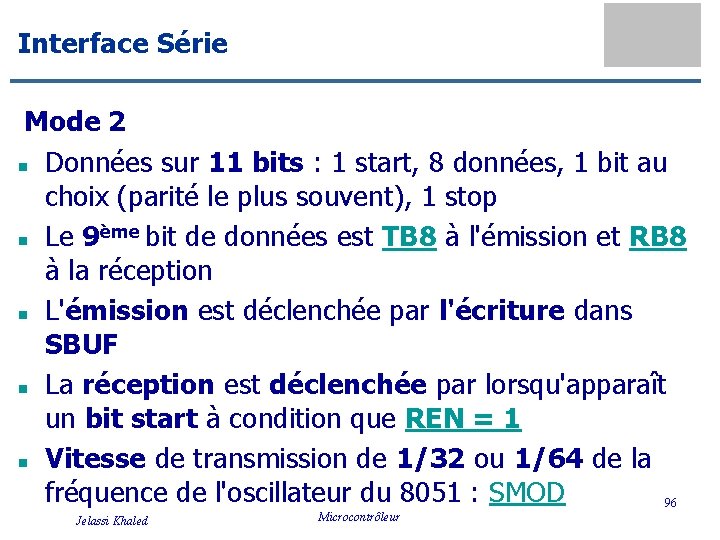

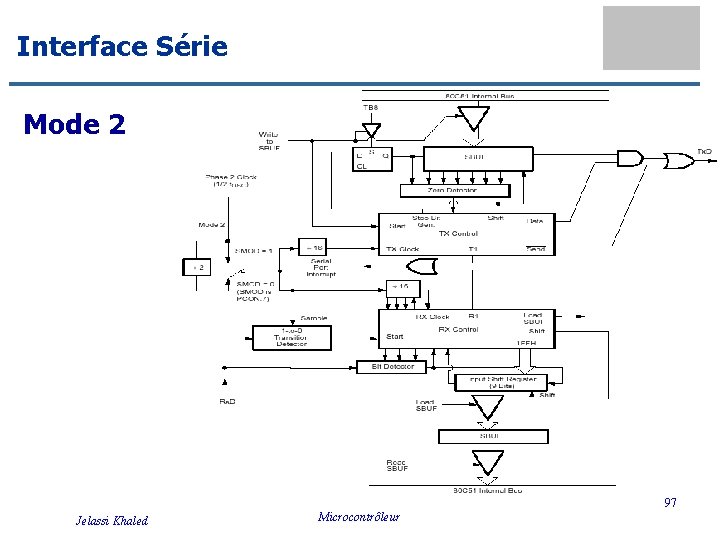

Interface Série Mode 2 n Données sur 11 bits : 1 start, 8 données, 1 bit au choix (parité le plus souvent), 1 stop ème bit de données est TB 8 à l'émission et RB 8 n Le 9 à la réception n L'émission est déclenchée par l'écriture dans SBUF n La réception est déclenchée par lorsqu'apparaît un bit start à condition que REN = 1 n Vitesse de transmission de 1/32 ou 1/64 de la fréquence de l'oscillateur du 8051 : SMOD 96 Jelassi Khaled Microcontrôleur

Interface Série Mode 2 97 Jelassi Khaled Microcontrôleur

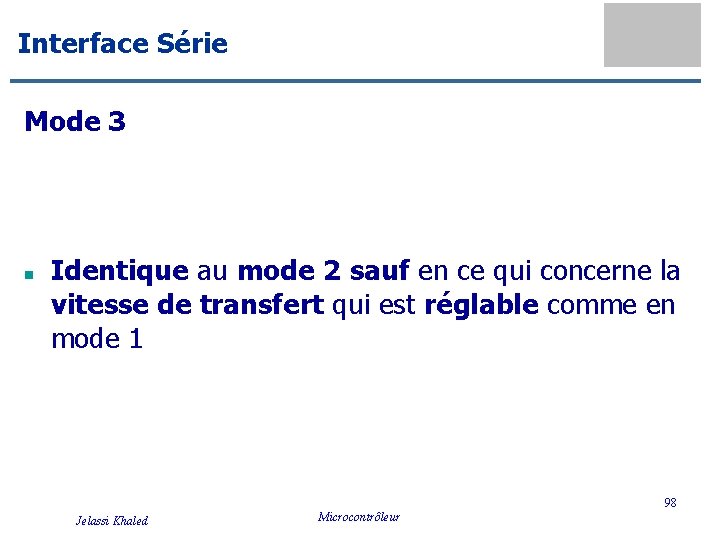

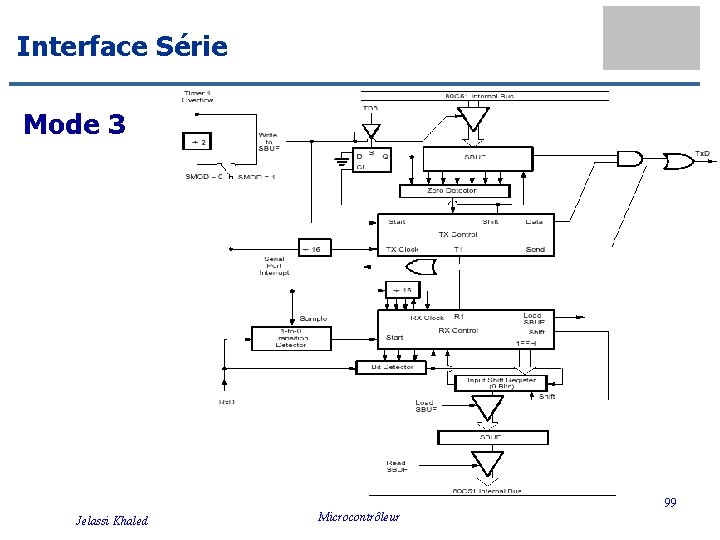

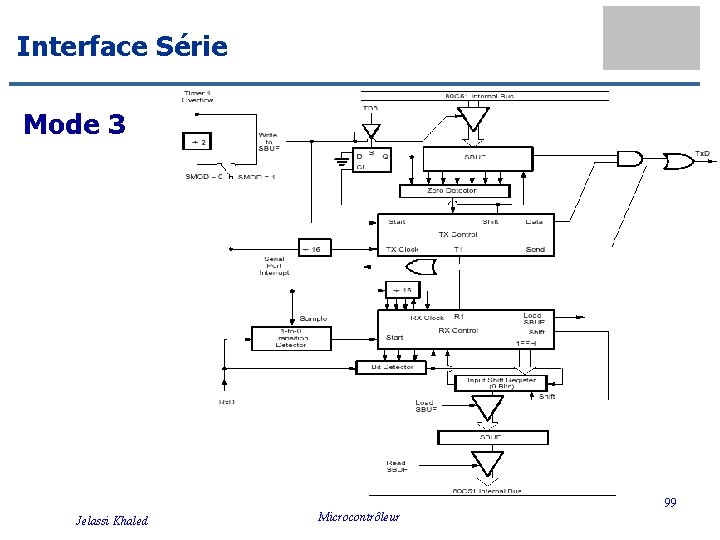

Interface Série Mode 3 n Identique au mode 2 sauf en ce qui concerne la vitesse de transfert qui est réglable comme en mode 1 98 Jelassi Khaled Microcontrôleur

Interface Série Mode 3 99 Jelassi Khaled Microcontrôleur

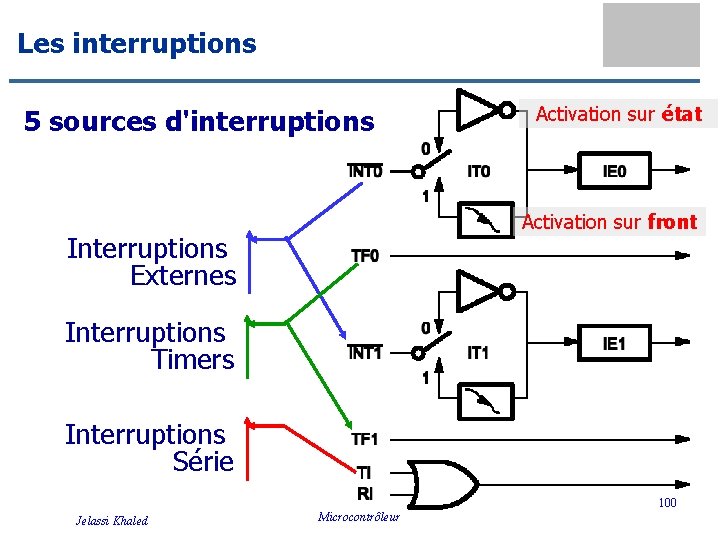

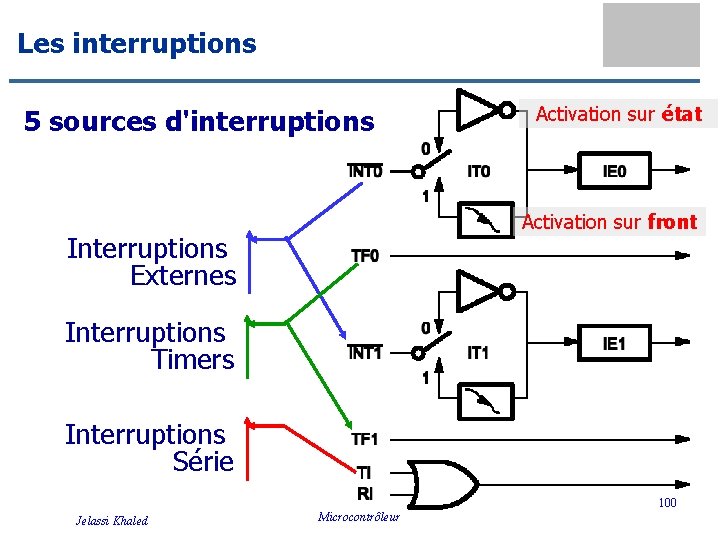

Les interruptions 5 sources d'interruptions Activation sur état Activation sur front Interruptions Externes Interruptions Timers Interruptions Série 100 Jelassi Khaled Microcontrôleur

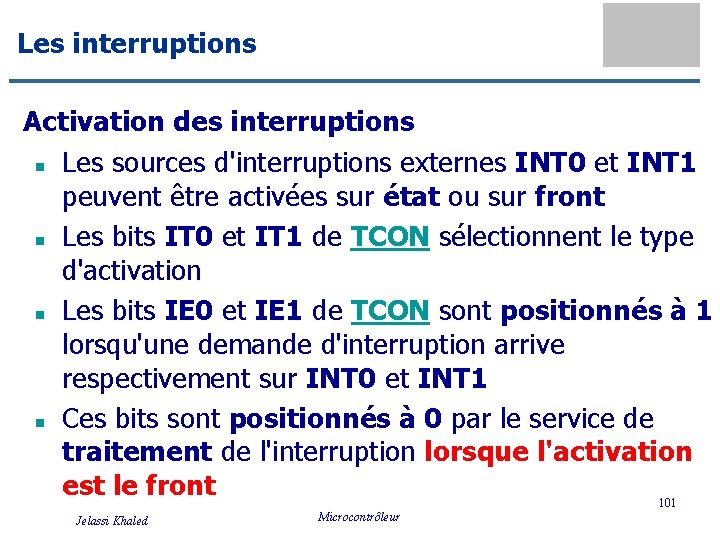

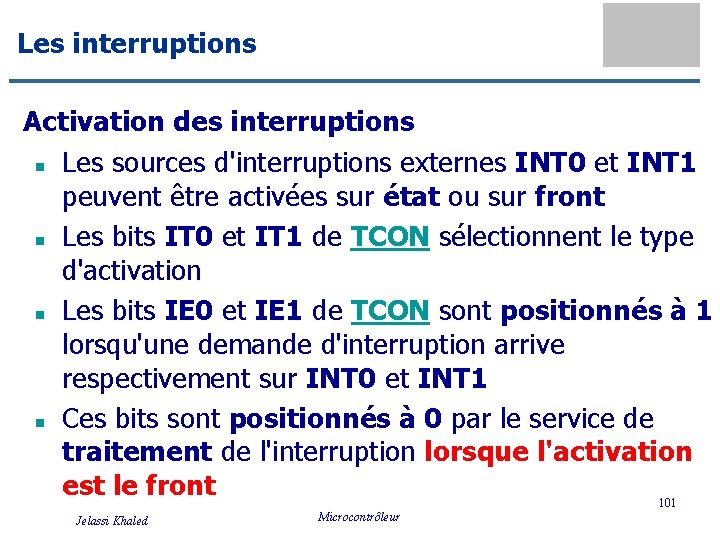

Les interruptions Activation des interruptions n Les sources d'interruptions externes INT 0 et INT 1 peuvent être activées sur état ou sur front n Les bits IT 0 et IT 1 de TCON sélectionnent le type d'activation n Les bits IE 0 et IE 1 de TCON sont positionnés à 1 lorsqu'une demande d'interruption arrive respectivement sur INT 0 et INT 1 n Ces bits sont positionnés à 0 par le service de traitement de l'interruption lorsque l'activation est le front 101 Jelassi Khaled Microcontrôleur

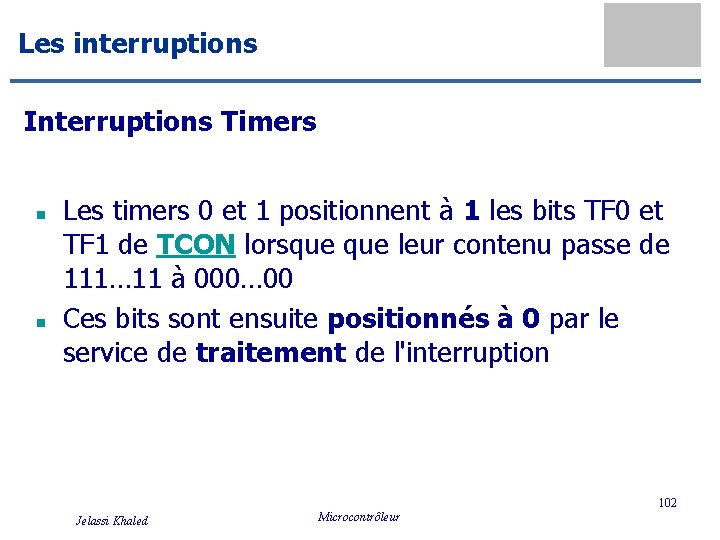

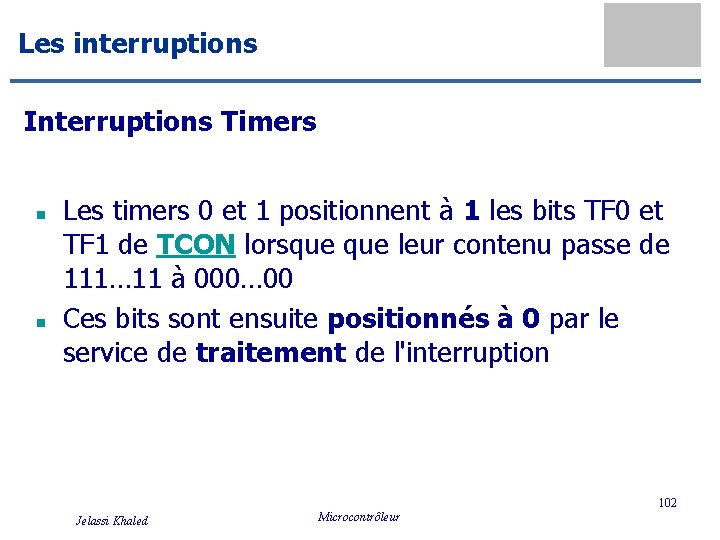

Les interruptions Interruptions Timers n n Les timers 0 et 1 positionnent à 1 les bits TF 0 et TF 1 de TCON lorsque leur contenu passe de 111… 11 à 000… 00 Ces bits sont ensuite positionnés à 0 par le service de traitement de l'interruption 102 Jelassi Khaled Microcontrôleur

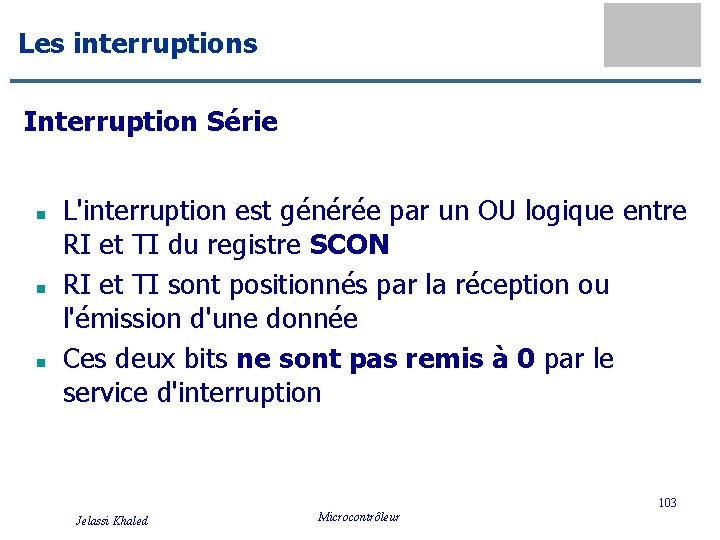

Les interruptions Interruption Série n n n L'interruption est générée par un OU logique entre RI et TI du registre SCON RI et TI sont positionnés par la réception ou l'émission d'une donnée Ces deux bits ne sont pas remis à 0 par le service d'interruption 103 Jelassi Khaled Microcontrôleur

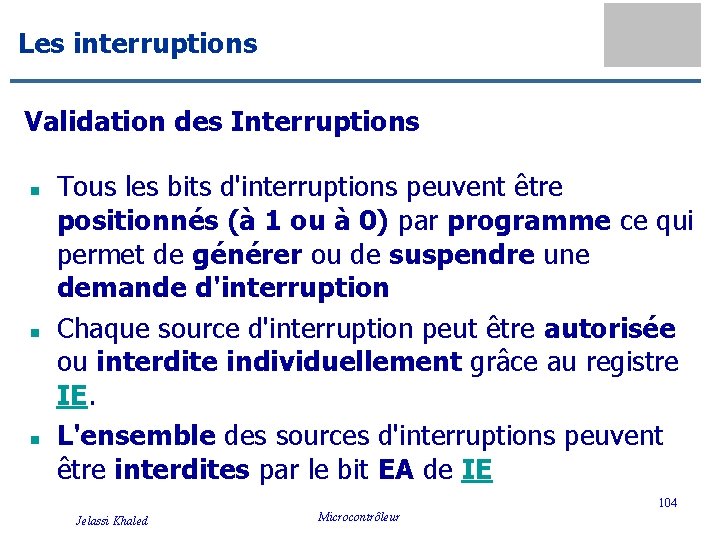

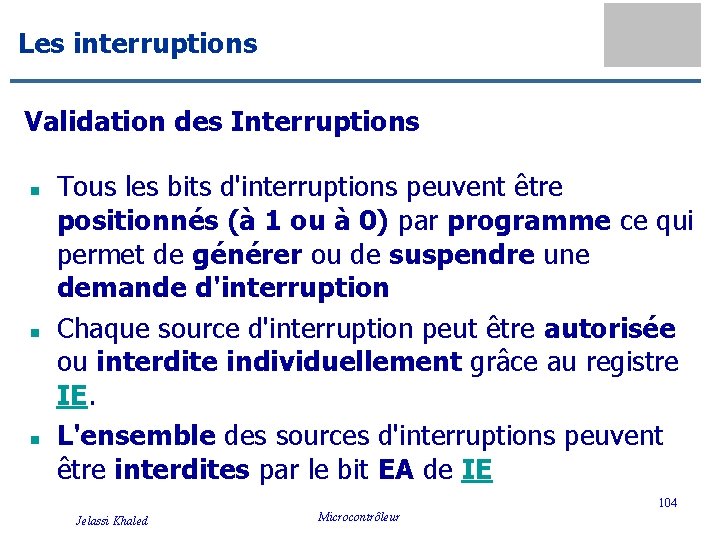

Les interruptions Validation des Interruptions n n n Tous les bits d'interruptions peuvent être positionnés (à 1 ou à 0) par programme ce qui permet de générer ou de suspendre une demande d'interruption Chaque source d'interruption peut être autorisée ou interdite individuellement grâce au registre IE. L'ensemble des sources d'interruptions peuvent être interdites par le bit EA de IE 104 Jelassi Khaled Microcontrôleur

Les interruptions Validation des Interruptions 105 Jelassi Khaled Microcontrôleur

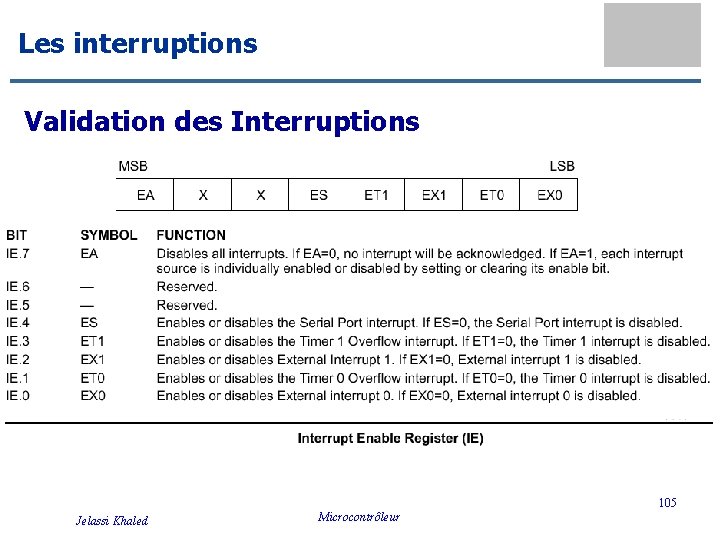

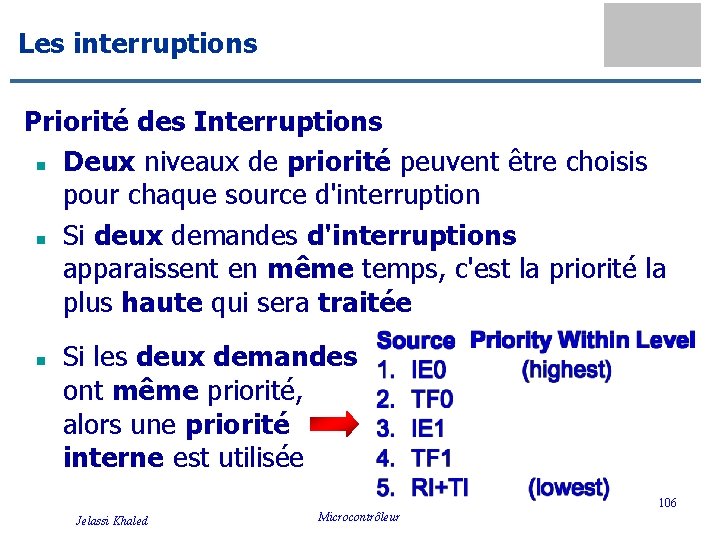

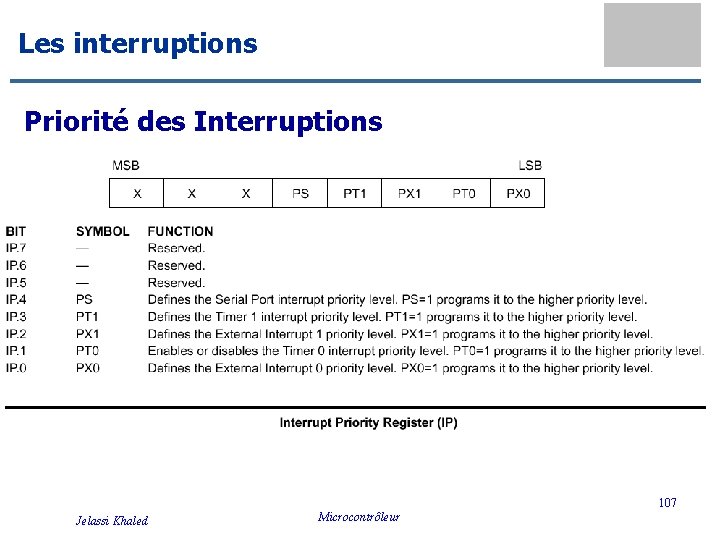

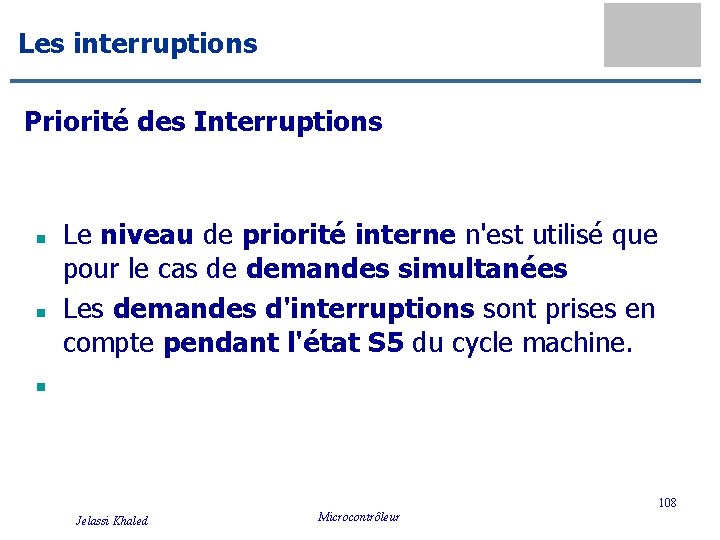

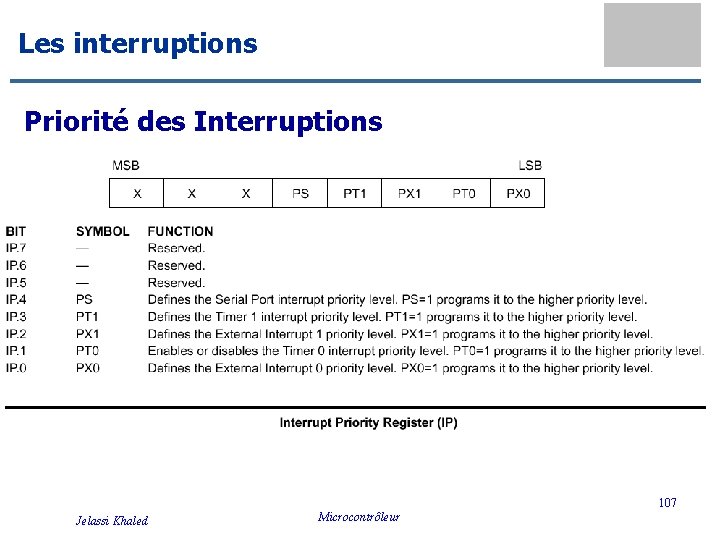

Les interruptions Priorité des Interruptions n Deux niveaux de priorité peuvent être choisis pour chaque source d'interruption n Si deux demandes d'interruptions apparaissent en même temps, c'est la priorité la plus haute qui sera traitée n Si les deux demandes ont même priorité, alors une priorité interne est utilisée 106 Jelassi Khaled Microcontrôleur

Les interruptions Priorité des Interruptions 107 Jelassi Khaled Microcontrôleur

Les interruptions Priorité des Interruptions n n n Le niveau de priorité interne n'est utilisé que pour le cas de demandes simultanées Les demandes d'interruptions sont prises en compte pendant l'état S 5 du cycle machine. 108 Jelassi Khaled Microcontrôleur

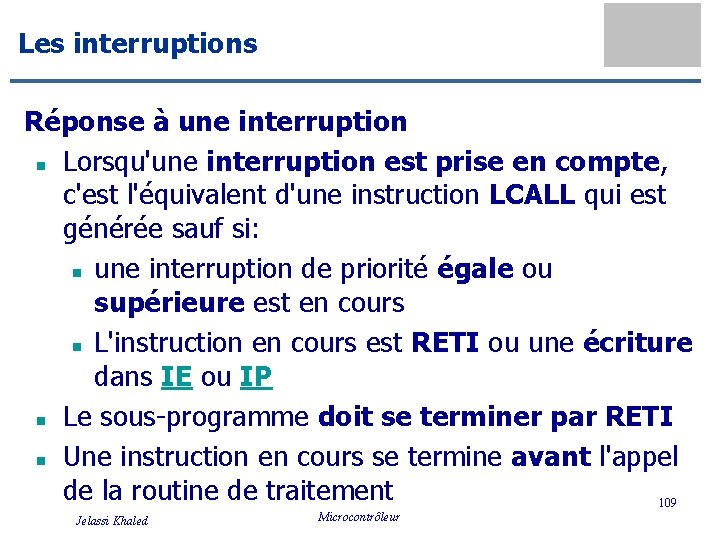

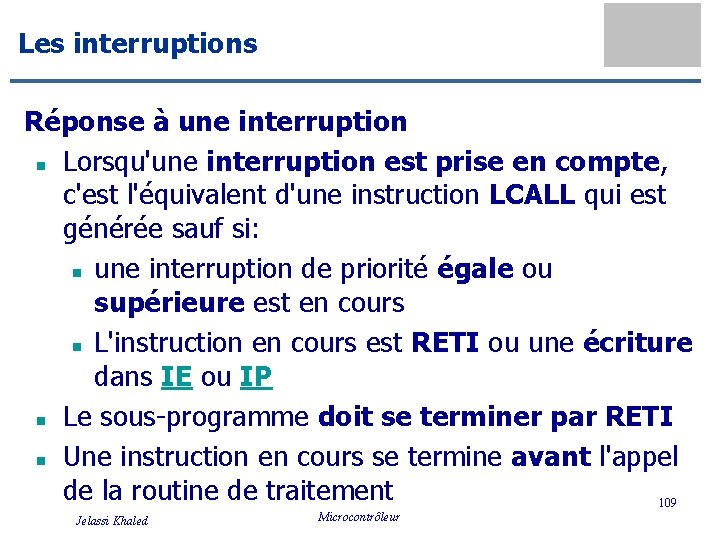

Les interruptions Réponse à une interruption n Lorsqu'une interruption est prise en compte, c'est l'équivalent d'une instruction LCALL qui est générée sauf si: n une interruption de priorité égale ou supérieure est en cours n L'instruction en cours est RETI ou une écriture dans IE ou IP n Le sous-programme doit se terminer par RETI n Une instruction en cours se termine avant l'appel de la routine de traitement 109 Jelassi Khaled Microcontrôleur

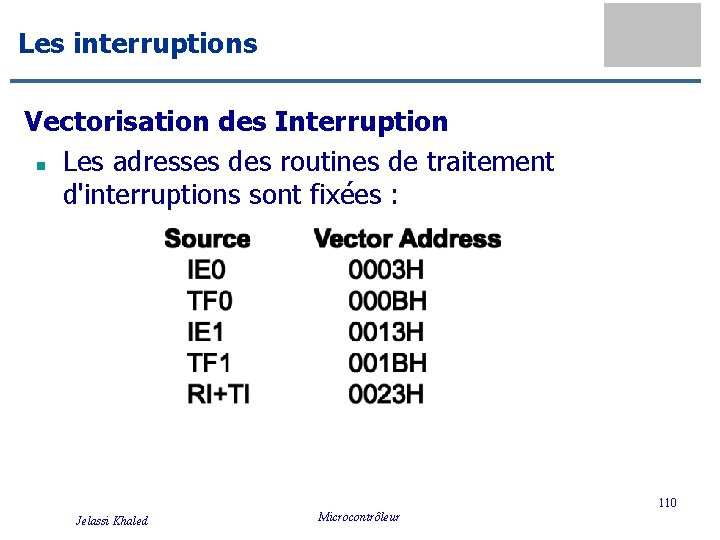

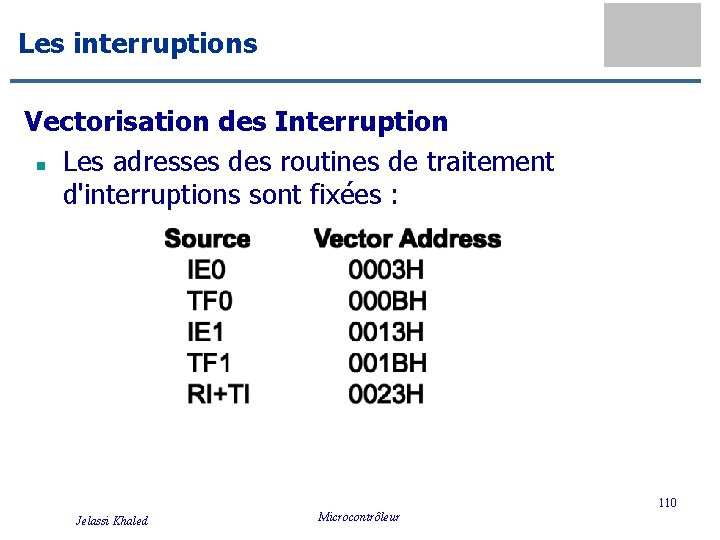

Les interruptions Vectorisation des Interruption n Les adresses des routines de traitement d'interruptions sont fixées : 110 Jelassi Khaled Microcontrôleur

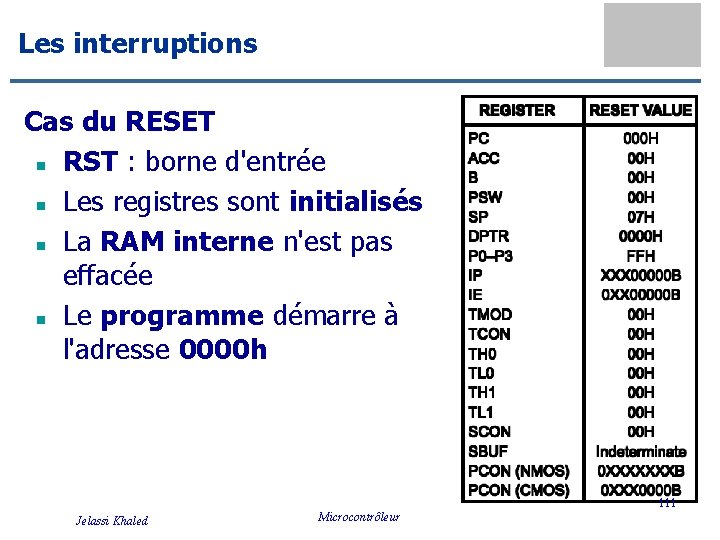

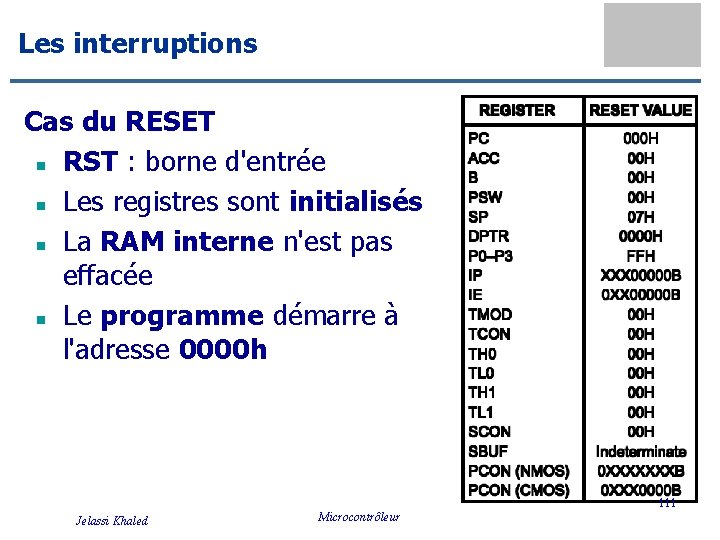

Les interruptions Cas du RESET n RST : borne d'entrée n Les registres sont initialisés n La RAM interne n'est pas effacée n Le programme démarre à l'adresse 0000 h 111 Jelassi Khaled Microcontrôleur

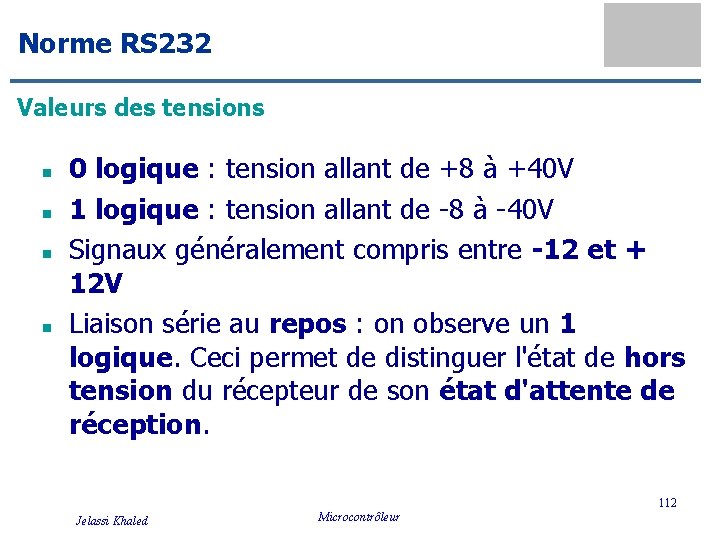

Norme RS 232 Valeurs des tensions n n 0 logique : tension allant de +8 à +40 V 1 logique : tension allant de -8 à -40 V Signaux généralement compris entre -12 et + 12 V Liaison série au repos : on observe un 1 logique. Ceci permet de distinguer l'état de hors tension du récepteur de son état d'attente de réception. 112 Jelassi Khaled Microcontrôleur

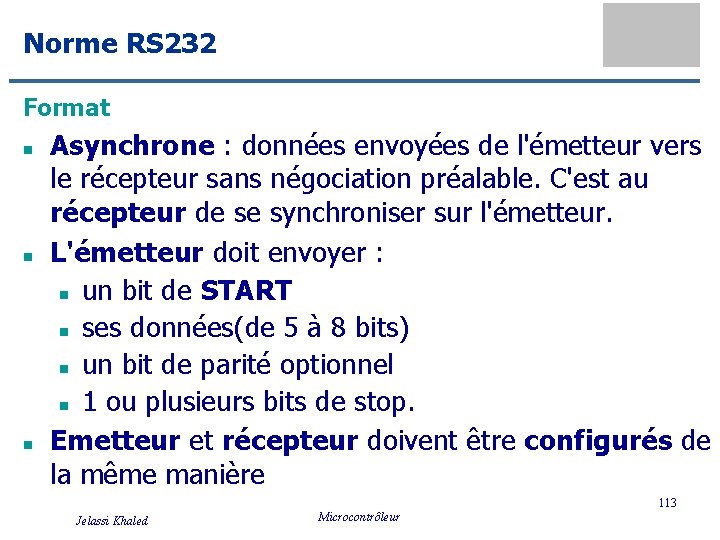

Norme RS 232 Format n n n Asynchrone : données envoyées de l'émetteur vers le récepteur sans négociation préalable. C'est au récepteur de se synchroniser sur l'émetteur. L'émetteur doit envoyer : n un bit de START n ses données(de 5 à 8 bits) n un bit de parité optionnel n 1 ou plusieurs bits de stop. Emetteur et récepteur doivent être configurés de la même manière 113 Jelassi Khaled Microcontrôleur

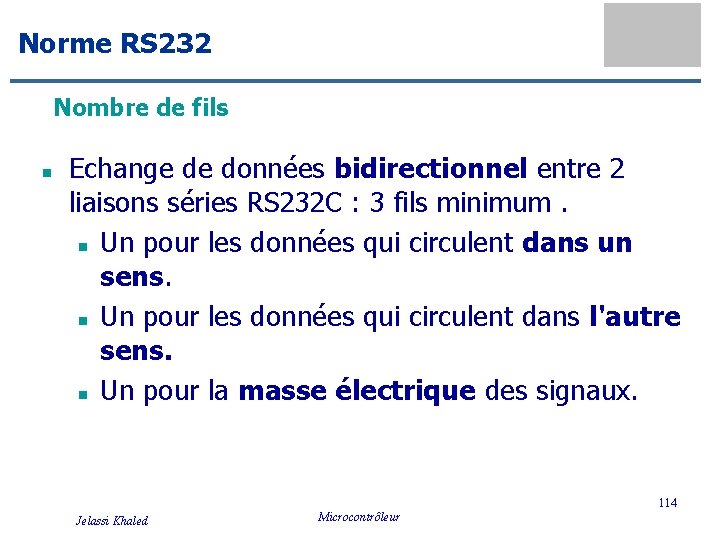

Norme RS 232 Nombre de fils n Echange de données bidirectionnel entre 2 liaisons séries RS 232 C : 3 fils minimum. n Un pour les données qui circulent dans un sens. n Un pour les données qui circulent dans l'autre sens. n Un pour la masse électrique des signaux. 114 Jelassi Khaled Microcontrôleur

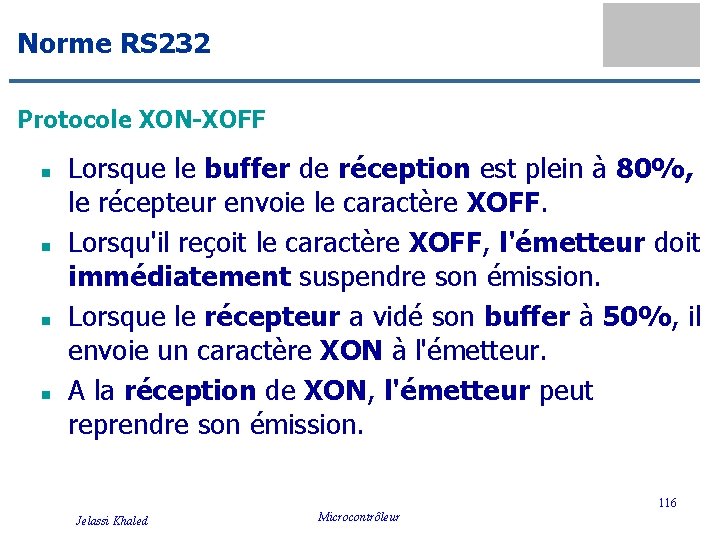

Norme RS 232 Protocoles de communication n Protocole XON XOFF : ne nécessite qu'une liaison sur 3 fils. La négociation entre l'émetteur et le récepteur pour échanger des données se fait par logiciel. Basé sur les caractères XON (ASCI 11 H) et XOFF (ASCI 13 H). 115 Jelassi Khaled Microcontrôleur

Norme RS 232 Protocole XON-XOFF n n Lorsque le buffer de réception est plein à 80%, le récepteur envoie le caractère XOFF. Lorsqu'il reçoit le caractère XOFF, l'émetteur doit immédiatement suspendre son émission. Lorsque le récepteur a vidé son buffer à 50%, il envoie un caractère XON à l'émetteur. A la réception de XON, l'émetteur peut reprendre son émission. 116 Jelassi Khaled Microcontrôleur

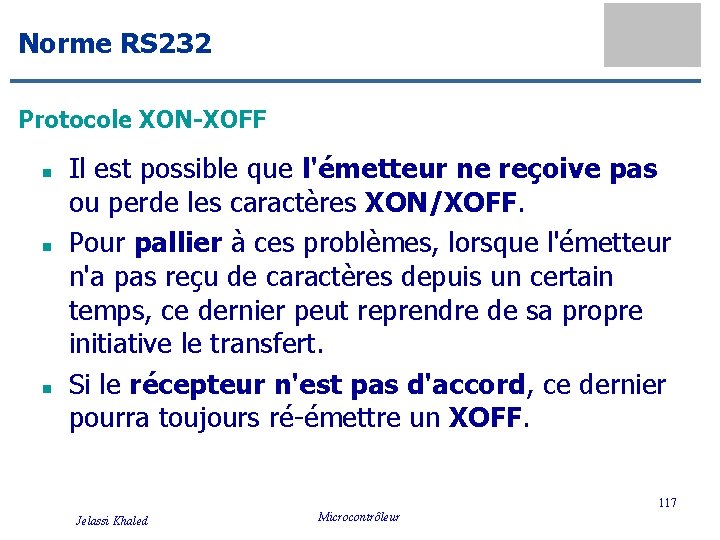

Norme RS 232 Protocole XON-XOFF n n n Il est possible que l'émetteur ne reçoive pas ou perde les caractères XON/XOFF. Pour pallier à ces problèmes, lorsque l'émetteur n'a pas reçu de caractères depuis un certain temps, ce dernier peut reprendre de sa propre initiative le transfert. Si le récepteur n'est pas d'accord, ce dernier pourra toujours ré-émettre un XOFF. 117 Jelassi Khaled Microcontrôleur

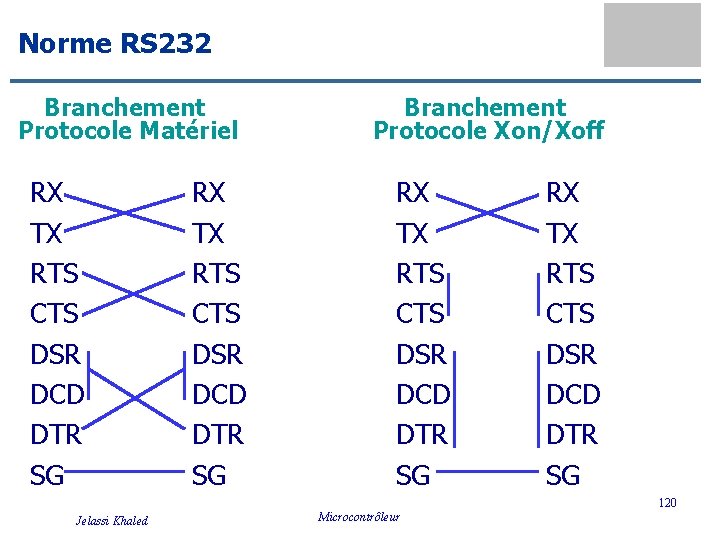

Norme RS 232 Protocole Matériel n n Lorsque l'émetteur veut émettre ses données, il doit positionner la ligne RTS pour demander au récepteur s'il est prêt à accepter ces données. Le récepteur, lorsqu'il est prêt à recevoir les données, va envoyer le signal DSR de l'émetteur pour lui indiquer qu'il est prêt. 118 Jelassi Khaled Microcontrôleur

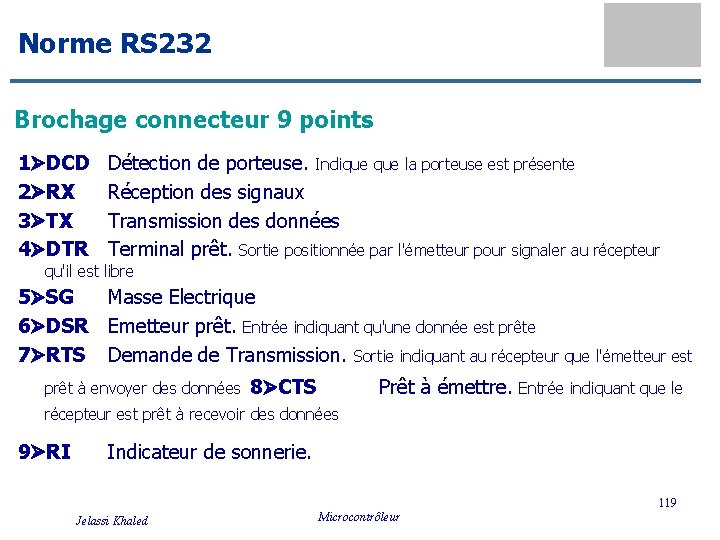

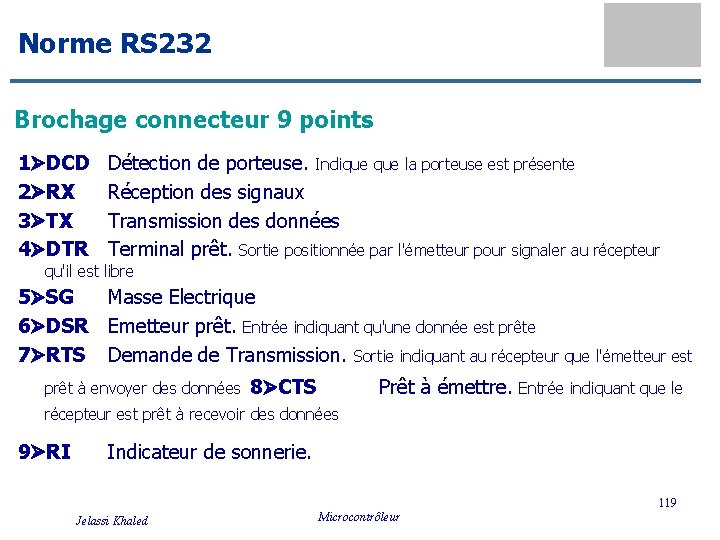

Norme RS 232 Brochage connecteur 9 points 1 DCD 2 RX 3 TX 4 DTR Détection de porteuse. Indique la porteuse est présente Réception des signaux Transmission des données Terminal prêt. Sortie positionnée par l'émetteur pour signaler au récepteur qu'il est libre 5 SG Masse Electrique 6 DSR Emetteur prêt. Entrée indiquant qu'une donnée est prête 7 RTS Demande de Transmission. Sortie indiquant au récepteur que l'émetteur est prêt à envoyer des données 8 CTS Prêt à émettre. Entrée indiquant que le récepteur est prêt à recevoir des données 9 RI Indicateur de sonnerie. 119 Jelassi Khaled Microcontrôleur

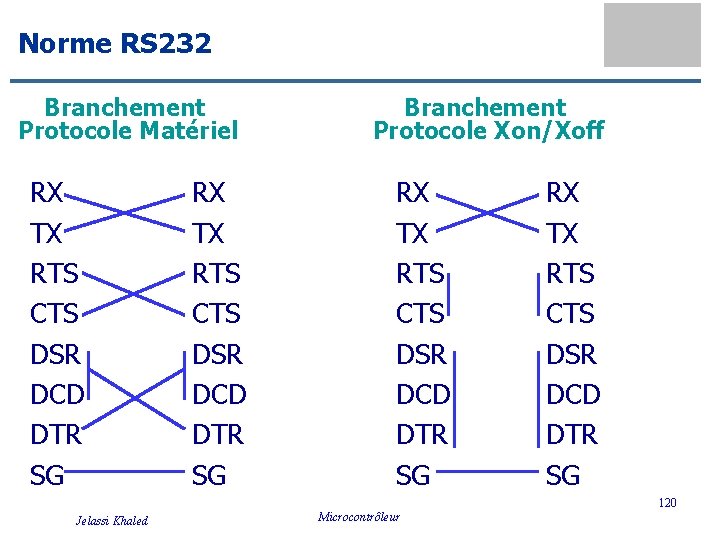

Norme RS 232 Branchement Protocole Matériel RX TX RTS CTS DSR DCD DTR SG Branchement Protocole Xon/Xoff RX TX RTS CTS DSR DCD DTR SG 120 Jelassi Khaled Microcontrôleur

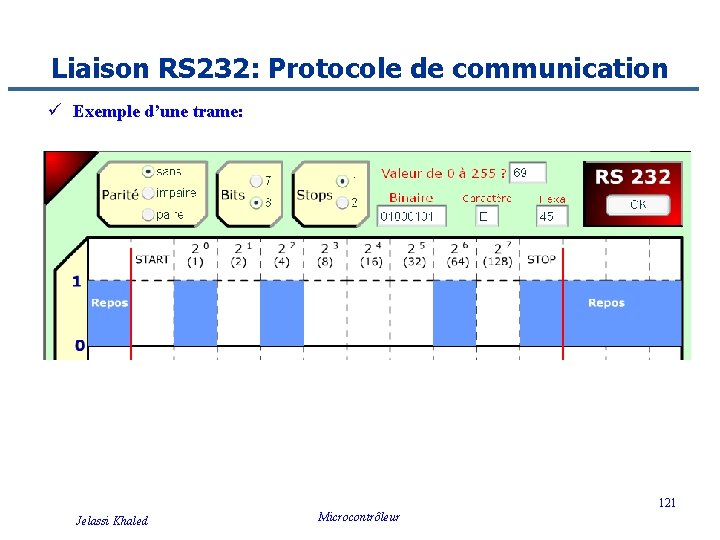

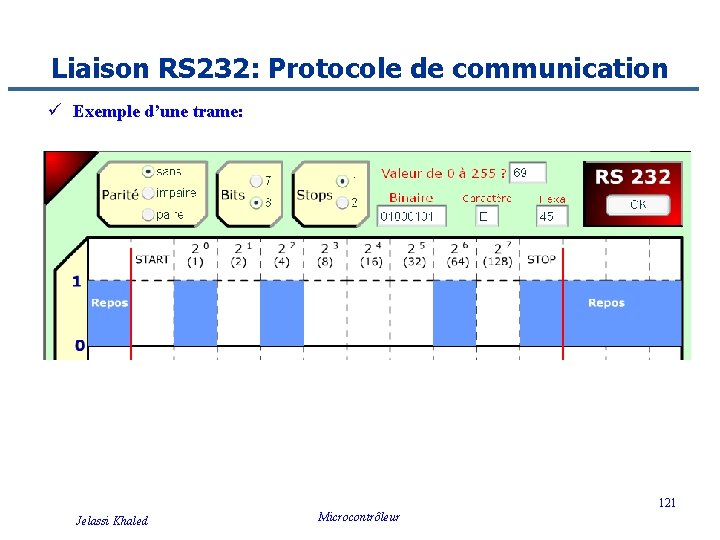

Liaison RS 232: Protocole de communication ü Exemple d’une trame: 121 Jelassi Khaled Microcontrôleur