LDO characterization Laura Gonella Physikalisches Institut Uni Bonn

LDO characterization Laura Gonella Physikalisches Institut Uni Bonn

Status • Tests performed on the LDO mode of the Shunt-LDO regulator – Single device characterization • Line regulation(*) – T dependence • Load transient – Parallel operation: same Vin, different Vout • Line regulation • Load transient (*) These results have already been shown and discussed. They are added here as useful material for the design review 2 4/20/2011

Single device characterization • • • Both regulators on chip have been tested independently Results are in good agreement Shown here results from Reg 2 3 4/20/2011

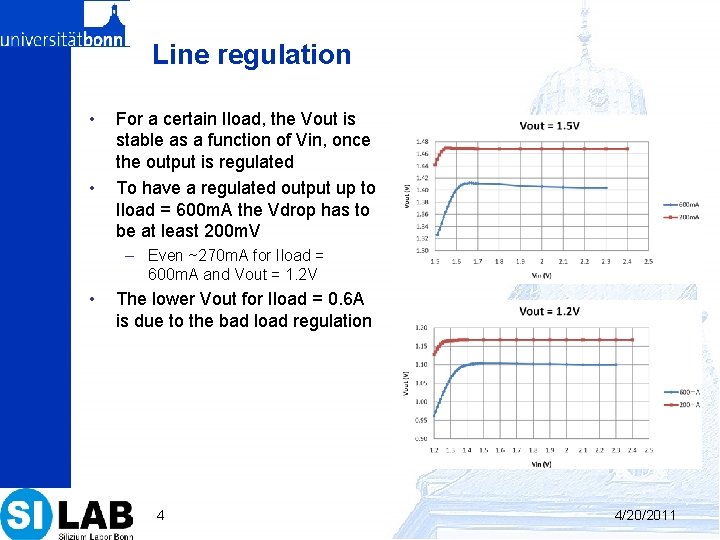

Line regulation • • For a certain Iload, the Vout is stable as a function of Vin, once the output is regulated To have a regulated output up to Iload = 600 m. A the Vdrop has to be at least 200 m. V – Even ~270 m. A for Iload = 600 m. A and Vout = 1. 2 V • The lower Vout for Iload = 0. 6 A is due to the bad load regulation 4 4/20/2011

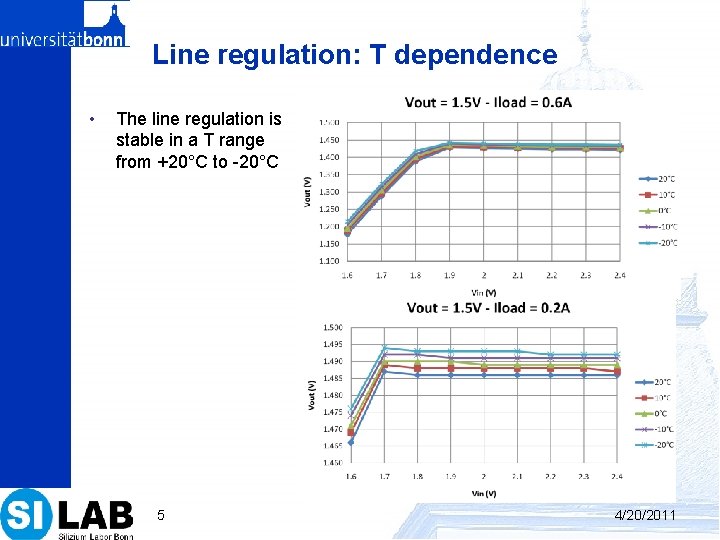

Line regulation: T dependence • The line regulation is stable in a T range from +20°C to -20°C 5 4/20/2011

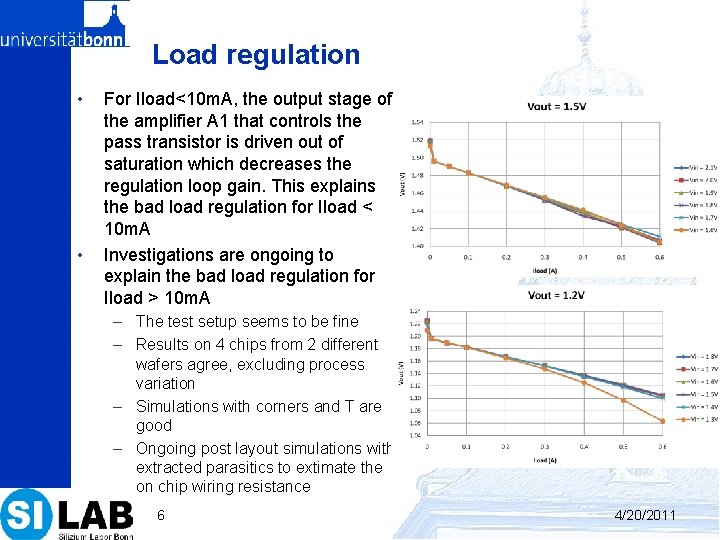

Load regulation • • For Iload<10 m. A, the output stage of the amplifier A 1 that controls the pass transistor is driven out of saturation which decreases the regulation loop gain. This explains the bad load regulation for Iload < 10 m. A Investigations are ongoing to explain the bad load regulation for Iload > 10 m. A – The test setup seems to be fine – Results on 4 chips from 2 different wafers agree, excluding process variation – Simulations with corners and T are good – Ongoing post layout simulations with extracted parasitics to extimate the on chip wiring resistance 6 4/20/2011

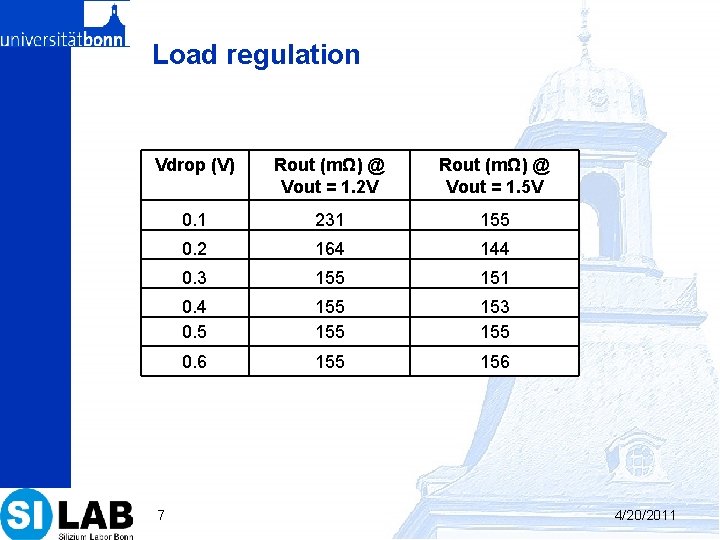

Load regulation Vdrop (V) Rout (mΩ) @ Vout = 1. 2 V Rout (mΩ) @ Vout = 1. 5 V 0. 1 231 155 0. 2 164 144 0. 3 155 151 0. 4 0. 5 155 153 155 0. 6 155 156 7 4/20/2011

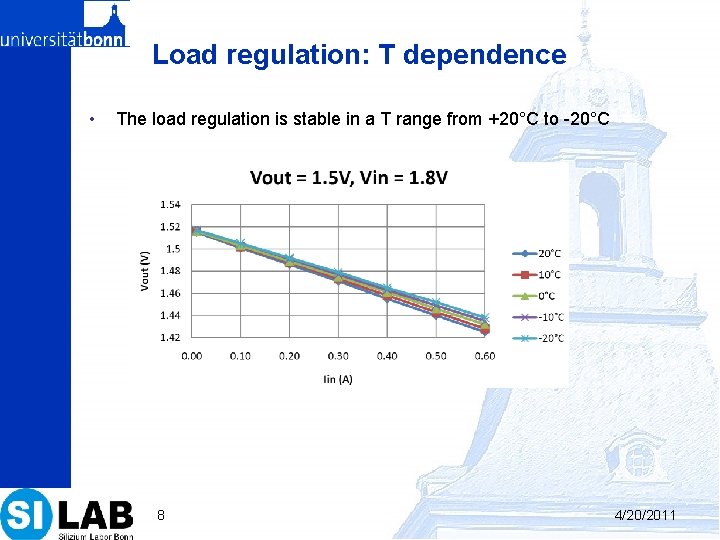

Load regulation: T dependence • The load regulation is stable in a T range from +20°C to -20°C 8 4/20/2011

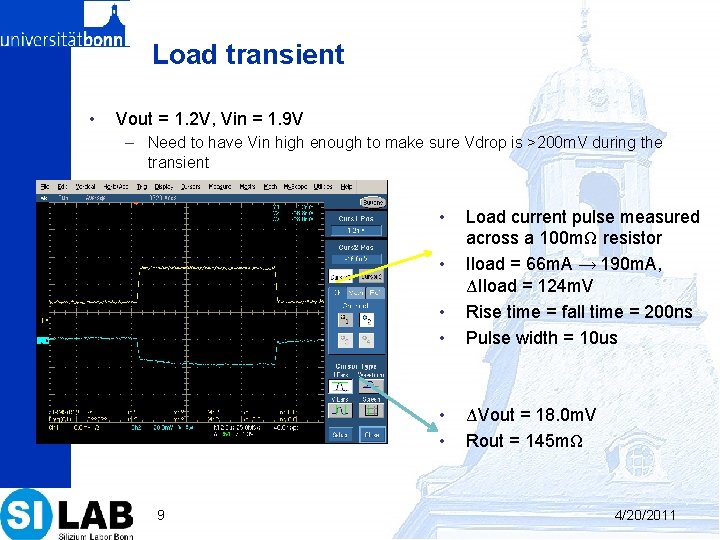

Load transient • Vout = 1. 2 V, Vin = 1. 9 V – Need to have Vin high enough to make sure Vdrop is >200 m. V during the transient • • • Load current pulse measured across a 100 mΩ resistor Iload = 66 m. A → 190 m. A, ΔIload = 124 m. V Rise time = fall time = 200 ns Pulse width = 10 us • • ΔVout = 18. 0 m. V Rout = 145 mΩ • 9 4/20/2011

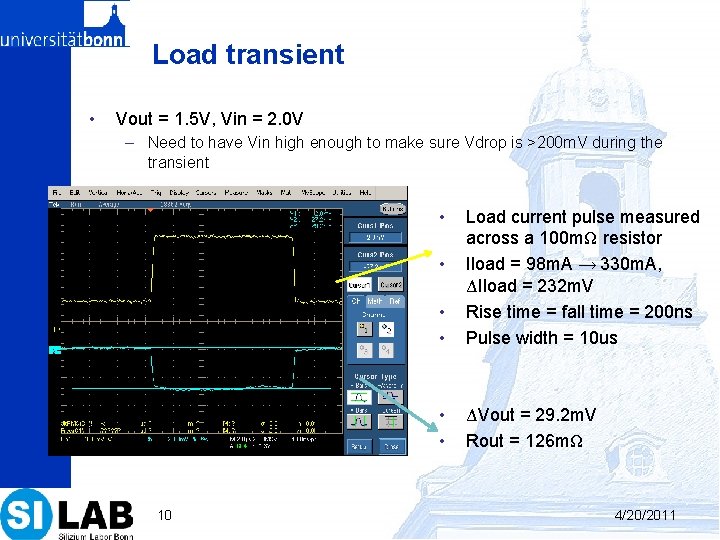

Load transient • Vout = 1. 5 V, Vin = 2. 0 V – Need to have Vin high enough to make sure Vdrop is >200 m. V during the transient • • • Load current pulse measured across a 100 mΩ resistor Iload = 98 m. A → 330 m. A, ΔIload = 232 m. V Rise time = fall time = 200 ns Pulse width = 10 us • • ΔVout = 29. 2 m. V Rout = 126 mΩ • 10 4/20/2011

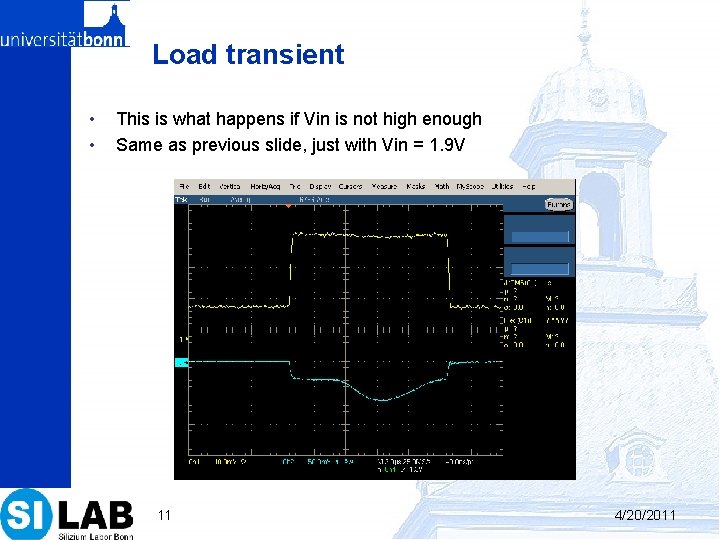

Load transient • • This is what happens if Vin is not high enough Same as previous slide, just with Vin = 1. 9 V 11 4/20/2011

Parallel operation • • • Reg 1 generates Vout = 1. 5 V Reg 2 generates Vout = 1. 2 V The Vin is in common – The Vdrop on the Vin lines (from supply to the chip pad) is slightly different so Vin 1 ≠ Vin 2 – Reg 2 sees a Vdrop ≥ 0. 4 V 12 4/20/2011

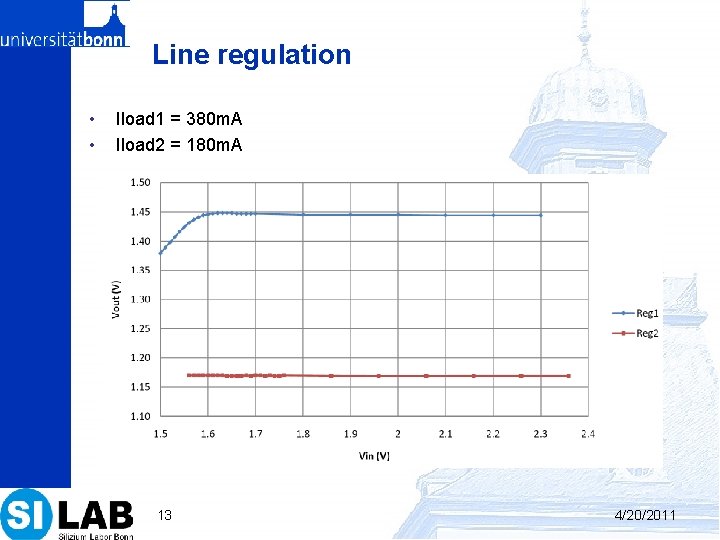

Line regulation • • Iload 1 = 380 m. A Iload 2 = 180 m. A 13 4/20/2011

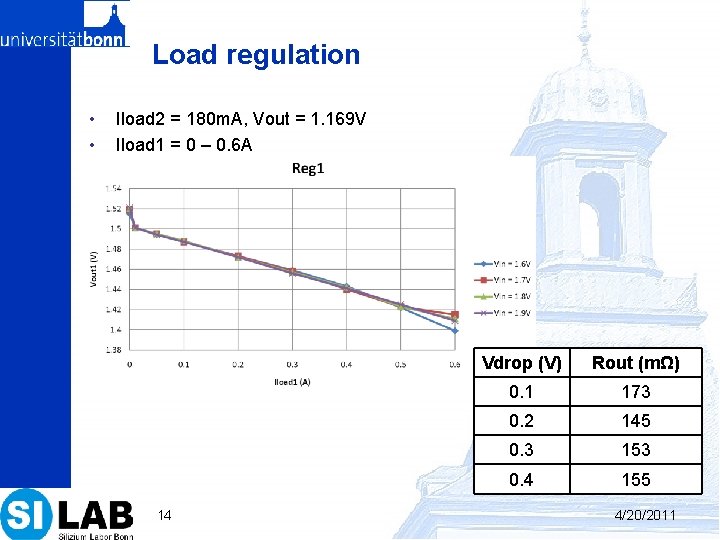

Load regulation • • Iload 2 = 180 m. A, Vout = 1. 169 V Iload 1 = 0 – 0. 6 A 14 Vdrop (V) Rout (mΩ) 0. 1 173 0. 2 145 0. 3 153 0. 4 155 4/20/2011

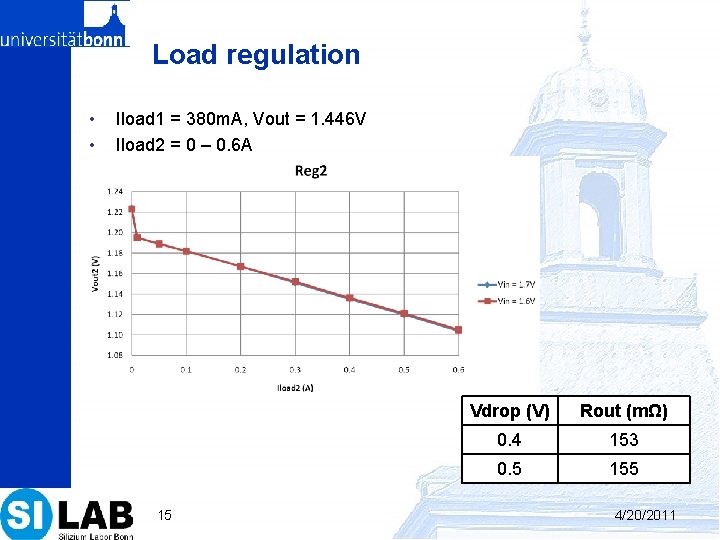

Load regulation • • Iload 1 = 380 m. A, Vout = 1. 446 V Iload 2 = 0 – 0. 6 A 15 Vdrop (V) Rout (mΩ) 0. 4 153 0. 5 155 4/20/2011

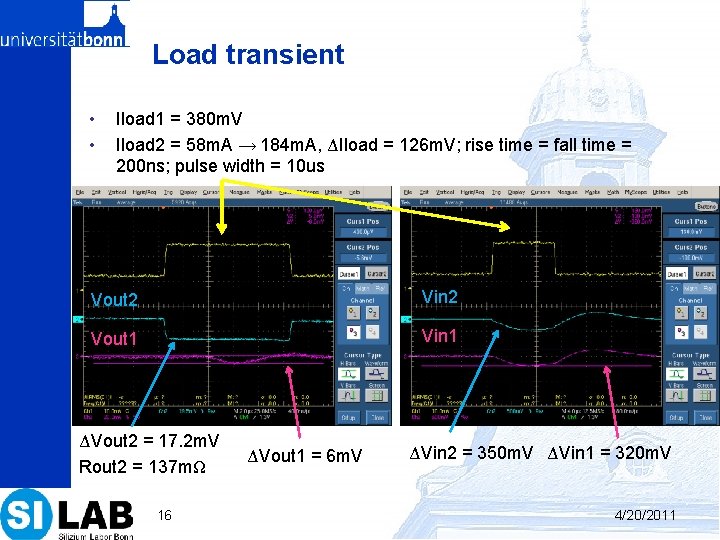

Load transient • • Iload 1 = 380 m. V Iload 2 = 58 m. A → 184 m. A, ΔIload = 126 m. V; rise time = fall time = 200 ns; pulse width = 10 us Vout 2 Vin 2 Vout 1 Vin 1 ΔVout 2 = 17. 2 m. V Rout 2 = 137 mΩ 16 ΔVout 1 = 6 m. V ΔVin 2 = 350 m. V ΔVin 1 = 320 m. V 4/20/2011

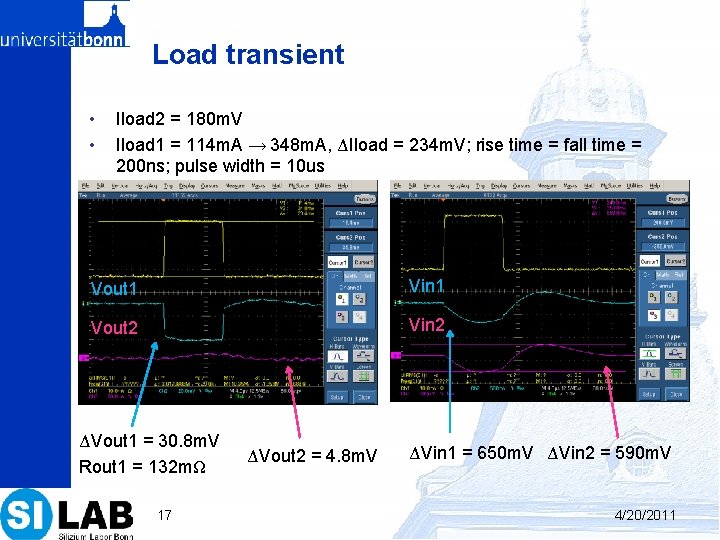

Load transient • • Iload 2 = 180 m. V Iload 1 = 114 m. A → 348 m. A, ΔIload = 234 m. V; rise time = fall time = 200 ns; pulse width = 10 us Vout 1 Vin 1 Vout 2 Vin 2 ΔVout 1 = 30. 8 m. V Rout 1 = 132 mΩ 17 ΔVout 2 = 4. 8 m. V ΔVin 1 = 650 m. V ΔVin 2 = 590 m. V 4/20/2011

- Slides: 17