Layout techniques for increased radiation tolerance in commercial

- Slides: 34

Layout techniques for increased radiation tolerance in commercial CMOS for pixel readout circuits W. Snoeys Microelectronics Group, EP Division, CERN Representing the ALICE pixel, LHCB RICH and RD 49 collaborations CERN EP Seminar October 19, 1998

Other contributors and Acknowledgements u u u u u Michael Campbell Eugenio Cantatore Ken Wyllie Domenico Minervini Roberto Dinapoli Elena Pernigotti Katelijn Vleugels Pierre-Marie Signe Federico Faccio Etam Noah Giovanni Anelli Marco Delmastro I. Ropotar L. Casagrande Bettina Mikulec Milo Luptak Peter Sonderegger Carlos Lourenco u u Erik Heijne Pierre Jarron Alessandro Marchioro Mike Letheren u u Willy Sansen Franco Corsi u u u Michael Burns Michel Morel Paolo Martinengo Stefania Saladino Fabio Formenti u Franco Meddi et al. u u Wolfgang Klempt Federico Antinori

OVERVIEW u u u Problem with total dose in standard CMOS technologies Principle and effectiveness of layout techniques Design description and electrical results on pixel prototypes Irradiation results on pixel prototype Design implications Conclusions and perspectives

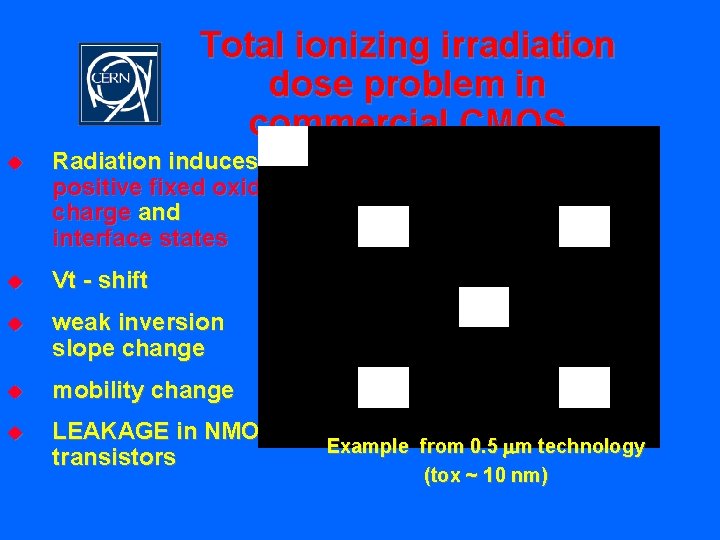

Total ionizing irradiation dose problem in commercial CMOS u Radiation induces positive fixed oxide charge and interface states u Vt - shift u weak inversion slope change u mobility change u LEAKAGE in NMOS transistors Example from 0. 5 mm technology (tox ~ 10 nm)

NMOS TRANSISTOR LEAKAGE ENCLOSED TRANSISTOR LAYOUT Example from 0. 5 mm technology (tox ~ 10 nm)

NMOS INTER-TRANSISTOR LEAKAGE GUARD RINGS Well/ Substrate Drain 1 Source 1 Gate 1 P+ Source 2 Gate 2 N+

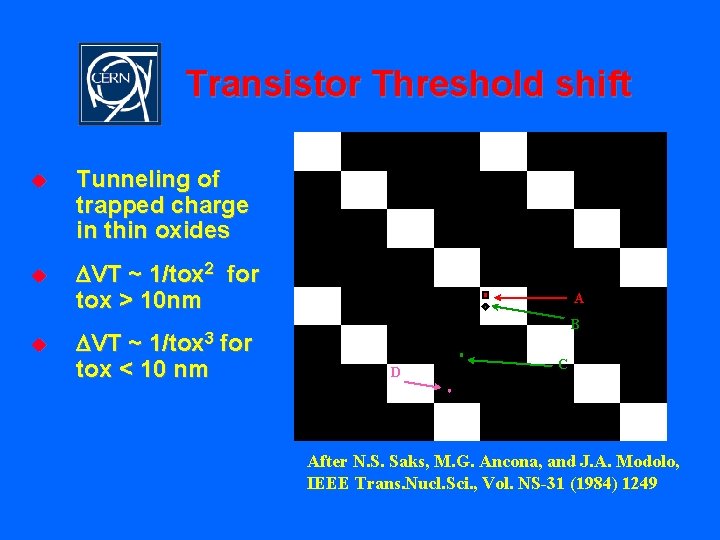

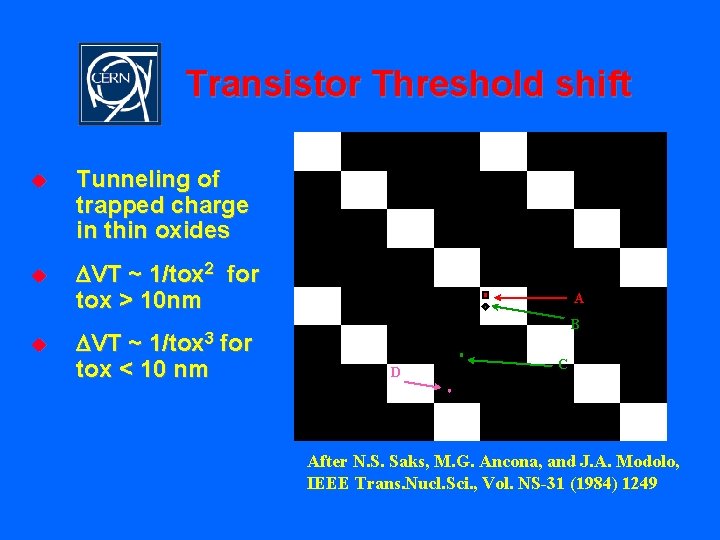

Transistor Threshold shift u Tunneling of trapped charge in thin oxides u DVT ~ 1/tox 2 for tox > 10 nm u DVT ~ for tox < 10 nm A B 1/tox 3 D C After N. S. Saks, M. G. Ancona, and J. A. Modolo, IEEE Trans. Nucl. Sci. , Vol. NS-31 (1984) 1249

Layout Techniques for Radiation Tolerance : Conclusion u u N-channel transistor leakage solved by enclosed geometry layout N-channel inter-transistor (field) leakage solved by guard rings Radiation induced trapped charge and interface : - reduced for thin oxides - for very thin oxides (tox < 10 nm) reduced much more => radiation induced transistor parameter shifts smaller and smaller in deeper submicron technologies

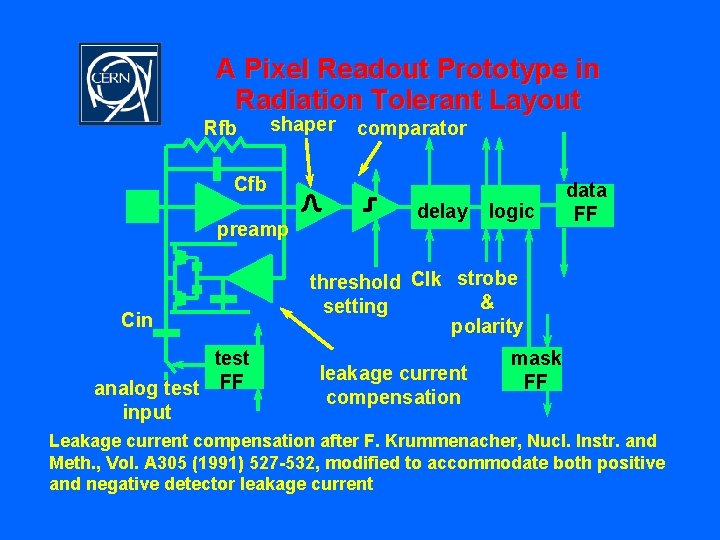

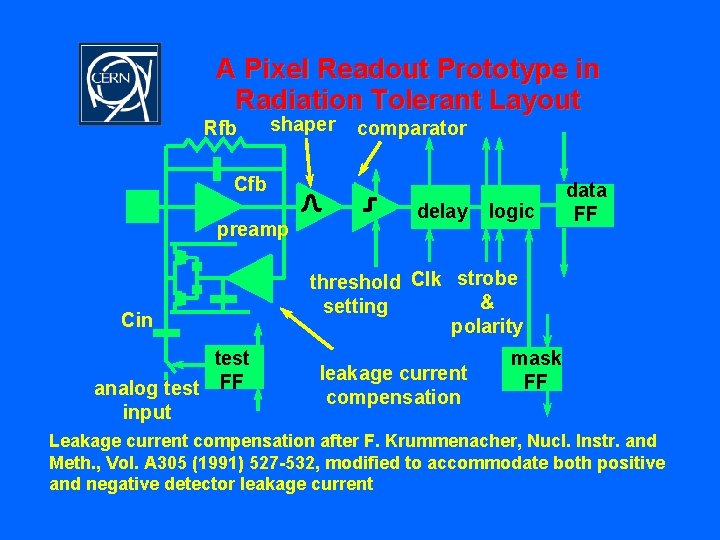

A Pixel Readout Prototype in Radiation Tolerant Layout Rfb shaper comparator Cfb preamp Cin test analog test FF input delay logic data FF threshold Clk strobe & setting polarity leakage current compensation mask FF Leakage current compensation after F. Krummenacher, Nucl. Instr. and Meth. , Vol. A 305 (1991) 527 -532, modified to accommodate both positive and negative detector leakage current

ALICE 1 ELECTRICAL RESULTS Detector leakage current compensation u u No pixel threshold change Noise increases with detector leakage current as expected

LHC 2 TEST/ALICE 1 TEST ELECTRICAL RESULTS Timewalk

ELECTRICAL RESULTS Timewalk on LHC 1 for comparison

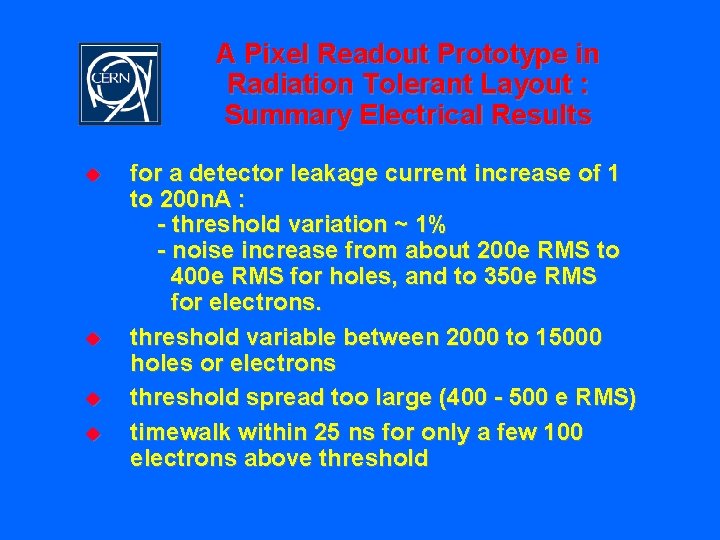

A Pixel Readout Prototype in Radiation Tolerant Layout : Summary Electrical Results u u for a detector leakage current increase of 1 to 200 n. A : - threshold variation ~ 1% - noise increase from about 200 e RMS to 400 e RMS for holes, and to 350 e RMS for electrons. threshold variable between 2000 to 15000 holes or electrons threshold spread too large (400 - 500 e RMS) timewalk within 25 ns for only a few 100 electrons above threshold

ALICE 2 TEST ELECTRICAL RESULTS Threshold uniformity and noise u u u Threshold variation about 160 e rms, without 3 bit threshold adjust Noise about 220 e rms 1 m. V ~ 100 e

ALICE 2 TEST ELECTRICAL RESULTS Average Threshold, Threshold variation and average noise

ALICE 2 TEST (0. 25 mm) : Summary Electrical Results u u Characterization in progress Already established : - minimum threshold 1500 e or below - 3 bit threshold adjust works - detector leakage current compensation works up to several 100 n. A/pixel - both dynamic and static counter based delay lines work

LHC 2 TEST/ALICE 1 TEST Evolution of Threshold and Threshold Variation with Xray Dose

LHC 2 TEST/ALICE 1 TEST Evolution of Power Consumption with Xray Dose u Analog no change u Digital can be explained by Vt shift u Validates layout approach on global scale

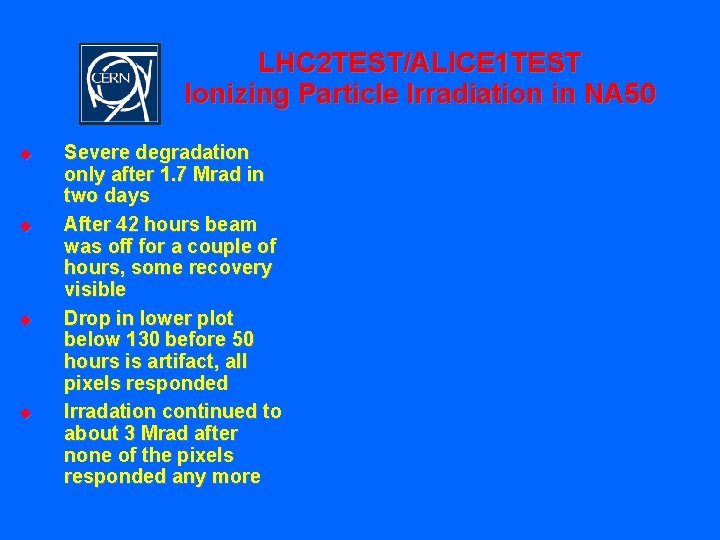

LHC 2 TEST/ALICE 1 TEST Ionizing Particle Irradiation in NA 50 u u Severe degradation only after 1. 7 Mrad in two days After 42 hours beam was off for a couple of hours, some recovery visible Drop in lower plot below 130 before 50 hours is artifact, all pixels responded Irradation continued to about 3 Mrad after none of the pixels responded any more

Ionizing Particle Irradiation in NA 50 : anneal u u Some pixels start to respond after 1 week of annealing at room temperature The last week of anneal was carried out at 100 C => slope change

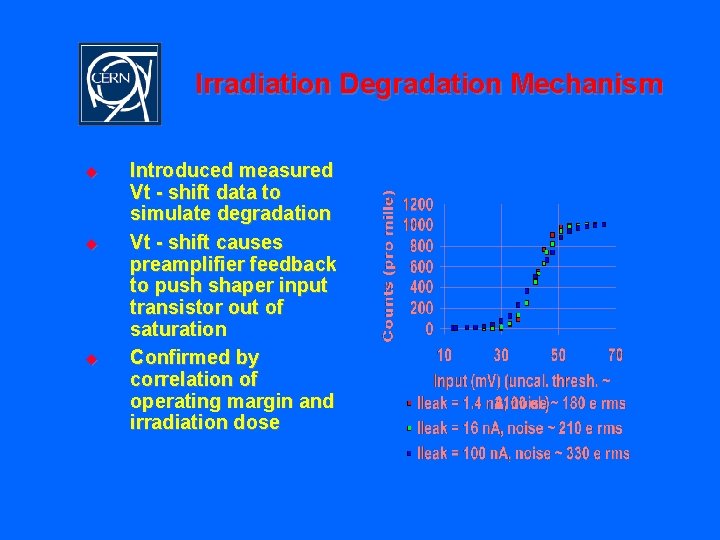

Irradiation Degradation Mechanism Measured NMOS transistor VT shift

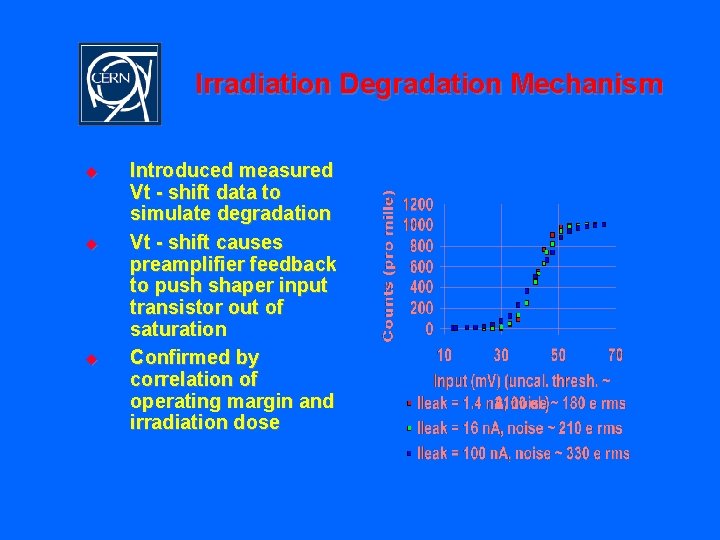

Irradiation Degradation Mechanism u u u Introduced measured Vt - shift data to simulate degradation Vt - shift causes preamplifier feedback to push shaper input transistor out of saturation Confirmed by correlation of operating margin and irradiation dose

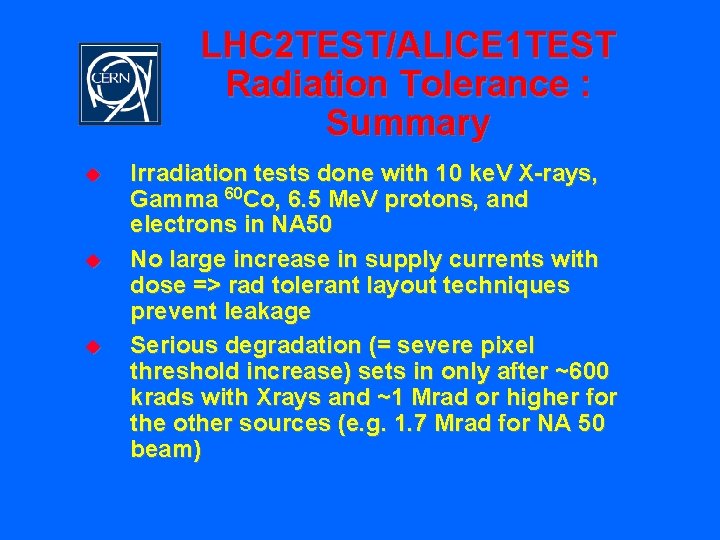

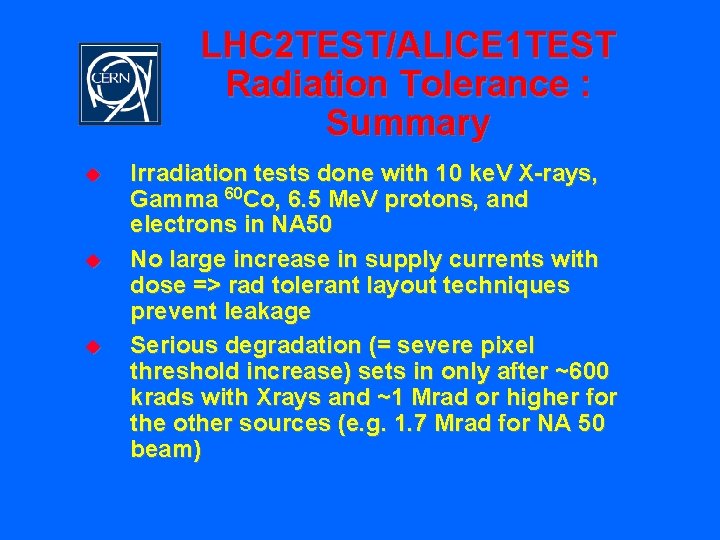

LHC 2 TEST/ALICE 1 TEST Radiation Tolerance : Summary u u u Irradiation tests done with 10 ke. V X-rays, Gamma 60 Co, 6. 5 Me. V protons, and electrons in NA 50 No large increase in supply currents with dose => rad tolerant layout techniques prevent leakage Serious degradation (= severe pixel threshold increase) sets in only after ~600 krads with Xrays and ~1 Mrad or higher for the other sources (e. g. 1. 7 Mrad for NA 50 beam)

LHC 2 TEST/ALICE 1 TEST Radiation Tolerance : Summary u u Degradation mechanism explained through Vt shift Significant recovery (annealing) after a relatively short time

ALICE 2 TEST Chip Evolution of power supply currents with X-ray dose (10 ke. V X-rays at 4 krad/min)

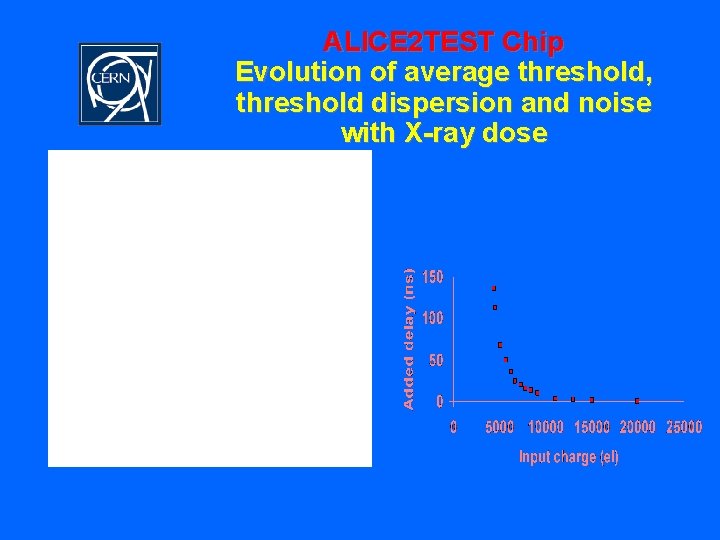

ALICE 2 TEST Chip Evolution of average threshold, threshold dispersion and noise with X-ray dose

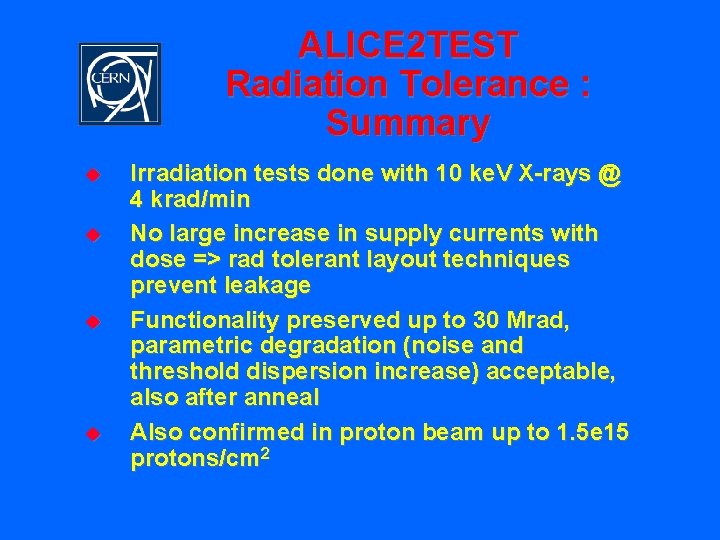

ALICE 2 TEST Radiation Tolerance : Summary u u Irradiation tests done with 10 ke. V X-rays @ 4 krad/min No large increase in supply currents with dose => rad tolerant layout techniques prevent leakage Functionality preserved up to 30 Mrad, parametric degradation (noise and threshold dispersion increase) acceptable, also after anneal Also confirmed in proton beam up to 1. 5 e 15 protons/cm 2

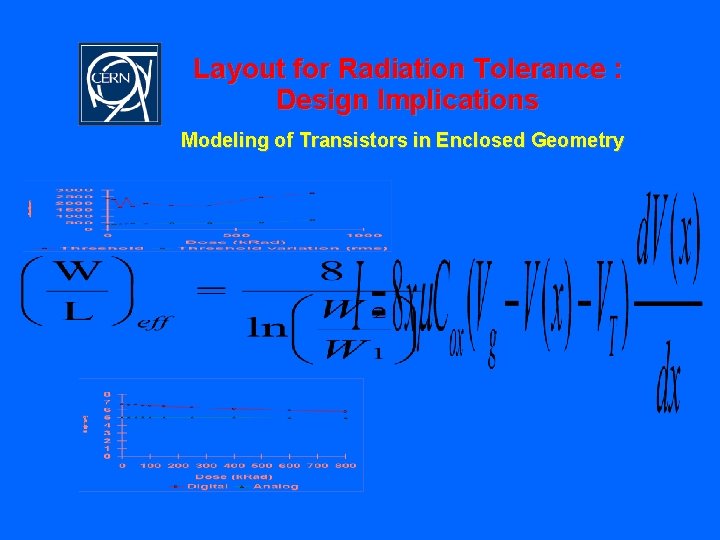

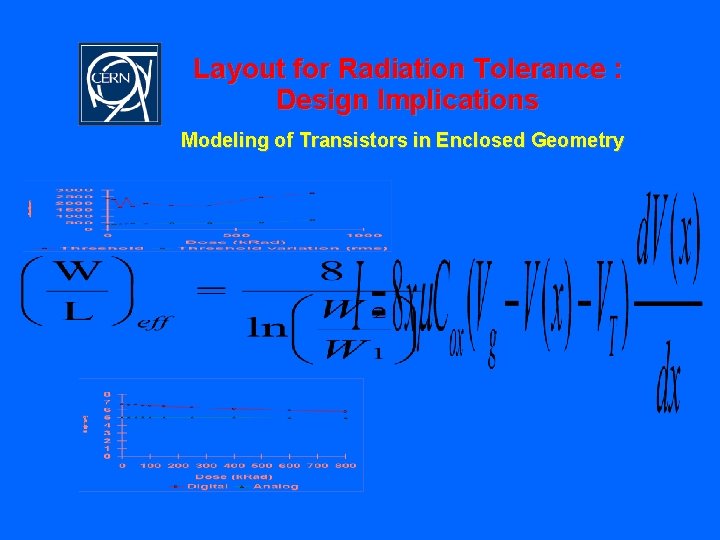

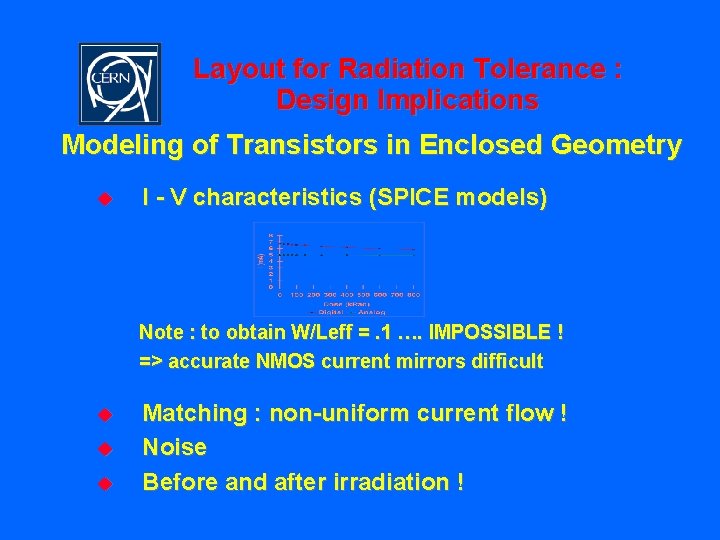

Layout for Radiation Tolerance : Design Implications Modeling of Transistors in Enclosed Geometry

Layout for Radiation Tolerance : Design Implications Modeling of Transistors in Enclosed Geometry u I - V characteristics (SPICE models) Note : to obtain W/Leff =. 1 …. IMPOSSIBLE ! => accurate NMOS current mirrors difficult u u u Matching : non-uniform current flow ! Noise Before and after irradiation !

Layout for Radiation Tolerance : Design Implications Circuit Density : u u u Digital : there clearly is a penalty for the same technology. However, one should compare not to the same technology but to a radiation hard/tolerant alternative. Analog : example showed certain circuit topologies (making use of accurate NMOS mirrors for instance…) should be avoided. In that case small penalty even for same technology. Number of metal layers plays a big role

Layout for Radiation Tolerance : Design Implications CAD Environment (!!!) u u Digital library = full custom Verification routines : DRC, extraction, LVS ALL require some modification

CONCLUSIONS AND PERSPECTIVES u u u Special layout + thin gate oxide = radiation tolerance Special layout techniques have made a pixel readout prototype implemented in a - commercial 0. 5 mm CMOS technology radiation tolerant up to ~ 1 Mrad. - commercial 0. 25 mm CMOS technology radiation tolerant up to 30 Mrad. Density, power-speed performance, and radiation tolerance => deeper submicron Design implications Note : Single event effects

CONCLUSIONS AND PERSPECTIVES u u Thinner gate oxide helps to reduce radiation induced transistor parameter shifts and therefore significantly increases radiation tolerance Density, power-speed performance, and radiation tolerance => deeper u submicron Some issues not discussed : Single Event Upset : will be very important in some of the future LHC experiments and Single Event Latchup

ALICE 2 TEST Radiation Tolerance : Summary u u Irradiation tests done with 10 ke. V X-rays @ 4 krad/min No large increase in supply currents with dose => rad tolerant layout techniques prevent leakage Functionality preserved up to 30 Mrad, parametric degradation (noise and threshold dispersion increase) acceptable, also after anneal Special layout techniques have made a pixel readout prototype implemented in a commercial 0. 25 mm CMOS technology radiation tolerant up to 30 Mrad.