Latches and FlipFlops Discussion D 4 1 Appendix

- Slides: 53

Latches and Flip-Flops Discussion D 4. 1 Appendix J

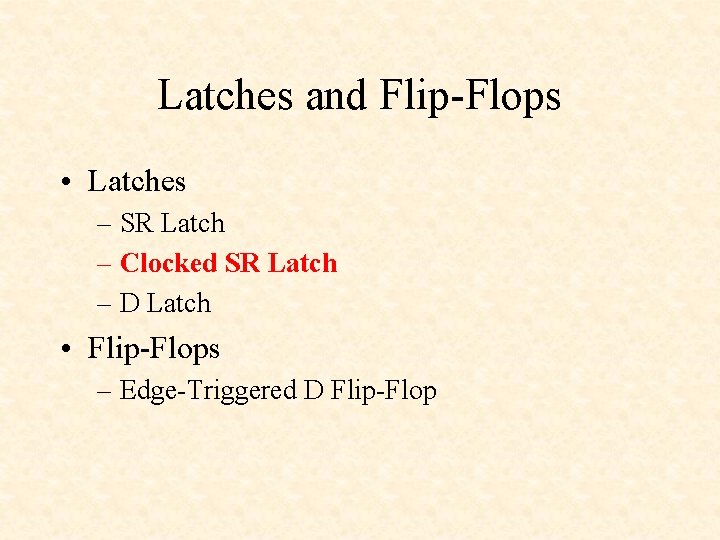

Latches and Flip-Flops • Latches – SR Latch – Clocked SR Latch – D Latch • Flip-Flops – Edge-Triggered D Flip-Flop

Sequential Logic • Combinational Logic – Output depends only on current input • Sequential Logic – Output depends not only on current input but also on past input values – Need some type of memory to remember the past input values

Cross-coupled Inverters State 1 State 2

Latches and Flip-Flops • Latches – SR Latch – Clocked SR Latch – D Latch • Flip-Flops – Edge-Triggered D Flip-Flop

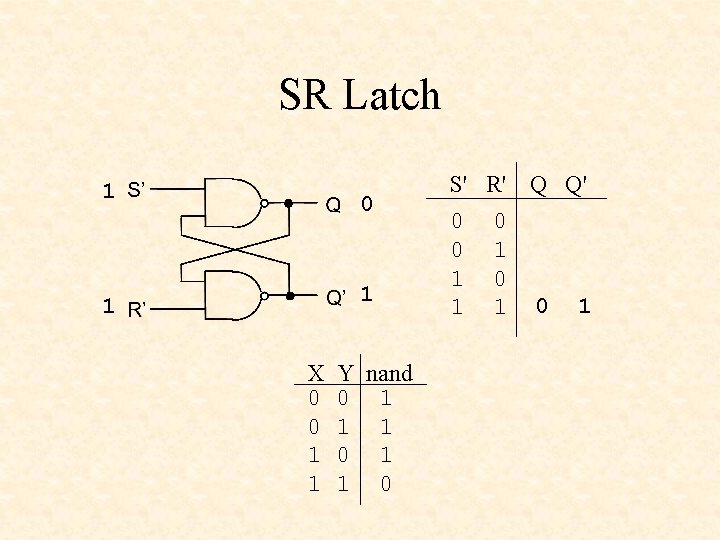

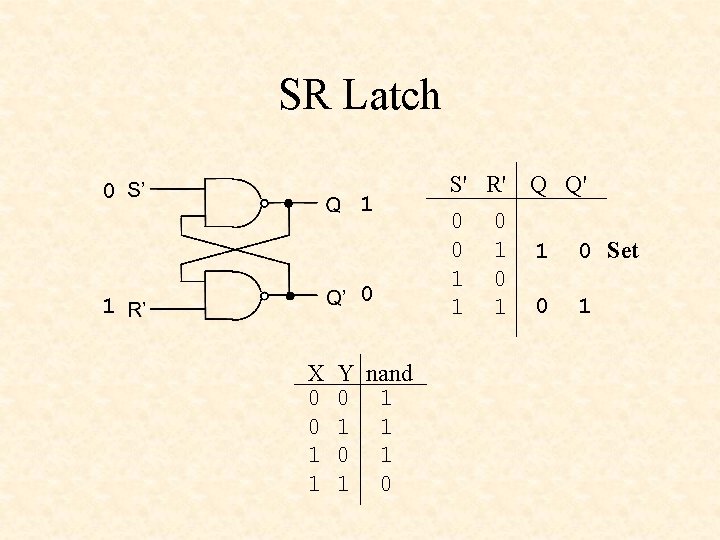

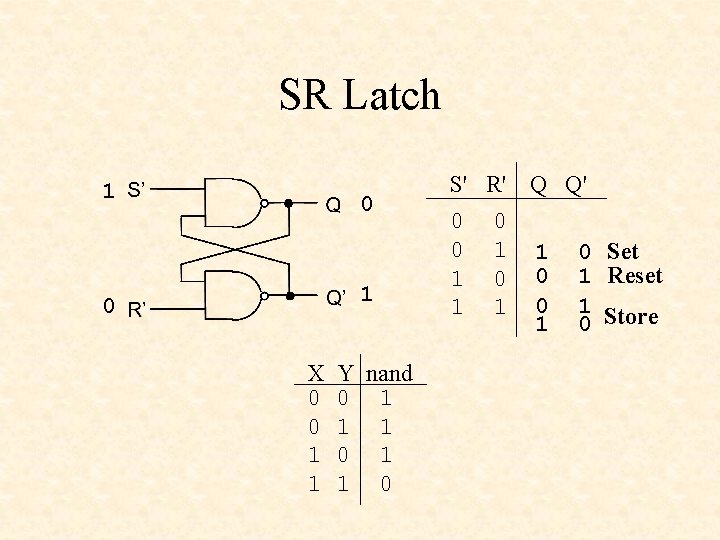

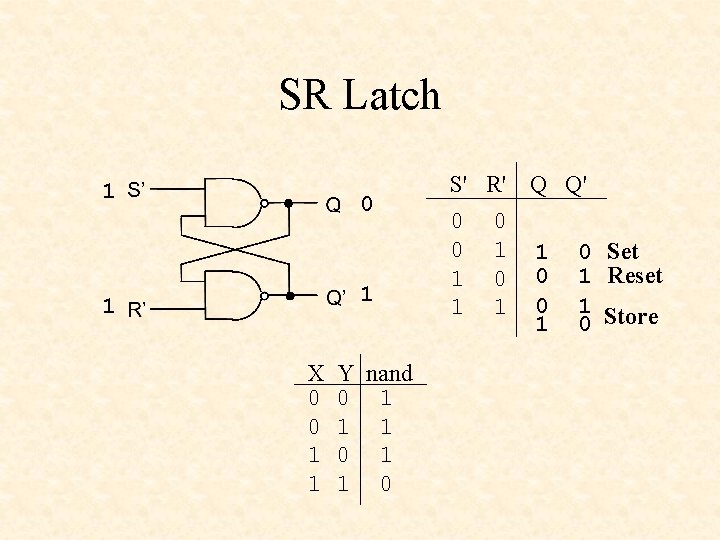

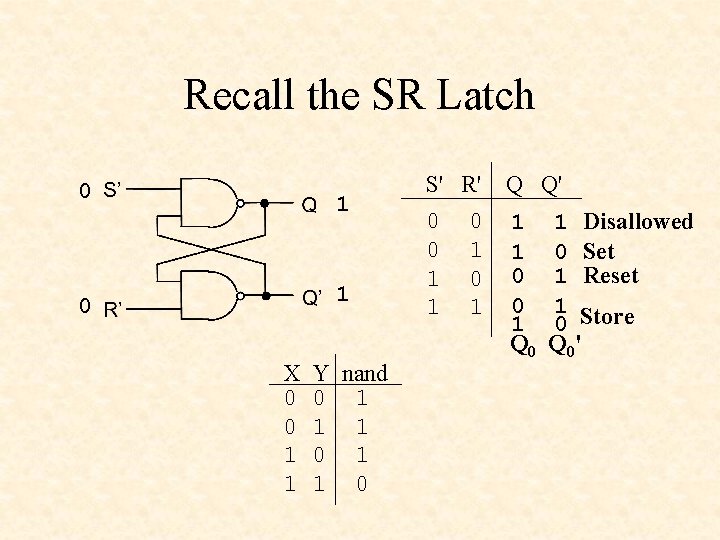

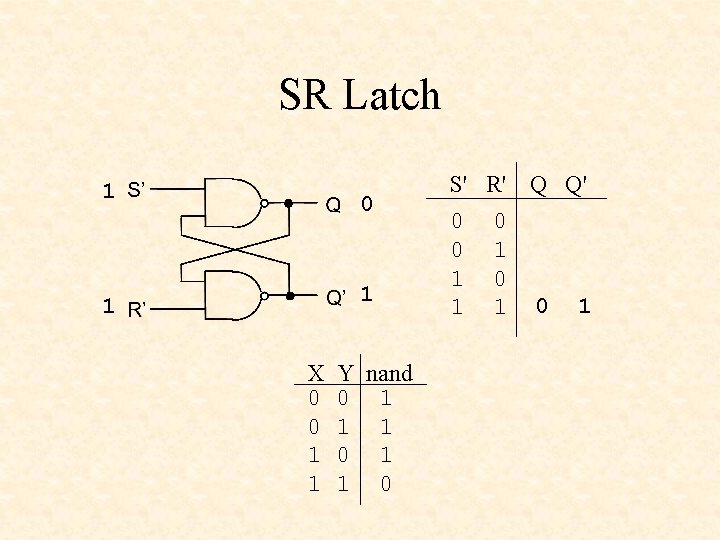

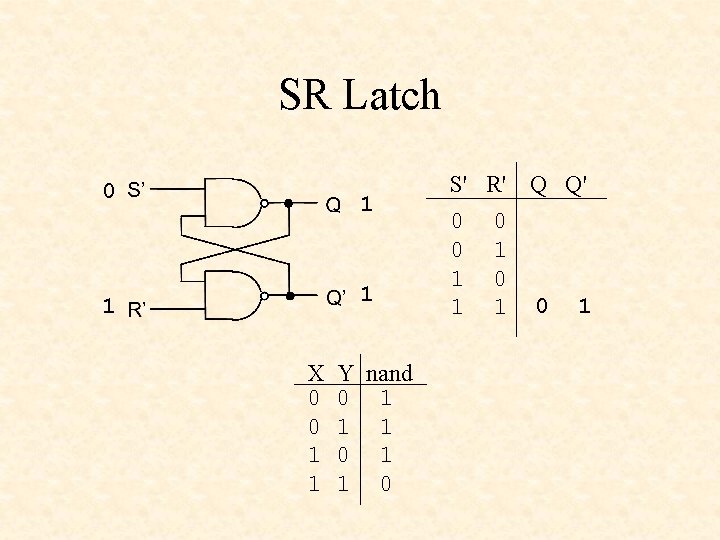

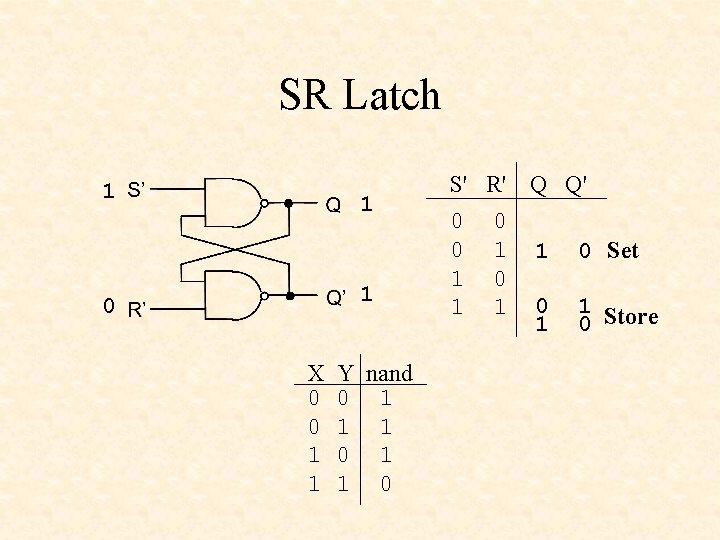

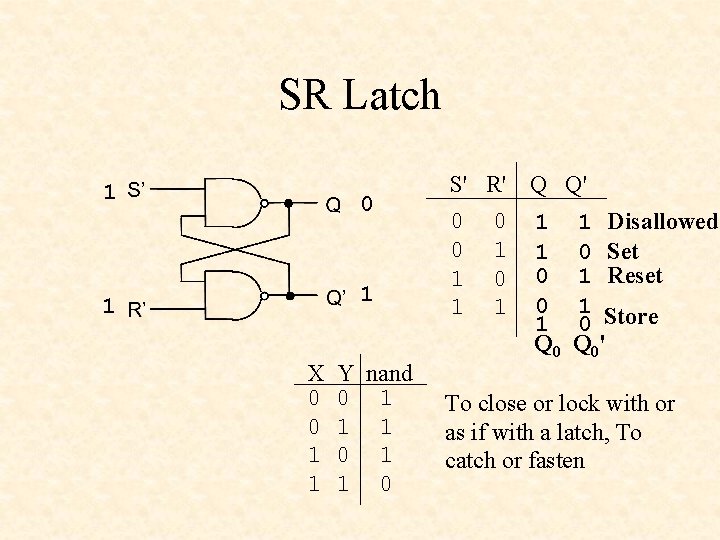

SR Latch 1 0 1 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 1

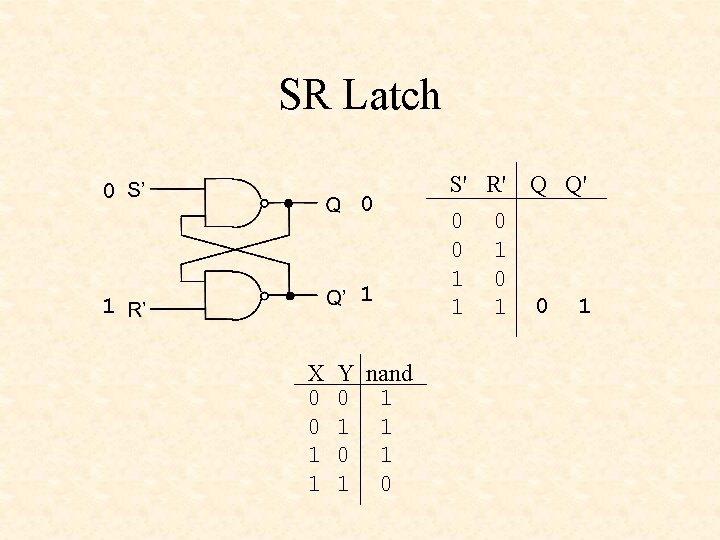

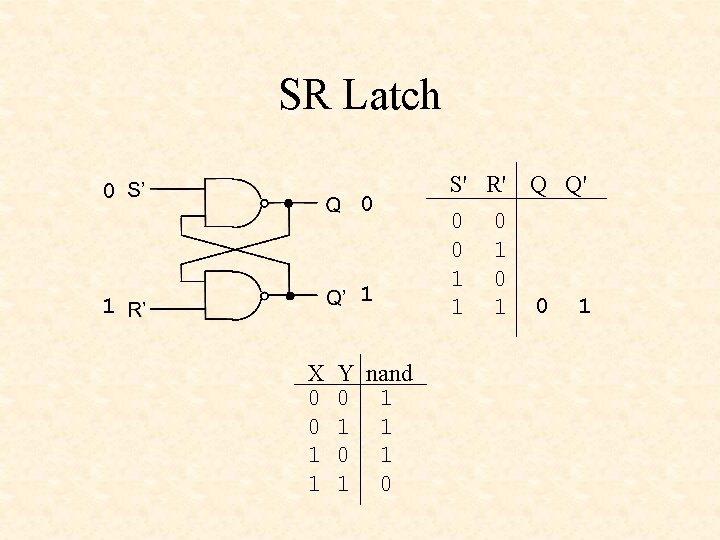

SR Latch 0 0 1 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 1

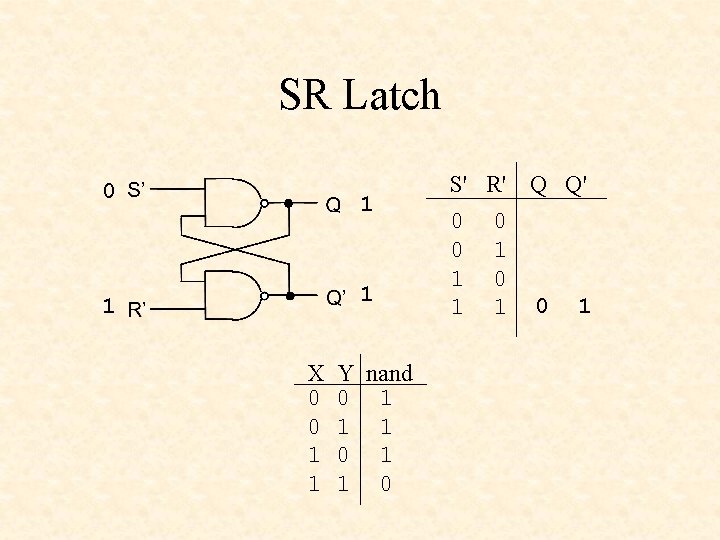

SR Latch 0 1 1 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 1

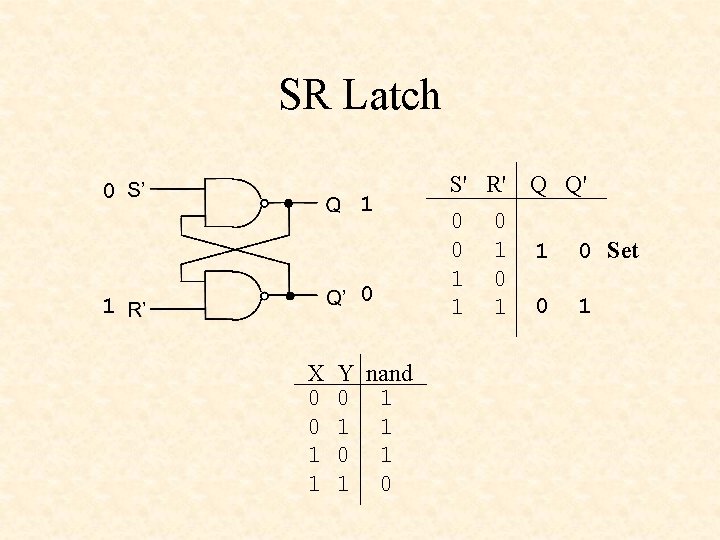

SR Latch 0 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 Set 1 0 1

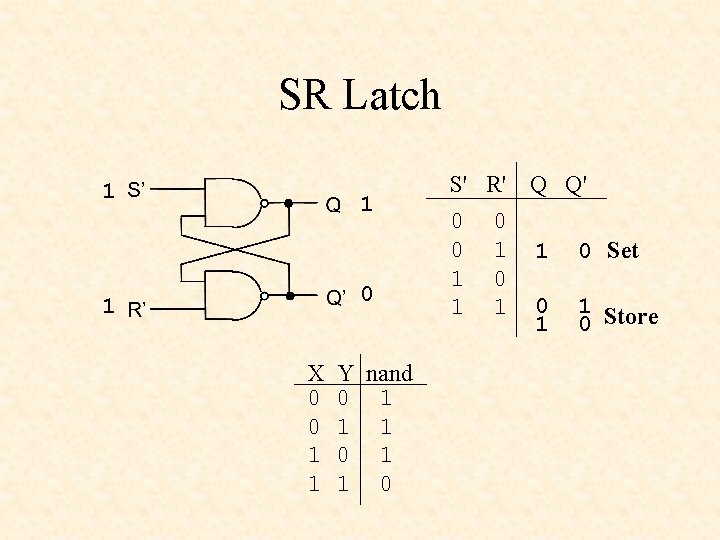

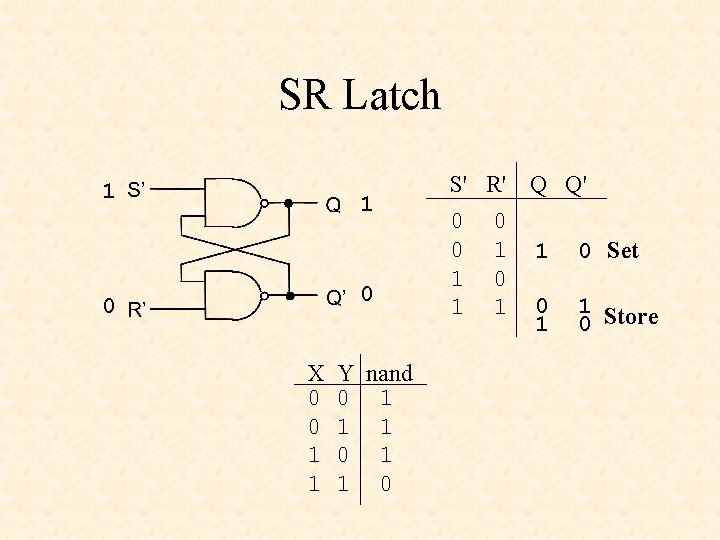

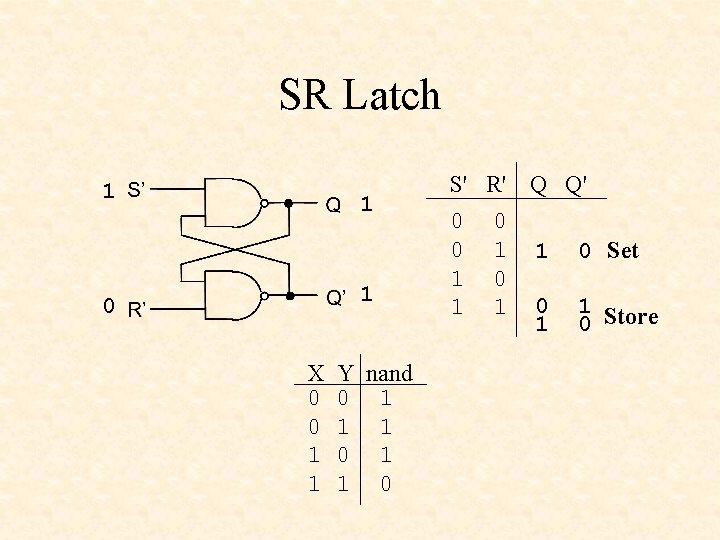

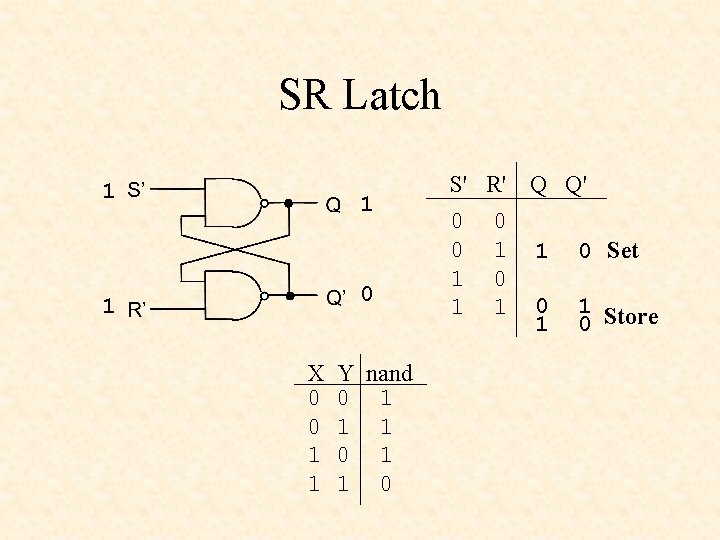

SR Latch 1 1 0 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 Set 1 0 1 Store 1 0

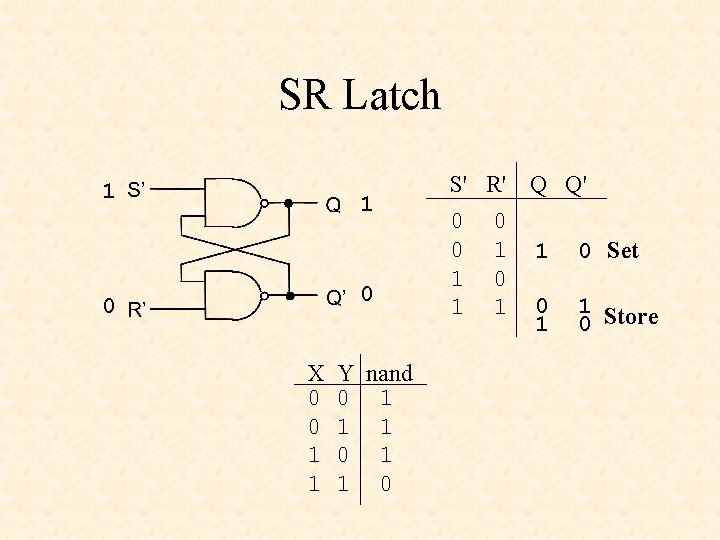

SR Latch 1 1 0 0 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 Set 1 0 1 Store 1 0

SR Latch 1 1 1 0 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 Set 1 0 1 Store 1 0

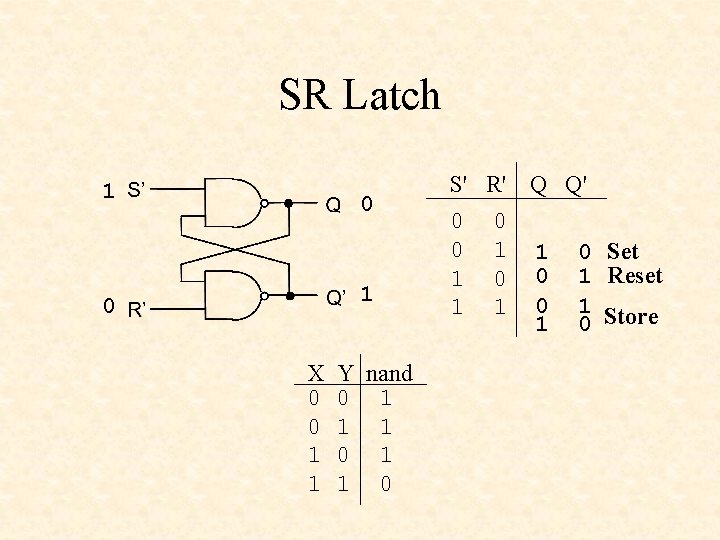

SR Latch 1 0 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 Set 1 0 0 1 Reset 1 1 0 1 Store 1 0

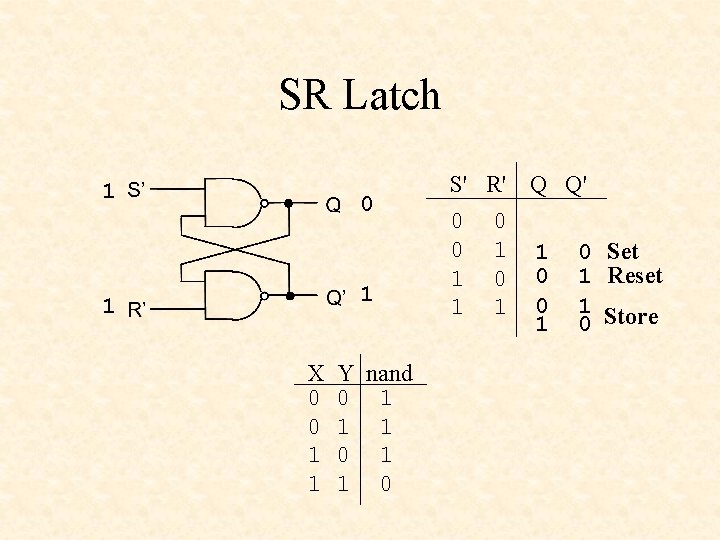

SR Latch 1 0 1 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 0 1 1 0 Set 1 0 0 1 Reset 1 1 0 1 Store 1 0

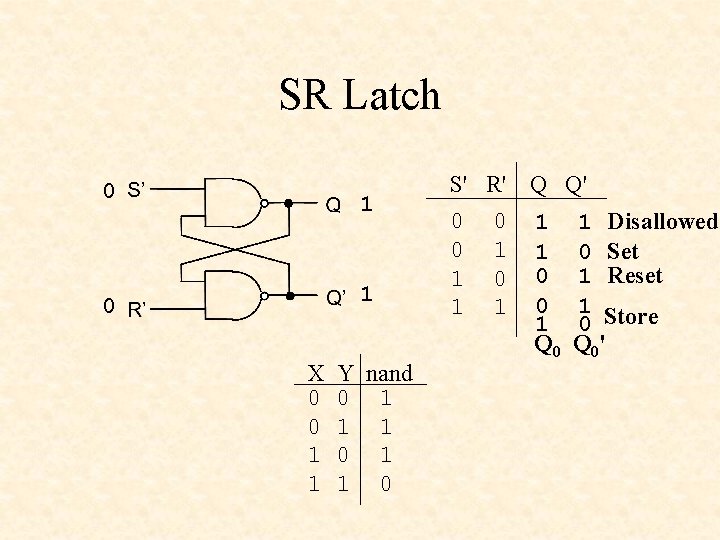

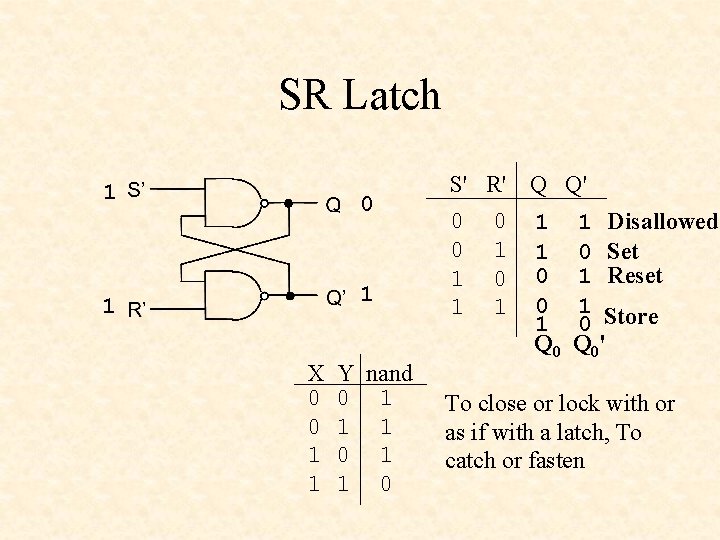

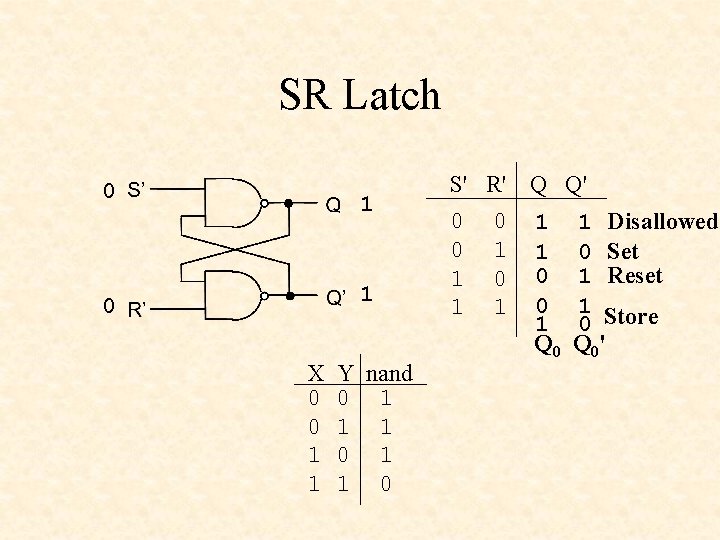

SR Latch 0 1 1 0 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 1 1 Disallowed 0 1 1 0 Set 1 0 0 1 Reset 1 1 0 1 Store 1 0 Q 0'

SR Latch 1 0 1 1 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 1 1 Disallowed 0 1 1 0 Set 1 0 0 1 Reset 1 1 0 1 Store 1 0 Q 0' To close or lock with or as if with a latch, To catch or fasten

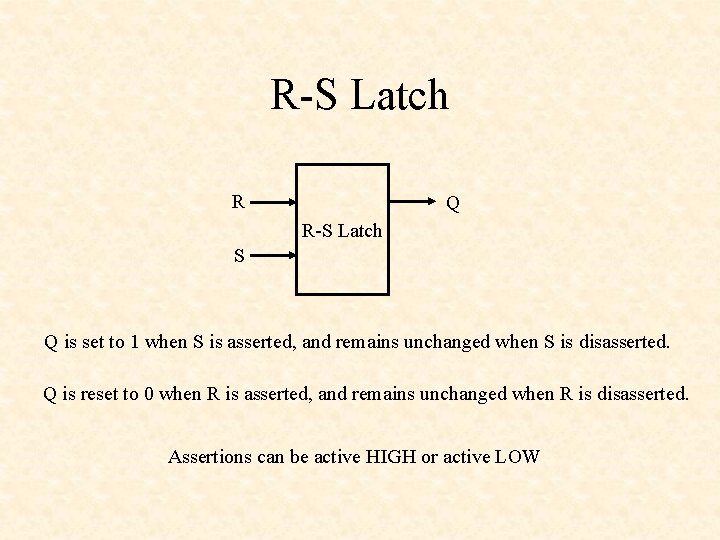

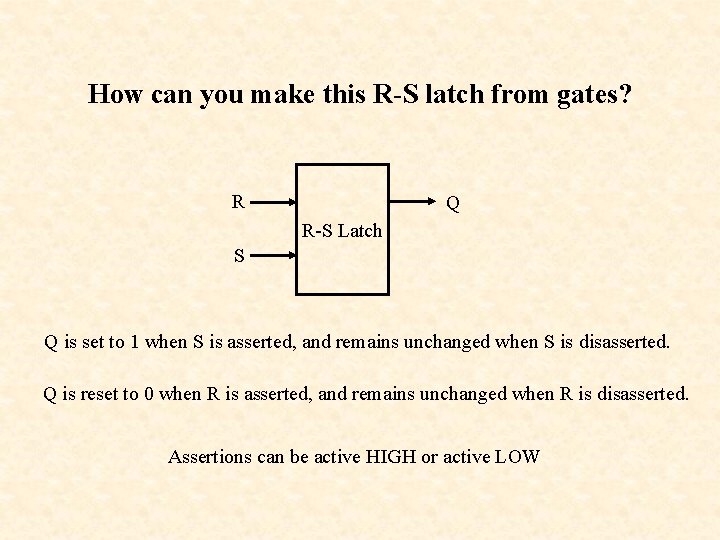

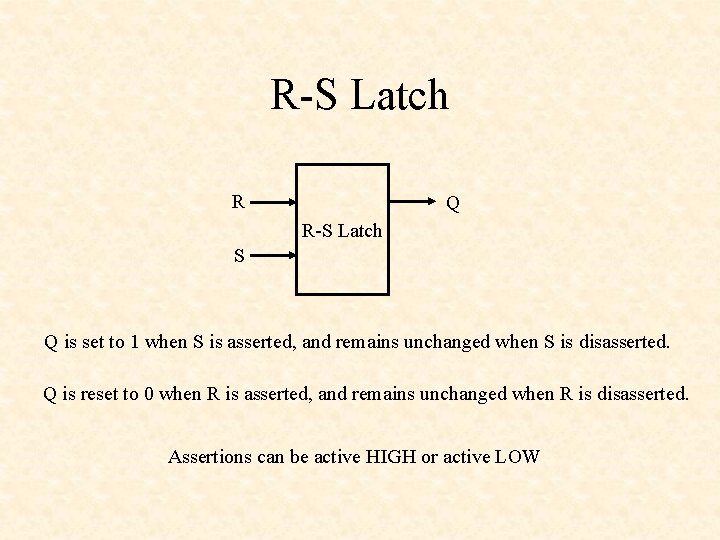

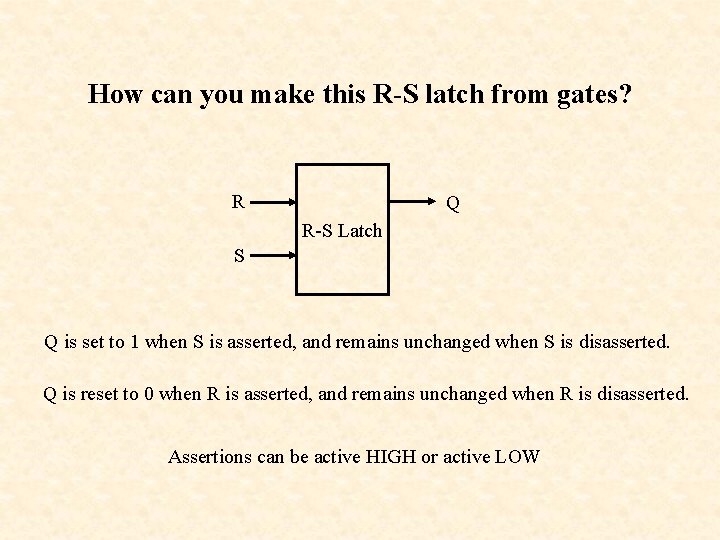

R-S Latch R Q R-S Latch S Q is set to 1 when S is asserted, and remains unchanged when S is disasserted. Q is reset to 0 when R is asserted, and remains unchanged when R is disasserted. Assertions can be active HIGH or active LOW

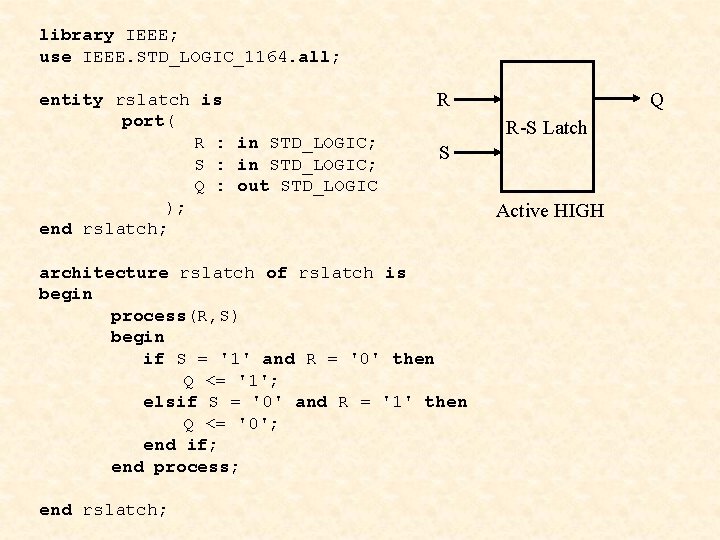

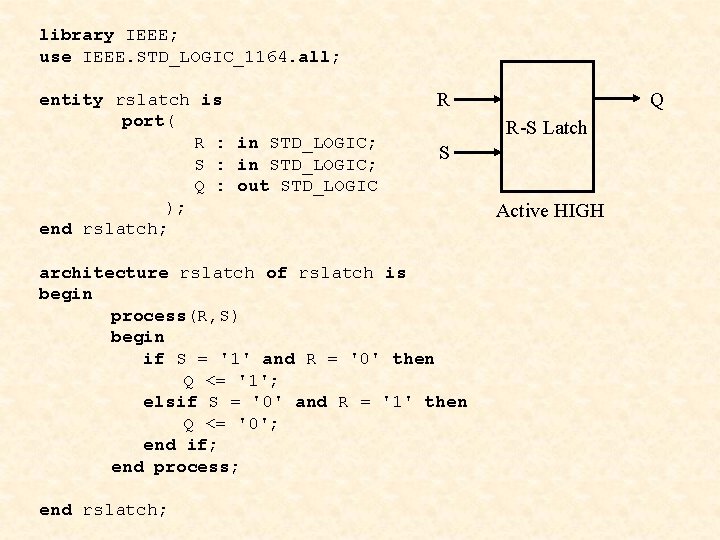

library IEEE; use IEEE. STD_LOGIC_1164. all; entity rslatch is port( R : in STD_LOGIC; S : in STD_LOGIC; Q : out STD_LOGIC ); end rslatch; R R-S Latch S architecture rslatch of rslatch is begin process(R, S) begin if S = '1' and R = '0' then Q <= '1'; elsif S = '0' and R = '1' then Q <= '0'; end if; end process; end rslatch; Q Active HIGH

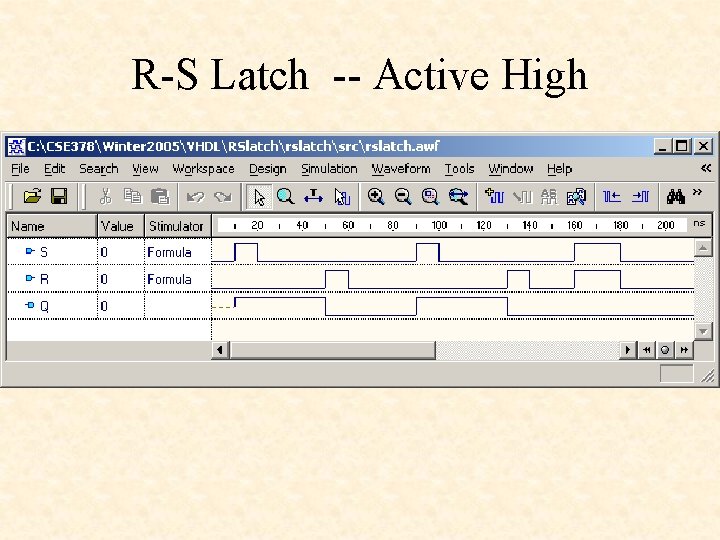

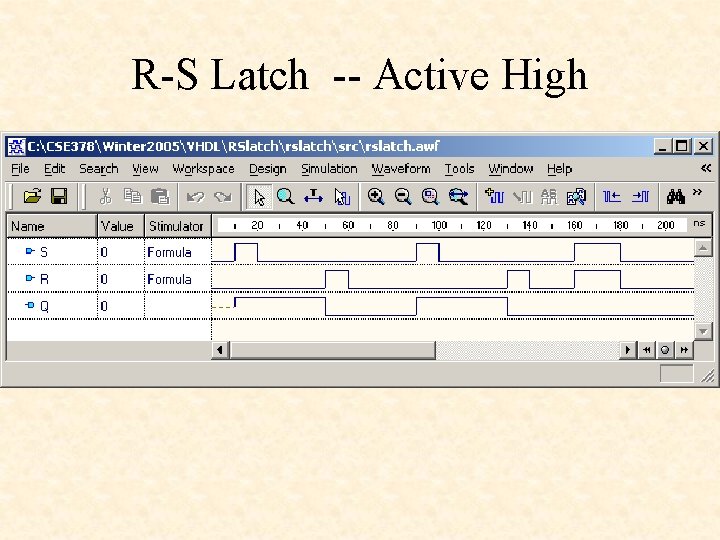

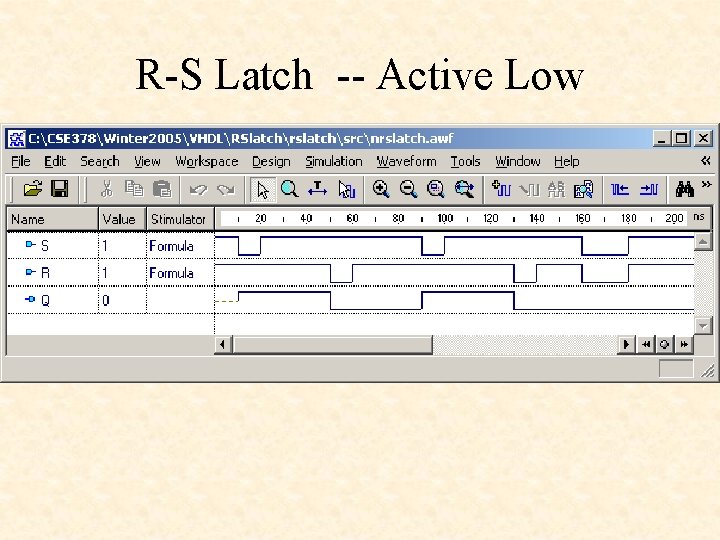

R-S Latch -- Active High

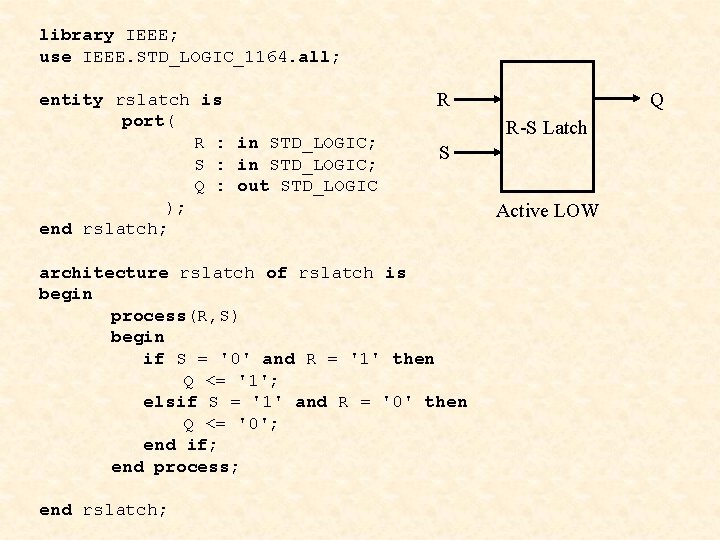

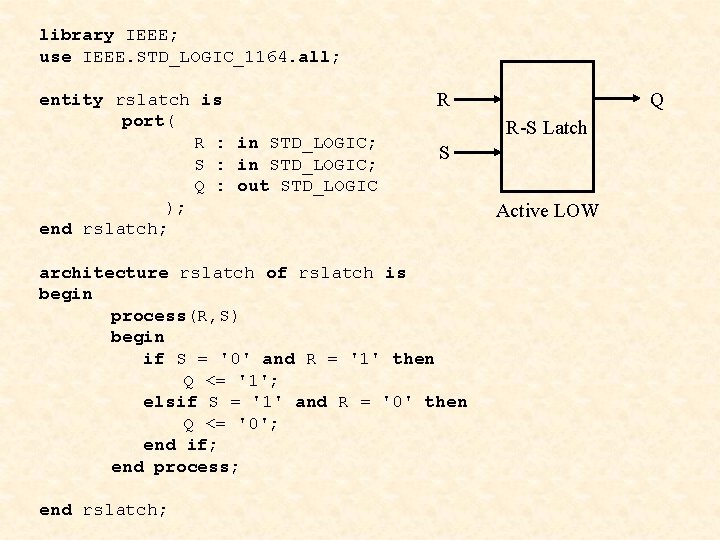

library IEEE; use IEEE. STD_LOGIC_1164. all; entity rslatch is port( R : in STD_LOGIC; S : in STD_LOGIC; Q : out STD_LOGIC ); end rslatch; R R-S Latch S architecture rslatch of rslatch is begin process(R, S) begin if S = '0' and R = '1' then Q <= '1'; elsif S = '1' and R = '0' then Q <= '0'; end if; end process; end rslatch; Q Active LOW

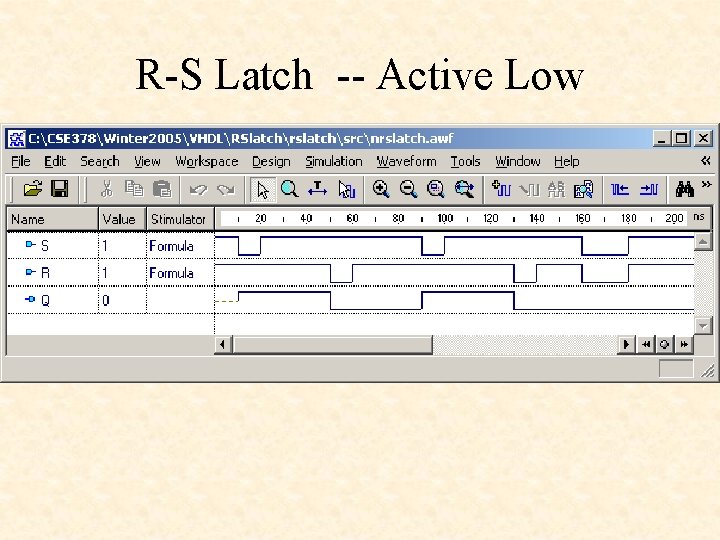

R-S Latch -- Active Low

How can you make this R-S latch from gates? R Q R-S Latch S Q is set to 1 when S is asserted, and remains unchanged when S is disasserted. Q is reset to 0 when R is asserted, and remains unchanged when R is disasserted. Assertions can be active HIGH or active LOW

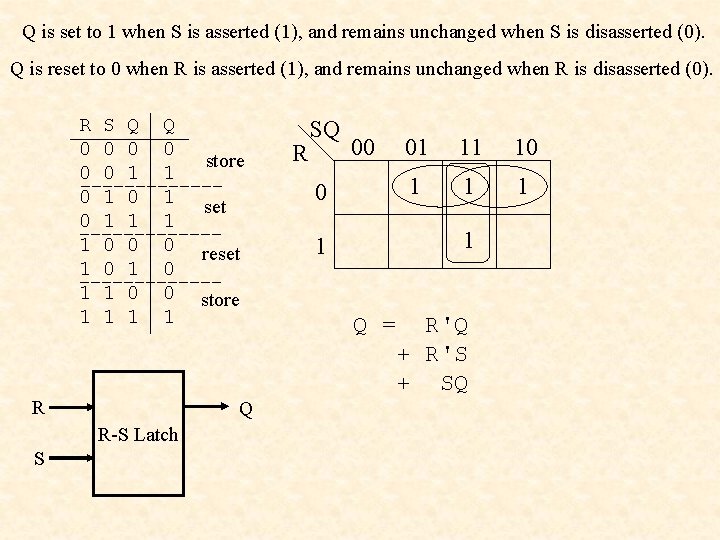

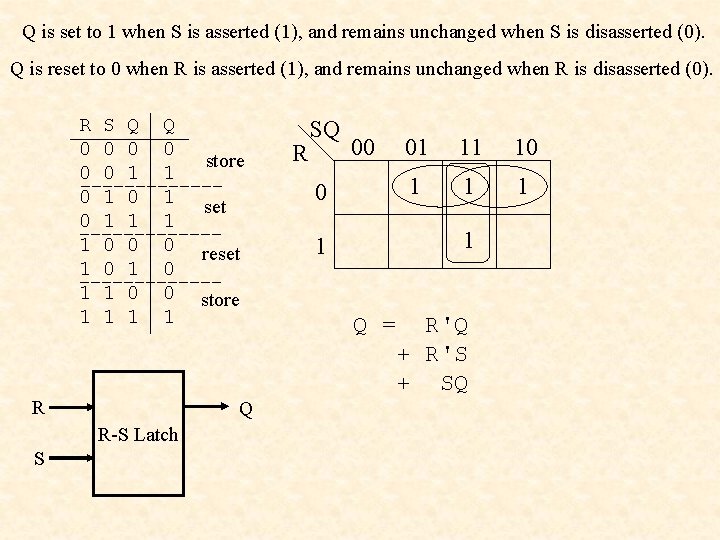

Q is set to 1 when S is asserted (1), and remains unchanged when S is disasserted (0). Q is reset to 0 when R is asserted (1), and remains unchanged when R is disasserted (0). R 0 0 1 1 S 0 0 1 1 Q 0 1 0 1 Q 0 1 1 1 0 0 0 1 R R 00 0 set reset 01 11 10 1 1 1 store Q = Q R-S Latch S store SQ R'Q + R'S + SQ

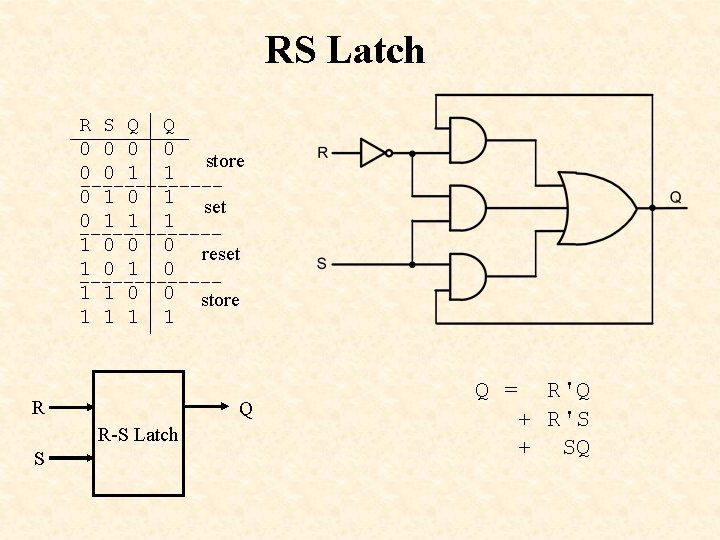

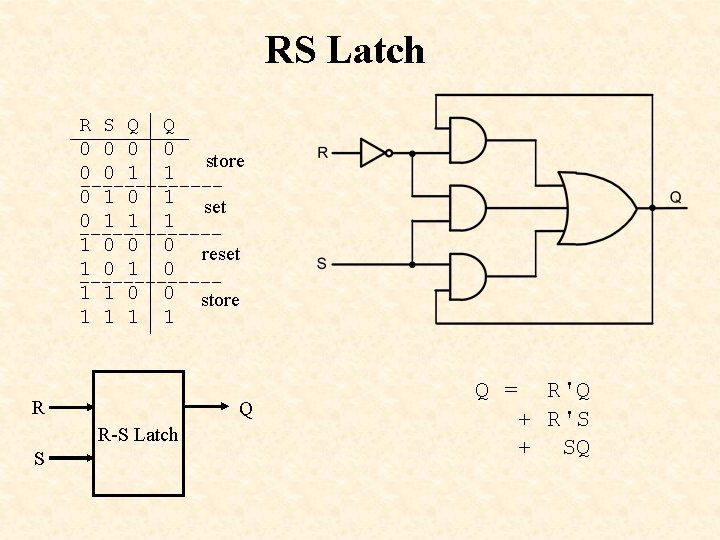

RS Latch R 0 0 1 1 S 0 0 1 1 Q 0 1 0 1 Q 0 1 1 1 0 0 0 1 R set reset store Q R-S Latch S store Q = R'Q + R'S + SQ

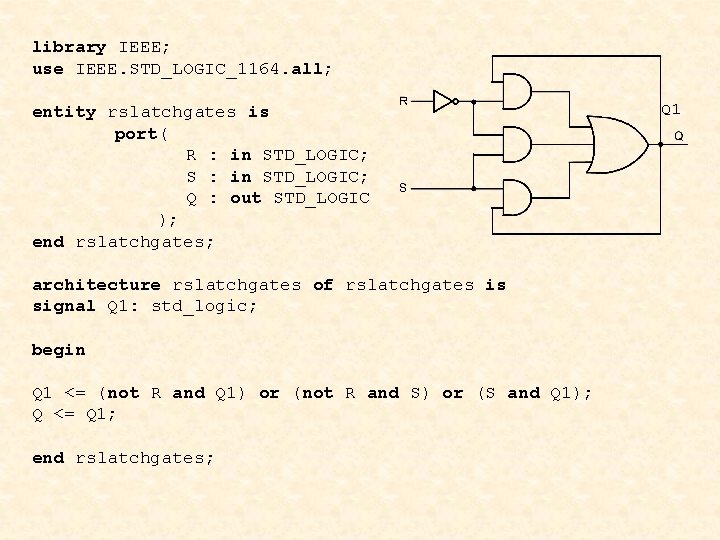

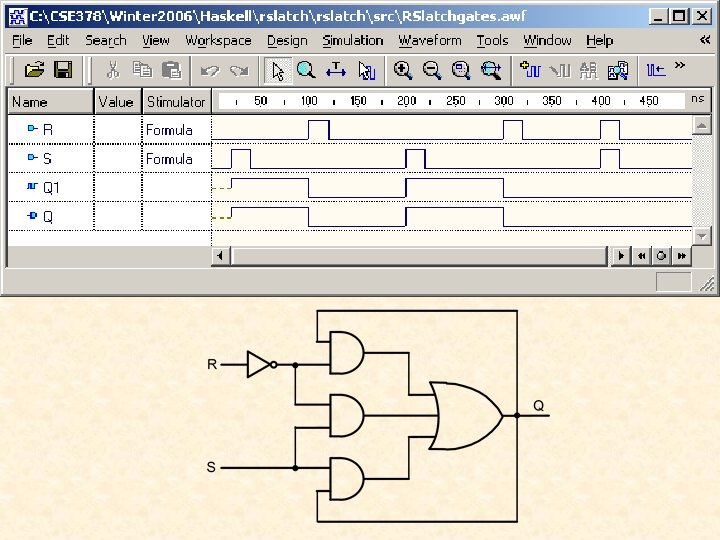

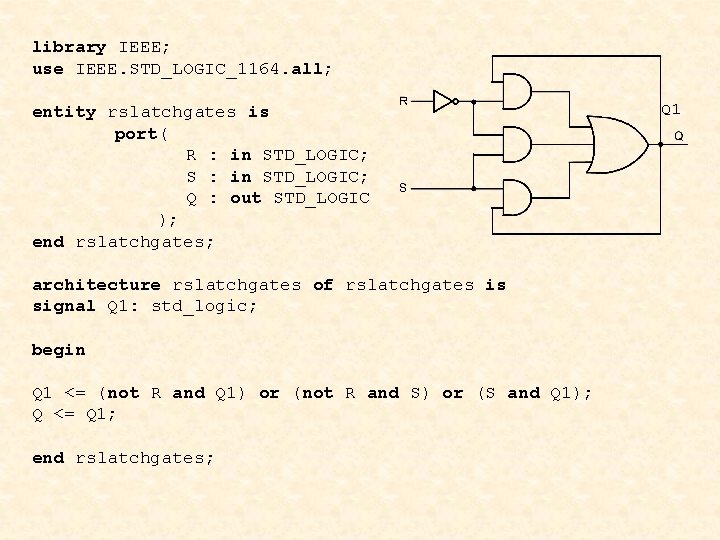

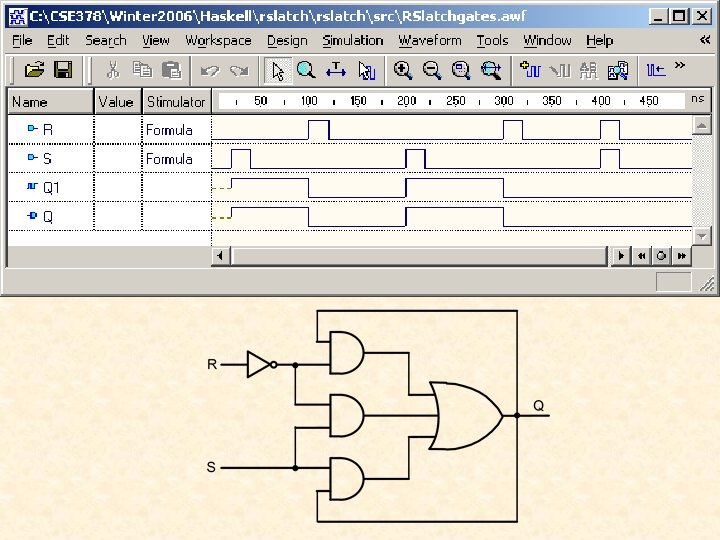

library IEEE; use IEEE. STD_LOGIC_1164. all; entity rslatchgates is port( R : in STD_LOGIC; S : in STD_LOGIC; Q : out STD_LOGIC ); end rslatchgates; architecture rslatchgates of rslatchgates is signal Q 1: std_logic; begin Q 1 <= (not R and Q 1) or (not R and S) or (S and Q 1); Q <= Q 1; end rslatchgates; Q 1

Latches and Flip-Flops • Latches – SR Latch – Clocked SR Latch – D Latch • Flip-Flops – Edge-Triggered D Flip-Flop

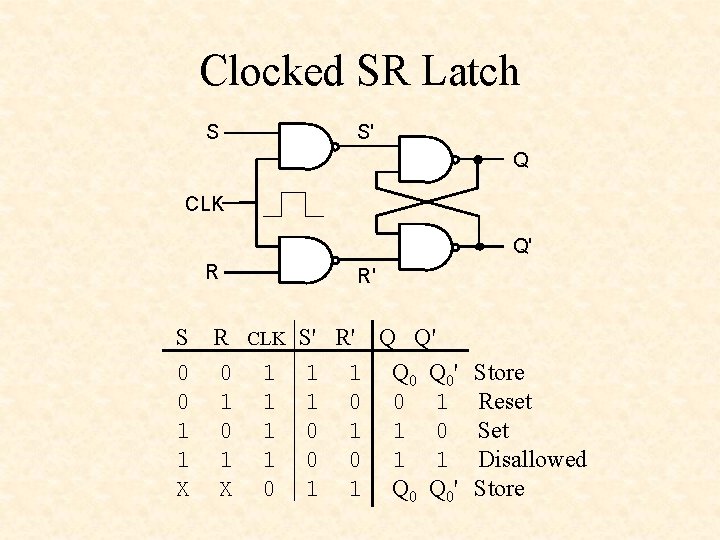

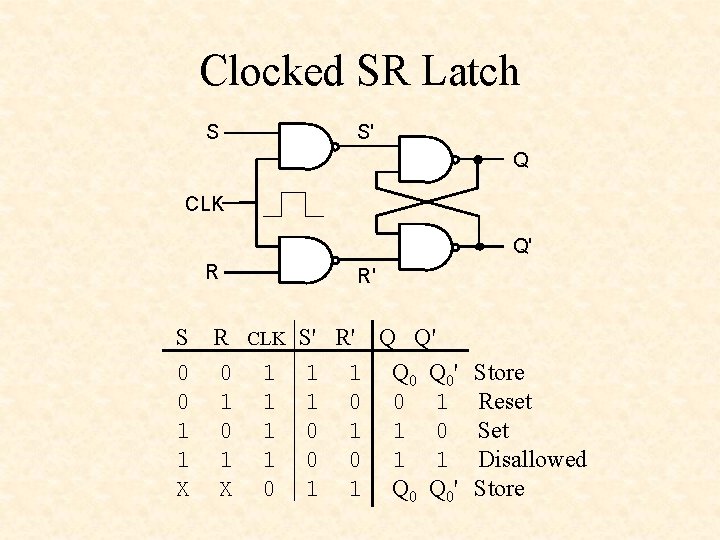

Clocked SR Latch S S' Q CLK Q' R R' S R CLK S' R' Q Q' 0 0 1 1 1 Q 0' 0 1 1 1 0 0 1 1 X X 0 1 1 Q 0' Store Reset Set Disallowed Store

Latches and Flip-Flops • Latches – SR Latch – Clocked SR Latch – D Latch • Flip-Flops – Edge-Triggered D Flip-Flop

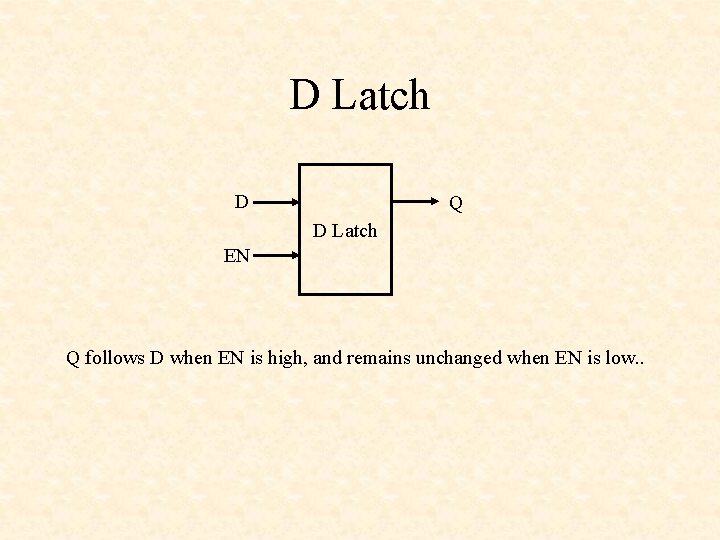

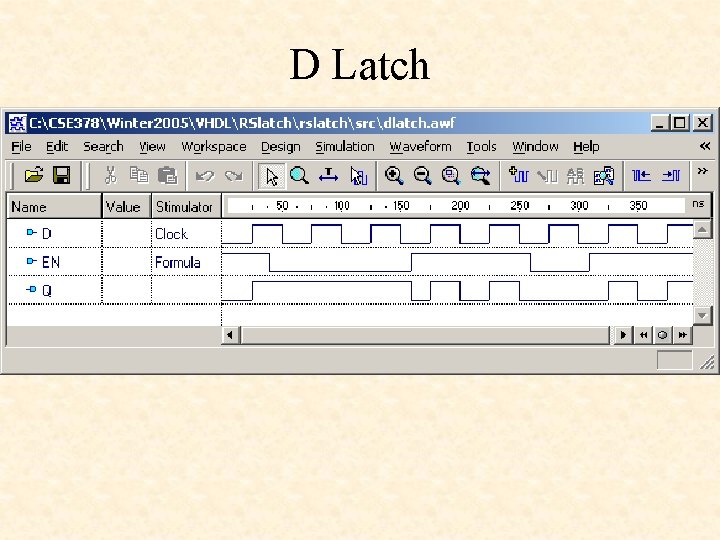

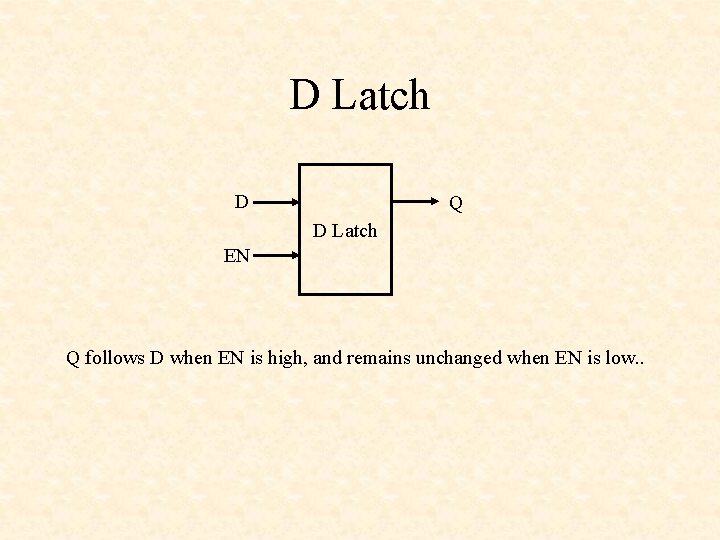

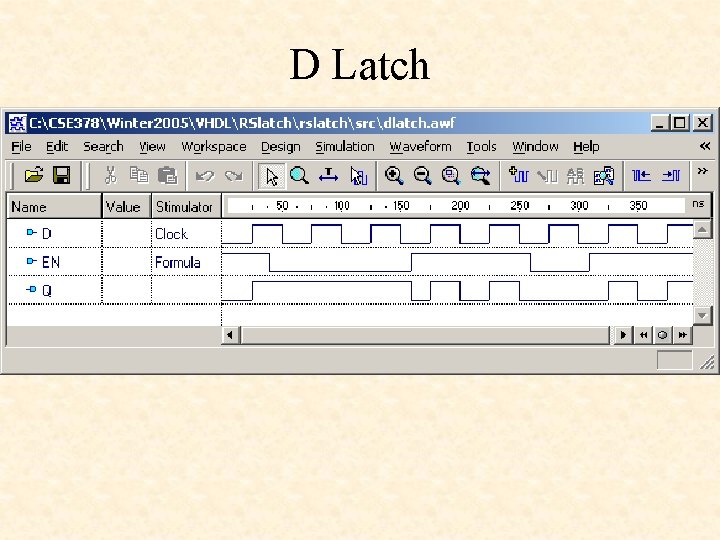

D Latch D Q D Latch EN Q follows D when EN is high, and remains unchanged when EN is low. .

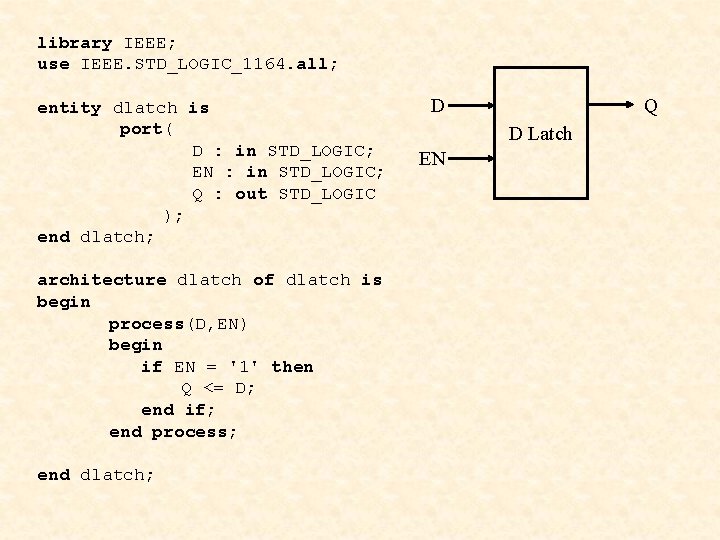

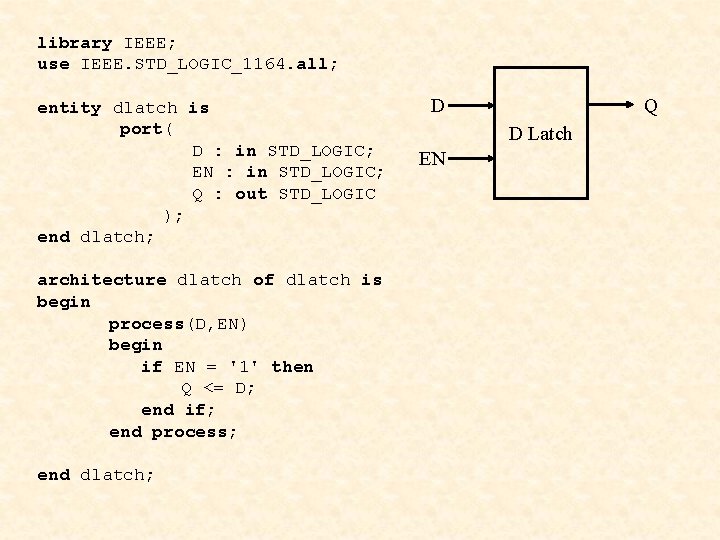

library IEEE; use IEEE. STD_LOGIC_1164. all; entity dlatch is port( D : in STD_LOGIC; EN : in STD_LOGIC; Q : out STD_LOGIC ); end dlatch; architecture dlatch of dlatch is begin process(D, EN) begin if EN = '1' then Q <= D; end if; end process; end dlatch; D Q D Latch EN

D Latch

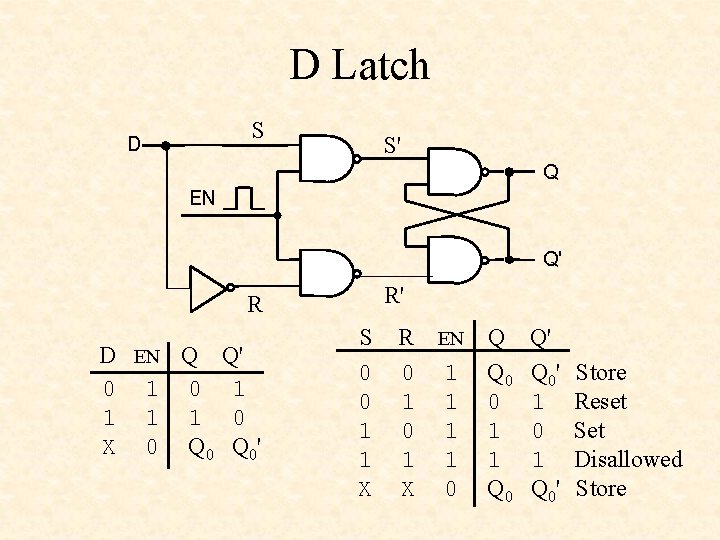

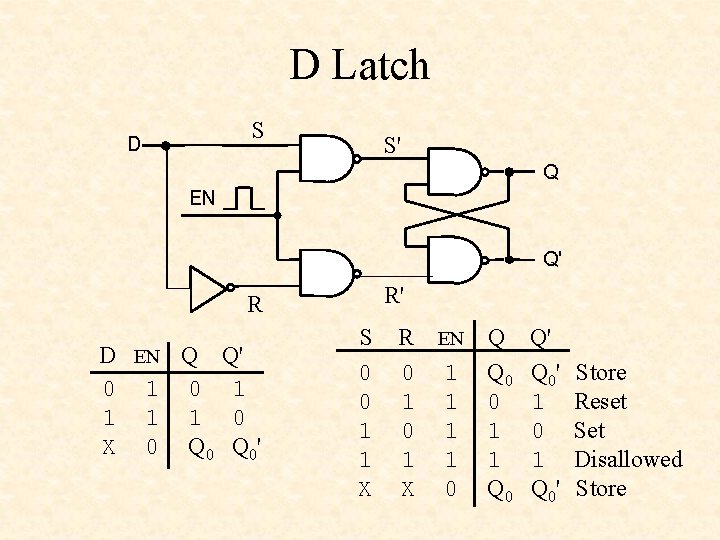

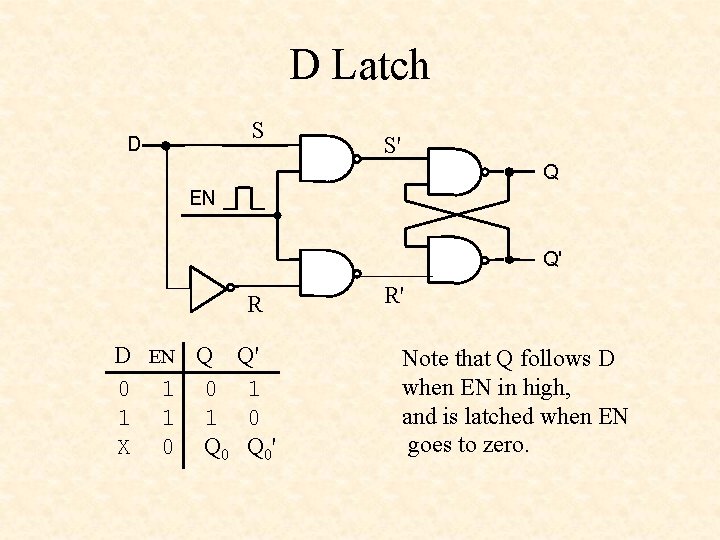

D Latch S D S' Q EN Q' R' R D EN Q 0 1 1 1 X 0 Q' 1 0 Q 0' S 0 0 1 1 X R EN Q 0 1 1 0 0 1 1 1 X 0 Q' Q 0' 1 0 1 Q 0' Store Reset Set Disallowed Store

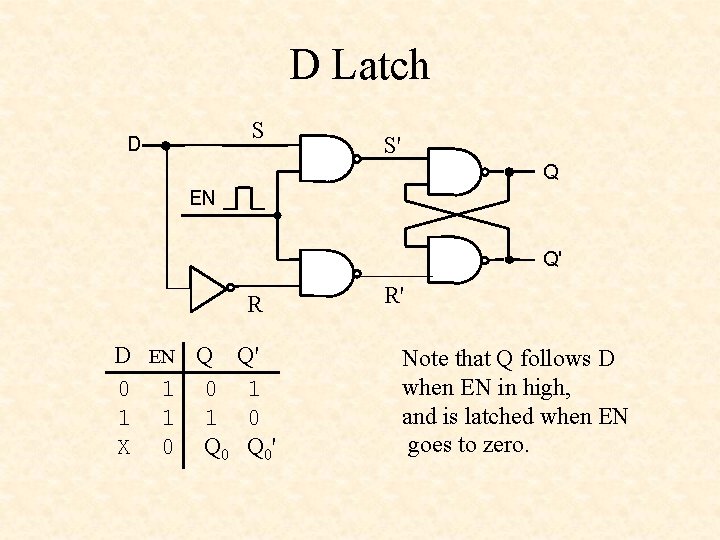

D Latch S D S' Q EN Q' R D EN Q 0 1 1 1 X 0 Q' 1 0 Q 0' R' Note that Q follows D when EN in high, and is latched when EN goes to zero.

Latches and Flip-Flops • Latches – SR Latch – Clocked SR Latch – D Latch • Flip-Flops – Edge-Triggered D Flip-Flop

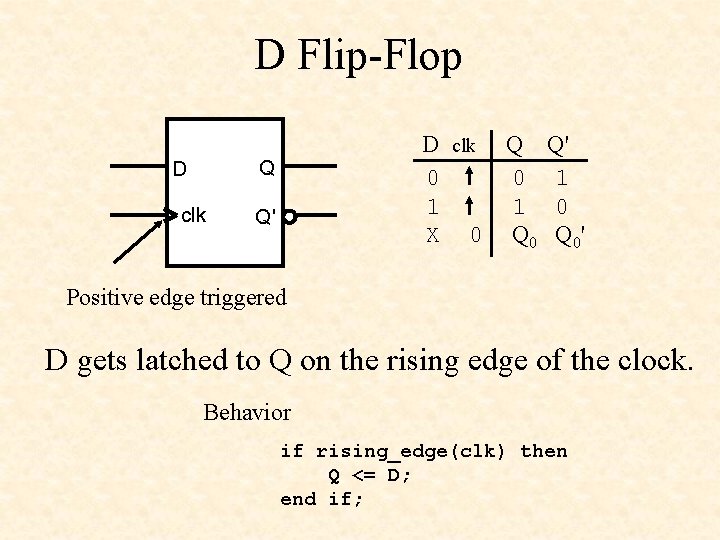

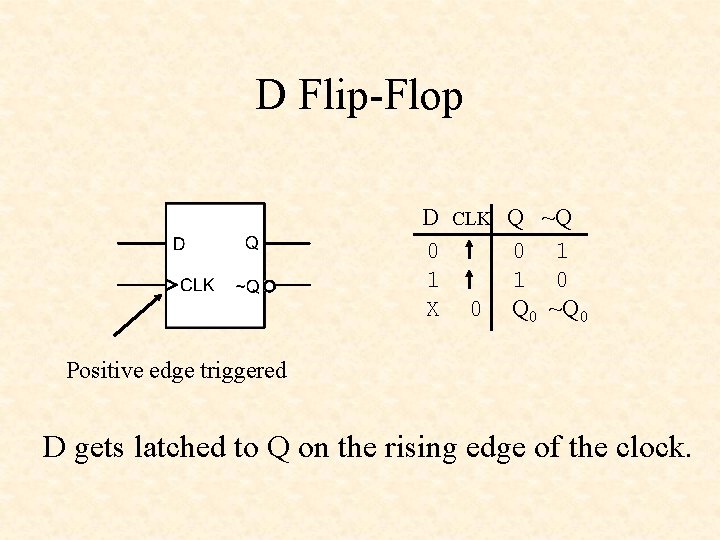

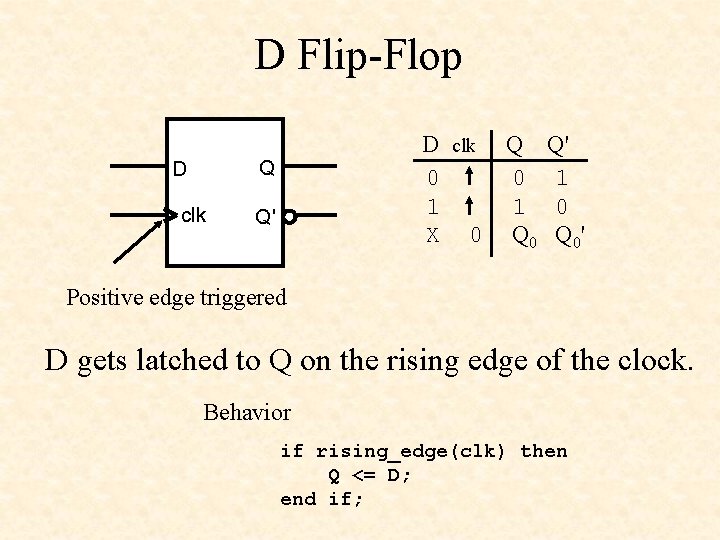

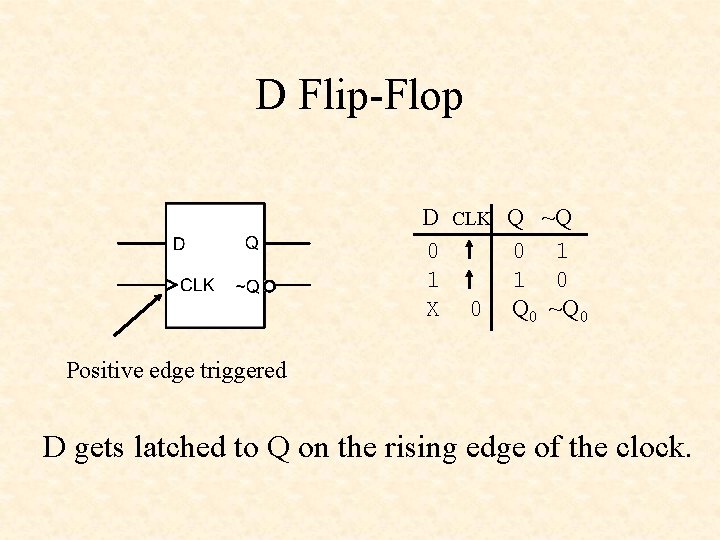

D Flip-Flop D clk Q 0 0 1 1 X 0 Q D clk Q' Q' 1 0 Q 0' Positive edge triggered D gets latched to Q on the rising edge of the clock. Behavior if rising_edge(clk) then Q <= D; end if;

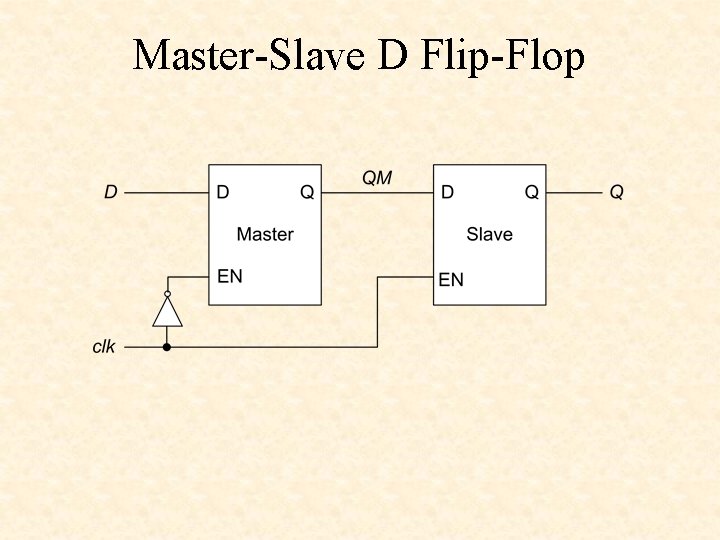

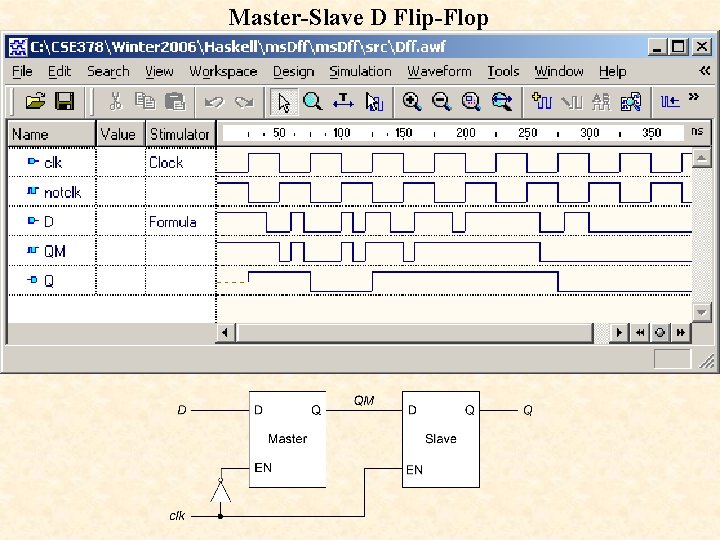

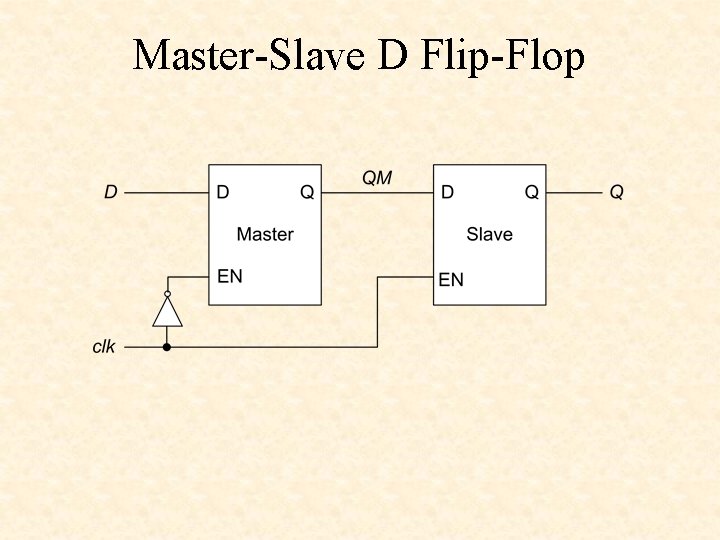

Master-Slave D Flip-Flop

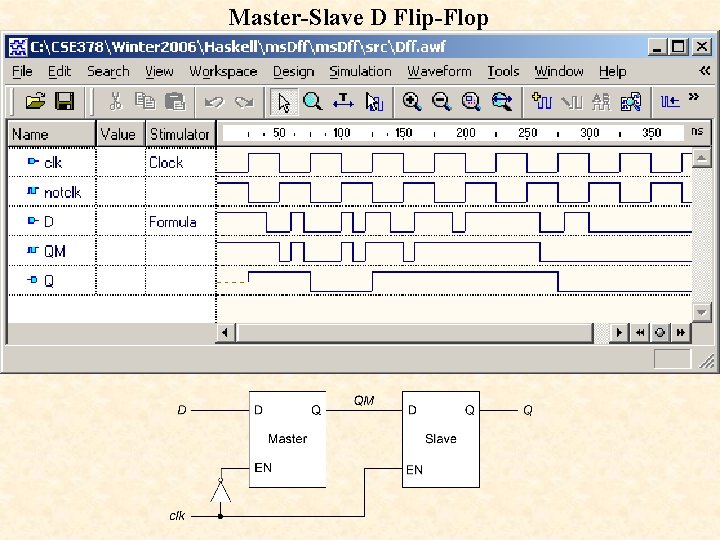

Master-Slave D Flip-Flop

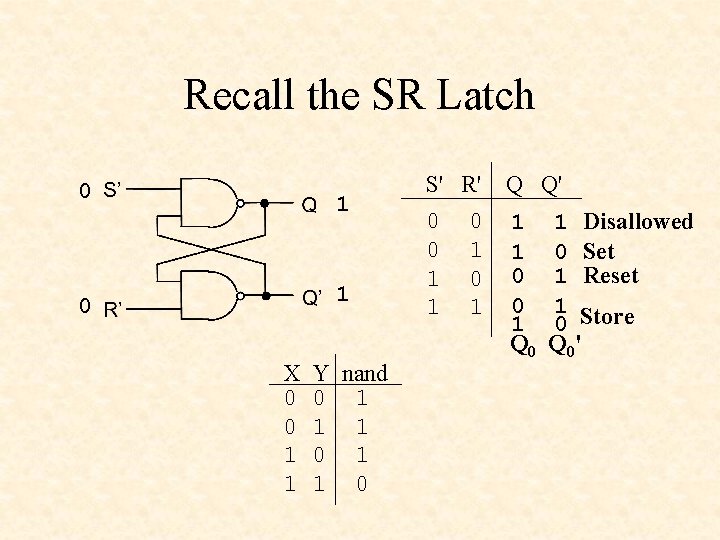

Recall the SR Latch 0 1 1 0 X 0 0 1 1 Y nand 0 1 1 1 0 S' R' Q Q' 0 0 1 1 Disallowed 0 1 1 0 Set 1 0 0 1 Reset 1 1 0 1 Store 1 0 Q 0'

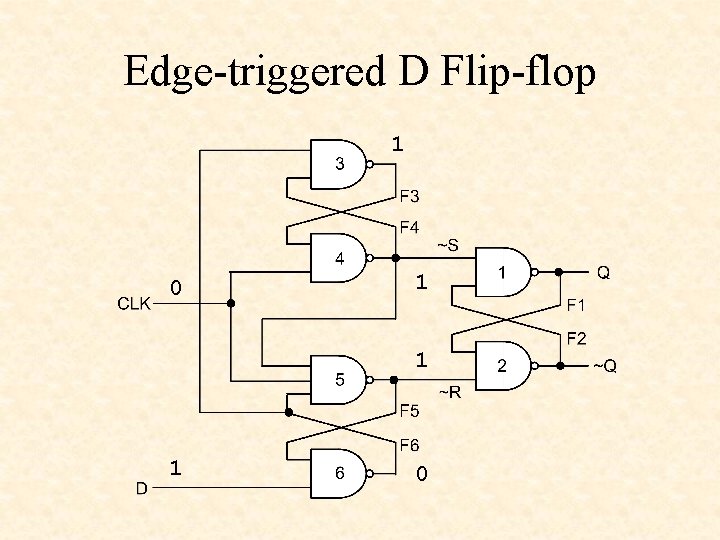

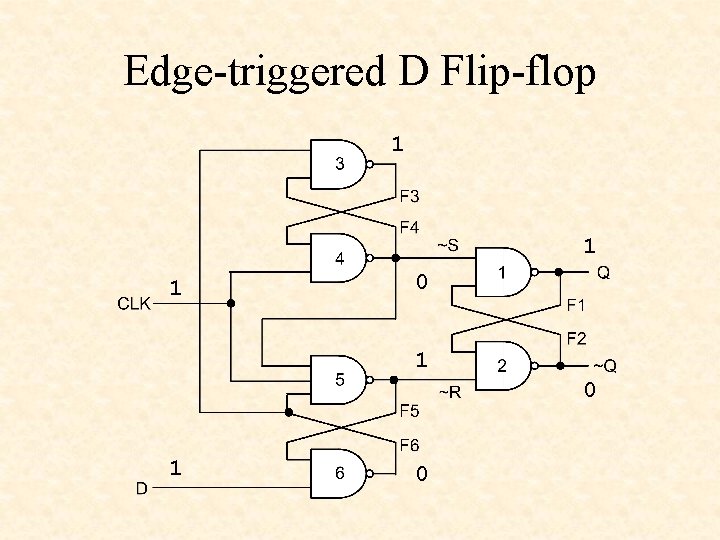

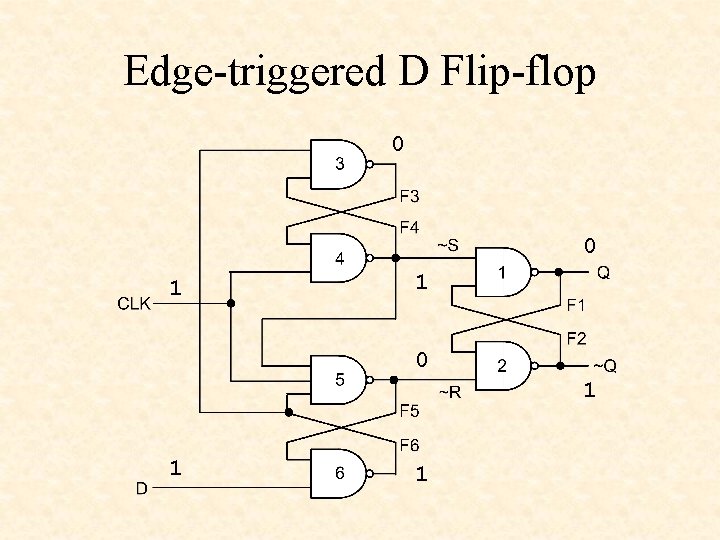

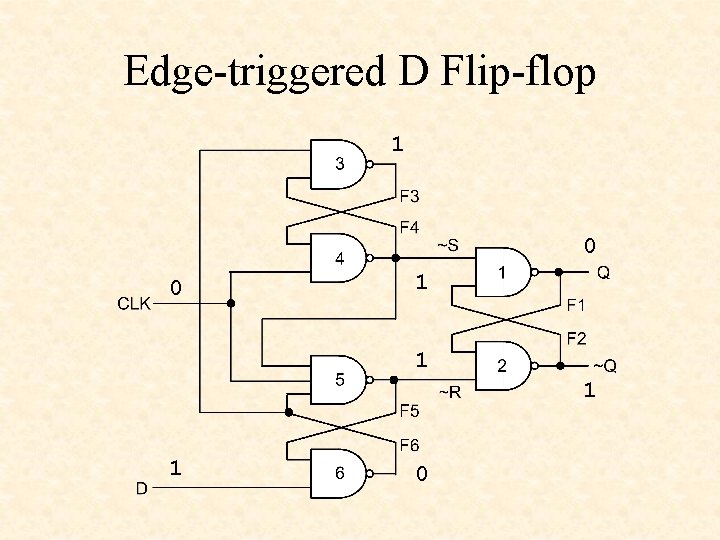

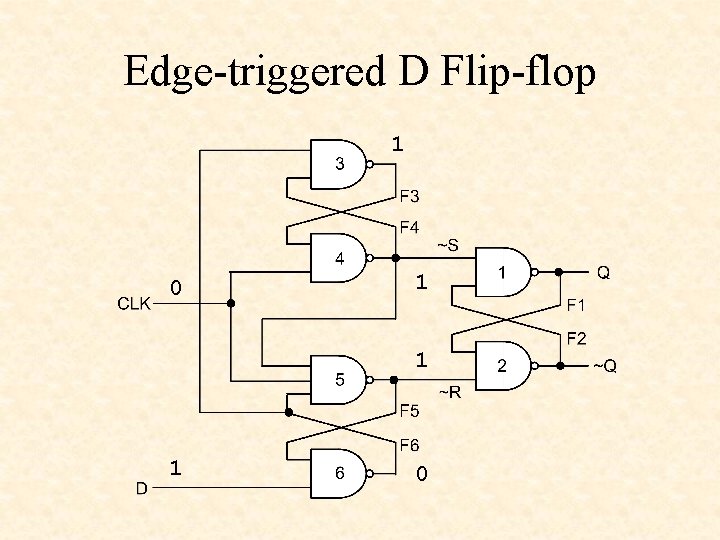

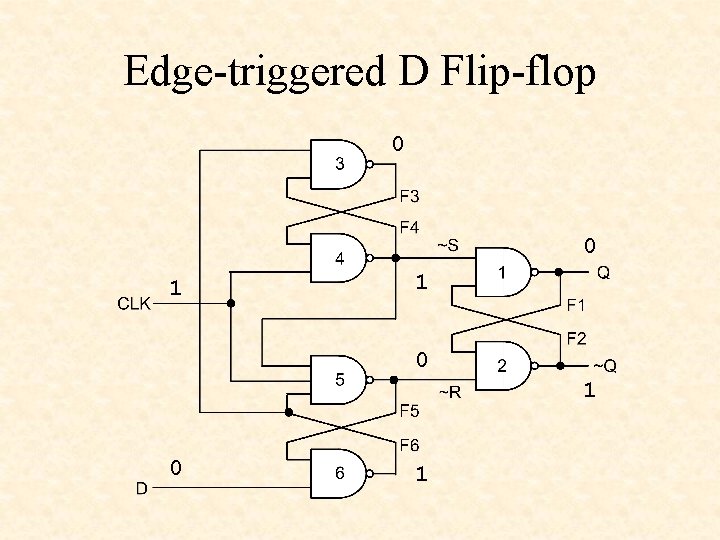

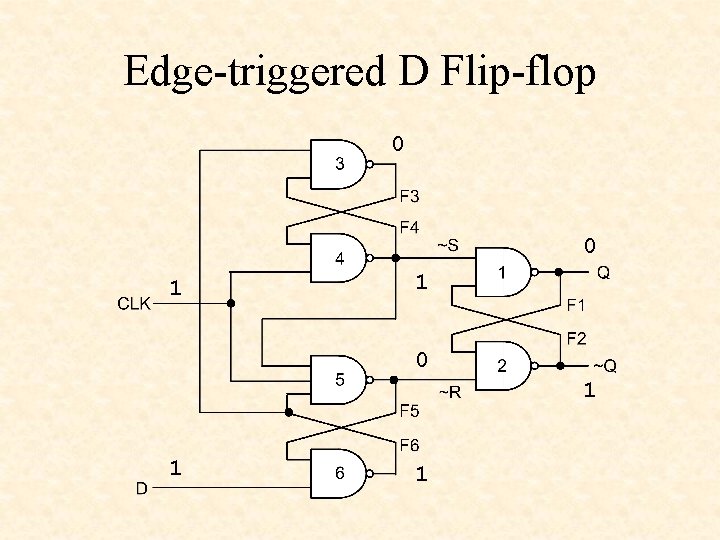

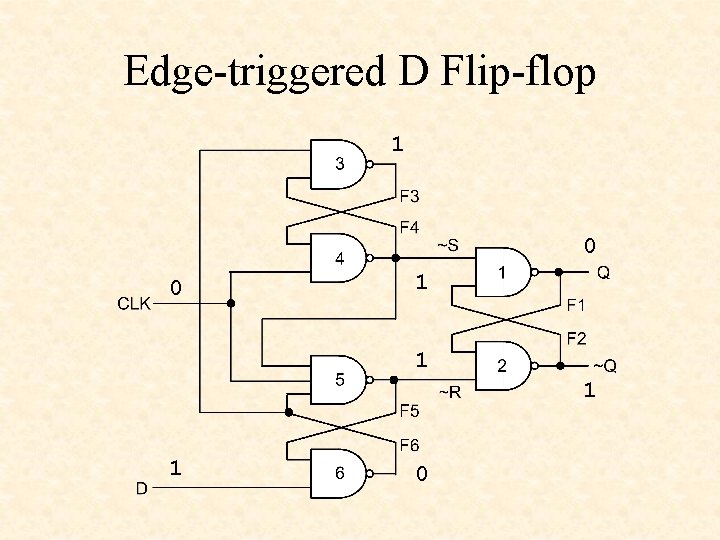

Edge-triggered D Flip-flop 1 0 1 1 1 0

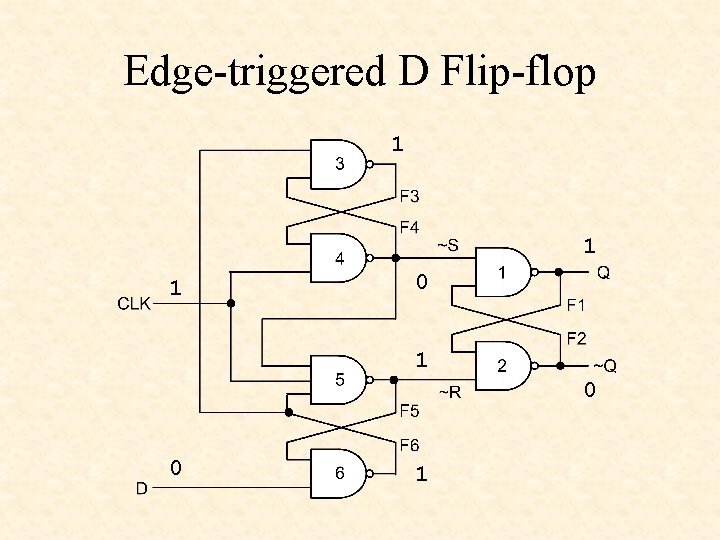

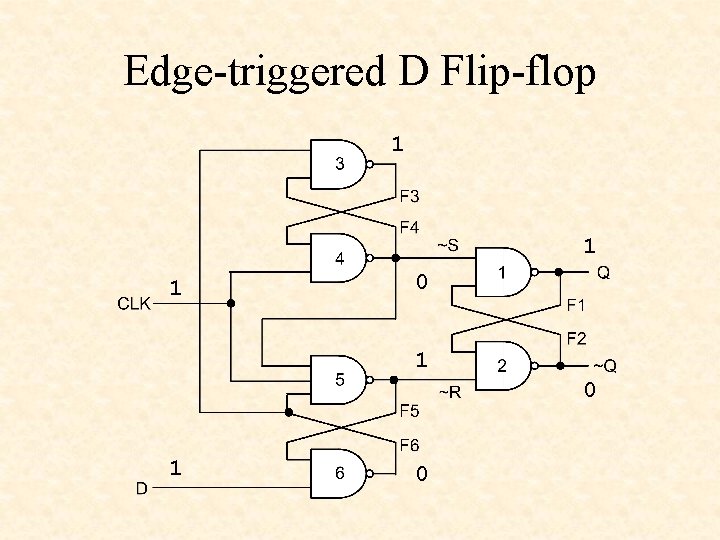

Edge-triggered D Flip-flop 1 1 1 0 1 0

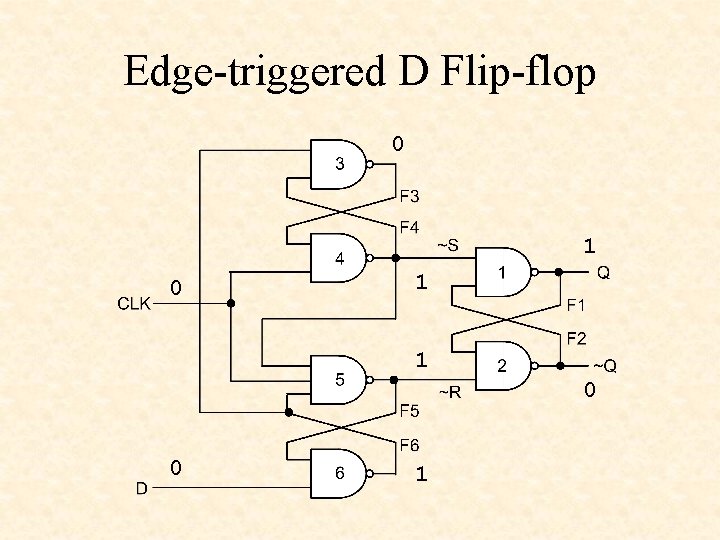

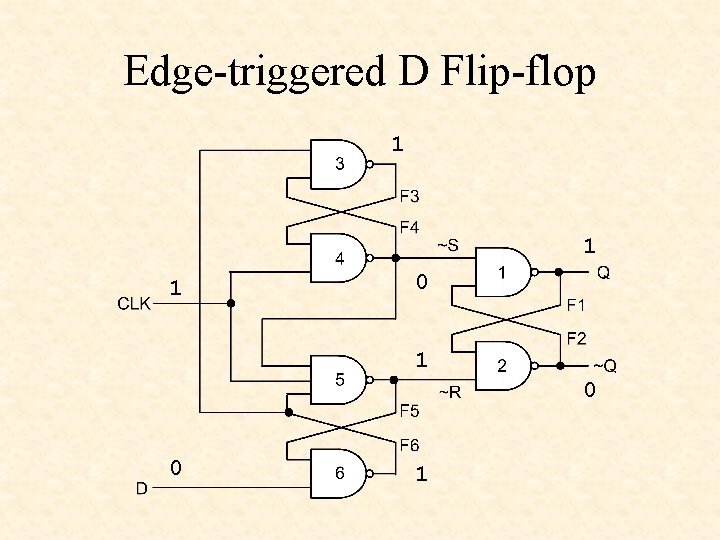

Edge-triggered D Flip-flop 1 1 1 0 0 1

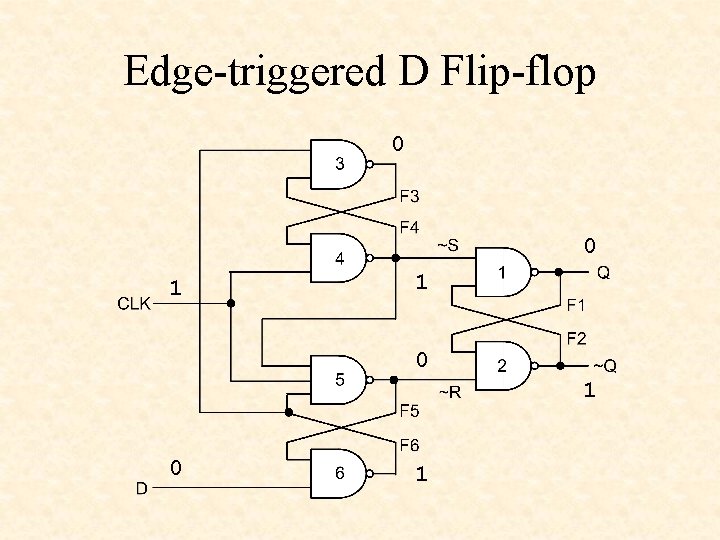

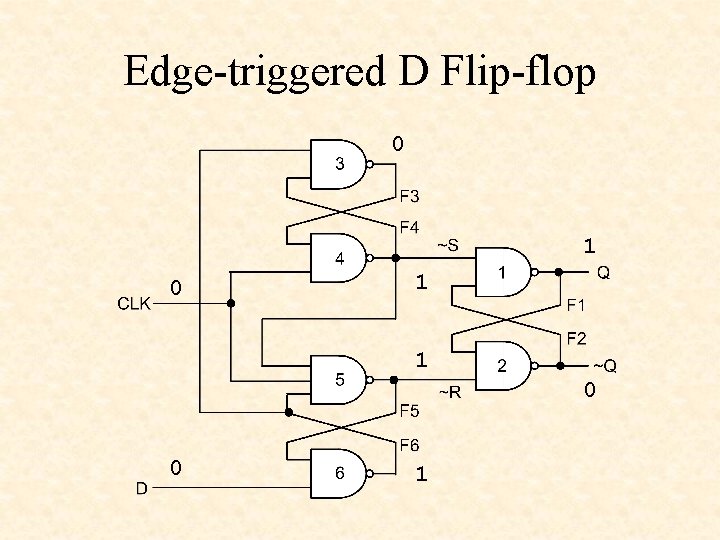

Edge-triggered D Flip-flop 0 1 1 0 0 1

Edge-triggered D Flip-flop 0 0 1 1 0 1

Edge-triggered D Flip-flop 0 0 1 1 1

Edge-triggered D Flip-flop 1 0 0 1 1 0

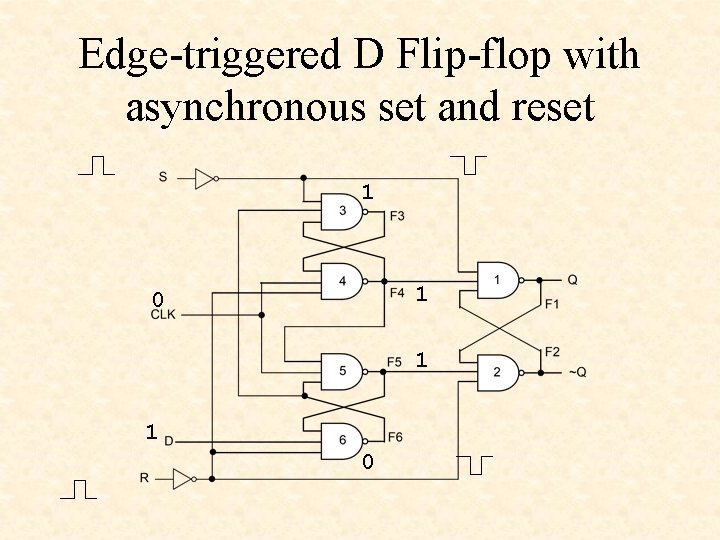

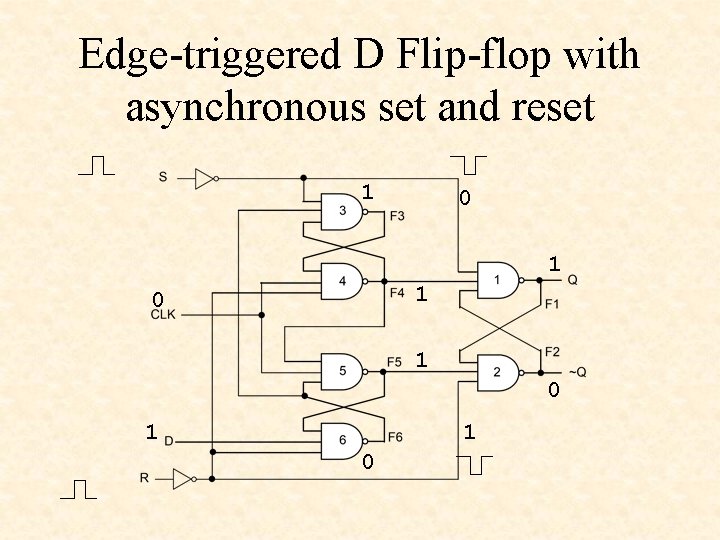

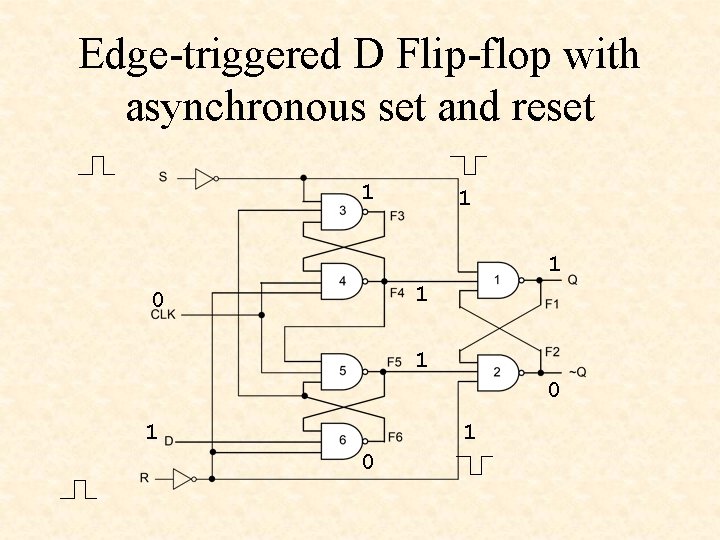

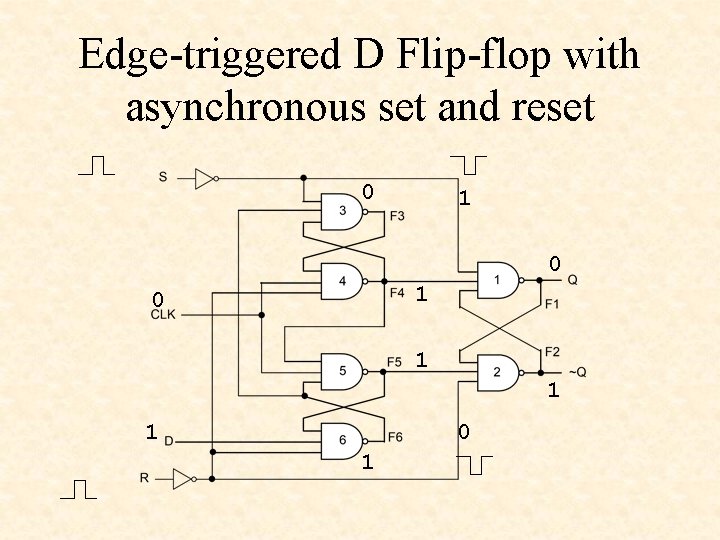

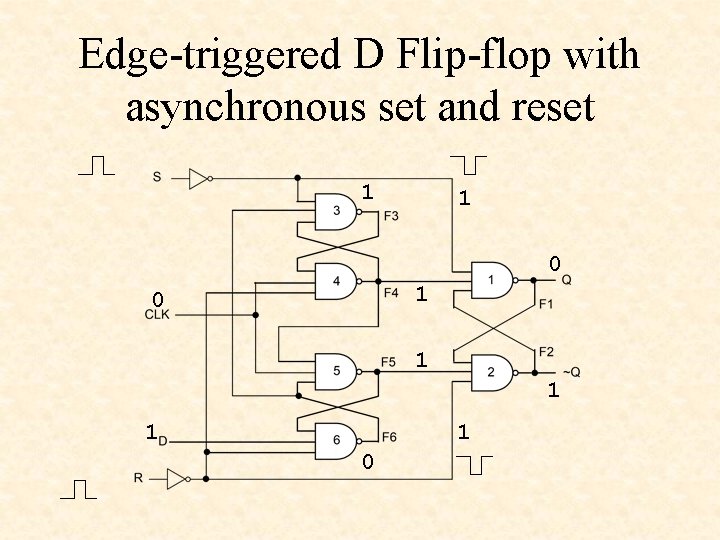

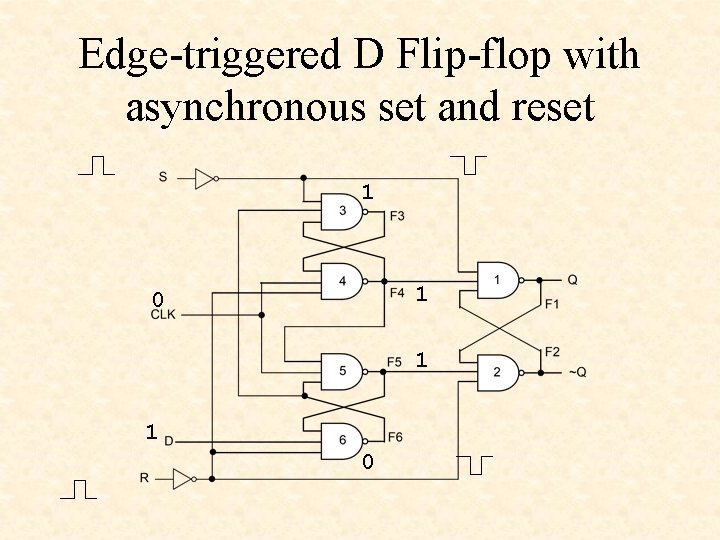

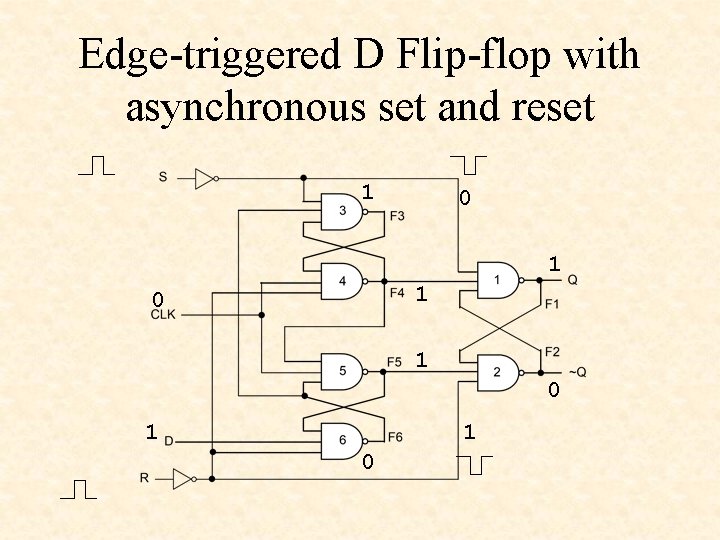

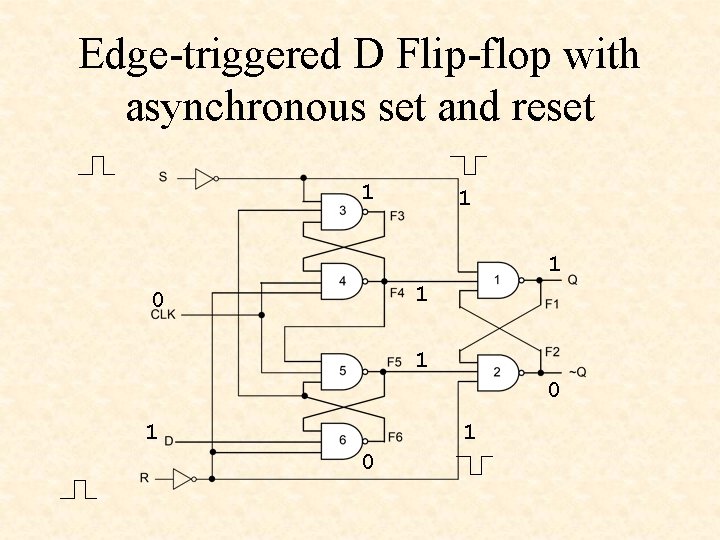

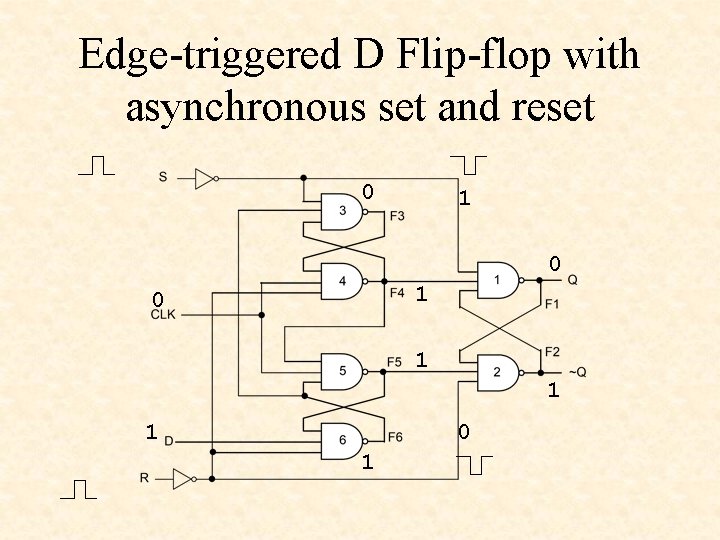

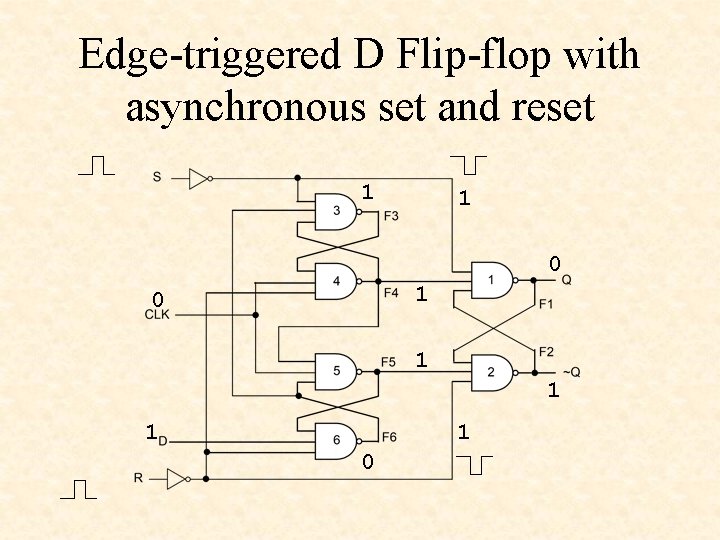

Edge-triggered D Flip-flop with asynchronous set and reset 1 1 0

Edge-triggered D Flip-flop with asynchronous set and reset 1 0 1 1 0

Edge-triggered D Flip-flop with asynchronous set and reset 1 1 0

Edge-triggered D Flip-flop with asynchronous set and reset 0 1 0 1 1 1 0 1

Edge-triggered D Flip-flop with asynchronous set and reset 1 1 0

D Flip-Flop D CLK Q ~Q 0 0 1 1 1 0 X 0 Q 0 ~Q 0 Positive edge triggered D gets latched to Q on the rising edge of the clock.

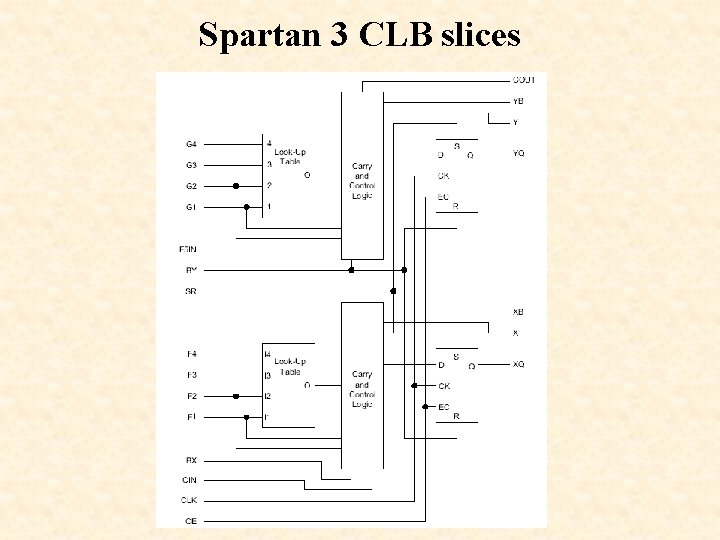

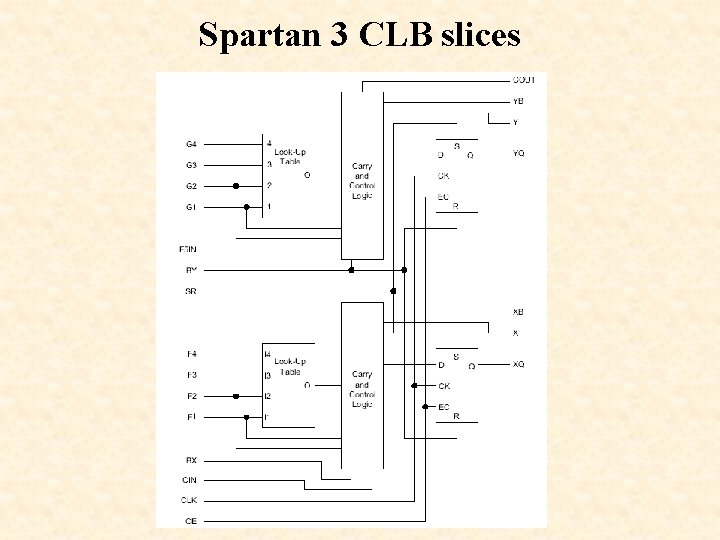

Spartan 3 CLB slices