LargeScale WireSpeed Packet Classification on FPGAs Author Weirong

- Slides: 18

Large-Scale Wire-Speed Packet Classification on FPGAs Author: Weirong Jiang, Viktor K. Prasanna Publisher: FPGA 2009 Presenter: Chung-Yi Lee

Outline o Architecture and Algorithm n Algorithmic Motivations n Architecture Overview n Algorithm o Implementation o Experimental Results 2

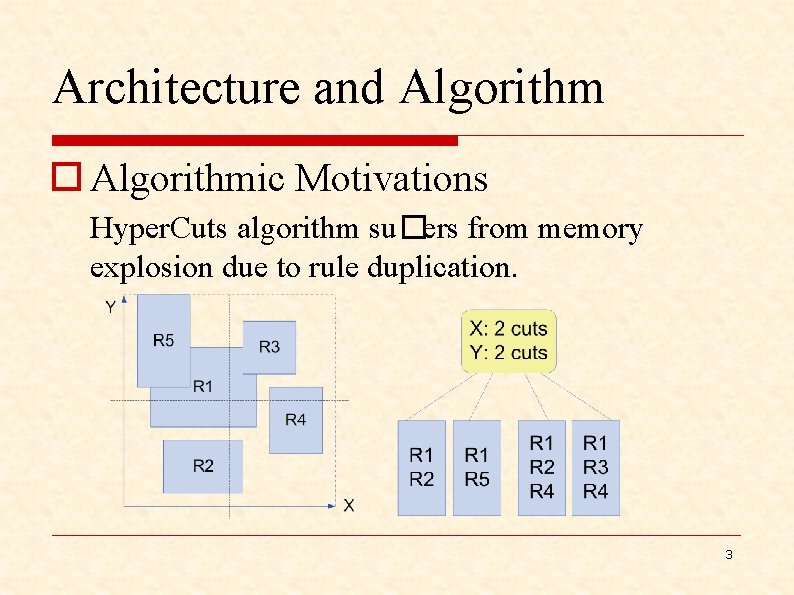

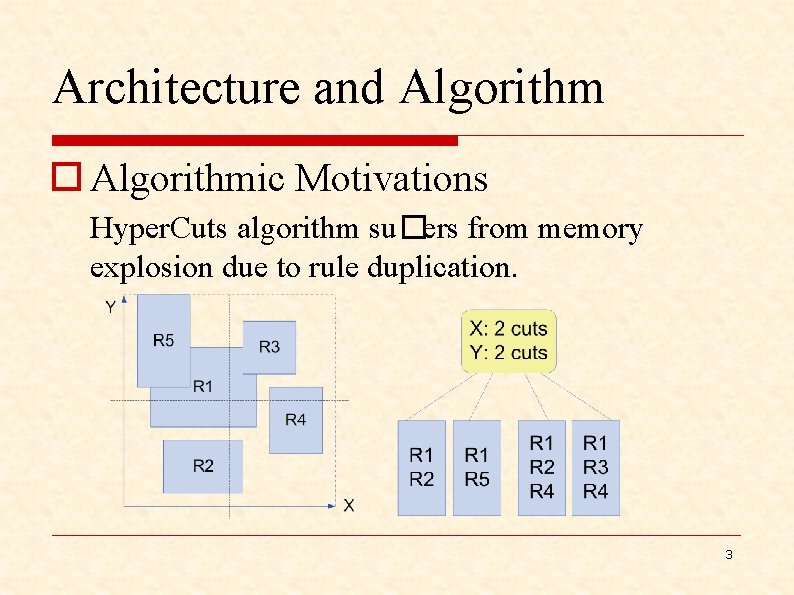

Architecture and Algorithm o Algorithmic Motivations Hyper. Cuts algorithm su�ers from memory explosion due to rule duplication. 3

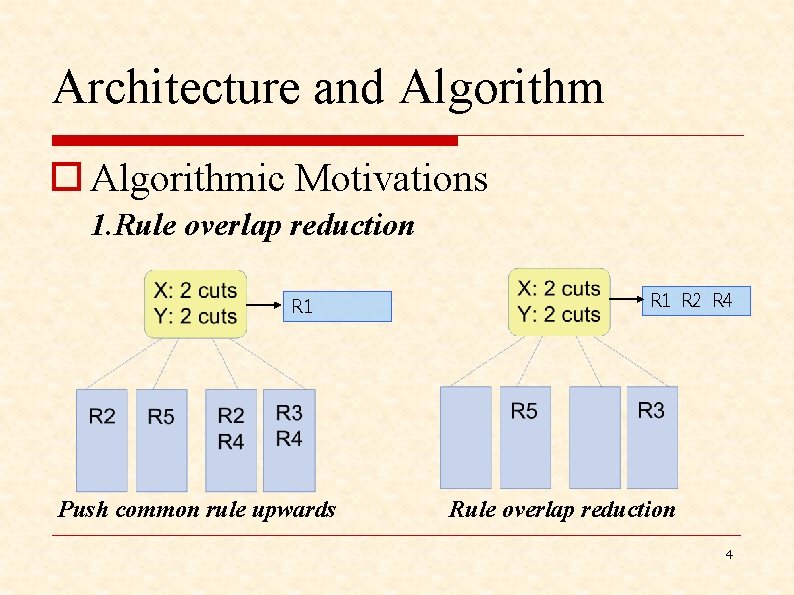

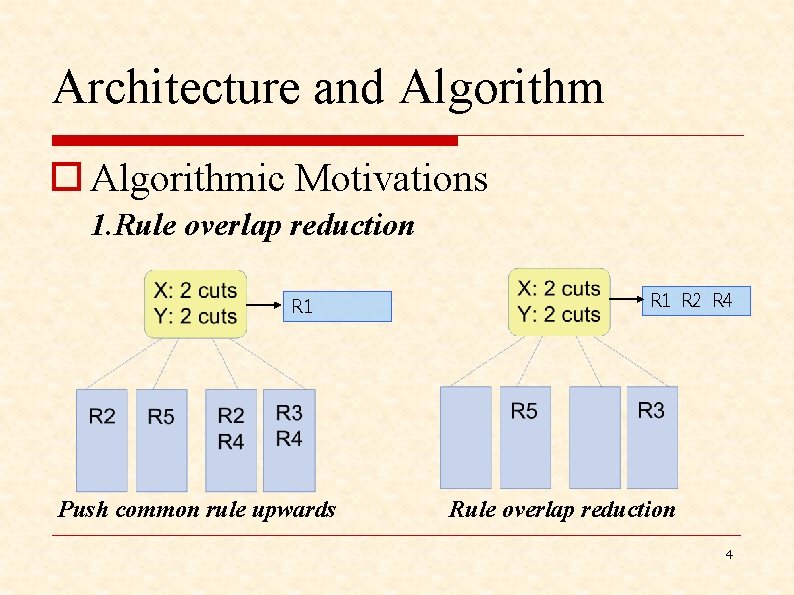

Architecture and Algorithm o Algorithmic Motivations 1. Rule overlap reduction R 1 Push common rule upwards R 1 R 2 R 4 Rule overlap reduction 4

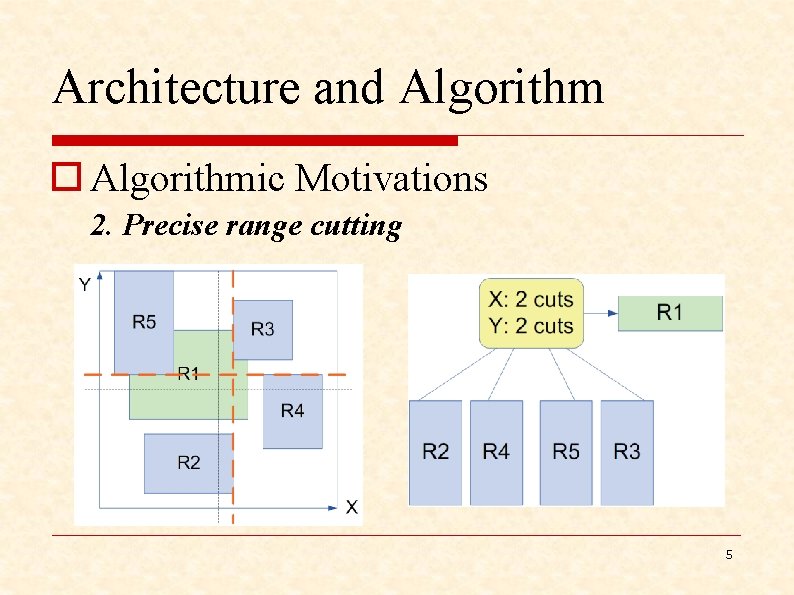

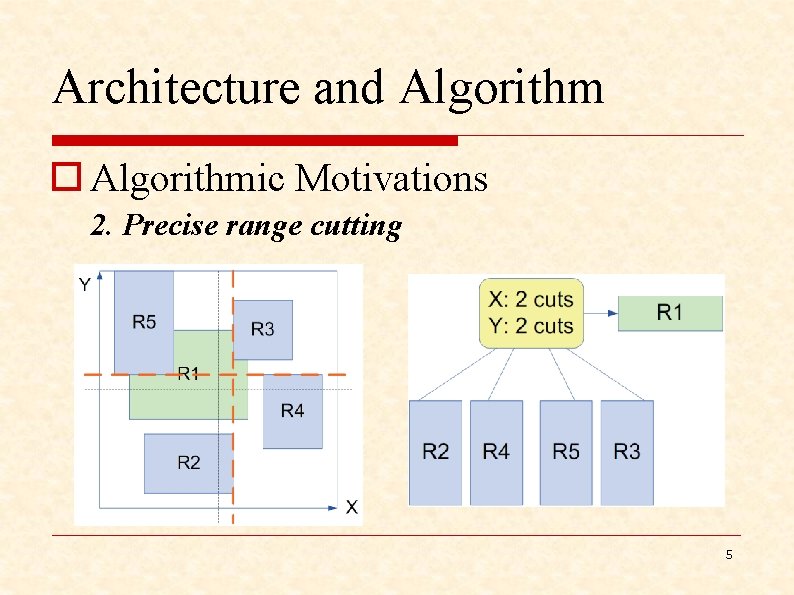

Architecture and Algorithm o Algorithmic Motivations 2. Precise range cutting 5

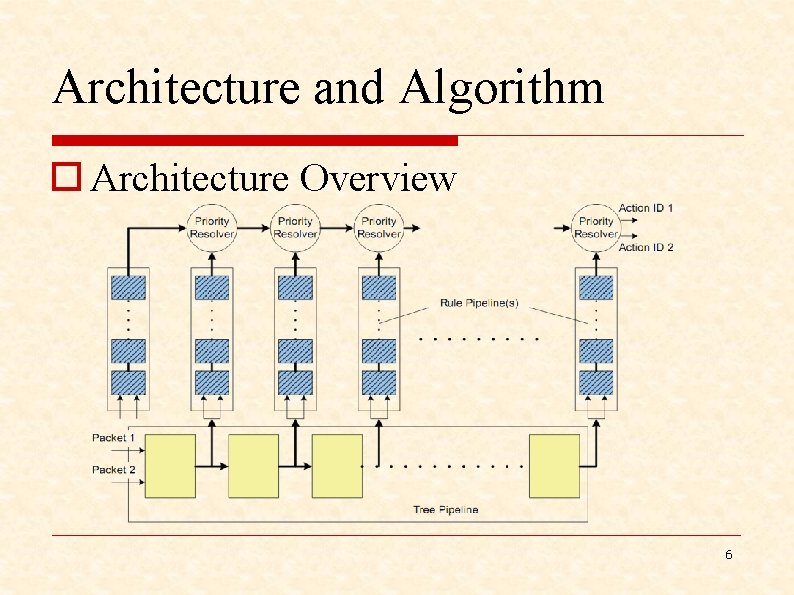

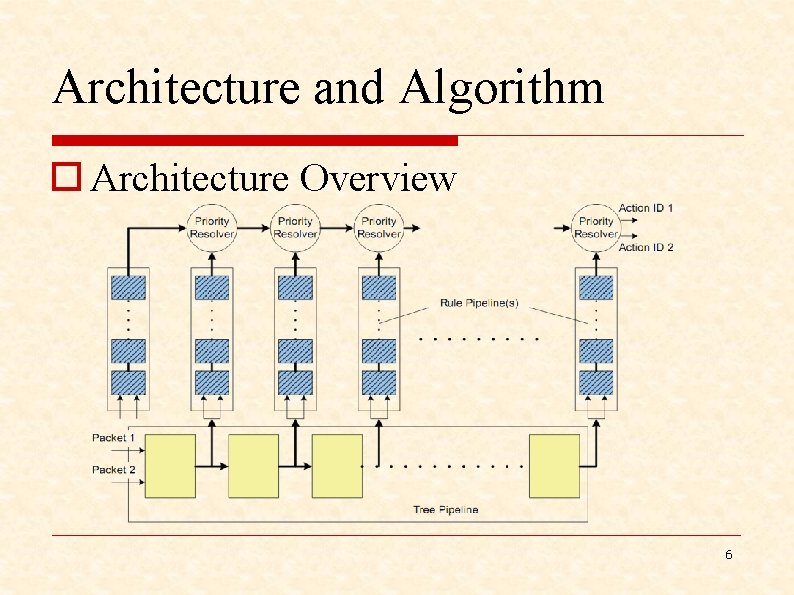

Architecture and Algorithm o Architecture Overview 6

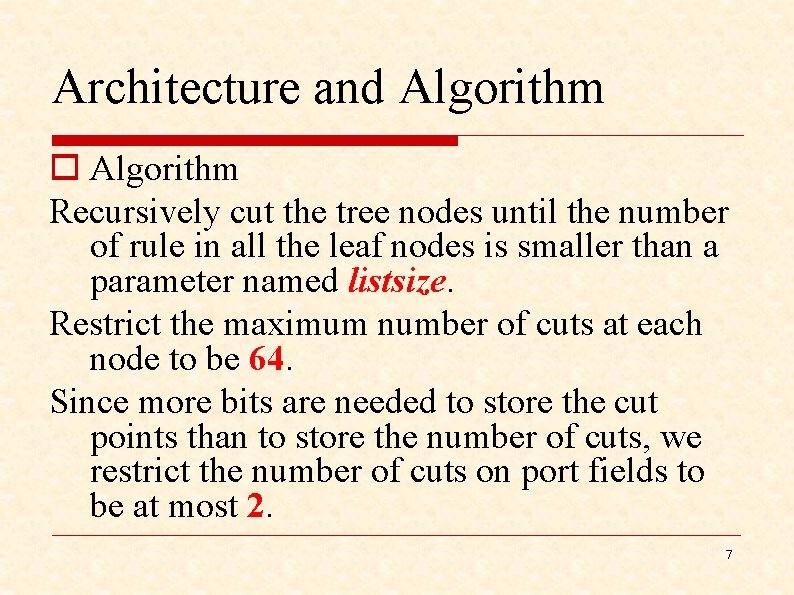

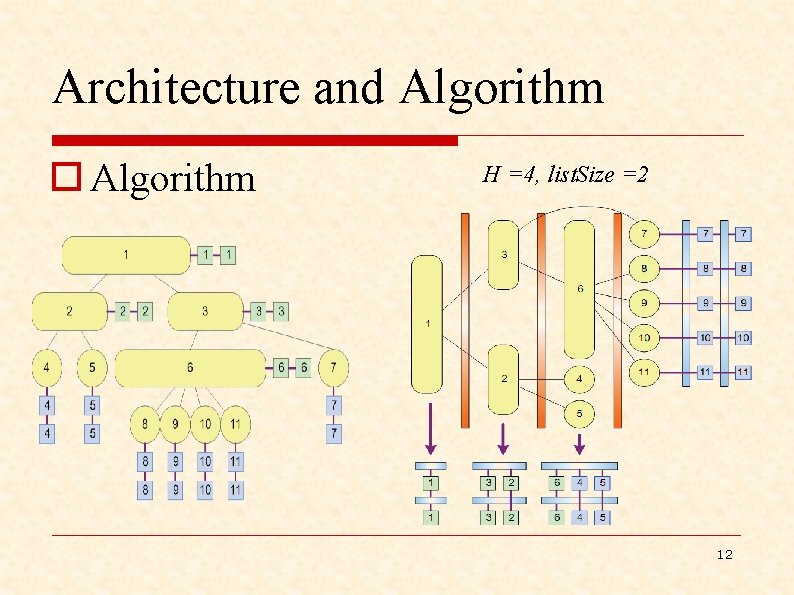

Architecture and Algorithm o Algorithm Recursively cut the tree nodes until the number of rule in all the leaf nodes is smaller than a parameter named listsize. Restrict the maximum number of cuts at each node to be 64. Since more bits are needed to store the cut points than to store the number of cuts, we restrict the number of cuts on port fields to be at most 2. 7

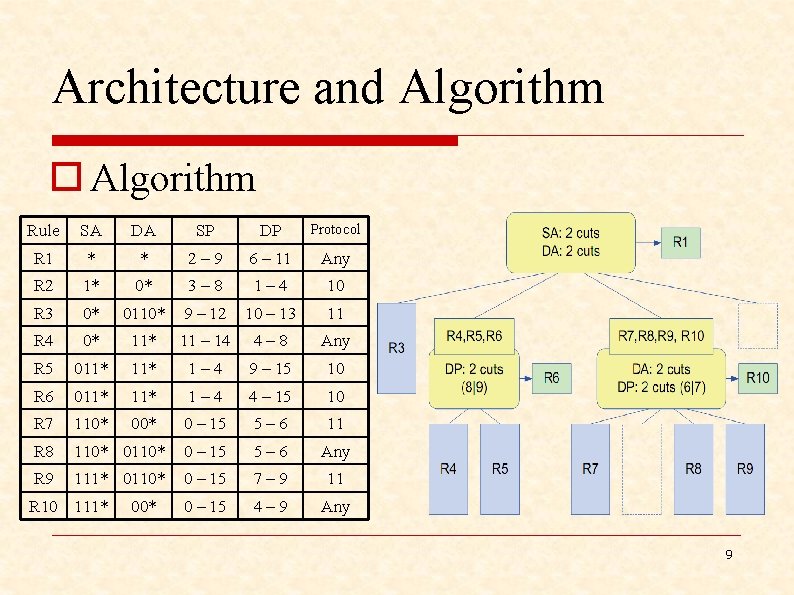

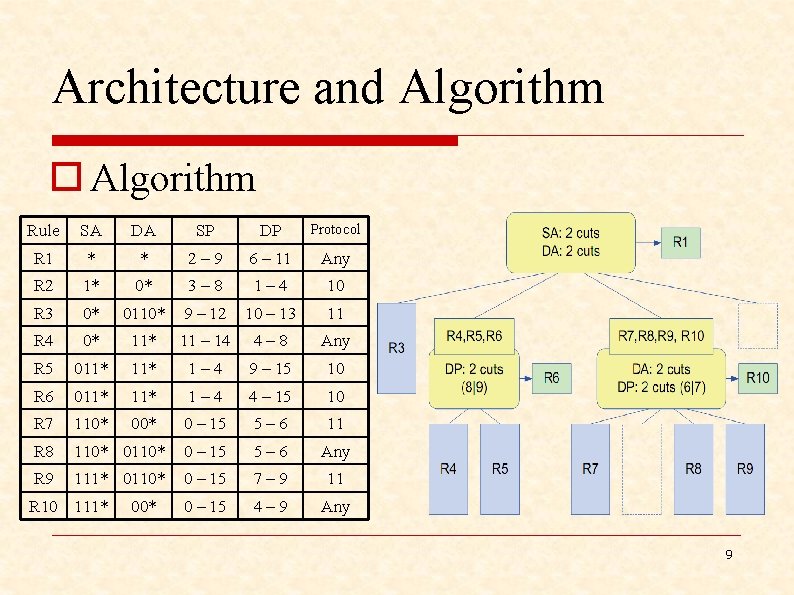

Architecture and Algorithm o Algorithm Rule SA DA SP DP Protocol R 1 * * 2– 9 6 – 11 Any R 2 1* 0* 3– 8 1– 4 10 R 3 0* 0110* 9 – 12 10 – 13 11 R 4 0* 11 – 14 4– 8 Any R 5 011* 1– 4 9 – 15 10 R 6 011* 1– 4 4 – 15 10 R 7 110* 0 – 15 5– 6 11 R 8 110* 0 – 15 5– 6 Any R 9 111* 0110* 0 – 15 7– 9 11 0 – 15 4– 9 Any R 10 111* 00* 9

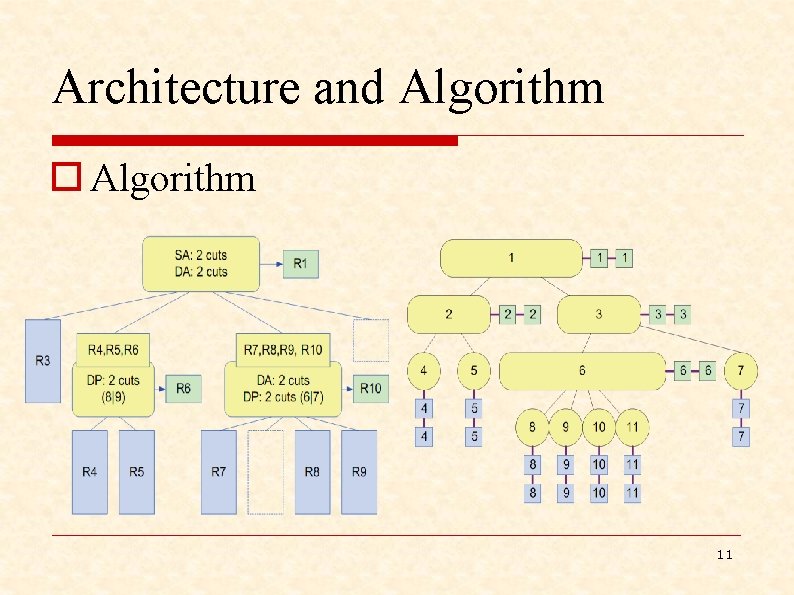

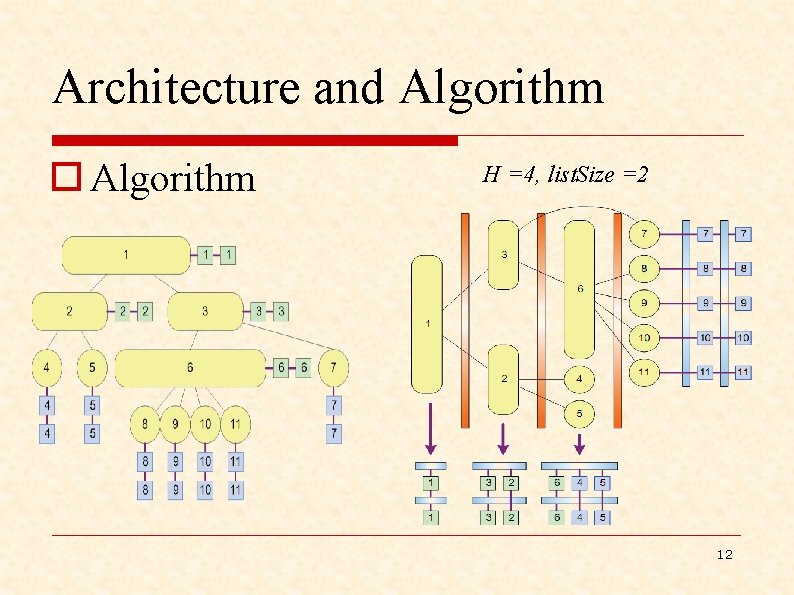

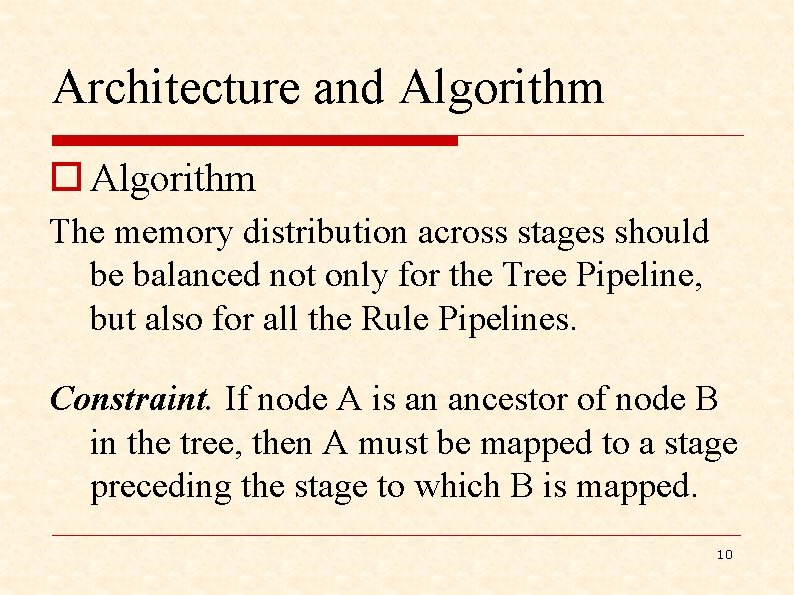

Architecture and Algorithm o Algorithm The memory distribution across stages should be balanced not only for the Tree Pipeline, but also for all the Rule Pipelines. Constraint. If node A is an ancestor of node B in the tree, then A must be mapped to a stage preceding the stage to which B is mapped. 10

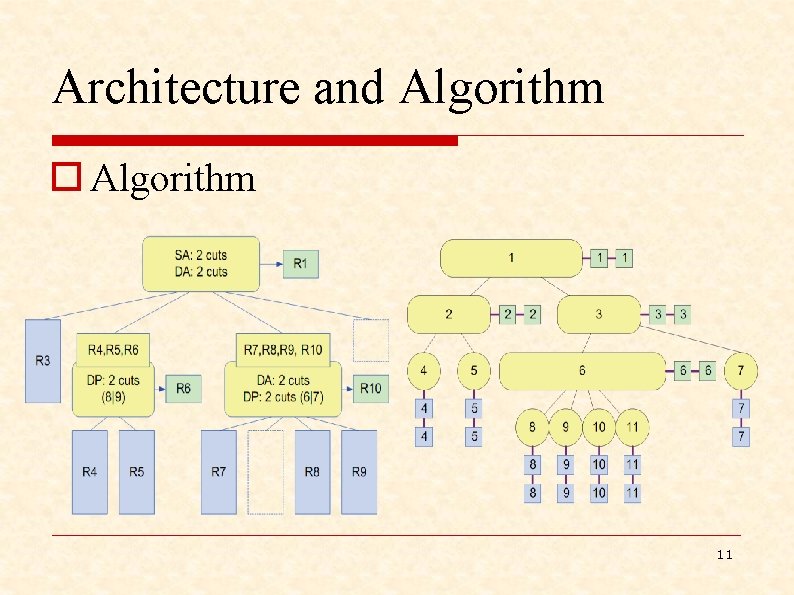

Architecture and Algorithm o Algorithm 11

Architecture and Algorithm o Algorithm H =4, list. Size =2 12

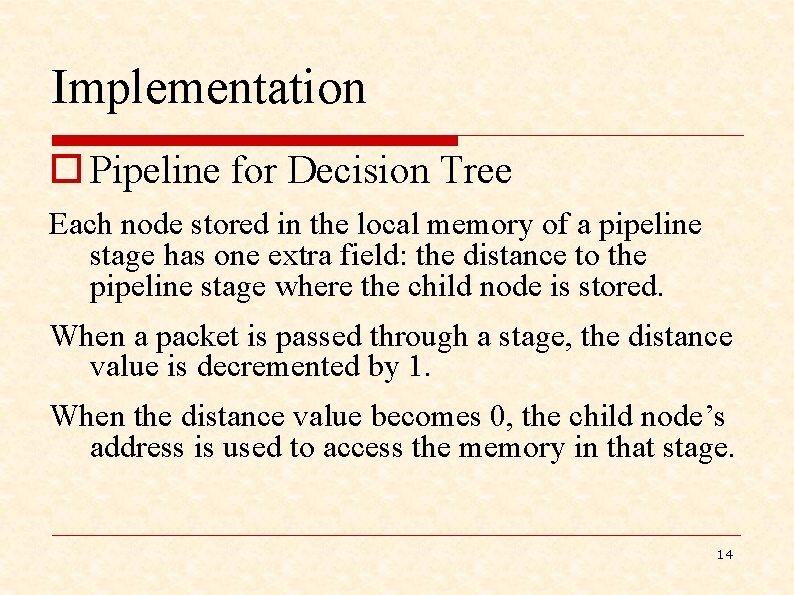

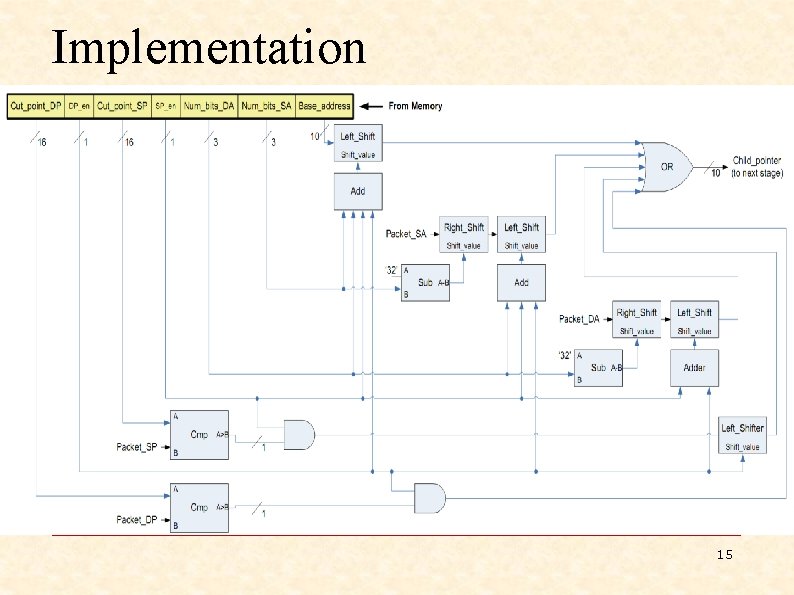

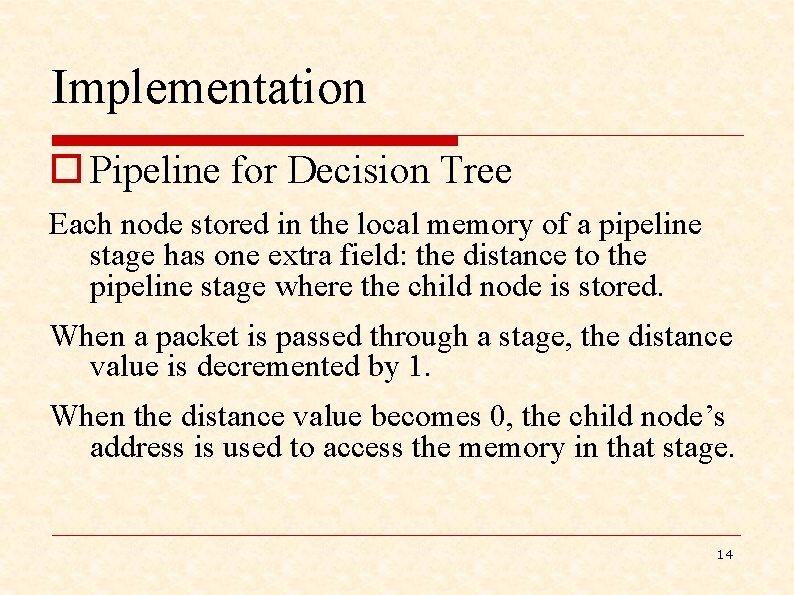

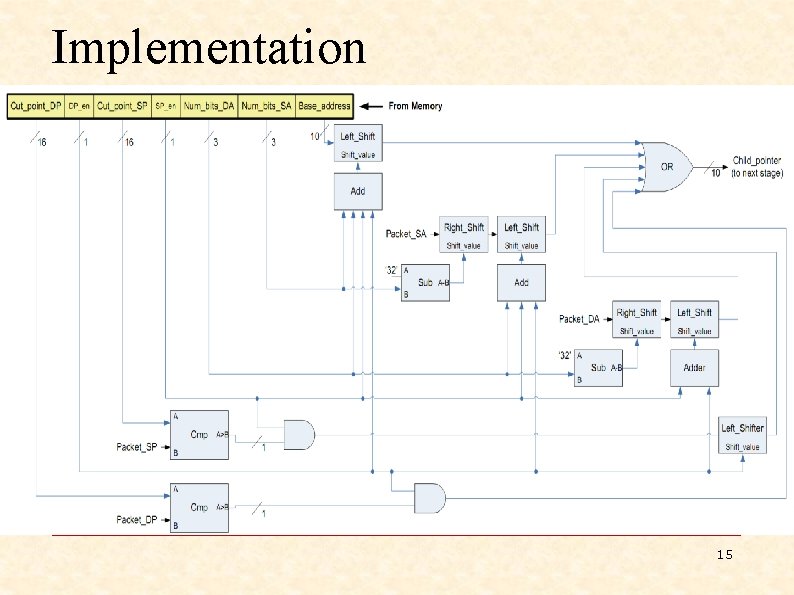

Implementation o Pipeline for Decision Tree Each node stored in the local memory of a pipeline stage has one extra field: the distance to the pipeline stage where the child node is stored. When a packet is passed through a stage, the distance value is decremented by 1. When the distance value becomes 0, the child node’s address is used to access the memory in that stage. 14

Implementation 15

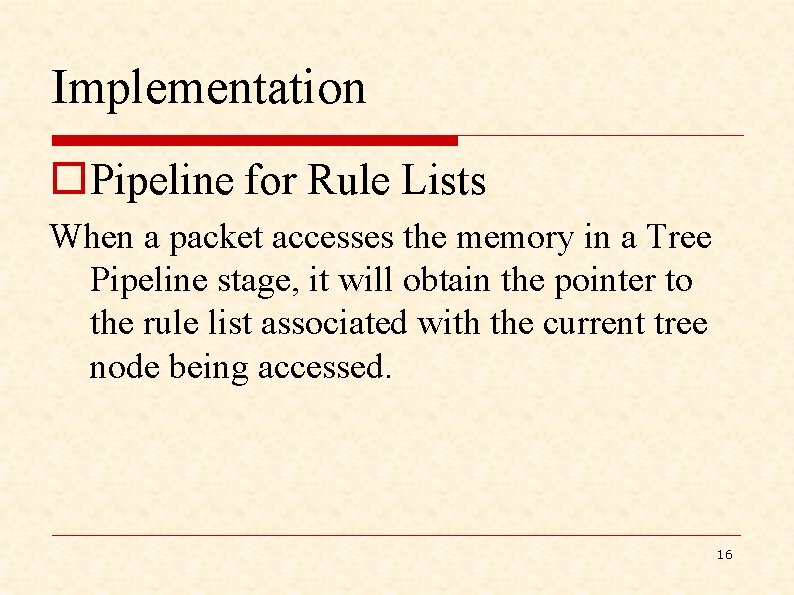

Implementation o. Pipeline for Rule Lists When a packet accesses the memory in a Tree Pipeline stage, it will obtain the pointer to the rule list associated with the current tree node being accessed. 16

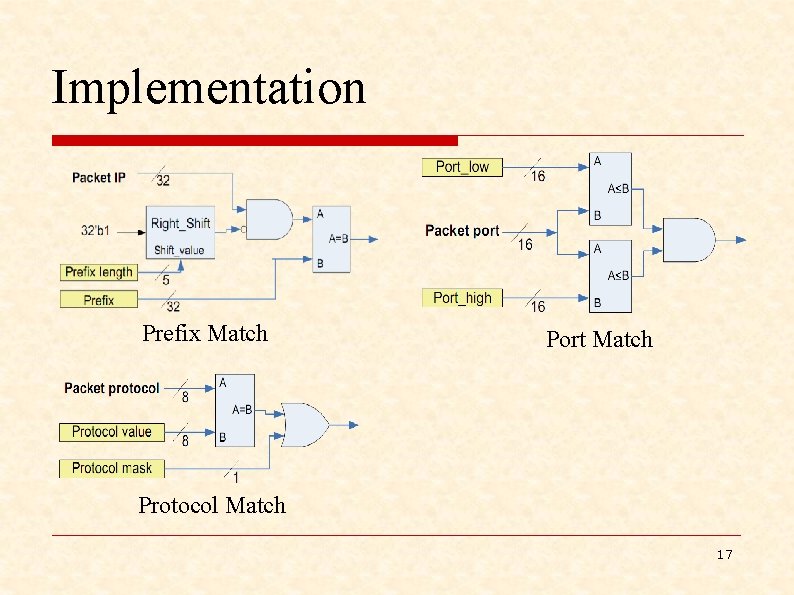

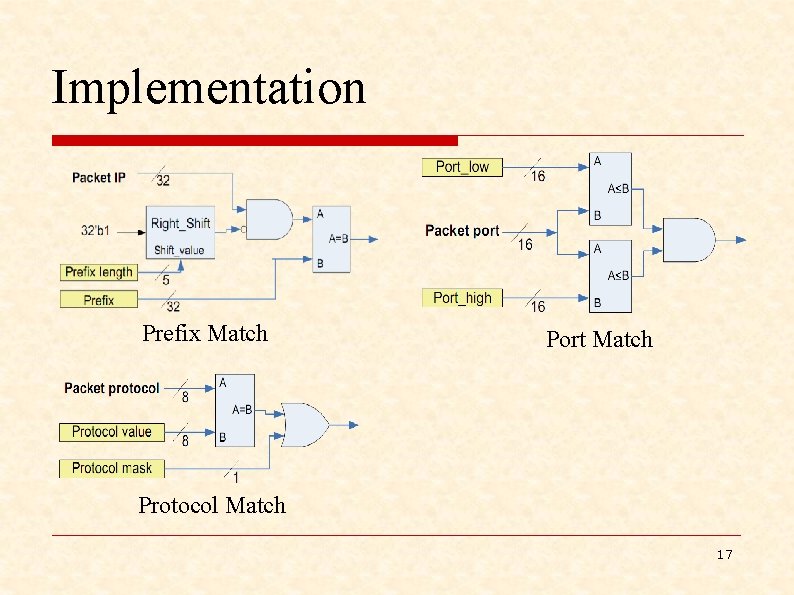

Implementation Prefix Match Port Match Protocol Match 17

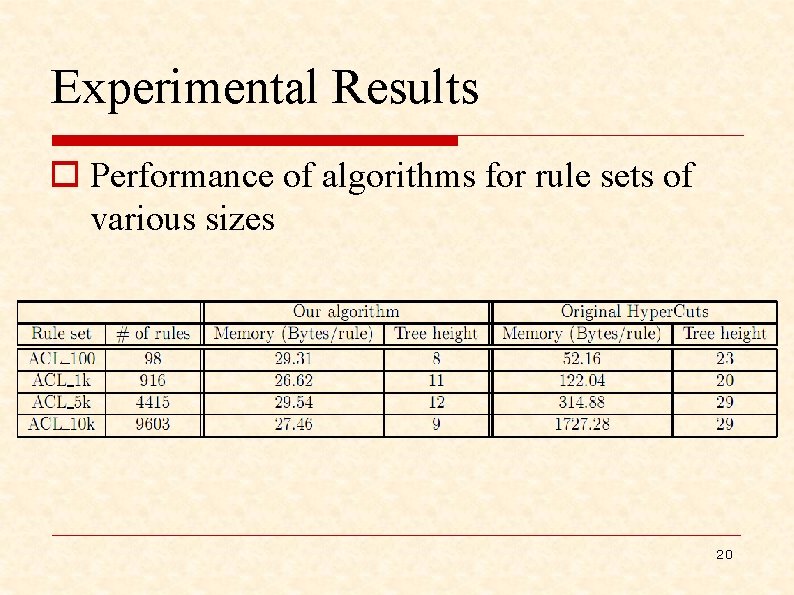

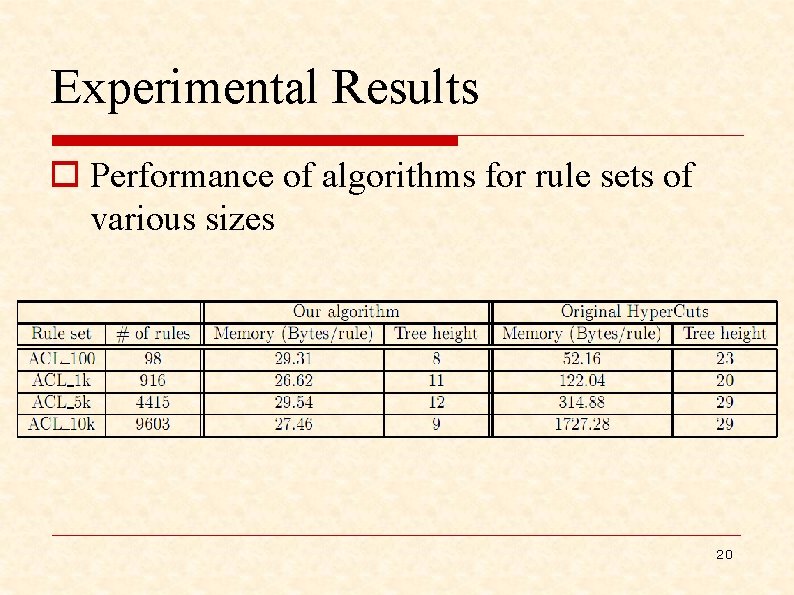

Experimental Results o Performance of algorithms for rule sets of various sizes 20

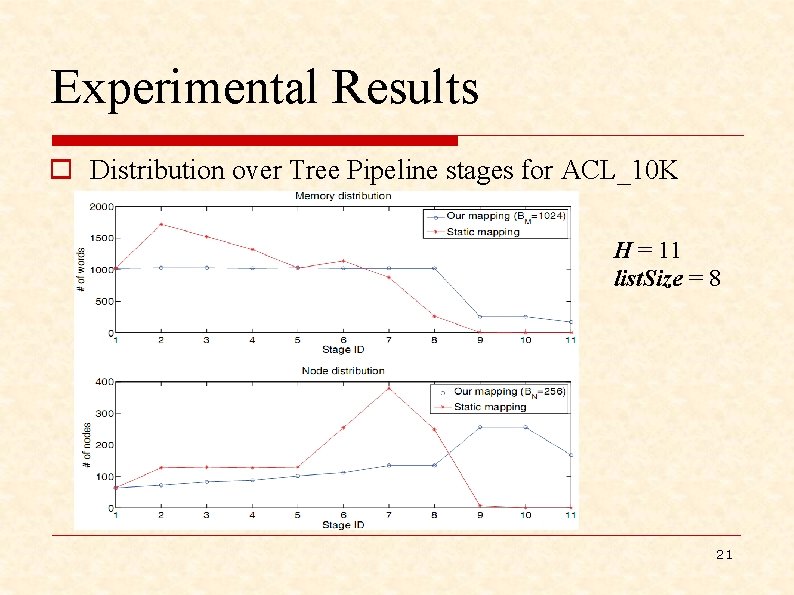

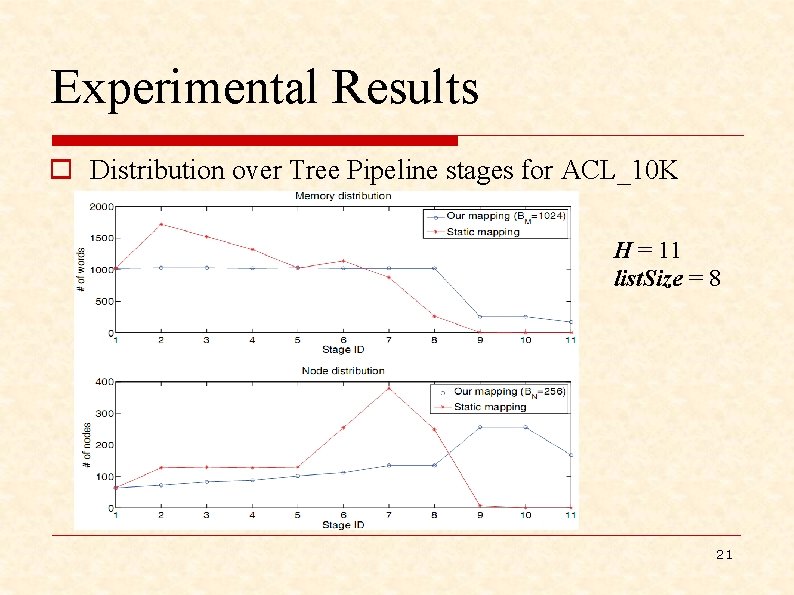

Experimental Results o Distribution over Tree Pipeline stages for ACL_10 K H = 11 list. Size = 8 21

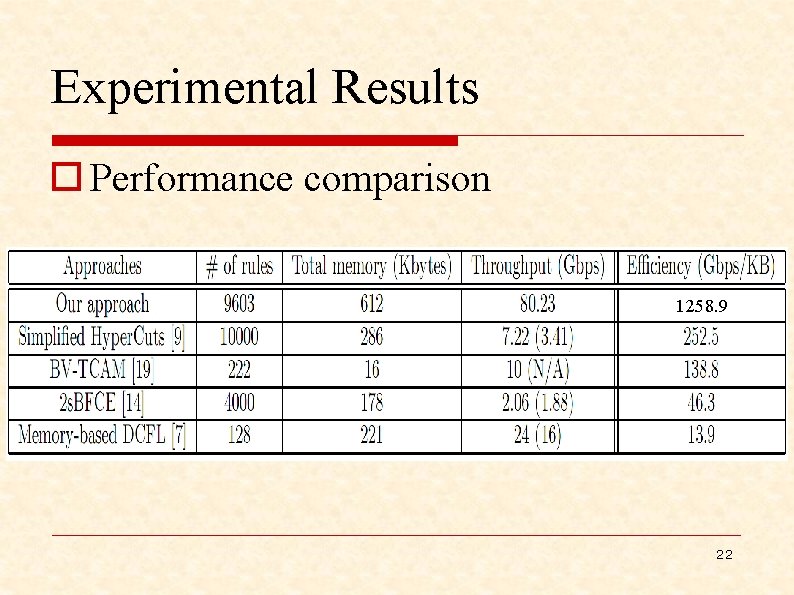

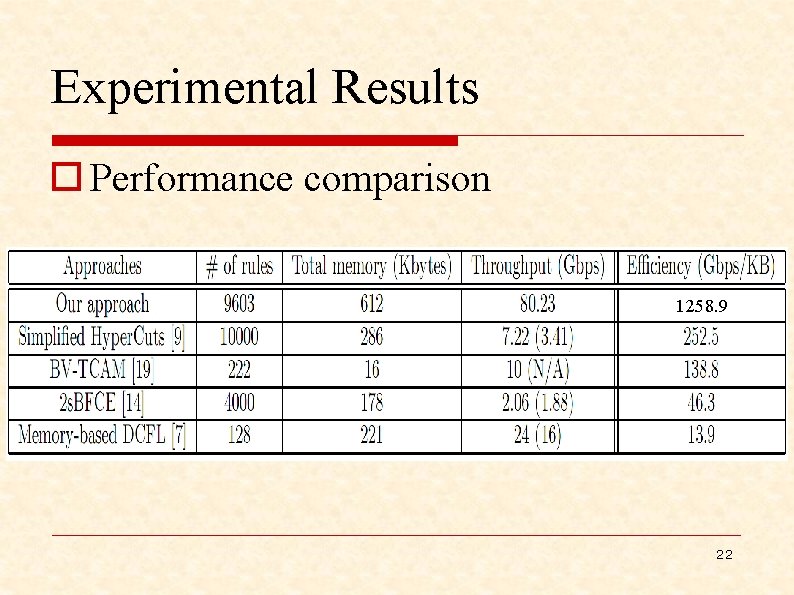

Experimental Results o Performance comparison 1258. 9 22