LargeScale SRAM Variability Characterization Chip in 45 nm

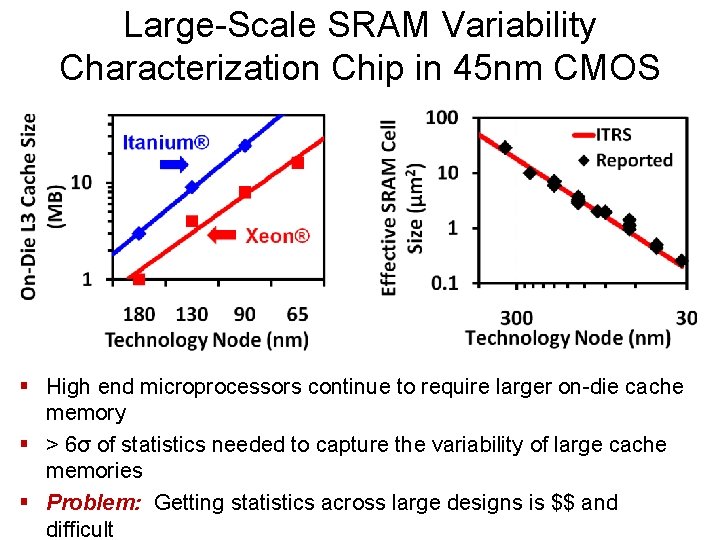

Large-Scale SRAM Variability Characterization Chip in 45 nm CMOS § High end microprocessors continue to require larger on-die cache memory § > 6σ of statistics needed to capture the variability of large cache memories § Problem: Getting statistics across large designs is $$ and difficult

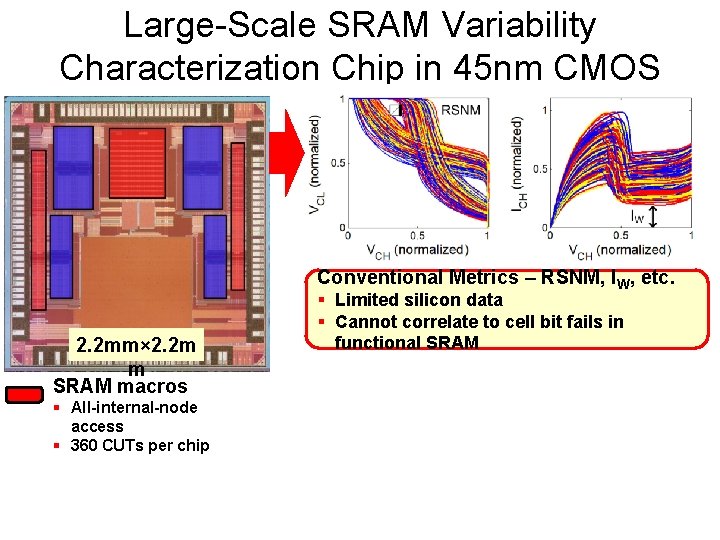

Large-Scale SRAM Variability Characterization Chip in 45 nm CMOS Conventional Metrics – RSNM, IW, etc. 2. 2 mm× 2. 2 m m SRAM macros § All-internal-node access § 360 CUTs per chip § Limited silicon data § Cannot correlate to cell bit fails in functional SRAM

Large-Scale SRAM Variability Characterization Chip in 45 nm CMOS Large-Scale SRAM Metrics – SRRV, WWTV, etc. 2. 2 mm× 2. 2 m m Functional SRAM arrays § Direct bit-line access § 768 Kb per chip § Silicon data measured for each SRAM cell § Characterized under natural operating environment § Correlate to cell bit fails in functional SRAM

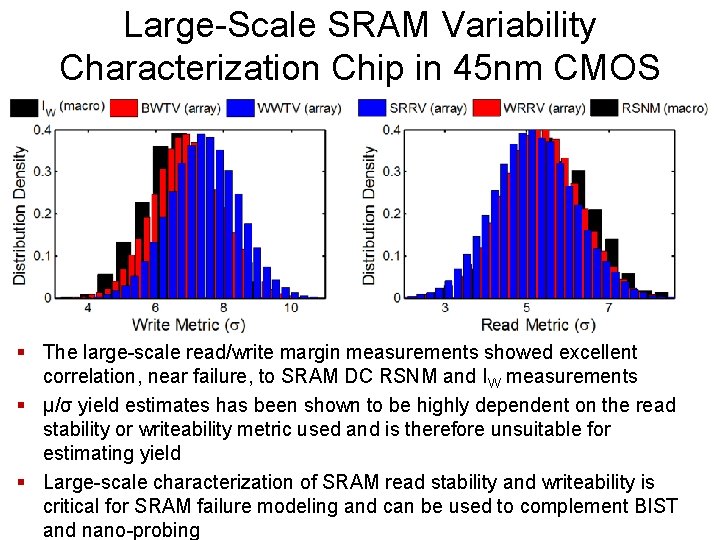

Large-Scale SRAM Variability Characterization Chip in 45 nm CMOS § The large-scale read/write margin measurements showed excellent correlation, near failure, to SRAM DC RSNM and IW measurements § µ/σ yield estimates has been shown to be highly dependent on the read stability or writeability metric used and is therefore unsuitable for estimating yield § Large-scale characterization of SRAM read stability and writeability is critical for SRAM failure modeling and can be used to complement BIST and nano-probing

- Slides: 4