LABORG Parte 6 VHDL Processos Paralelismo e o

LABORG Parte 6 - VHDL: Processos, Paralelismo e o Comando process César Augusto Missio Marcon Ney Laert Vilar Calazans 05/outubro/2009

Sumário ØIntrodução ØProcessos em VHDL ØTRABALHO A FAZER ØA ENTREGAR César Marcon / Ney Calazans 2

Sumário ØIntrodução ØProcessos em VHDL ØTRABALHO A FAZER ØA ENTREGAR César Marcon / Ney Calazans 3

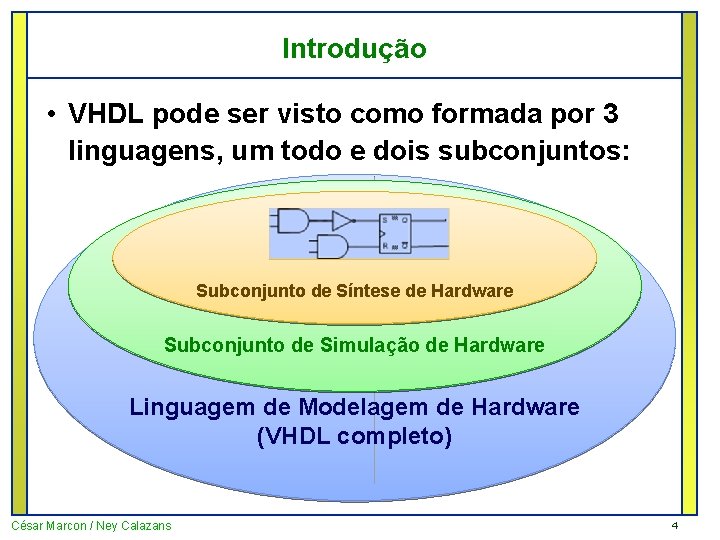

Introdução • VHDL pode ser visto como formada por 3 linguagens, um todo e dois subconjuntos: Subconjunto de Síntese de Hardware Subconjunto de Simulação de Hardware Linguagem de Modelagem de Hardware (VHDL completo) César Marcon / Ney Calazans 4

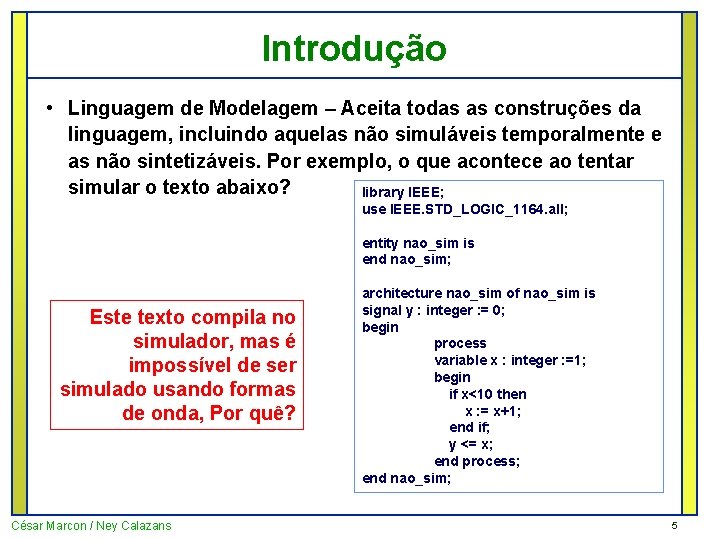

Introdução • Linguagem de Modelagem – Aceita todas as construções da linguagem, incluindo aquelas não simuláveis temporalmente e as não sintetizáveis. Por exemplo, o que acontece ao tentar simular o texto abaixo? library IEEE; use IEEE. STD_LOGIC_1164. all; entity nao_sim is end nao_sim; Este texto compila no simulador, mas é impossível de ser simulado usando formas de onda, Por quê? César Marcon / Ney Calazans architecture nao_sim of nao_sim is signal y : integer : = 0; begin process variable x : integer : =1; begin if x<10 then x : = x+1; end if; y <= x; end process; end nao_sim; 5

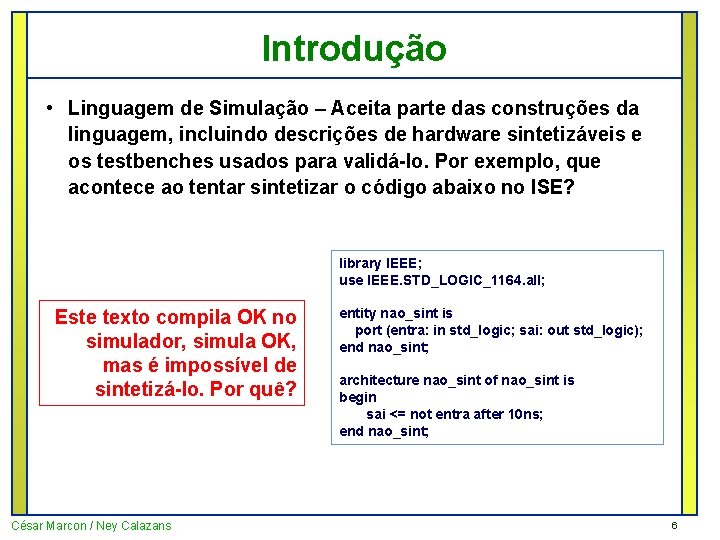

Introdução • Linguagem de Simulação – Aceita parte das construções da linguagem, incluindo descrições de hardware sintetizáveis e os testbenches usados para validá-lo. Por exemplo, que acontece ao tentar sintetizar o código abaixo no ISE? library IEEE; use IEEE. STD_LOGIC_1164. all; Este texto compila OK no simulador, simula OK, mas é impossível de sintetizá-lo. Por quê? César Marcon / Ney Calazans entity nao_sint is port (entra: in std_logic; sai: out std_logic); end nao_sint; architecture nao_sint of nao_sint is begin sai <= not entra after 10 ns; end nao_sint; 6

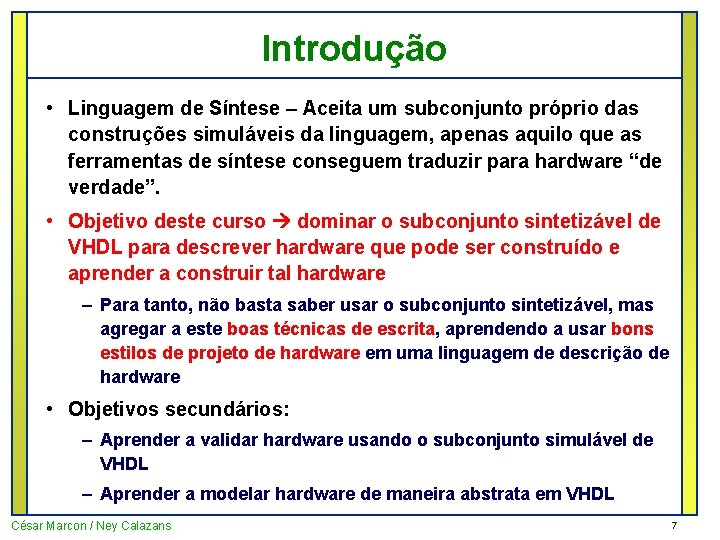

Introdução • Linguagem de Síntese – Aceita um subconjunto próprio das construções simuláveis da linguagem, apenas aquilo que as ferramentas de síntese conseguem traduzir para hardware “de verdade”. • Objetivo deste curso dominar o subconjunto sintetizável de VHDL para descrever hardware que pode ser construído e aprender a construir tal hardware – Para tanto, não basta saber usar o subconjunto sintetizável, mas agregar a este boas técnicas de escrita, aprendendo a usar bons estilos de projeto de hardware em uma linguagem de descrição de hardware • Objetivos secundários: – Aprender a validar hardware usando o subconjunto simulável de VHDL – Aprender a modelar hardware de maneira abstrata em VHDL César Marcon / Ney Calazans 7

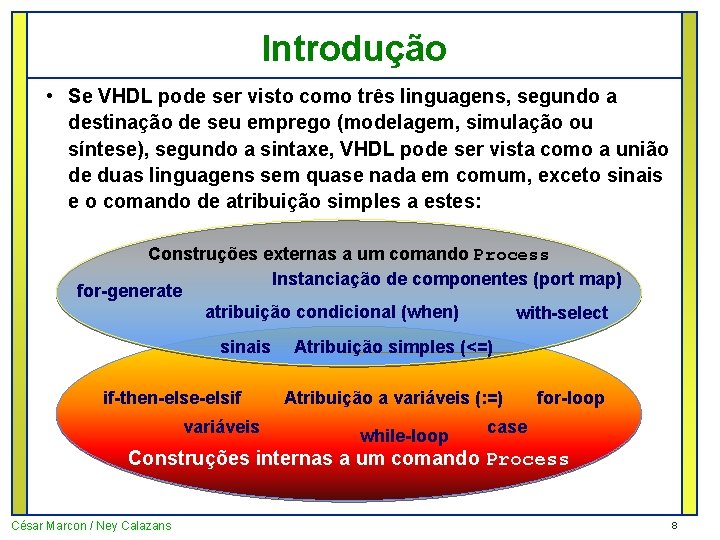

Introdução • Se VHDL pode ser visto como três linguagens, segundo a destinação de seu emprego (modelagem, simulação ou síntese), segundo a sintaxe, VHDL pode ser vista como a união de duas linguagens sem quase nada em comum, exceto sinais e o comando de atribuição simples a estes: Construções externas a um comando Process Instanciação de componentes (port map) for-generate atribuição condicional (when) with-select sinais if-then-else-elsif variáveis Atribuição simples (<=) Atribuição a variáveis (: =) while-loop for-loop case Construções internas a um comando Process César Marcon / Ney Calazans 8

Sumário üIntrodução ØProcessos em VHDL ØTRABALHO A FAZER ØA ENTREGAR César Marcon / Ney Calazans 9

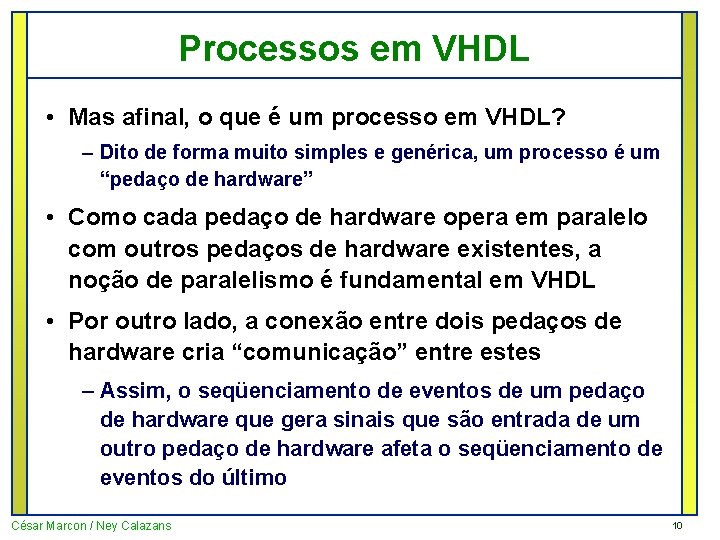

Processos em VHDL • Mas afinal, o que é um processo em VHDL? – Dito de forma muito simples e genérica, um processo é um “pedaço de hardware” • Como cada pedaço de hardware opera em paralelo com outros pedaços de hardware existentes, a noção de paralelismo é fundamental em VHDL • Por outro lado, a conexão entre dois pedaços de hardware cria “comunicação” entre estes – Assim, o seqüenciamento de eventos de um pedaço de hardware que gera sinais que são entrada de um outro pedaço de hardware afeta o seqüenciamento de eventos do último César Marcon / Ney Calazans 10

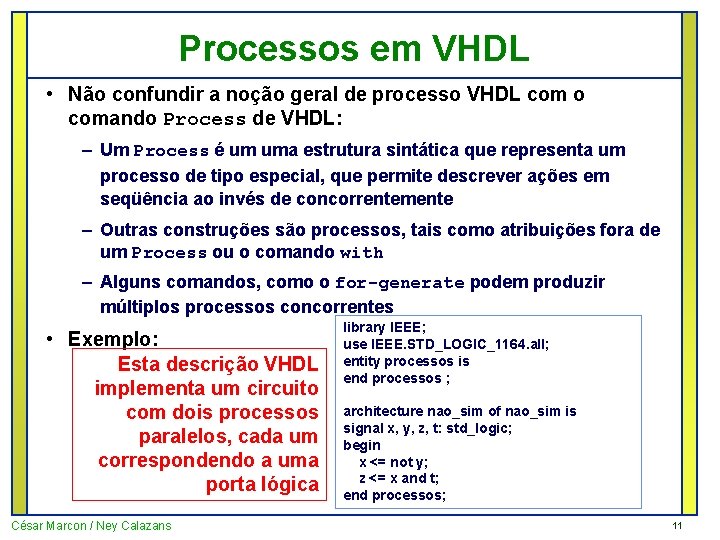

Processos em VHDL • Não confundir a noção geral de processo VHDL com o comando Process de VHDL: – Um Process é um uma estrutura sintática que representa um processo de tipo especial, que permite descrever ações em seqüência ao invés de concorrentemente – Outras construções são processos, tais como atribuições fora de um Process ou o comando with – Alguns comandos, como o for-generate podem produzir múltiplos processos concorrentes • Exemplo: Esta descrição VHDL implementa um circuito com dois processos paralelos, cada um correspondendo a uma porta lógica César Marcon / Ney Calazans library IEEE; use IEEE. STD_LOGIC_1164. all; entity processos is end processos ; architecture nao_sim of nao_sim is signal x, y, z, t: std_logic; begin x <= not y; z <= x and t; end processos; 11

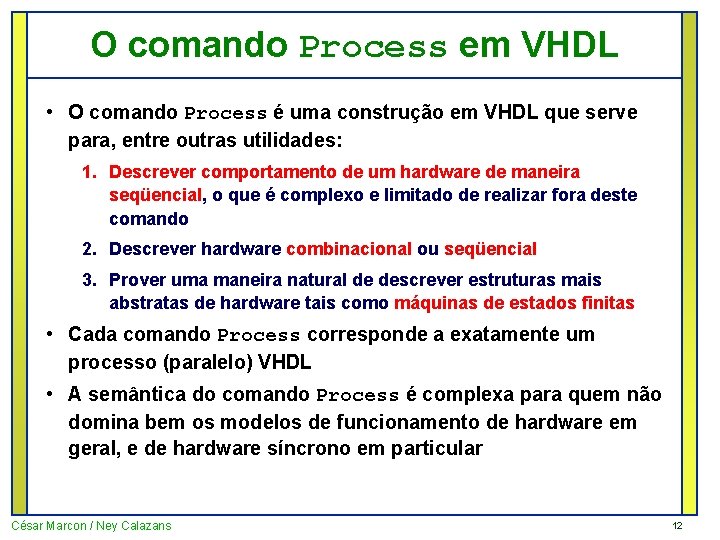

O comando Process em VHDL • O comando Process é uma construção em VHDL que serve para, entre outras utilidades: 1. Descrever comportamento de um hardware de maneira seqüencial, o que é complexo e limitado de realizar fora deste comando 2. Descrever hardware combinacional ou seqüencial 3. Prover uma maneira natural de descrever estruturas mais abstratas de hardware tais como máquinas de estados finitas • Cada comando Process corresponde a exatamente um processo (paralelo) VHDL • A semântica do comando Process é complexa para quem não domina bem os modelos de funcionamento de hardware em geral, e de hardware síncrono em particular César Marcon / Ney Calazans 12

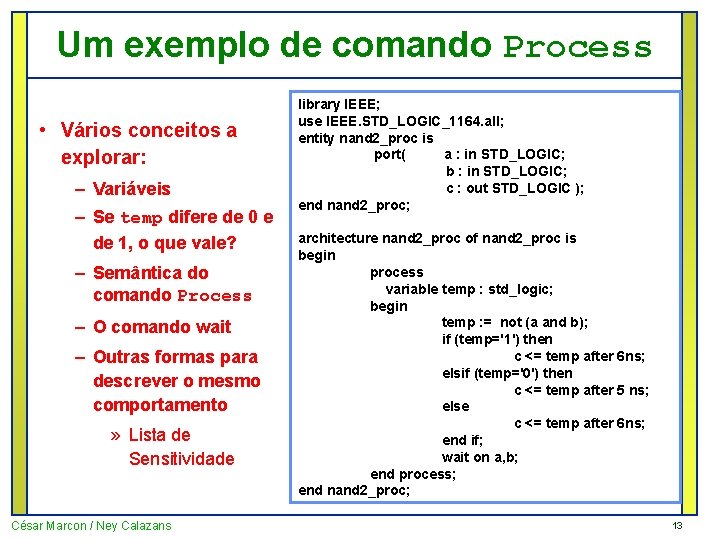

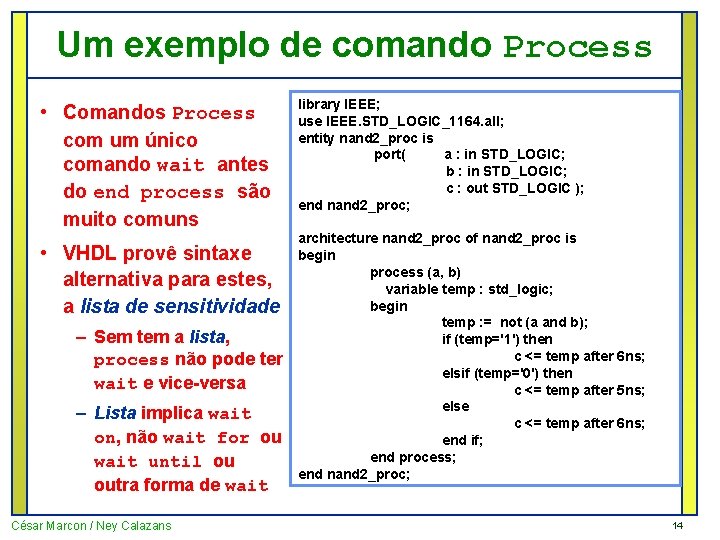

Um exemplo de comando Process • Vários conceitos a explorar: – Variáveis – Se temp difere de 0 e de 1, o que vale? – Semântica do comando Process – O comando wait – Outras formas para descrever o mesmo comportamento » Lista de Sensitividade César Marcon / Ney Calazans library IEEE; use IEEE. STD_LOGIC_1164. all; entity nand 2_proc is port( a : in STD_LOGIC; b : in STD_LOGIC; c : out STD_LOGIC ); end nand 2_proc; architecture nand 2_proc of nand 2_proc is begin process variable temp : std_logic; begin temp : = not (a and b); if (temp='1') then c <= temp after 6 ns; elsif (temp='0') then c <= temp after 5 ns; else c <= temp after 6 ns; end if; wait on a, b; end process; end nand 2_proc; 13

Um exemplo de comando Process • Comandos Process com um único comando wait antes do end process são muito comuns • VHDL provê sintaxe alternativa para estes, a lista de sensitividade – Sem tem a lista, process não pode ter wait e vice-versa – Lista implica wait on, não wait for ou wait until ou outra forma de wait César Marcon / Ney Calazans library IEEE; use IEEE. STD_LOGIC_1164. all; entity nand 2_proc is port( a : in STD_LOGIC; b : in STD_LOGIC; c : out STD_LOGIC ); end nand 2_proc; architecture nand 2_proc of nand 2_proc is begin process (a, b) variable temp : std_logic; begin temp : = not (a and b); if (temp='1') then c <= temp after 6 ns; elsif (temp='0') then c <= temp after 5 ns; else c <= temp after 6 ns; end if; end process; end nand 2_proc; 14

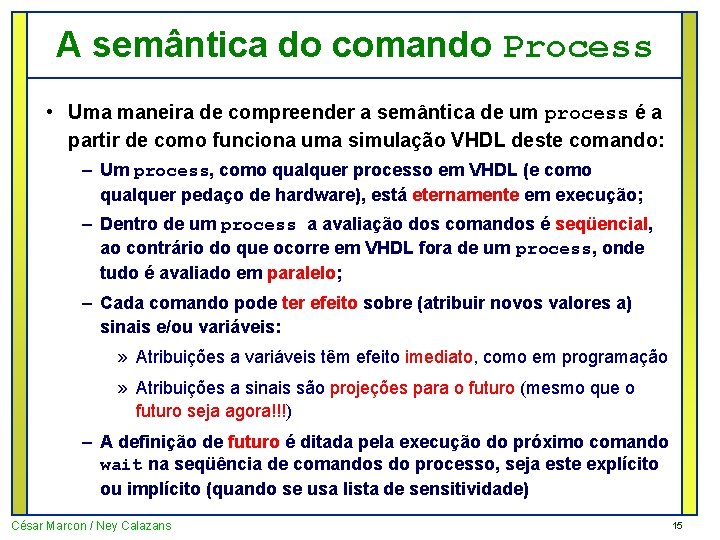

A semântica do comando Process • Uma maneira de compreender a semântica de um process é a partir de como funciona uma simulação VHDL deste comando: – Um process, como qualquer processo em VHDL (e como qualquer pedaço de hardware), está eternamente em execução; – Dentro de um process a avaliação dos comandos é seqüencial, ao contrário do que ocorre em VHDL fora de um process, onde tudo é avaliado em paralelo; – Cada comando pode ter efeito sobre (atribuir novos valores a) sinais e/ou variáveis: » Atribuições a variáveis têm efeito imediato, como em programação » Atribuições a sinais são projeções para o futuro (mesmo que o futuro seja agora!!!) – A definição de futuro é ditada pela execução do próximo comando wait na seqüência de comandos do processo, seja este explícito ou implícito (quando se usa lista de sensitividade) César Marcon / Ney Calazans 15

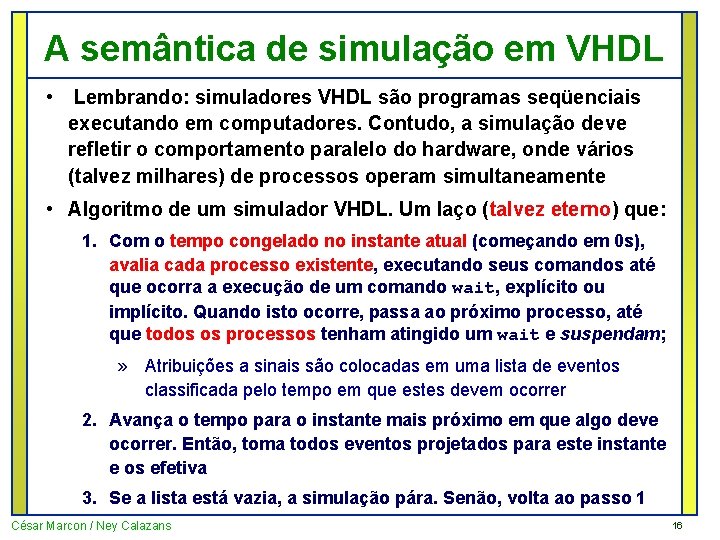

A semântica de simulação em VHDL • Lembrando: simuladores VHDL são programas seqüenciais executando em computadores. Contudo, a simulação deve refletir o comportamento paralelo do hardware, onde vários (talvez milhares) de processos operam simultaneamente • Algoritmo de um simulador VHDL. Um laço (talvez eterno) que: 1. Com o tempo congelado no instante atual (começando em 0 s), avalia cada processo existente, executando seus comandos até que ocorra a execução de um comando wait, explícito ou implícito. Quando isto ocorre, passa ao próximo processo, até que todos os processos tenham atingido um wait e suspendam; » Atribuições a sinais são colocadas em uma lista de eventos classificada pelo tempo em que estes devem ocorrer 2. Avança o tempo para o instante mais próximo em que algo deve ocorrer. Então, toma todos eventos projetados para este instante e os efetiva 3. Se a lista está vazia, a simulação pára. Senão, volta ao passo 1 César Marcon / Ney Calazans 16

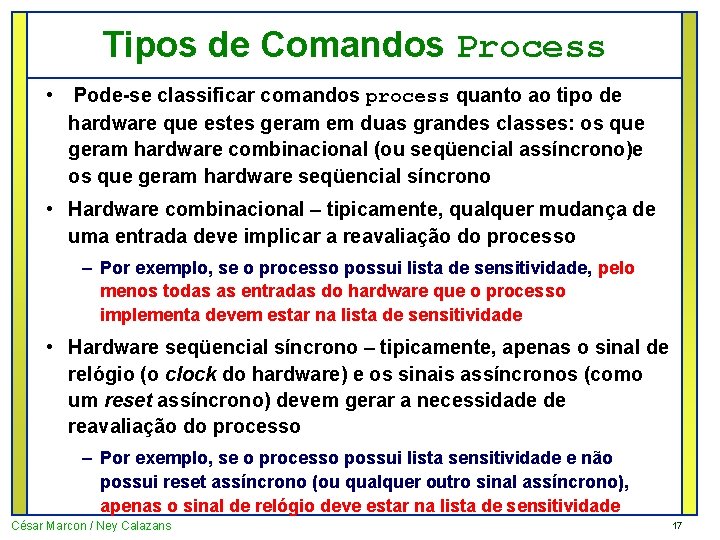

Tipos de Comandos Process • Pode-se classificar comandos process quanto ao tipo de hardware que estes geram em duas grandes classes: os que geram hardware combinacional (ou seqüencial assíncrono)e os que geram hardware seqüencial síncrono • Hardware combinacional – tipicamente, qualquer mudança de uma entrada deve implicar a reavaliação do processo – Por exemplo, se o processo possui lista de sensitividade, pelo menos todas as entradas do hardware que o processo implementa devem estar na lista de sensitividade • Hardware seqüencial síncrono – tipicamente, apenas o sinal de relógio (o clock do hardware) e os sinais assíncronos (como um reset assíncrono) devem gerar a necessidade de reavaliação do processo – Por exemplo, se o processo possui lista sensitividade e não possui reset assíncrono (ou qualquer outro sinal assíncrono), apenas o sinal de relógio deve estar na lista de sensitividade César Marcon / Ney Calazans 17

Sumário üIntrodução üProcessos em VHDL ØTRABALHO A FAZER ØA ENTREGAR César Marcon / Ney Calazans 18

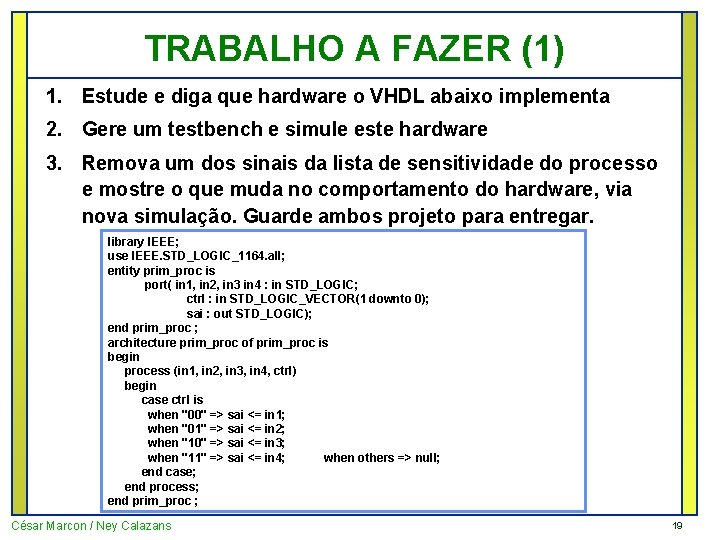

TRABALHO A FAZER (1) 1. Estude e diga que hardware o VHDL abaixo implementa 2. Gere um testbench e simule este hardware 3. Remova um dos sinais da lista de sensitividade do processo e mostre o que muda no comportamento do hardware, via nova simulação. Guarde ambos projeto para entregar. library IEEE; use IEEE. STD_LOGIC_1164. all; entity prim_proc is port( in 1, in 2, in 3 in 4 : in STD_LOGIC; ctrl : in STD_LOGIC_VECTOR(1 downto 0); sai : out STD_LOGIC); end prim_proc ; architecture prim_proc of prim_proc is begin process (in 1, in 2, in 3, in 4, ctrl) begin case ctrl is when "00" => sai <= in 1; when "01" => sai <= in 2; when "10" => sai <= in 3; when "11" => sai <= in 4; when others => null; end case; end process; end prim_proc ; César Marcon / Ney Calazans 19

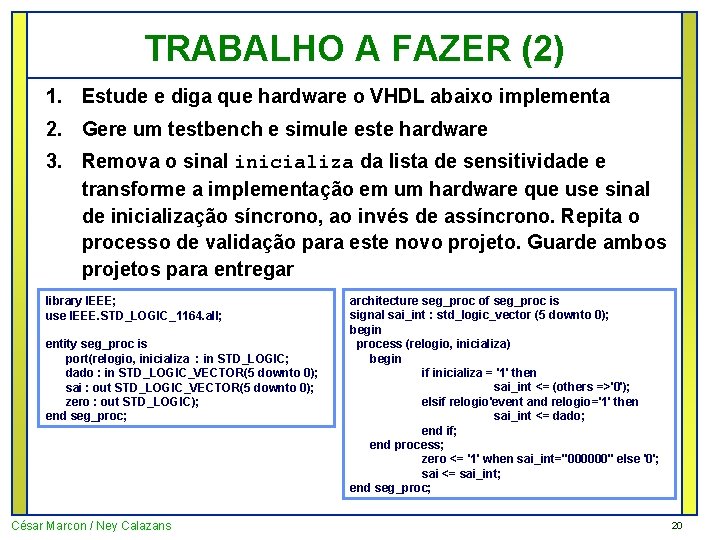

TRABALHO A FAZER (2) 1. Estude e diga que hardware o VHDL abaixo implementa 2. Gere um testbench e simule este hardware 3. Remova o sinal inicializa da lista de sensitividade e transforme a implementação em um hardware que use sinal de inicialização síncrono, ao invés de assíncrono. Repita o processo de validação para este novo projeto. Guarde ambos projetos para entregar library IEEE; use IEEE. STD_LOGIC_1164. all; entity seg_proc is port(relogio, inicializa : in STD_LOGIC; dado : in STD_LOGIC_VECTOR(5 downto 0); sai : out STD_LOGIC_VECTOR(5 downto 0); zero : out STD_LOGIC); end seg_proc; César Marcon / Ney Calazans architecture seg_proc of seg_proc is signal sai_int : std_logic_vector (5 downto 0); begin process (relogio, inicializa) begin if inicializa = '1' then sai_int <= (others =>'0'); elsif relogio'event and relogio='1' then sai_int <= dado; end if; end process; zero <= '1' when sai_int="000000" else '0'; sai <= sai_int; end seg_proc; 20

Sumário üIntrodução üProcessos em VHDL üTRABALHO A FAZER ØA ENTREGAR César Marcon / Ney Calazans 21

A ENTREGAR Os quatro projetos Active-HDL com as implementações dois processos (o código não simulável, o código não-sintetizável, e os dois trabalhos da Seção TRABALHO A FAZER), contendo: 1. Os fontes de cada implementação 2. Os testbenches de cada implementação 3. Formas de onda mostrando a funcionalidade da implementação, ou a falta desta (com mensagem(ns) de erro) 4. Texto breve descrevendo cada projeto (pode ser arquivo. txt acrescentado a cada projeto) César Marcon / Ney Calazans 22

- Slides: 22