Laboratoire de lAcclrateur Linaire IN 2 P 3

Laboratoire de l’Accélérateur Linéaire (IN 2 P 3 -CNRS) Orsay, France Upgrade calo FE review Comments : Digital part This is just a support to start the discussion Friday, 20 September 2013 Calorimeter upgrade meeting Olivier Duarte

FPGA Choice u Point (2) : Ø Open questions on the architecture of the FEB and the CB Ø a single FPGA could do the job of the "Trigger-PGA" and the job of the Ä Ä "Control-PGA” Ø New target Smart. Fusion 2 flash FPGA from Micro. Semi At the moment we target A 3 PE 1500 FPGA for the FEPGA of the FE block (FEB). It’s a compromise between radiation tolerance, price, number and standart IOs and internal resource in the chip. A single FPGA for “Trigger and Control” Why not ! It will be define when we define precisely the architecture of the board ! The new family FPGA Smart. Fusion 2 include specifiques functions as Ser. Des, Arm processor, etc (We haven’t need of the function !). But “Buffers Implemented with SEU Resistant Latches on the DDR bridge SPI FIFO”. Price and availability? Need more investigation on this new family ! Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 2

SLVS-LVDS translation u Point (3) : Ø The need for SLVS-LVDS translation must be evaluated. The GBTX is specified to receive LVDS signals. Basic tests from CMS indicate that the A 3 PE 1500 can accept SLVS signals, but these should be verified with more detailed tests. Ä The prototype FEB and CROC board will be used to test this compatibility of the A 3 PE and SLVS Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 3

Clock distribution on the backplane u Point (6) : Ø The clock distribution architecture in the FEB crate should be investigated. Ø Usage of buffers or translators within FPGAs might create additional jitter or destroy fine phase/latency control. Ø If it is possible to go directly from the GBTX chip to the FPGA or analog chip via the backplane (with no significant degradation of signal in terms of jitter) than that should be the cleanest option. Ä On the board it’s possible to go directly from the GBTX chip to the FPGA. Ä On the backplane we will used LVDS, It will be tested with the prototype board (FEB and CROC) Ä Even if we want to use SLVS on backplane, it’s necessary to use buffer (vey low jitter!) between the board and the backplane. Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 4

First prototype with mezzanine for GBTX and SCA u Point (7) : Ø It was suggested to design the first prototypes to have mezzanines or similar so that external chips (GBT-SCAs or GBTXs) can be plugged when available and tests can still be performed while waiting for those chips to be available. Ä The idea is to do the prototype FEB and CROC with the footprint describe in the GBT datasheet (BGA) Ä Very difficult to implement a mezzanine (area, type of connectors, . . . ) Ä It’s possible to start the tests of the board without GBT solder on the PCB ! Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 5

No mezzanine for data transmission u Point (8) : Ø In the initial version of the new design, event data serializers and associated optical drivers were located on mezzanines. Due to the lack of manpower following this option, it might be wise to come back to a direct implementation of these components on the front-end boards. Ø Increase the intrinsic cost of the front-end boards Ä No mezzanine, event data serializers and asociated optical drivers will be located on the FEB and on the CROC. Ä To separate the cost of the links (serializers + optical drivers/receivers + fiber optics) from that of the boards and to have a separate funding See Frédéric Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 6

Firmware download by Slow Control u Point (10) : Ø In-situ programming of the FPGAs should be investigated in more detail. This assumes that the bit-stream can be transmitted via the GBT-SCA. Ø The power requirements for the flash programming should be clarified and incorporated into the system. Ä Completely agree with this point Ä In fact we want to reuse and adapt the development of the CMS team Ä What is the situation of this development ? Ä Completely agree with this point Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 7

Spare Olivier Duarte Calorimeter upgrade meeting Friday, 20 September 2013 8

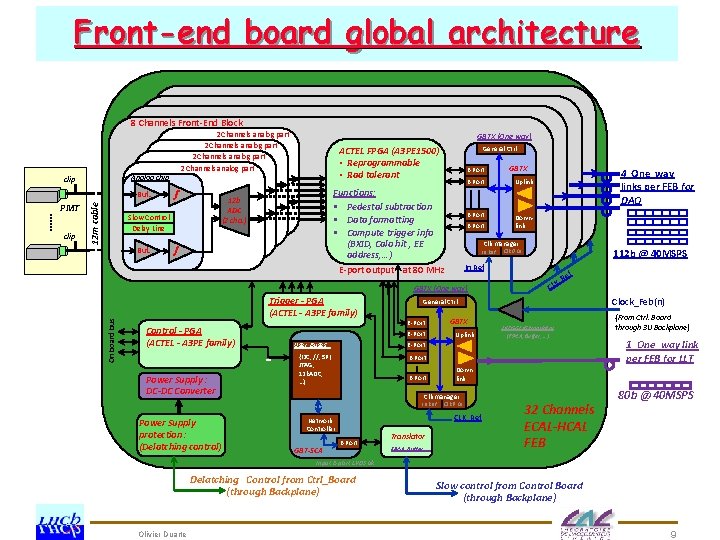

Front-end board global architecture 8 Channels Front-End Block 2 Channels analog part clip 12 m cable …… Buf. E-Port Functions: • Pedestal subtraction • Data formatting • Compute trigger info (BXID, Calo hit , EE address, …) 12 b ADC (2 cha. ) Slow Control Delay Line General Ctrl ACTEL FPGA (A 3 PE 1500) • Reprogrammable • Rad tolerant Analog chip clip PMT GBTX (One way) Detector cells Uplink E-Port Downlink E-Port Power Supply : DC-DC Converter On board bus GBTX E-Port {I 2 C, //, SPI, JTAG, 12 b. ADC, …} Uplink LVDS-SLVS translator (FPGA, Buffer, …) E-Port Clk[7: 0] CLK_Ref Network Controller E-Port Translator FPGA, Buffer, … {From Ctrl. Board through 3 U Backplane} 1 One way link per FEB for LLT Downlink E-Port Clk manager GBT-SCA Clock_Feb(n) E-Port User Buses : In Ref Power Supply protection : (Delatching control) f Re K_ CL General Ctrl E-Port : 112 b @ 40 MSPS Clk[7: 0] In Ref GBTX (One way) Control - PGA (ACTEL - A 3 PE family) 4 One way links per FEB for DAQ Clk manager In Ref E-port output at 80 MHz Trigger - PGA (ACTEL - A 3 PE family) GBTX E-Port 32 Channels ECAL-HCAL FEB 80 b @ 40 MSPS Input E-port LVDS ok Delatching Control from Ctrl_Board (through Backplane) Olivier Duarte Slow control from Control Board (through Backplane) 9

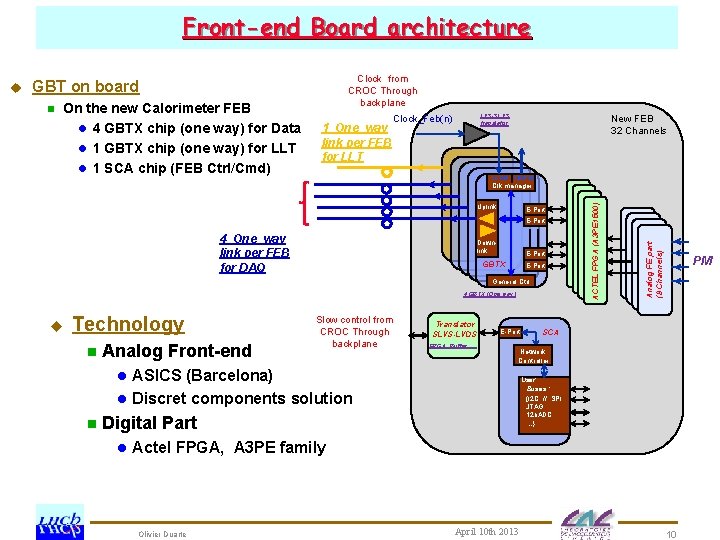

Front-end Board architecture Clock from CROC Through backplane GBT on board n On the new Calorimeter FEB l 4 GBTX chip (one way) for Data l 1 GBTX chip (one way) for LLT l 1 SCA chip (FEB Ctrl/Cmd) 1 One way link per FEB for LLT LVS-SLVS translator Clock_Feb(n) New FEB 32 Channels In Ref Clk[7: 0] Uplink E-Port 4 One way link per FEB for DAQ Downlink E-Port GBTX E-Port General Ctrl 4 GBTX (One way) u Technology n Analog Front-end Slow control from CROC Through backplane Translator SLVS-LVDS FPGA, Buffer, … E-Port ASICS (Barcelona) l Discret components solution SCA User Buses : {I 2 C, //, SPI, JTAG, 12 b. ADC, …} Digital Part l PM Network Controller l n Analog FE part (8 Channels) Clk manager ACTEL FPGA (A 3 PE 1500) u Actel FPGA, A 3 PE family Olivier Duarte April 10 th 2013 10

![CROC architecture u Why keep the CROC n n n Clk[0] Provide the distribution CROC architecture u Why keep the CROC n n n Clk[0] Provide the distribution](http://slidetodoc.com/presentation_image/73923e2b72c925067df8abe126273692/image-11.jpg)

CROC architecture u Why keep the CROC n n n Clk[0] Provide the distribution of the synchronous commands signal (Channel B, …) to the FEB inside FE Crate Provide Slow Control distribution Provide Clk distribution One GBTX master SLVS-LVDS translator In Ref Clock distribution to FEB through backplane Clk[7: 0] Clk manager Uplink E-Port x (18) 2 bidir link Downlink GBTX Buffer E-Port_TVB E-Port_FEB E-Port General Ctrl E-Port SCA _New. CROC Translator SLVS-LVDS FPGA, Buffer, … 2 bidir link 2 GBTX E-Port SCA_New. CROC Network Controller u GBT on board n On new CROC board l 2 GBTX (one master) chip with bidirectional optical fiber (right side and left side of FE crate) l 1 SCA chip (CROC Ctrl/Cmd) Olivier Duarte User Buses : {I 2 C, //, SPI, JTAG, 12 b. ADC, …} New CROC LHCb AMC 40 firmware workshop 1 SCA April 10 th 2013 11

- Slides: 11