Laboratoire de lAcclrateur Linaire IN 2 P 3

Laboratoire de l’Accélérateur Linéaire (IN 2 P 3 -CNRS) Orsay, Packing Chiche Ronic Caceres Thierry Duarte Olivier LHCb upgrade meeting France

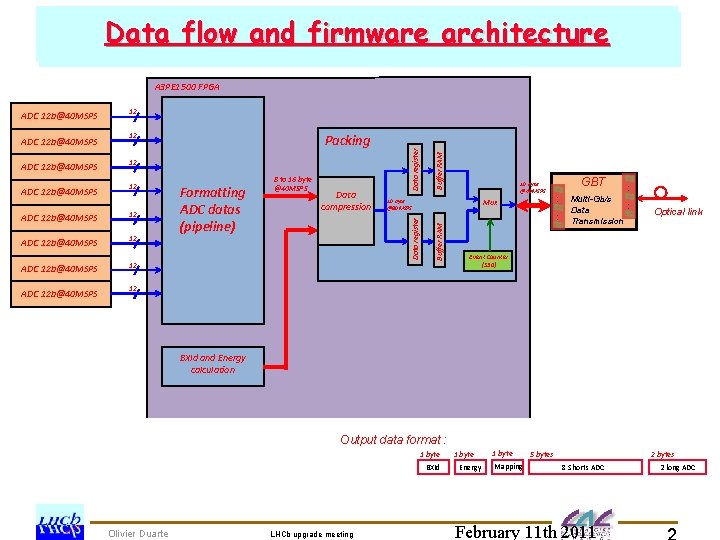

Data flow and firmware architecture prototype tests development : schedule SCROC chedule for SPECS A 3 PE 1500 FPGA 12 12 ADC 12 b@40 MSPS 12 Formatting ADC datas (pipeline) 8 to 16 byte @40 MSPS Data compression Buffer RAM ADC 12 b@40 MSPS Packing 10 byte @40 MSPS Mux 10 byte @80 MSPS GBT. . Buffer RAM ADC 12 b@40 MSPS 12 Data register ADC 12 b@40 MSPS . . Multi-Gb/s. . Data Transmission Optical link Event counter (350) BXId and Energy calculation Output data format : 1 byte BXId Olivier Duarte LHCb upgrade meeting 1 byte Energy 1 byte Mapping 5 bytes 2 bytes 8 Shorts ADC February 11 th 2011 2 long ADC

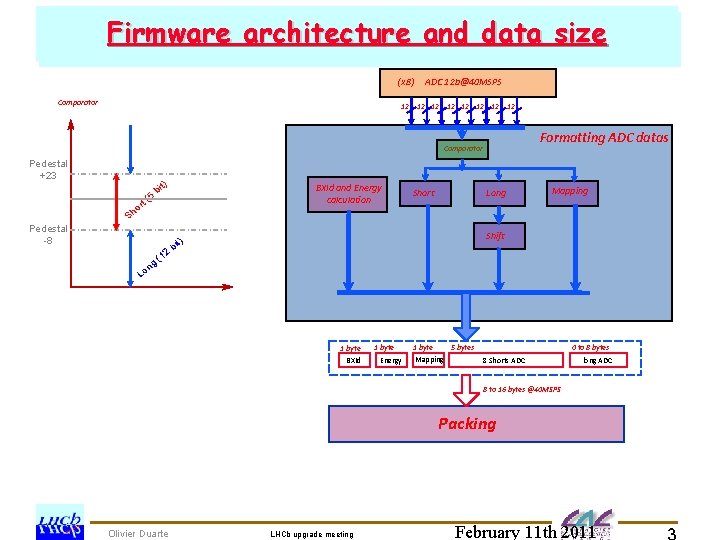

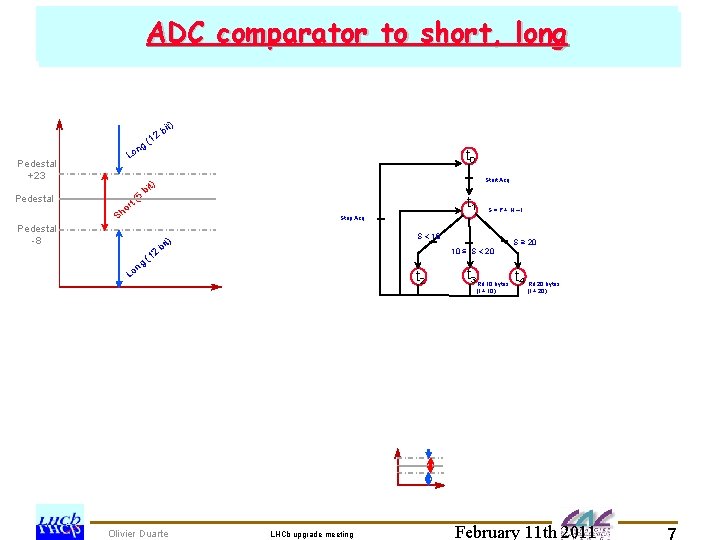

Firmware architecture size prototype testsand : sdata chedule SCROC chedule for SPECS development (x 8) Comparator ADC 12 b@40 MSPS 12 12 Formatting ADC datas Comparator Pedestal +23 or Sh 5 t( t) BXId and Energy calculation bi Pedestal -8 ng Lo 2 (1 Short Long Mapping Shift t) bi 1 byte BXId 1 byte Energy 1 byte 5 bytes Mapping 0 to 8 bytes 8 Shorts ADC long ADC 8 to 16 bytes @40 MSPS Packing Olivier Duarte LHCb upgrade meeting February 11 th 2011

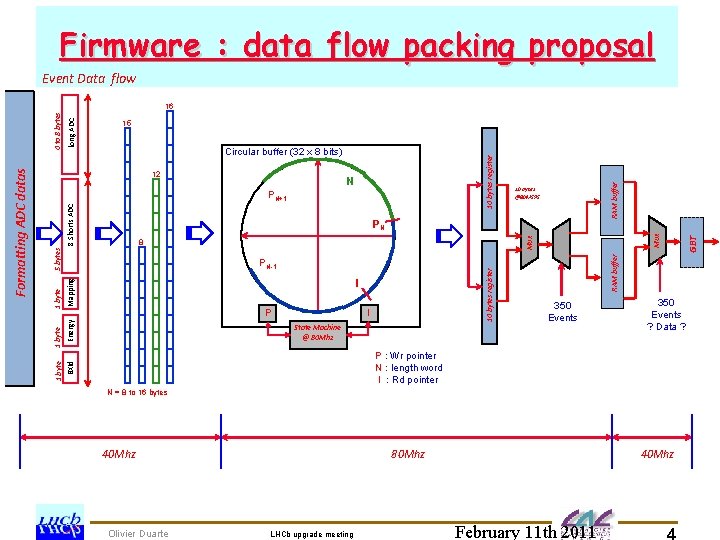

Firmware : data flow packing proposal Event Data flow 8 Shorts ADC 10 bytes register PN-1 Mapping I I P State Machine @ 80 Mhz RAM buffer Mux 5 bytes 8 Energy Mux PN 350 Events ? Data ? P : Wr pointer N : length word I : Rd pointer BXId 1 byte 10 bytes @80 MSPS N = 8 to 16 bytes 40 Mhz Olivier Duarte 80 Mhz LHCb upgrade meeting 40 Mhz February 11 th 2011 GBT N PN+1 RAM buffer Circular buffer (32 x 8 bits) 10 bytes register long ADC 15 12 1 byte Formatting ADC datas 0 to 8 bytes 16

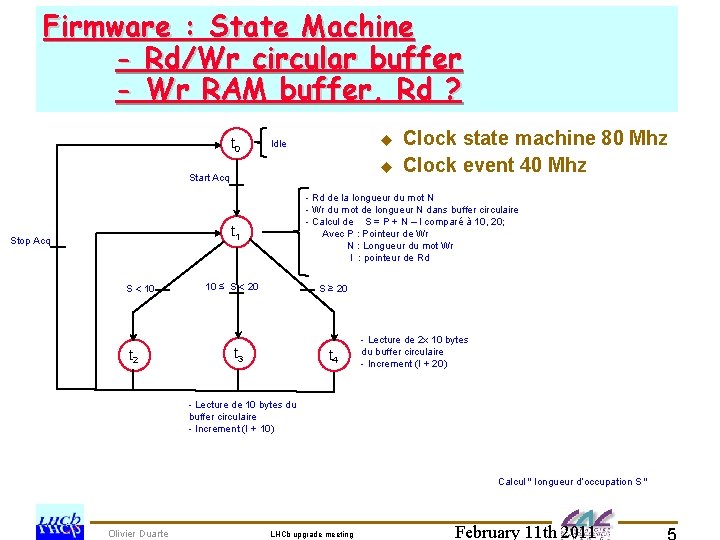

Firmware : State Machine - Rd/Wr circular buffer - Wr RAM buffer, Rd ? t 0 u Idle u Start Acq - Rd de la longueur du mot N - Wr du mot de longueur N dans buffer circulaire - Calcul de S = P + N – I comparé à 10, 20; Avec P : Pointeur de Wr N : Longueur du mot Wr I : pointeur de Rd t 1 Stop Acq S 10 t 2 Clock state machine 80 Mhz Clock event 40 Mhz 10 ≤ S 20 S ≥ 20 t 3 t 4 - Lecture de 2 x 10 bytes du buffer circulaire - Increment (I + 20) - Lecture de 10 bytes du buffer circulaire - Increment (I + 10) Calcul " longueur d’occupation S " Olivier Duarte LHCb upgrade meeting February 11 th 2011

SPARE Olivier Duarte LHCb upgrade meeting

ADCprototype comparator to short, long tests : schedule SCROC chedule for SPECS development ng Pedestal +23 Pedestal 2 (1 ) bit t 0 Lo rt o Sh (5 Start Acq t) bi t 1 S=P+N–I Stop Acq Pedestal -8 g n Lo 2 (1 S 10 t) bi 10 ≤ S 20 t 2 t 3 Rd 10 bytes t 4 Rd 20 bytes (I + 10) Olivier Duarte LHCb upgrade meeting S ≥ 20 (I + 20) February 11 th 2011

- Slides: 7