Lab II VerilogXL Simulation Lab II 1 Introduction

Lab. II Verilog-XL을 이용한 Simulation Lab. II - 1

Introduction p Hardware Description Language(HDL) a programming language that can describe the functionality and timing of hardware circuits l Verilog, VHDL, etc l p Simulator software which reads the HDL and emulates the hardware described by the HDL l Verilog-XL l 2

Different Levels of Abstraction p Architecture / Algorithmic l described in the terms of the algorithms it performs p Register Transfer Logic(RTL) describes the flow of data and control signals l schedules assignments at clock edges l p Gate l interconnection of switch elements(or gates) to check functionality, performance, or timing of design p Switch l describes logic behavior of transistor circuits 3

Major Data Type Classes p Nets l represent physical connection between devices p Registers l represent abstract storage devices p Parameters l declare run-time constants 4

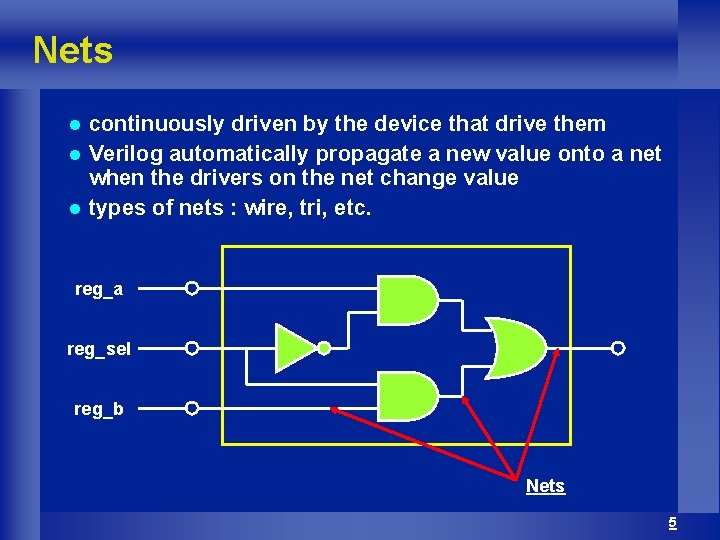

Nets continuously driven by the device that drive them l Verilog automatically propagate a new value onto a net when the drivers on the net change value l types of nets : wire, tri, etc. l reg_a reg_sel reg_b Nets 5

Registers holds its value until a new value is assigned to it. l used extensively in behavioral modeling and in applying stimuli. l values are applied to registers using behavioral constructs. l types of registers : reg, integer, real, time l 6

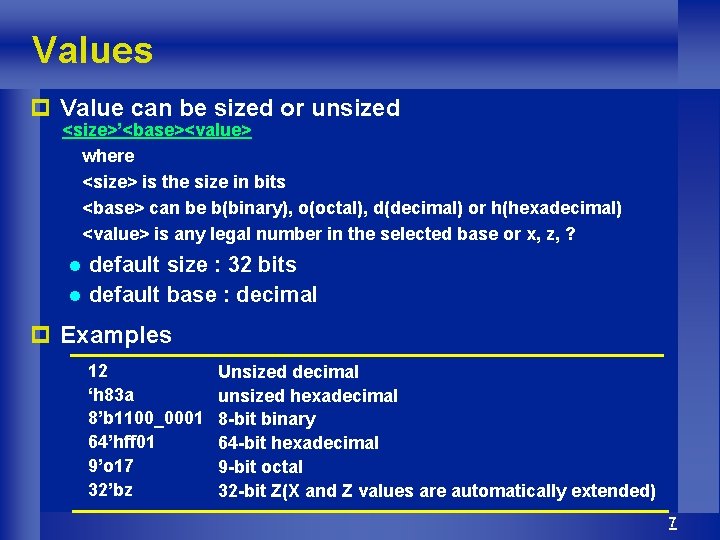

Values p Value can be sized or unsized <size>’<base><value> where <size> is the size in bits <base> can be b(binary), o(octal), d(decimal) or h(hexadecimal) <value> is any legal number in the selected base or x, z, ? default size : 32 bits l default base : decimal l p Examples 12 ‘h 83 a 8’b 1100_0001 64’hff 01 9’o 17 32’bz Unsized decimal unsized hexadecimal 8 -bit binary 64 -bit hexadecimal 9 -bit octal 32 -bit Z(X and Z values are automatically extended) 7

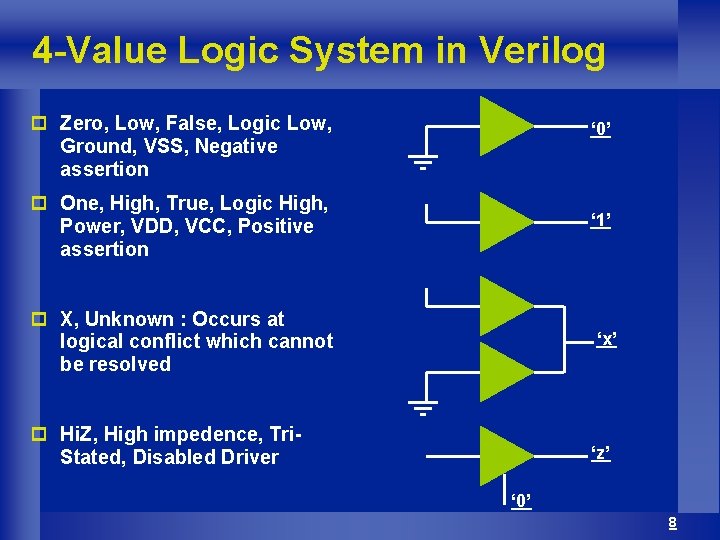

4 -Value Logic System in Verilog p Zero, Low, False, Logic Low, Ground, VSS, Negative assertion ‘ 0’ p One, High, True, Logic High, Power, VDD, VCC, Positive assertion ‘ 1’ p X, Unknown : Occurs at logical conflict which cannot be resolved ‘x’ p Hi. Z, High impedence, Tri. Stated, Disabled Driver ‘z’ ‘ 0’ 8

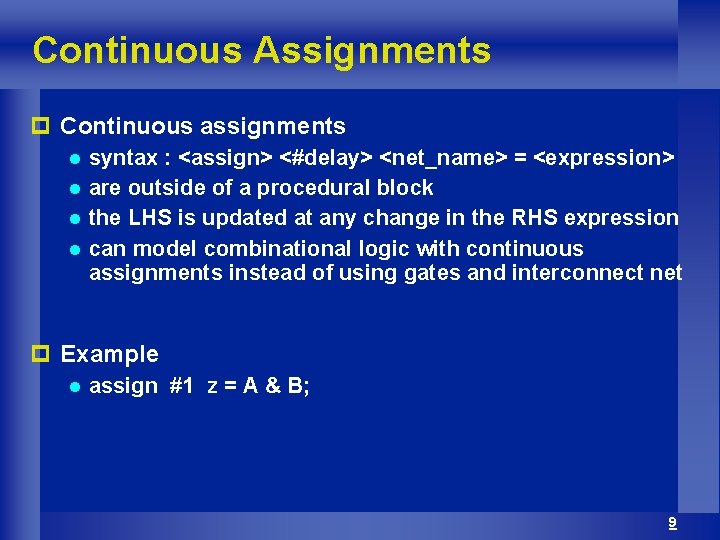

Continuous Assignments p Continuous assignments syntax : <assign> <#delay> <net_name> = <expression> l are outside of a procedural block l the LHS is updated at any change in the RHS expression l can model combinational logic with continuous assignments instead of using gates and interconnect net l p Example l assign #1 z = A & B; 9

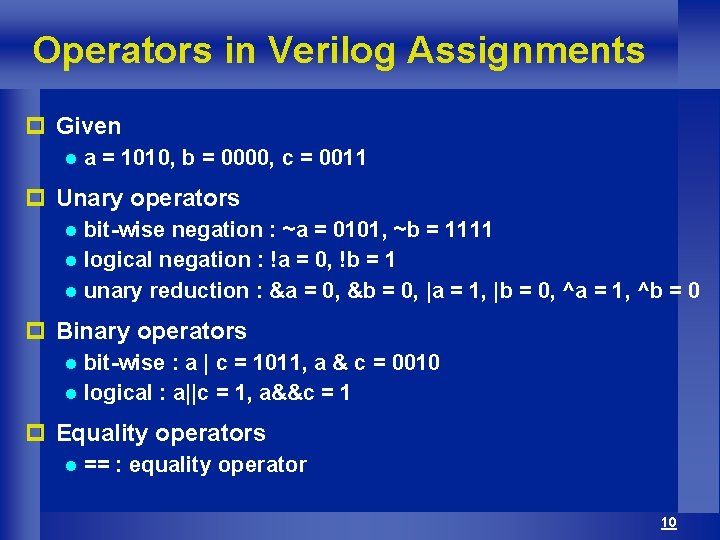

Operators in Verilog Assignments p Given l a = 1010, b = 0000, c = 0011 p Unary operators bit-wise negation : ~a = 0101, ~b = 1111 l logical negation : !a = 0, !b = 1 l unary reduction : &a = 0, &b = 0, |a = 1, |b = 0, ^a = 1, ^b = 0 l p Binary operators bit-wise : a | c = 1011, a & c = 0010 l logical : a||c = 1, a&&c = 1 l p Equality operators l == : equality operator 10

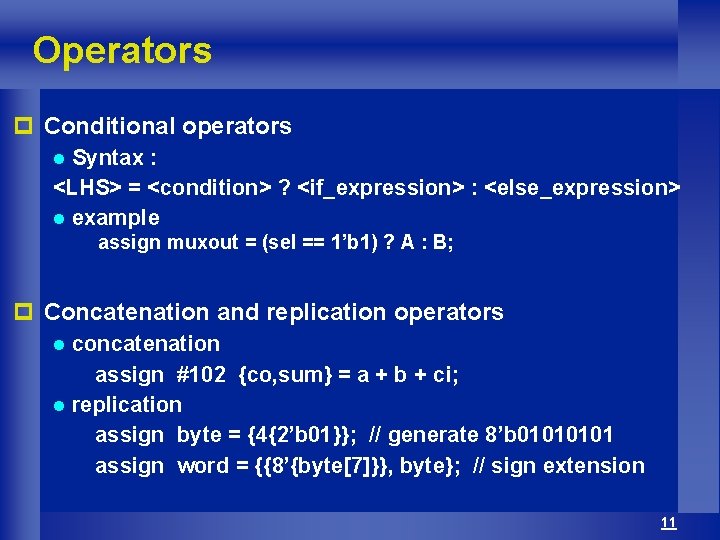

Operators p Conditional operators Syntax : <LHS> = <condition> ? <if_expression> : <else_expression> l example l assign muxout = (sel == 1’b 1) ? A : B; p Concatenation and replication operators concatenation assign #102 {co, sum} = a + b + ci; l replication assign byte = {4{2’b 01}}; // generate 8’b 0101 assign word = {{8’{byte[7]}}, byte}; // sign extension l 11

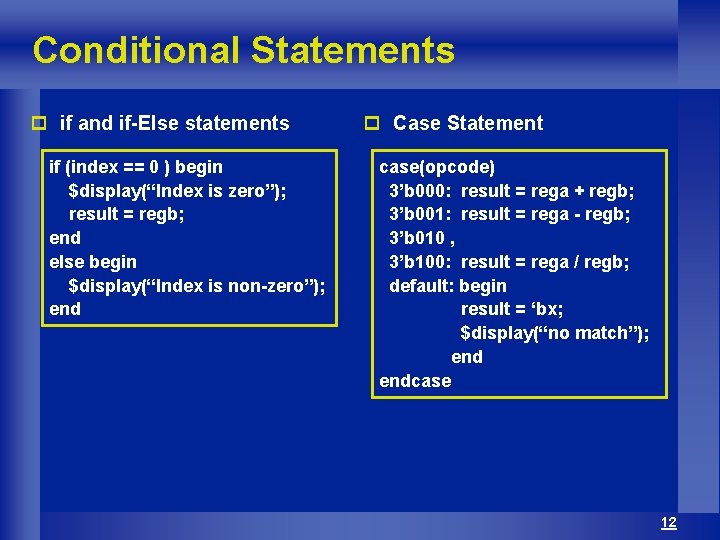

Conditional Statements p if and if-Else statements if (index == 0 ) begin $display(“Index is zero”); result = regb; end else begin $display(“Index is non-zero”); end p Case Statement case(opcode) 3’b 000: result = rega + regb; 3’b 001: result = rega - regb; 3’b 010 , 3’b 100: result = rega / regb; default: begin result = ‘bx; $display(“no match”); endcase 12

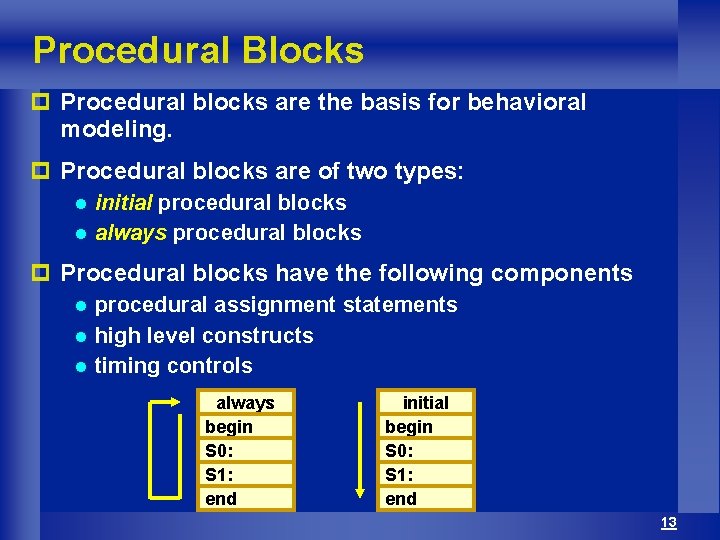

Procedural Blocks p Procedural blocks are the basis for behavioral modeling. p Procedural blocks are of two types: initial procedural blocks l always procedural blocks l p Procedural blocks have the following components procedural assignment statements l high level constructs l timing controls l always begin S 0: S 1: end initial begin S 0: S 1: end 13

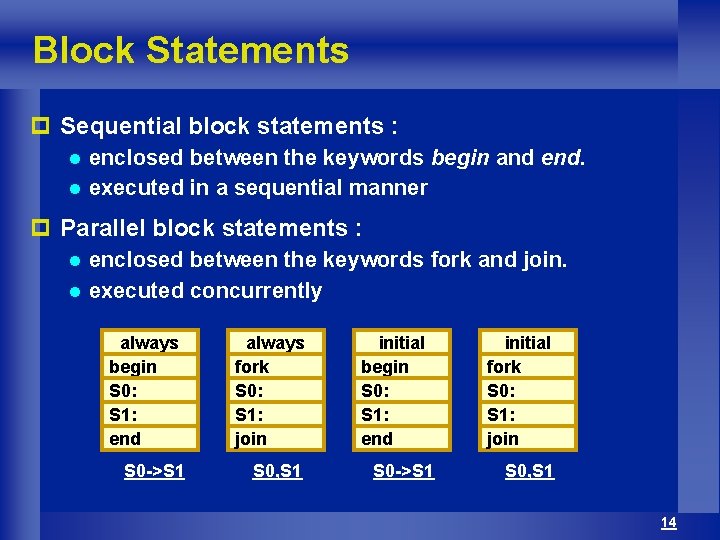

Block Statements p Sequential block statements : enclosed between the keywords begin and end. l executed in a sequential manner l p Parallel block statements : enclosed between the keywords fork and join. l executed concurrently l always begin S 0: S 1: end always fork S 0: S 1: join S 0 ->S 1 S 0, S 1 initial begin S 0: S 1: end S 0 ->S 1 initial fork S 0: S 1: join S 0, S 1 14

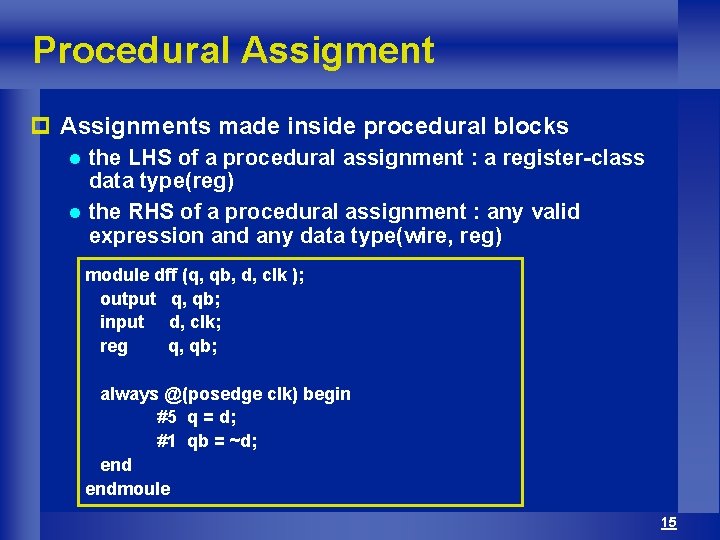

Procedural Assigment p Assignments made inside procedural blocks the LHS of a procedural assignment : a register-class data type(reg) l the RHS of a procedural assignment : any valid expression and any data type(wire, reg) l module dff (q, qb, d, clk ); output q, qb; input d, clk; reg q, qb; always @(posedge clk) begin #5 q = d; #1 qb = ~d; endmoule 15

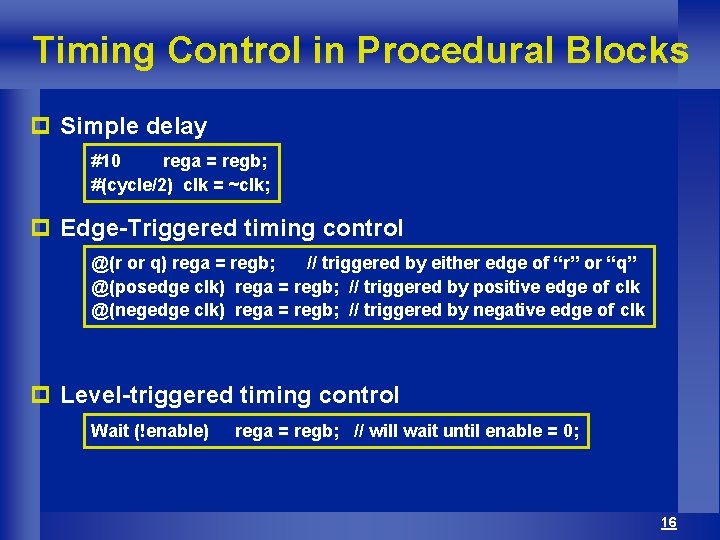

Timing Control in Procedural Blocks p Simple delay #10 rega = regb; #(cycle/2) clk = ~clk; p Edge-Triggered timing control @(r or q) rega = regb; // triggered by either edge of “r” or “q” @(posedge clk) rega = regb; // triggered by positive edge of clk @(negedge clk) rega = regb; // triggered by negative edge of clk p Level-triggered timing control Wait (!enable) rega = regb; // will wait until enable = 0; 16

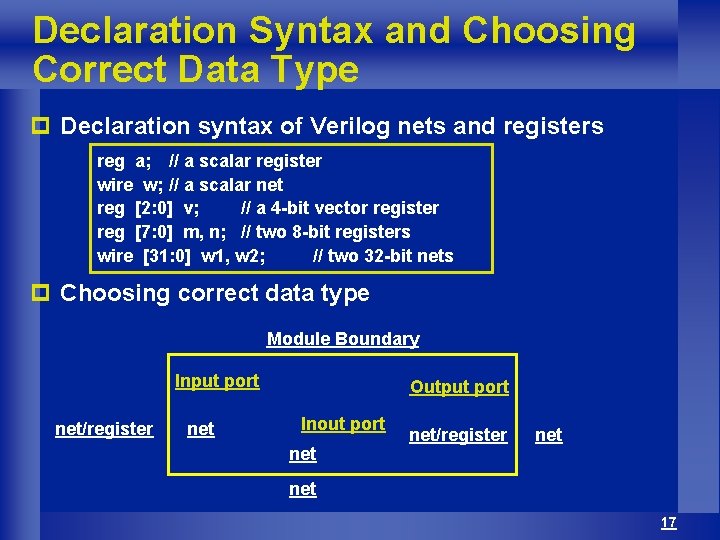

Declaration Syntax and Choosing Correct Data Type p Declaration syntax of Verilog nets and registers reg a; // a scalar register wire w; // a scalar net reg [2: 0] v; // a 4 -bit vector register reg [7: 0] m, n; // two 8 -bit registers wire [31: 0] w 1, w 2; // two 32 -bit nets p Choosing correct data type Module Boundary Input port net/register net Output port Inout port net/register net 17

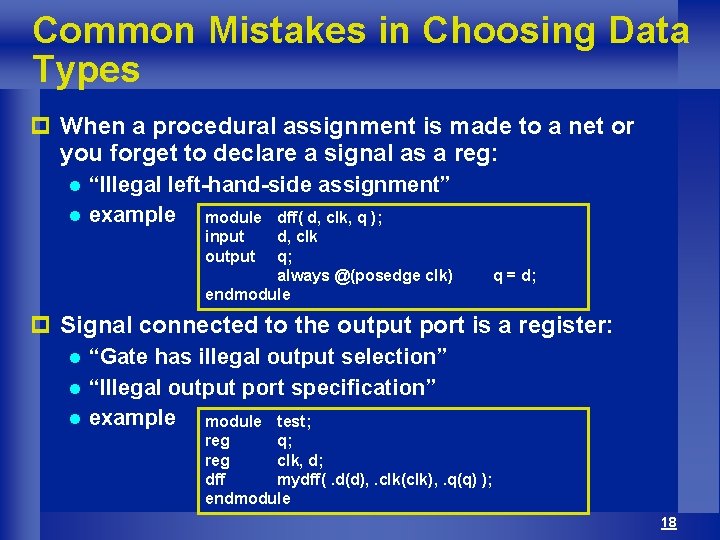

Common Mistakes in Choosing Data Types p When a procedural assignment is made to a net or you forget to declare a signal as a reg: “Illegal left-hand-side assignment” l example module dff( d, clk, q ); l input output d, clk q; always @(posedge clk) endmodule q = d; p Signal connected to the output port is a register: “Gate has illegal output selection” l “Illegal output port specification” l example module test; l reg q; reg clk, d; dff mydff(. d(d), . clk(clk), . q(q) ); endmodule 18

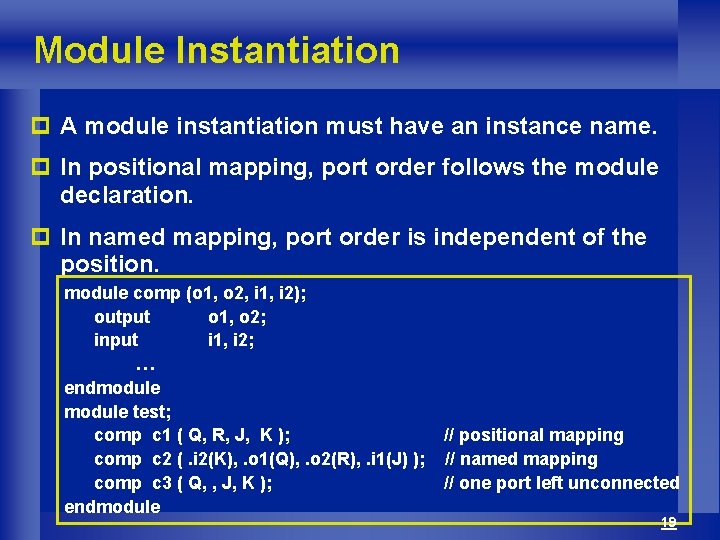

Module Instantiation p A module instantiation must have an instance name. p In positional mapping, port order follows the module declaration. p In named mapping, port order is independent of the position. module comp (o 1, o 2, i 1, i 2); output o 1, o 2; input i 1, i 2; … endmodule test; comp c 1 ( Q, R, J, K ); comp c 2 (. i 2(K), . o 1(Q), . o 2(R), . i 1(J) ); comp c 3 ( Q, , J, K ); endmodule // positional mapping // named mapping // one port left unconnected 19

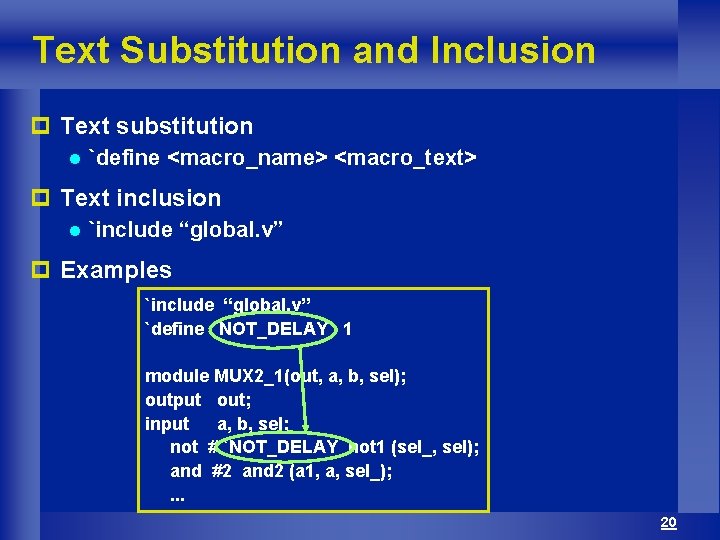

Text Substitution and Inclusion p Text substitution l `define <macro_name> <macro_text> p Text inclusion l `include “global. v” p Examples `include “global. v” `define NOT_DELAY 1 module MUX 2_1(out, a, b, sel); output out; input a, b, sel; not # `NOT_DELAY not 1 (sel_, sel); and #2 and 2 (a 1, a, sel_); . . . 20

Behavioral Modeling p Enables you to describe the system at a high level of abstraction. p Is described by specifying a set of concurrently active procedural blocks 21

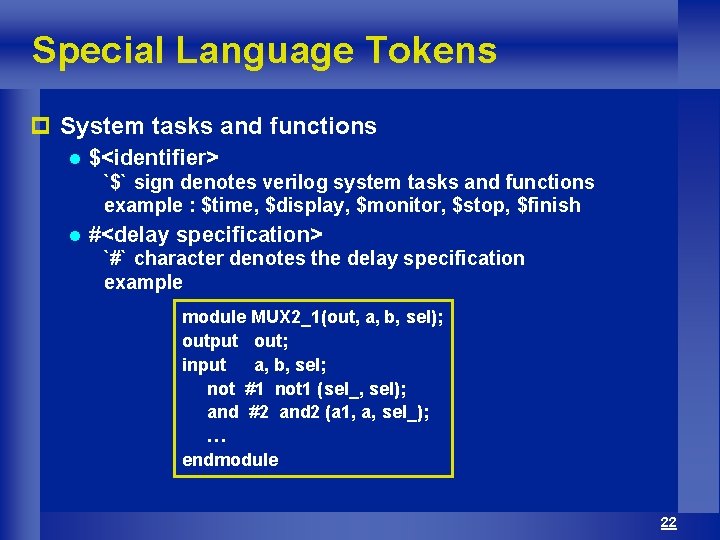

Special Language Tokens p System tasks and functions l $<identifier> `$` sign denotes verilog system tasks and functions example : $time, $display, $monitor, $stop, $finish l #<delay specification> `#` character denotes the delay specification example module MUX 2_1(out, a, b, sel); output out; input a, b, sel; not #1 not 1 (sel_, sel); and #2 and 2 (a 1, a, sel_); … endmodule 22

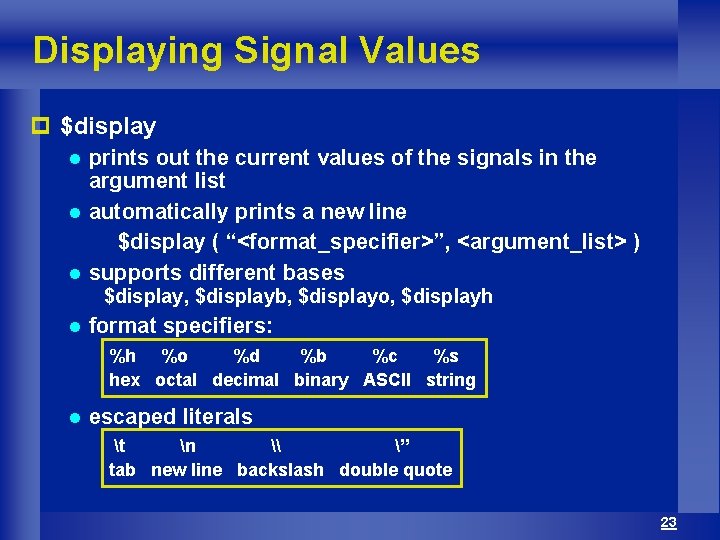

Displaying Signal Values p $display prints out the current values of the signals in the argument list l automatically prints a new line $display ( “<format_specifier>”, <argument_list> ) l supports different bases l $display, $displayb, $displayo, $displayh l format specifiers: %h %o %d %b %c %s hex octal decimal binary ASCII string l escaped literals t n \ ” tab new line backslash double quote 23

Displaying Signal Values(cont. ) p $write identical to $display except that it does not print a new line character l supports different bases l $write, $writeb, $writeo, $writeh 24

![Displaying Signal Values(cont. ) p Example module textio; reg flag; reg [31: 0] data; Displaying Signal Values(cont. ) p Example module textio; reg flag; reg [31: 0] data;](http://slidetodoc.com/presentation_image_h2/9e51838494233a0078b759607a119a46/image-25.jpg)

Displaying Signal Values(cont. ) p Example module textio; reg flag; reg [31: 0] data; initial begin $writeb(“%d”, $time, , “%h t”, data, , flag, “n” ); #15 flag = 1; data = 16; $displayh($time, , data, , flag ); end initial begin #10 data = 20; $display($time, , data ); data = 30; endmodule 25

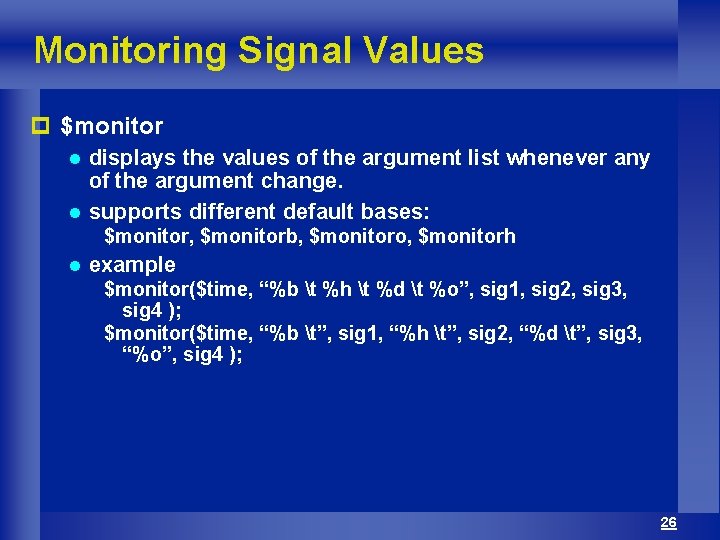

Monitoring Signal Values p $monitor displays the values of the argument list whenever any of the argument change. l supports different default bases: l $monitor, $monitorb, $monitoro, $monitorh l example $monitor($time, “%b t %h t %d t %o”, sig 1, sig 2, sig 3, sig 4 ); $monitor($time, “%b t”, sig 1, “%h t”, sig 2, “%d t”, sig 3, “%o”, sig 4 ); 26

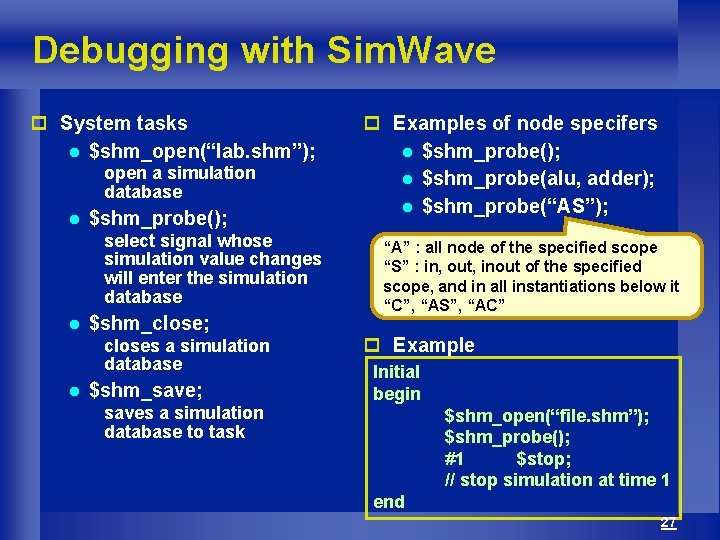

Debugging with Sim. Wave p System tasks l $shm_open(“lab. shm”); open a simulation database l $shm_probe(); select signal whose simulation value changes will enter the simulation database l $shm_close; closes a simulation database l $shm_save; saves a simulation database to task p Examples of node specifers l $shm_probe(); l $shm_probe(alu, adder); l $shm_probe(“AS”); “A” : all node of the specified scope “S” : in, out, inout of the specified scope, and in all instantiations below it “C”, “AS”, “AC” p Example Initial begin $shm_open(“file. shm”); $shm_probe(); #1 $stop; // stop simulation at time 1 end 27

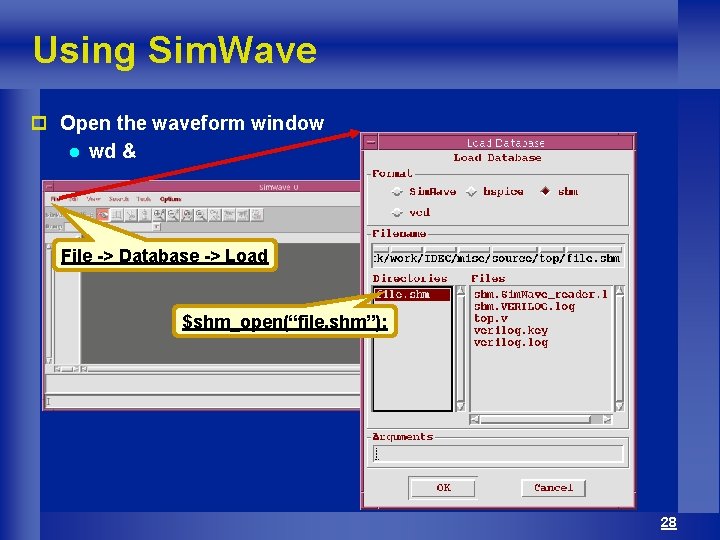

Using Sim. Wave p Open the waveform window l wd & File -> Database -> Load $shm_open(“file. shm”); 28

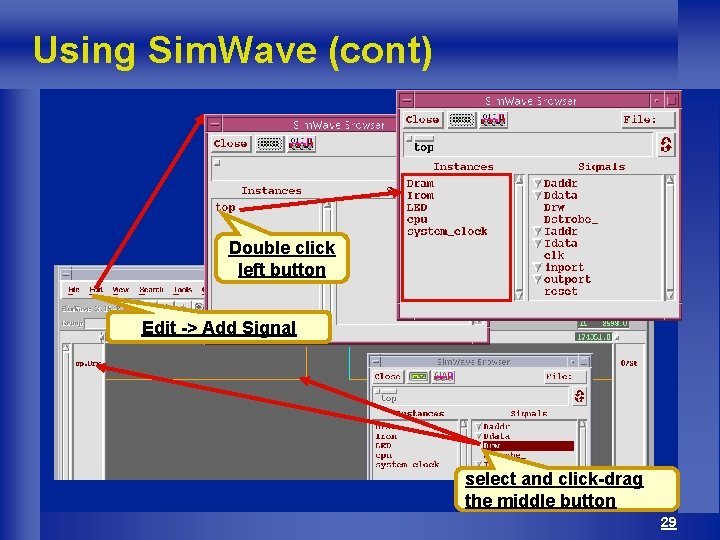

Using Sim. Wave (cont) Double click left button Edit -> Add Signal select and click-drag the middle button 29

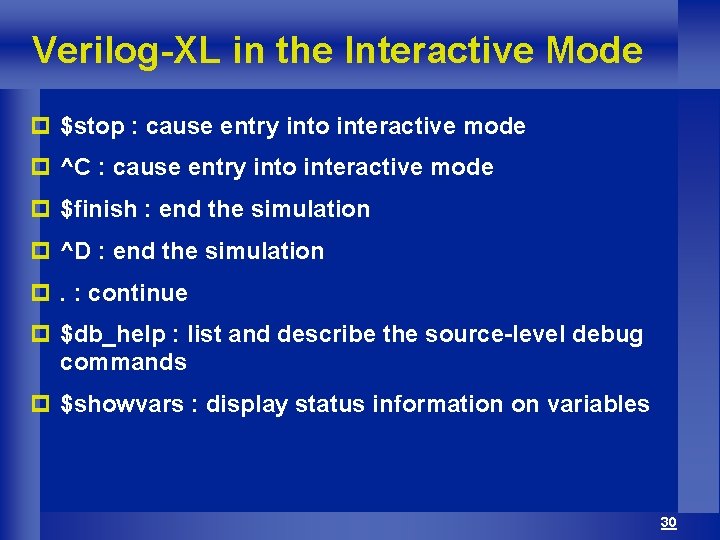

Verilog-XL in the Interactive Mode p $stop : cause entry into interactive mode p ^C : cause entry into interactive mode p $finish : end the simulation p ^D : end the simulation p. : continue p $db_help : list and describe the source-level debug commands p $showvars : display status information on variables 30

Reference p Verilog-XL 교육 자료 l IC Design Education Center (1998. 12. 22 ~ 12. 24) p Verilog-XL Reference Manual (Vol. 1, Vol. 2) l Cadence p The Verilog Hardware Description Language Donald E. Thomas and Philip Moorby l Kluwer Academic Publishers l 31

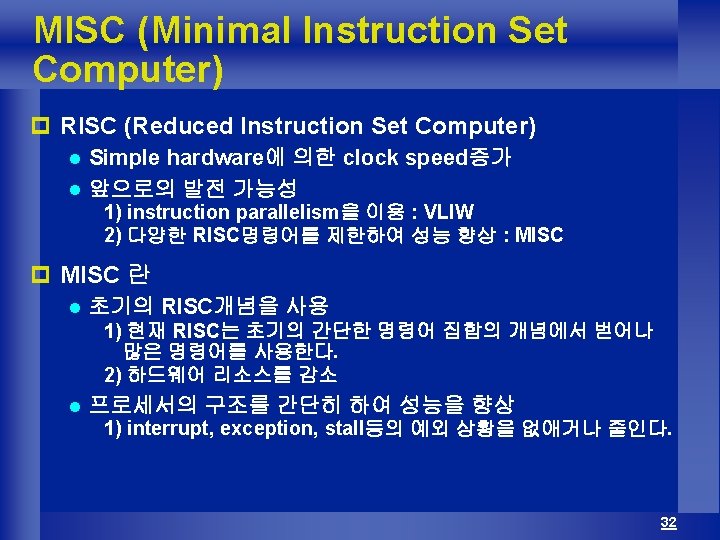

MISC p MISC의 사용 용도 l controller또는 제어용 mini computer p MISC의 적용 분야 High speed communication systems l Intelligent hard disk controllers l Robotic controller l p MISC 제작 history l 제 1회 IDEC MPW 1) 0. 8 um SOG (Samsung 공정) l IDEC-C 631 개발 1) 0. 6 um TLM (LG 공정) 2) test chip으로 이용 3) Test program과 board를 통한 동작 확인 33

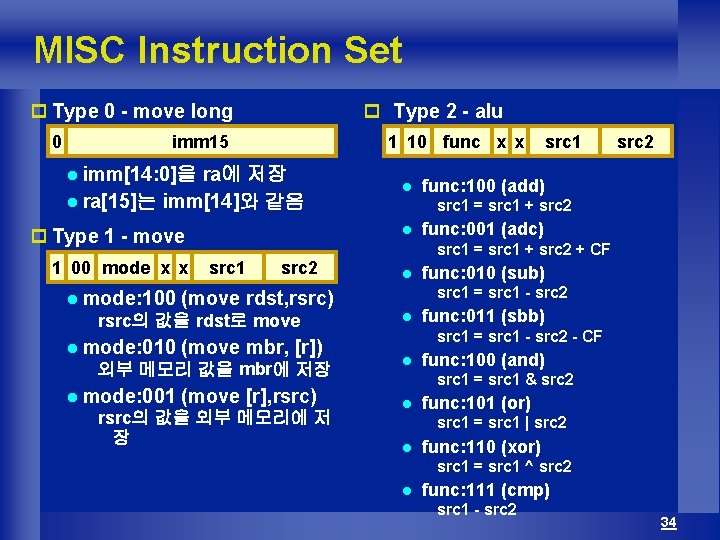

MISC Instruction Set p Type 0 - move long 0 p Type 2 - alu imm 15 1 10 func x x l imm[14: 0]을 ra에 저장 l ra[15]는 imm[14]와 같음 l mode: 100 src 1 src 2 l mode: 010 (move mbr, [r]) 외부 메모리 값을 mbr에 저장 l mode: 001 (move [r], rsrc) rsrc의 값을 외부 메모리에 저 장 func: 100 (add) func: 001 (adc) src 1 = src 1 + src 2 + CF l func: 010 (sub) src 1 = src 1 - src 2 (move rdst, rsrc) rsrc의 값을 rdst로 move src 2 src 1 = src 1 + src 2 l p Type 1 - move 1 00 mode x x l src 1 l func: 011 (sbb) src 1 = src 1 - src 2 - CF l func: 100 (and) src 1 = src 1 & src 2 l func: 101 (or) src 1 = src 1 | src 2 l func: 110 (xor) src 1 = src 1 ^ src 2 l func: 111 (cmp) src 1 - src 2 34

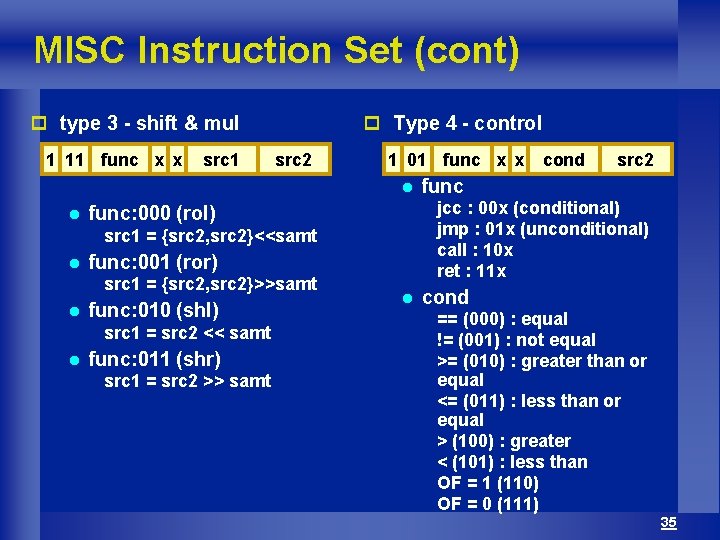

MISC Instruction Set (cont) p type 3 - shift & mul 1 11 func x x src 1 p Type 4 - control src 2 1 01 func x x l l func: 001 (ror) src 1 = {src 2, src 2}>>samt l func: 010 (shl) src 1 = src 2 << samt l func: 011 (shr) src 1 = src 2 >> samt src 2 func jcc : 00 x (conditional) jmp : 01 x (unconditional) call : 10 x ret : 11 x func: 000 (rol) src 1 = {src 2, src 2}<<samt l cond == (000) : equal != (001) : not equal >= (010) : greater than or equal <= (011) : less than or equal > (100) : greater < (101) : less than OF = 1 (110) OF = 0 (111) 35

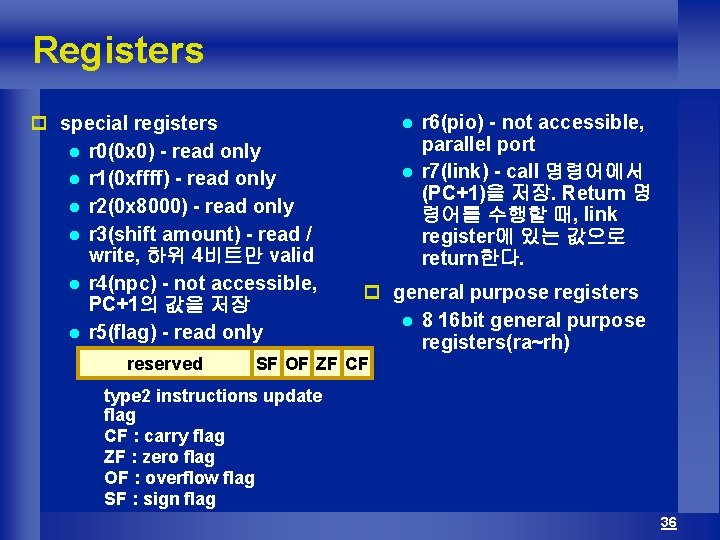

Registers p special registers l r 0(0 x 0) - read only l r 1(0 xffff) - read only l r 2(0 x 8000) - read only l r 3(shift amount) - read / write, 하위 4비트만 valid l r 4(npc) - not accessible, PC+1의 값을 저장 l r 5(flag) - read only reserved l l r 6(pio) - not accessible, parallel port r 7(link) - call 명령어에서 (PC+1)을 저장. Return 명 령어를 수행할 때, link register에 있는 값으로 return한다. p general purpose registers l 8 16 bit general purpose registers(ra~rh) SF OF ZF CF type 2 instructions update flag CF : carry flag ZF : zero flag OF : overflow flag SF : sign flag 36

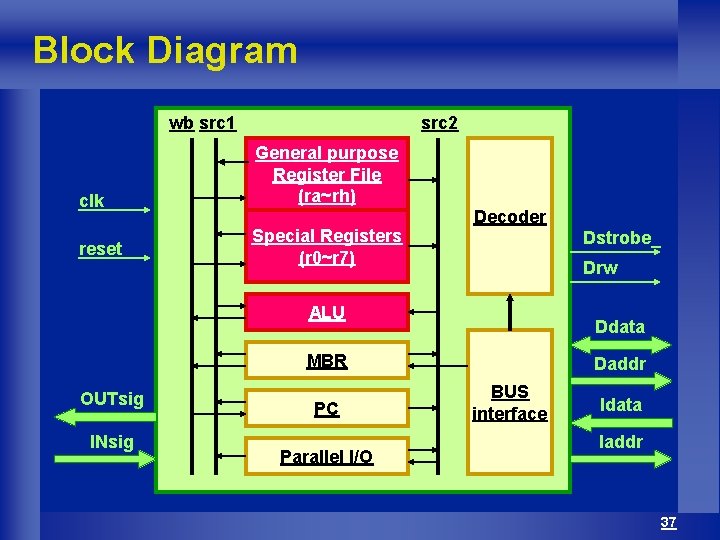

Block Diagram wb src 1 src 2 clk General purpose Register File (ra~rh) reset Special Registers (r 0~r 7) Decoder Dstrobe_ Drw ALU Ddata MBR OUTsig INsig PC Parallel I/O Daddr BUS interface Idata Iaddr 37

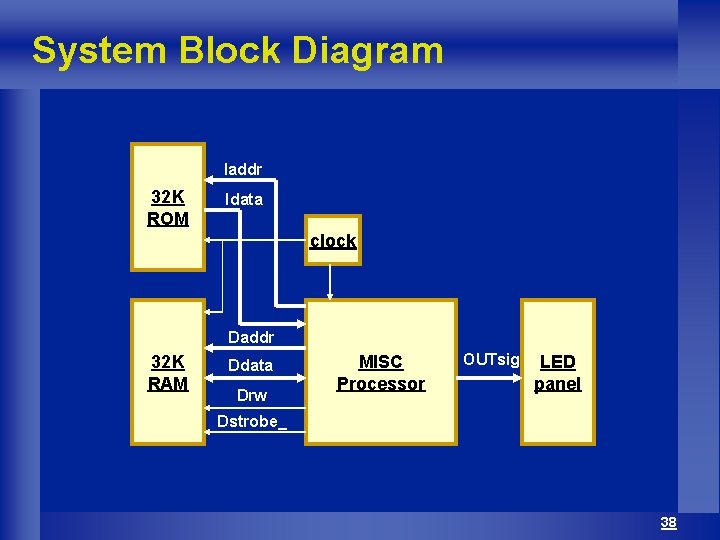

System Block Diagram Iaddr 32 K ROM Idata clock Daddr 32 K RAM Ddata Drw MISC Processor OUTsig LED panel Dstrobe_ 38

- Slides: 38