Lab Environment and Miniproject Assignment Spring 2009 ECE

Lab Environment and Miniproject Assignment Spring 2009 ECE 554 Digital Engineering Laboratory

Lab Environment Ten 1. 8 GHz Core 2 Duo Workstations with 4 GB RAM and 200 GB Harddrives l Design Tools l – Xilinx ISE – Integrated Software Environment – Xilinx EDK – System Level Integration Software – Modelsim – Simulation Environment l Instrumentation – Hewlett-Packard Oscilloscopes – probing logic values – Agilent Logic Analyzers – monitor data on output pins – Xilinx Virtex 2 -Pro FPGA Boards

Lab Warnings l l l l Do not wear static electricity generating clothing (wool sweaters) Report stuff dripping from ceiling (don’t touch it). Don’t sit or stand on backs of chairs or lab tables Don’t probe (with oscilloscope) or touch anything on the FPGA board, except for push buttons, DIP switches, and special pins for clocks and expansion headers (left and right sides of board) Do not do any wiring on the board with power on Be sure you download the correct files to the FPGA Carefully read all warnings in Lab Environment handout

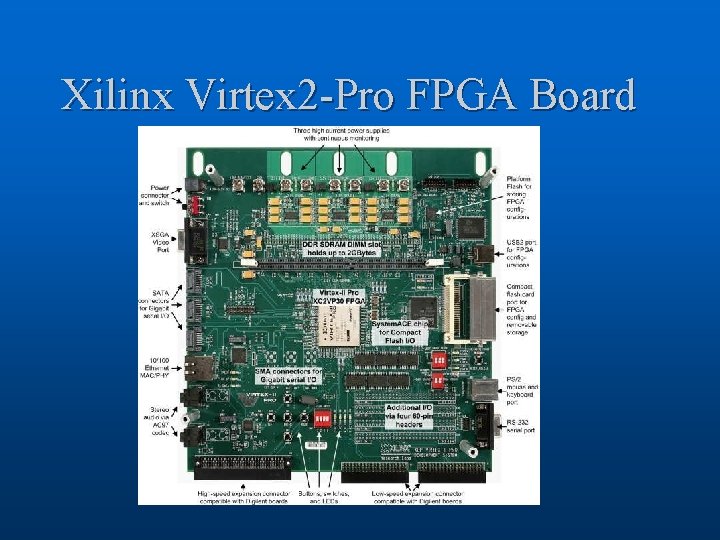

Xilinx Virtex 2 -Pro FPGA Board

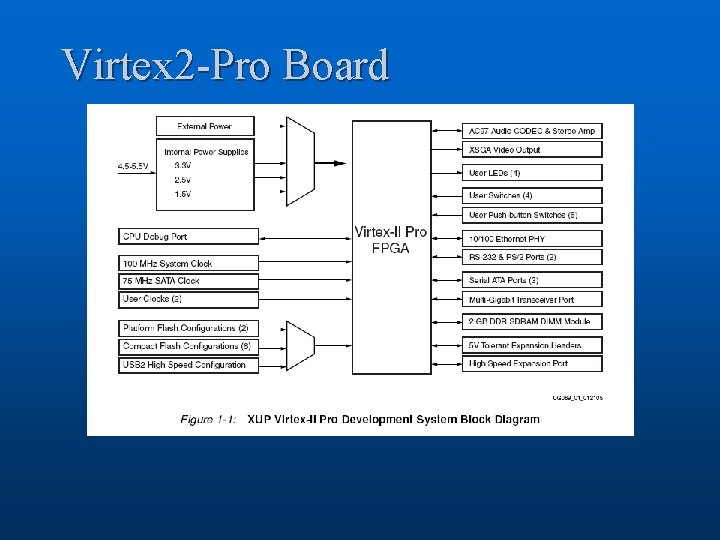

Virtex 2 -Pro Board

Virtex 2 -Pro Board: Features l l l l Xilinx Virtex FPGA (Compute) 256 MB DDR Memory (PC 2100) (Store for Read/Write) Serial Ports to PC (I/O from/to Outside World) Keyboard/Mouse (PS/2) Port VGA Output to VGA Monitor Audio/Video Converters See Virtex 2 -Pro Board Manual at: http: //www. digilentinc. com/Data/Products/XUPV 2 P_User_Guide. pdf

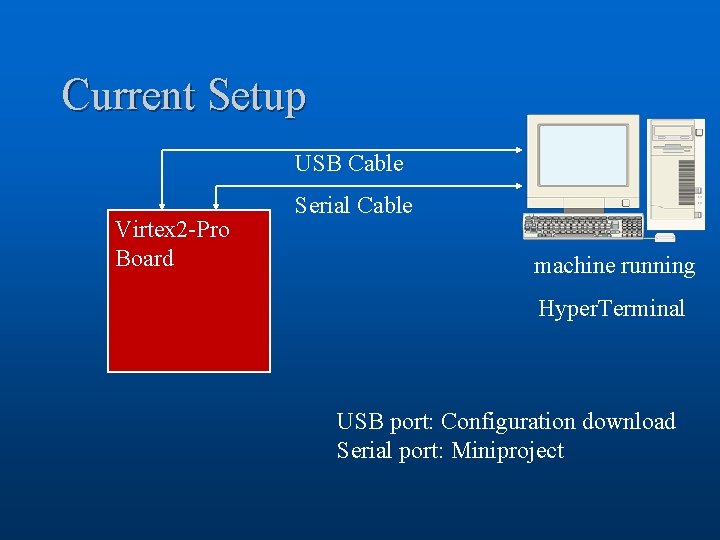

Current Setup USB Cable Virtex 2 -Pro Board Serial Cable machine running Hyper. Terminal USB port: Configuration download Serial port: Miniproject

Miniproject Specification l For the miniproject, you will – Design a Special Purpose Asynchronous Receiver/Transmitter (SPART) and its testbench in Verilog/VHDL – Simulate the design to ensure correct performance – Download the design and associated files and demonstrate correction functionality – Prepare a report on your design

Miniproject Objectives To get familiar with the lab environment prior to the class project and bench exam l To get practice using HDL in your designs l To provide the basic I/O interface to the class project l To get experience working with a partner l

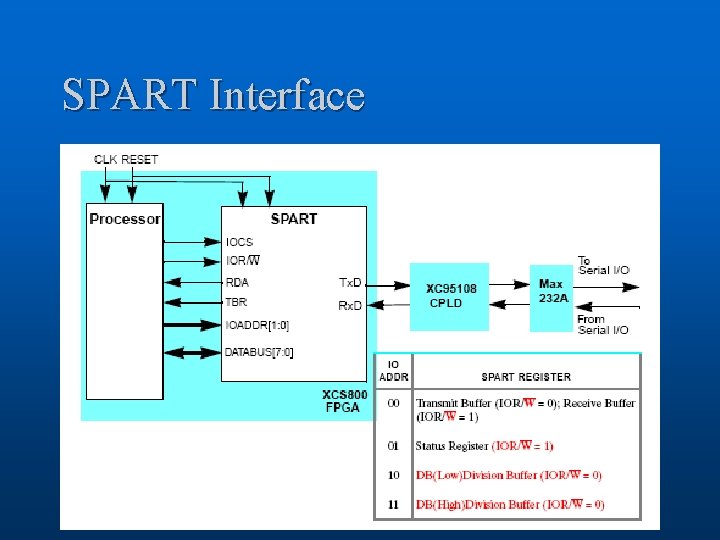

SPART Interface

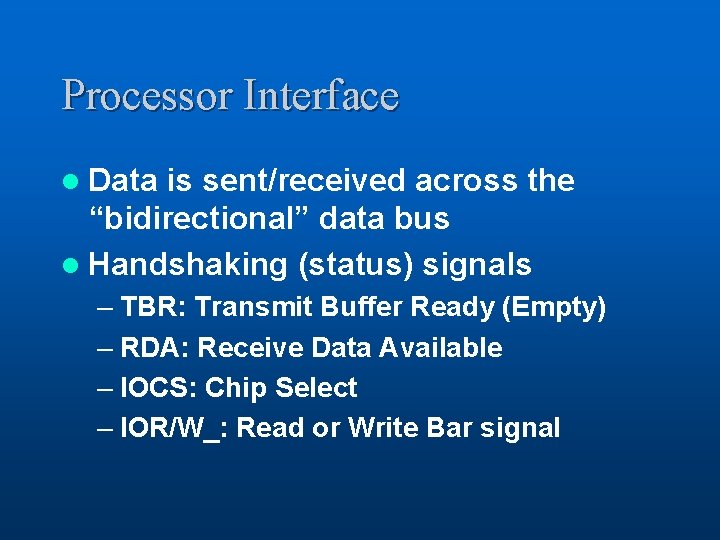

Processor Interface l Data is sent/received across the “bidirectional” data bus l Handshaking (status) signals – TBR: Transmit Buffer Ready (Empty) – RDA: Receive Data Available – IOCS: Chip Select – IOR/W_: Read or Write Bar signal

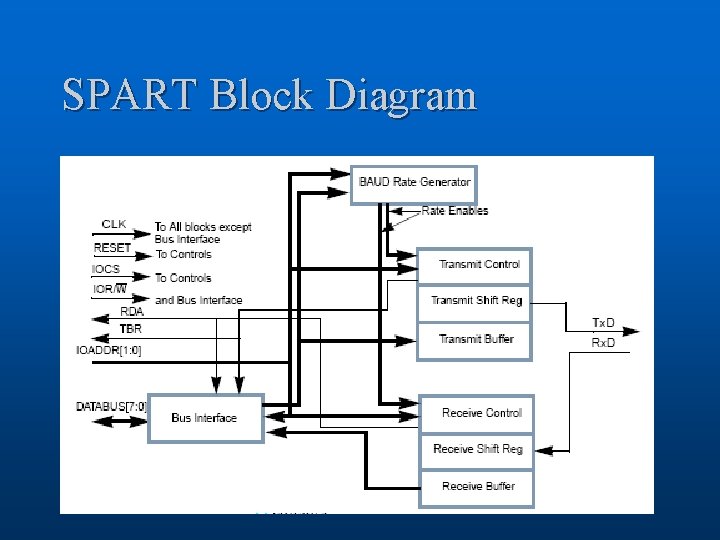

SPART Block Diagram

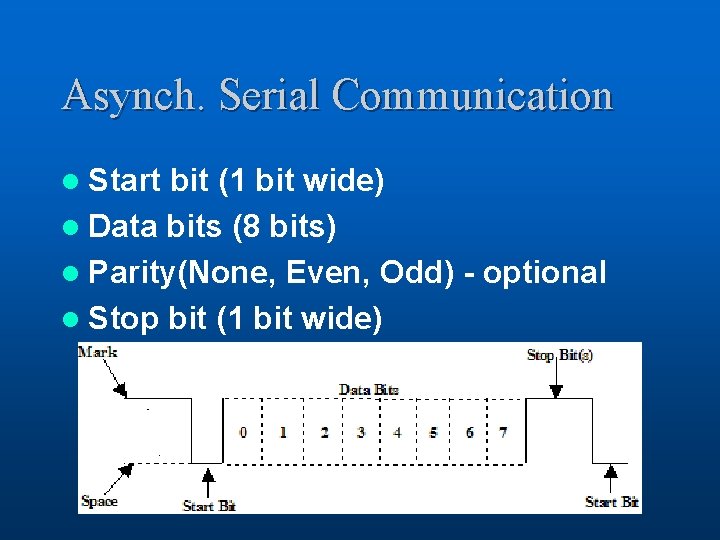

Asynch. Serial Communication l Start bit (1 bit wide) l Data bits (8 bits) l Parity(None, Even, Odd) - optional l Stop bit (1 bit wide)

Transmitting l Tx must be tested first. l Tx shifts the “LSB” out from Tx buffer first. l Tx sends “stop bit” when there is nothing to send.

Receiving l Receiver samples the Rx. D to get the beginning of the “start bit” l Use “resynchronization” to avoid “metastability” of any flip-flop

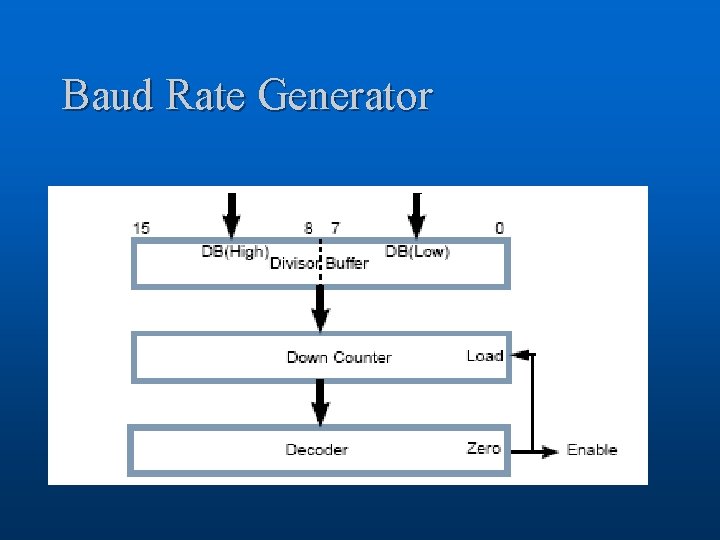

Baud Rate Generator

Baudrate and Sampling We want the transmission rate to be constant for different input clocks l Baud rates of 4800 and 9600 bit per second l Sampling rate = x 16 of the baud rate (bit rate) l Divide the clock to get the “Enable” signal (sampling rate) l

Testbench l l l Previously a mock processor implemented as a simiple finite state machine Use the EDK to interface your SPART to a bus which can communicate with a Power. PC processor Receive data on the Rx. D from keyboard and transmit (echos) back on the Tx. D back to the Hyper. Terminal Implement a simplified printf that can print character strings Load Baud Rate Generator with Arbitrary value Demonstrate ability to work at different Baud Rates using the BRG register

Demonstration Show the ability to receive and transmit characters at 4800 and 9600 buad rates. l Demos class. done in lab on 2/5 at start of

Miniproject Report l l l Due 2/5 at start of class Verilog/VHDL code for your design with clear comments Description of the function of the SPART and each block in the design, including the testbench Record of experiments conducted and how the design was tested Problems encountered and solutions employed

- Slides: 20