Lab 3 Introduction ORCAD Schematic Symbols Hardware Timer

Lab 3 Introduction ORCAD Schematic Symbols Hardware Timer (output compare) Modular Programming Concept XY Keypad Scanning RS 232 Transmission 10/3/2020 Intro to Lab 3 1

Install ORCAD Lite V. 9. 2 • Install ORCAD Lite 9. 2 from ECE 250 Textbook CDROM or the ECE 331 AFS Class Website • Click “Setup. exe”. • Choose to install “Capture CIS” and “PSPICE” only. • Take the defaults as you install. 10/3/2020 Intro to Lab 3 2

Installing ORCAD Digikey Part Symbol Libraries • Digikey parts library found on the ECE 331 Lab 1 Class Folder • Double left click on DIGIKEYLIBRARIES. zip • Extract to C: Program FilesOrcad. LiteCaptureLibrary • Do the same with the DIGIKEYDATABASE. zip file. 10/3/2020 Intro to Lab 3 3

To Find ORCAD 9 S 12 C 128 Module Symbol • Open the Orcad schematic folder in the Lab 1 folder. • Open the Lab 1 schematic. • The CSM 12 C 128 module symbol must be now be cut and pasted from this diagram into your own design project that is set up elsewhere on your hard drive. 10/3/2020 Intro to Lab 3 4

To find SPST Pushbutton Symbol • Click on “Place Part” (AND gate symbol) Icon (2 nd down on right). The “Place Part Window” should open. • Click on “Add Library” button. A “Browse File” window should appear with library choices that start with “Amplifier” and end with “Transistor”. Highlight all of these files by SINGLE left clicking on “Amplifier” and then hold the SHIFT key down while single left click on “Transistor”. All libraries should now be highlighted. Press the “OPEN” button to select all of these libraries. • Now many parts should be available for inclusion in your schematic drawing. For example, In the “Part” dialog box, type “SW” (you must type capital letters!) and then browse down to the “Down Arrow” to see all of the different switch symbols displayed at the lower left of the Place Part window. Select SW PUSHBUTTON/DISCRETE by double left clicking on it to select this part and to place it in the schematic. 10/3/2020 Intro to Lab 3 5

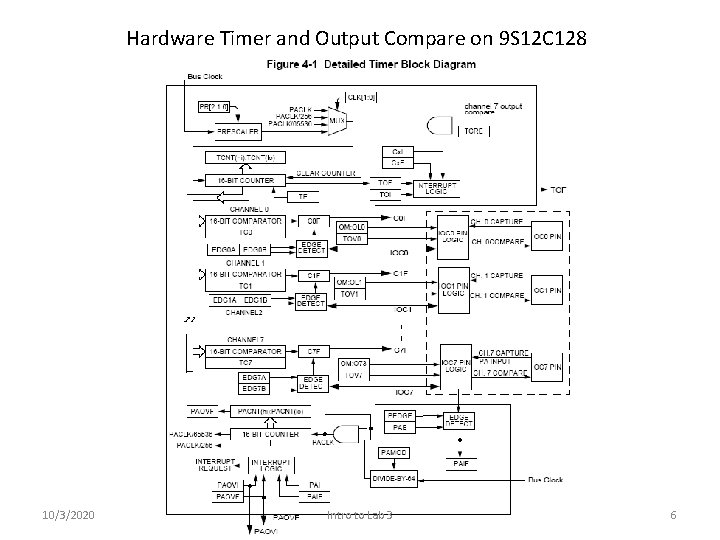

Hardware Timer and Output Compare on 9 S 12 C 128 10/3/2020 Intro to Lab 3 6

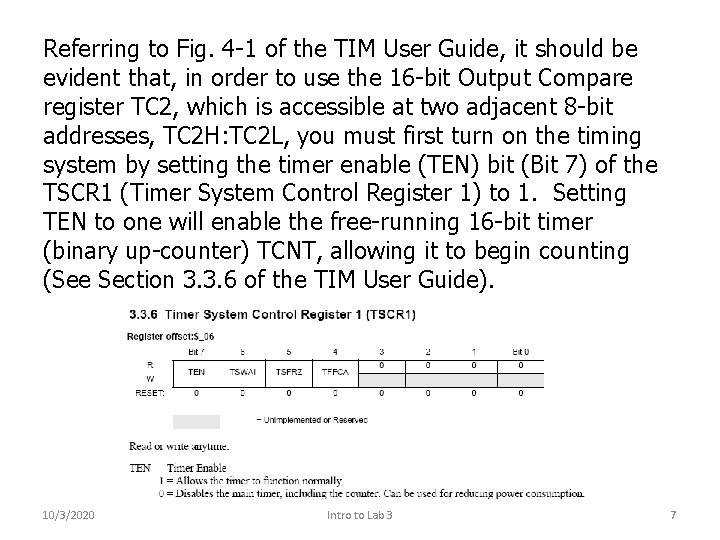

Referring to Fig. 4 -1 of the TIM User Guide, it should be evident that, in order to use the 16 -bit Output Compare register TC 2, which is accessible at two adjacent 8 -bit addresses, TC 2 H: TC 2 L, you must first turn on the timing system by setting the timer enable (TEN) bit (Bit 7) of the TSCR 1 (Timer System Control Register 1) to 1. Setting TEN to one will enable the free-running 16 -bit timer (binary up-counter) TCNT, allowing it to begin counting (See Section 3. 3. 6 of the TIM User Guide). 10/3/2020 Intro to Lab 3 7

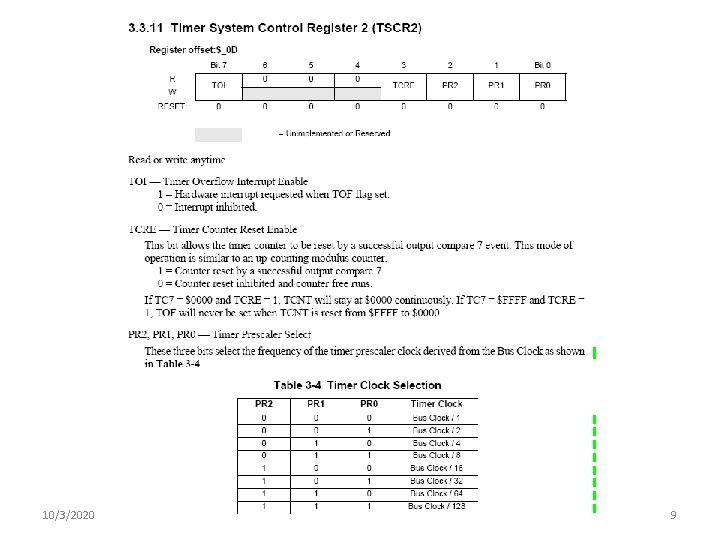

Since TCNT is 16 bits long, and the 9 S 12 C 128 is an “eight bit” microcontroller, meaning that there can only be 8 bits at each memory location, TCNT must be broken up into two adjacent (8 -bit) registers (just as with any 16 -bit register in the 9 S 12 C 128), with the high (most significant) 8 bits of TCNT in register “TCNTHi”, and the lower 8 bits of TCNT in register “TCNTLo”. We will allow TCNT to “free run”, continuously counting from 0 x 0000 up to 0 x. FFFF, and then wrapping back to 0 x 0000 and repeating the cycle endlessly (until the microcontroller is reset). The rate at which TCNT is incremented (clocked) is selected by the prescaler bits, PR 2: PR 0. These prescale bits may be found in the bottom 3 bits of the Timer System Control Register 2 (TSCR 2), as explained in Section 3. 3. 11 of the TIM User Guide. Your subroutine should set these prescale bits to %011 (see Table 3 -4 in the TIM 16 B 8 Block User Guide) so that the 2 MHz system bus clock frequency will be “prescaled” (divided) by 8, and then used to clock the 16 -bit up counter, TCNT = TCNTHi: TCNTLo. Therefore, we may assume that TCNT increments once every 8 / 2 MHz = 4 μs. (Note: the bus clock frequency = ½ * external crystal oscillator frequency. ) 10/3/2020 Intro to Lab 3 8

10/3/2020 Intro to Lab 3 9

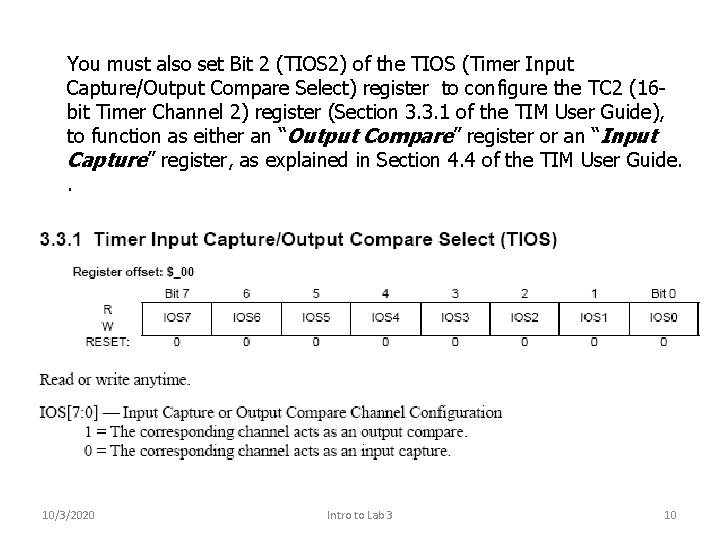

You must also set Bit 2 (TIOS 2) of the TIOS (Timer Input Capture/Output Compare Select) register to configure the TC 2 (16 bit Timer Channel 2) register (Section 3. 3. 1 of the TIM User Guide), to function as either an “Output Compare” register or an “Input Capture” register, as explained in Section 4. 4 of the TIM User Guide. . 10/3/2020 Intro to Lab 3 10

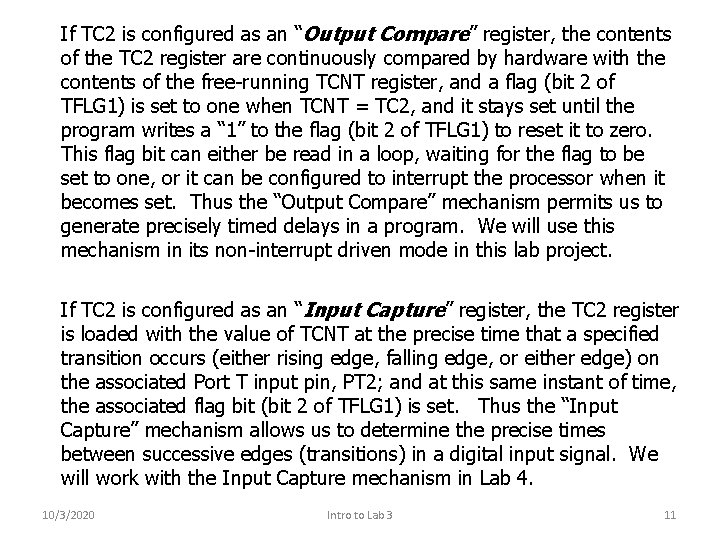

If TC 2 is configured as an “Output Compare” register, the contents of the TC 2 register are continuously compared by hardware with the contents of the free-running TCNT register, and a flag (bit 2 of TFLG 1) is set to one when TCNT = TC 2, and it stays set until the program writes a “ 1” to the flag (bit 2 of TFLG 1) to reset it to zero. This flag bit can either be read in a loop, waiting for the flag to be set to one, or it can be configured to interrupt the processor when it becomes set. Thus the “Output Compare” mechanism permits us to generate precisely timed delays in a program. We will use this mechanism in its non-interrupt driven mode in this lab project. If TC 2 is configured as an “Input Capture” register, the TC 2 register is loaded with the value of TCNT at the precise time that a specified transition occurs (either rising edge, falling edge, or either edge) on the associated Port T input pin, PT 2; and at this same instant of time, the associated flag bit (bit 2 of TFLG 1) is set. Thus the “Input Capture” mechanism allows us to determine the precise times between successive edges (transitions) in a digital input signal. We will work with the Input Capture mechanism in Lab 4. 10/3/2020 Intro to Lab 3 11

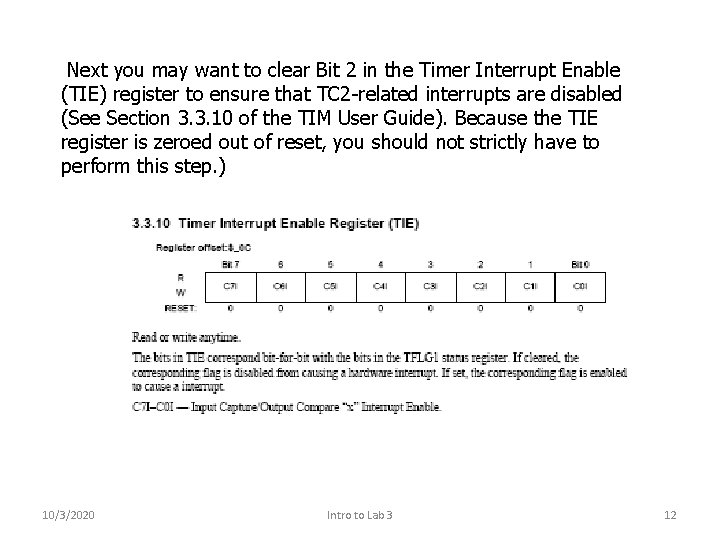

Next you may want to clear Bit 2 in the Timer Interrupt Enable (TIE) register to ensure that TC 2 -related interrupts are disabled (See Section 3. 3. 10 of the TIM User Guide). Because the TIE register is zeroed out of reset, you should not strictly have to perform this step. ) 10/3/2020 Intro to Lab 3 12

Next you should read the present value of the 16 -bit TCNT free running timer, which is accessible at two consecutive addresses, TCNTHi (high byte) and TCNTLo (low byte). (See Section 3. 3. 5 of the TIM User Guide. ) Because we know that the TC 2 flag in the TFLG 1 register will be set as soon as the TCNT register counts up to a value that equals the value loaded in the TC 2 register (Section 4. 4 of the TIM User Guide), you simply need to add the value in the 16 -bit Register Y (which contains Ny, the number of 2 μs time increments we desire to wait) to the current time value found in TCNTHi: TCNTLo. Then store the result in the TC 2 Output Compare Register at TC 2 Hi: TC 2 Lo. This act “ schedules” an output compare event to occur at a time equal to Ny*(4 μs) from the present time, thereby achieving the desired delay. 10/3/2020 Intro to Lab 3 13

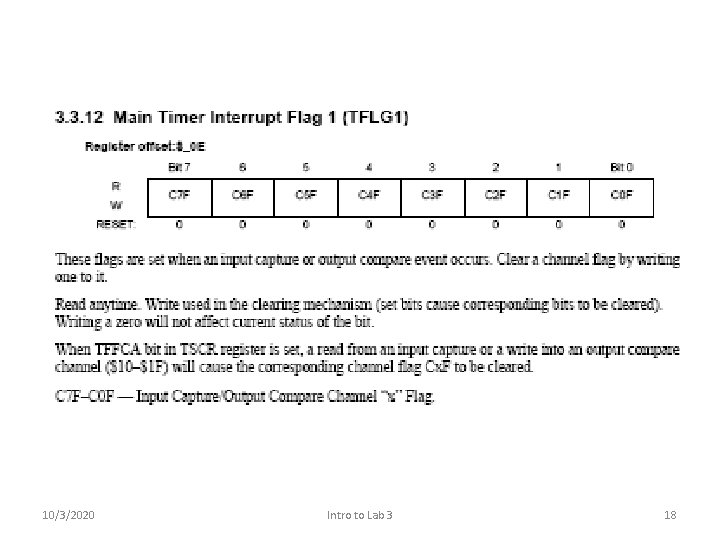

Immediately after you schedule the new output compare event, you must take action to CLEAR the TC 2 Output Compare flag bit by writing a “ 1” (Not a “ 0”!) to the position of that flag bit (Bit #2) in the Main Timer Interrupt Flag (TFLG 1) register, since TC 2 flag has probably already been set from a previous time that the TCNT register “counted past” whatever (garbage value) was previously held by the TC 2 register before the desired output compare event was scheduled. Note from Section 3. 3. 12 in the TIM User Guide that writing a zero to a bit position in TFLG 1 will NOT change that flag. Thus the instruction MOVB #4, TFLG 1 will clear the TC 2 flag, but it will NOT affect the state of any of the other timer interrupt flags (See Section 3. 3. 12 of the TIM User Guide). This is important if other output compares are simultaneously being used in a program to perform other timing functions. 10/3/2020 Intro to Lab 3 14

IMPORTANT NOTE: Do not attempt to clear a timer flag using the BSET instruction when more than one Timer Channel is being used. 10/3/2020 Intro to Lab 3 15

For example, imagine that we attempt to use “BSET TFLG 1, $40” to clear the TC 6 flag, but we are also using the TC 2 flag to time another event elsewhere in the program. Then the BSET instruction will first READ the entire TFLG 1 register, logically OR it with $40, and then write the result back to TFLG 1. This procedure works FINE for setting Bit #6 in a normal RAM location, but it will CLEAR all of the timer flags (both TC 6 and also TC 2) in the TFLG 1 register! 10/3/2020 Intro to Lab 3 16

Thus the operation of Timer Channel 2 will be disturbed by our effort to clear the Timer Channel 6 flag! The solution is simple: use “MOVB #$40, TFLG 1” to clear TC 6! This will not affect any other of the flags in TFLG 1, since 0 s are written to all of the other flags. 10/3/2020 Intro to Lab 3 17

10/3/2020 Intro to Lab 3 18

Finally, your program must enter a loop that waits until TCNT counts up to a value that equals the contents previously stored in the TC 2 Output Compare register. This event causes the TC 2 flag in the TFLG 1 register to be set to 1 by the Output Compare hardware at the point in time when TCNTHi: TCNTLo has counted up to the value stored at TC 2 H: TC 2 L. This happens after Ny*(4 μs) have elapsed. Note that the Timer Control Registers 1 and 2 (TCTL 1 and TCTL 2) allow output compare events to cause automatic changes on the corresponding PORT T I/O pin. (See Section 3. 3. 8 and Table 3. 2 of the TIM User Guide). However, in this application we do not want to activate this feature, allowing the PORT T pins to be used for simple parallel I/O functions. Note that TCTL 1 and TCTL 2 registers are cleared out of reset, and according to Table 3 -2 of the TIM User Guide, this will disable the output compare function on the PORT T pins, as we desire. Therefore your subroutine can either ignore TCTL 1 and TCTL 2, or you may want to set them to zero up near the beginning of the subroutine, just to be sure that an output compare event will not affect the PORT T pins. 10/3/2020 Intro to Lab 3 19

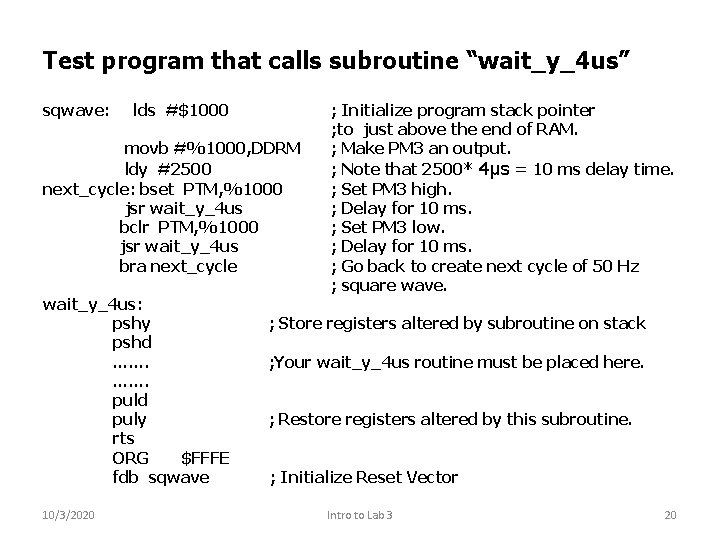

Test program that calls subroutine “wait_y_4 us” sqwave: lds #$1000 movb #%1000, DDRM ldy #2500 next_cycle: bset PTM, %1000 jsr wait_y_4 us bclr PTM, %1000 jsr wait_y_4 us bra next_cycle wait_y_4 us: pshy pshd ……. puld puly rts ORG $FFFE fdb sqwave 10/3/2020 ; Initialize program stack pointer ; to just above the end of RAM. ; Make PM 3 an output. ; Note that 2500* 4μs = 10 ms delay time. ; Set PM 3 high. ; Delay for 10 ms. ; Set PM 3 low. ; Delay for 10 ms. ; Go back to create next cycle of 50 Hz ; square wave. ; Store registers altered by subroutine on stack ; Your wait_y_4 us routine must be placed here. ; Restore registers altered by this subroutine. ; Initialize Reset Vector Intro to Lab 3 20

Modular Program Design A software module is very much like a hardware module, in that it is an easily detachable and separately testable section of code that has just one entry point and one exit point. In this project, each module will be written as a subroutine. A separate project will be created to test each subroutine using a "“short and simple” test program that calls that subroutine under test and exercises it sufficiently. Finally, once all of the component subroutine modules have been individually validated, they will be integrated together via a main program that calls each subroutine in turn. 10/3/2020 Intro to Lab 3 21

Top-Down Modular Design: The steps in the top-down modular system design (this applies to both hardware and/or software design) are listed below: 1. Precisely and fully specify the overall design. When a need arises for a new product, many “gaps” usually exist in the initially (somewhat vague) product description. Many secondary design decisions usually have to be made in order to “fill the gaps”. 2. Intuitively break the overall design into smaller subsystems (modules), which are easily designed, debugged, and modified separately from each other. Furthermore, each module should be able to interconnect with the other modules in a clean and straightforward way that requires the fewest possible number of “interconnections”. 3. Develop precise and detailed specifications for each module. 10/3/2020 Intro to Lab 3 22

4. Implement each module exactly as specified. (Perhaps several designers will implement several modules concurrently. ) New designers sometimes have trouble following this step. Although they are certainly encouraged to be as clever and creative as possible as they internally design the modules, they MUST NOT creatively modify any of the external module interface specifications in any way. After all, their modules are going to have to integrate with other modules created by others. 5. The source (assembly or C) code for each module (usually a subroutine) must be fully described, along with revision number and author, in a “ header comment block”. Many companies have a standard header block format that must be followed by any programmers who work for the company. This guarantees that all modules are fully documented right in their source code, permitting these modules to be used easily in future applications as well as in the present one. 6. Fully debug and then test each module SEPARATELY until each module fully complies with the specifications that were assigned to it. 7. Integrate all modules into a complete system. Then test to see that the original overall system specifications have been fully met. If not, “loop back” to Step 4. 10/3/2020 Intro to Lab 3 23

Header Block • • • The program (or subroutine) name. Description of its intended purpose and possible application. Author’s name, phone number, and company location and job site. Date of initial writing. For each revision made: revision number, descriptions of revision made and date of revision. Text or journal reference(s) to algorithm(s) used in the module. Description of all input data needed, and how this input data is to be sent to the module. (There at least three possibilities: (a) in specified machine registers, (b) in specified RAM locations, and (c) on the stack. ) Description of output data produced by the module; how each resulting output datum relates to the input data, and where each of the output data can be found after the module is executed. Statement of potential problems or side effects of using this software module. Indicate which, if any, internal machine registers are modified (clobbered) by the module. 10/3/2020 Intro to Lab 3 24

Switch Debounce Delay Study • Project Board SPST pushbutton switch bounces appear to die out so quickly that no delay routine need be called to debounce (just the instruction delays in the programs provide sufficient debouncing delay!) • To have a much more “bouncy” switch to work with, take out the SPST pushbutton, and replace it with a grounded wire. • Now investigate how long a delay is needed to adequately debounce this “wire” switch so that the LED can be toggled reliably. 10/3/2020 Intro to Lab 3 25

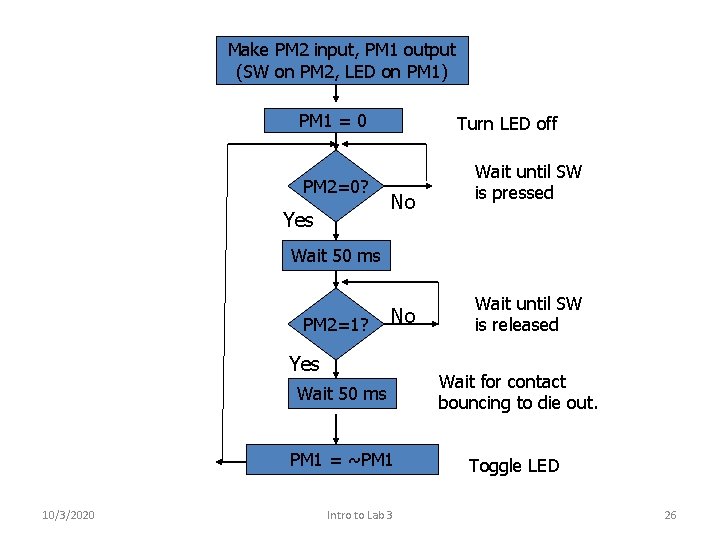

Make PM 2 input, PM 1 output (SW on PM 2, LED on PM 1) PM 1 = 0 PM 2=0? Yes Turn LED off No Wait until SW is pressed Wait 50 ms PM 2=1? No Yes 10/3/2020 Wait until SW is released Wait 50 ms Wait for contact bouncing to die out. PM 1 = ~PM 1 Toggle LED Intro to Lab 3 26

XY-Keypad Scanning • Our keypad is made up of 16 SPST keyswitches. • Normally, 16 wires (plus a 17 th ground wire) would be needed to interface 16 switches to our microcontroller. • But “X-Y” keypad scanning can do it in just 8 wires! • Each keyswitch bridges one of four row wires to one of four column wires when pressed. • Keypad scanning is easiest to implement with an 8 -bit bidirectional I/O port whose directionality can be reconfigured “on the fly” in software. • In our lab, we could any 8 -bit bidirectional port, such as PORTAD or Port T for this task. 10/3/2020 Intro to Lab 3 27

Interfacing a 4 X 4 16 -key X-Y Keypad to PORT T (Note: Internal input pull-up resistors must be enabled by setting PERT = $FF!) 10/3/2020 Intro to Lab 3 28

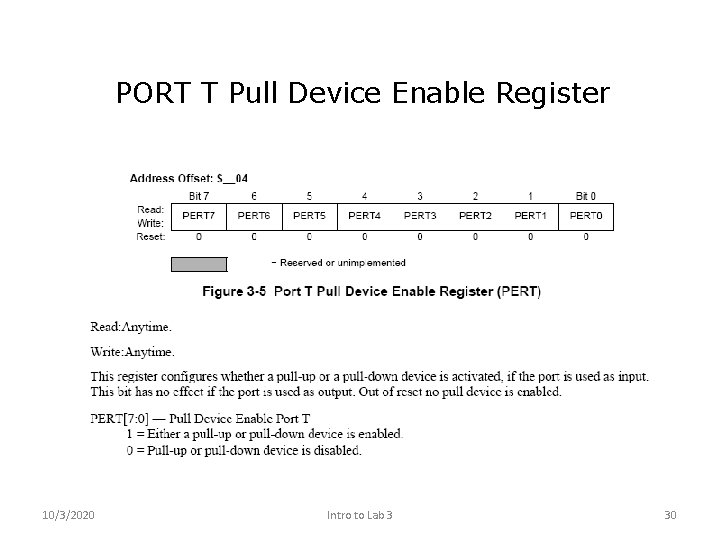

Keypad Scanning Procedure • To find out when a key is depressed (and also to identify the key’s location in the keypad matrix), the four pins connected to the rows (PT 3: 0) are initially configured as inputs, while the four pins connected to the columns (PT 7: 4) are initially configured as outputs. • It is very important to enable the internal (10 kΩ) pull-up resistors on the Port T pins that are configured as inputs. • This is done by setting the “Port T Pull Device Enable” (PERT = $204) register to $FF. (See Section 3. 3. 1 and Figure 3 -5 of the Port Interface Module (PIM) 9 C 32 Block Guide, S 12 C 32 PIMV 1. pdf). 10/3/2020 Intro to Lab 3 29

PORT T Pull Device Enable Register 10/3/2020 Intro to Lab 3 30

• The output (column) pins (PT 7: 4) are then driven low, that is PT 7: 4 are set to %0000, and the input (row) pins (PT 3: 0) are repetitively read in a loop. • While no key is yet depressed, all four of the input (row) pins should read high “ 1”; that is PT 3: 0 should be read as %1111. • But if a key is depressed, the row pin that is connected to the pressed switch is driven low “ 0”, since the output resistance of a 9 S 12 C 32 output pin is much lower than the (internal) 10 k-Ohm pull-up resistor. • The row pin that reads low (all the rest should read high) corresponds to the row that the depressed key is in. 10/3/2020 Intro to Lab 3 31

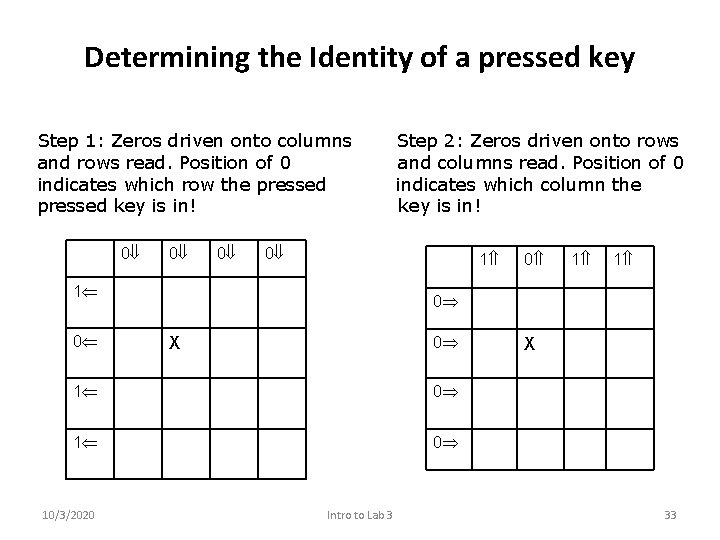

• In order to discover the column that the switch is in, the I/O directions of the column pins and row pins should next be reversed. This time all four of the output (row) pins (PT 3: 0) are driven low, that is PT 3: 0 = %0000. • The column pins (PT 7: 4) may now be read by the M 9 S 12 C 128 in order to find out which one of these pins is low (certainly one of them should be low, since a key was already found to be depressed). • The column pin that reads low (the other 3 inputs should read high) corresponds to the column that the depressed key is in. • The entire procedure for determining the row and column of a depressed key is illustrated on the next slide. The drawing on the left shows the first step, where the columns (PT 7: 4) are driven low and the position of the pressed key is read as a “ 0”on the rows (PT 3: 0). The drawing on the right shows the second step, where the rows are driven low (PT 3: 0) are driven low, and the position of the pressed key is read as a “ 0” on the columns (PT 7: 4). 10/3/2020 Intro to Lab 3 32

Determining the Identity of a pressed key Step 1: Zeros driven onto columns and rows read. Position of 0 indicates which row the pressed key is in! 0 0 1 1 0 Step 2: Zeros driven onto rows and columns read. Position of 0 indicates which column the key is in! 1 1 0 X 0 10/3/2020 0 Intro to Lab 3 X 33

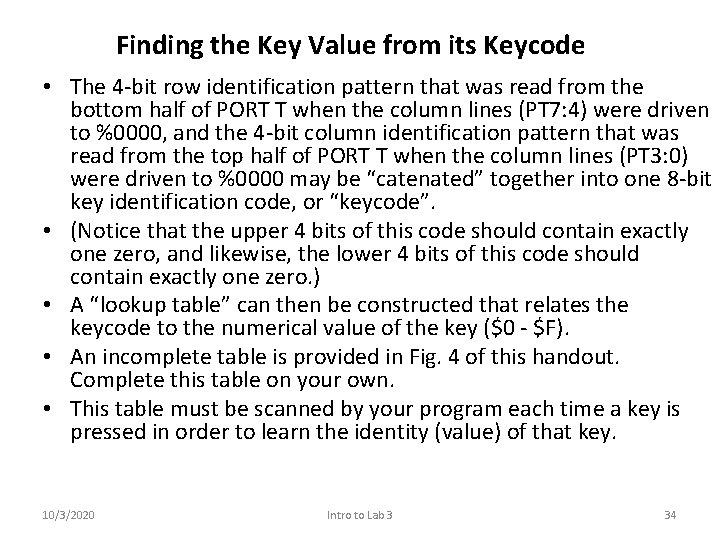

Finding the Key Value from its Keycode • The 4 -bit row identification pattern that was read from the bottom half of PORT T when the column lines (PT 7: 4) were driven to %0000, and the 4 -bit column identification pattern that was read from the top half of PORT T when the column lines (PT 3: 0) were driven to %0000 may be “catenated” together into one 8 -bit key identification code, or “keycode”. • (Notice that the upper 4 bits of this code should contain exactly one zero, and likewise, the lower 4 bits of this code should contain exactly one zero. ) • A “lookup table” can then be constructed that relates the keycode to the numerical value of the key ($0 - $F). • An incomplete table is provided in Fig. 4 of this handout. Complete this table on your own. • This table must be scanned by your program each time a key is pressed in order to learn the identity (value) of that key. 10/3/2020 Intro to Lab 3 34

10/3/2020 P T 7 P T 6 P T 5 P T 4 P T 3 P T 2 P T 1 P T 0 DIG IT 1 0 1 1 1 0 1 1 1 1 1 0 2 1 1 0 3 0 1 1 1 0 1 4 Intro to Lab 3 35

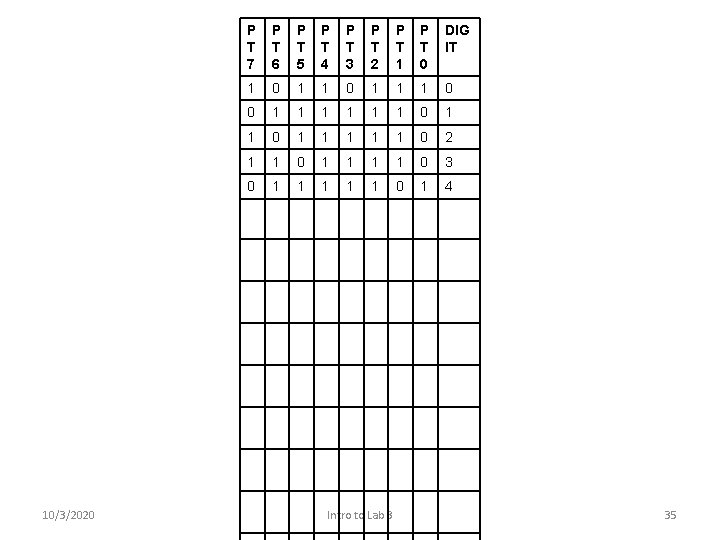

Setting up the keycode search table • Use FCB (DC. B) Directive to set up table in ROM: Keycode_Table: fcb $B 7, $7 E, $BE, $DE, $7 D, . . • Note that the first entry in the Keycode_Table contains the keycode for the “ 0” key, the next entry is the keycode for the “ 1” key, etc. • Thus, when a key is pressed on the keypad and a keycode has been determined by getkey, this table may be searched for a match with the keycode. • The position (index offset) of the matching element ($0 - $F) can then be used to index into a second lookup table, ASCII_Table: fcb ‘ 0’, ’ 1’, ’ 2’, ’ 3’, ’ 4’, …. . To find the ASCII code of the depressed key. Note that apostrophes extract ASCII code: ‘A’ = $41, ‘ 5’ = $35, etc. 10/3/2020 Intro to Lab 3 36

Summary of Get. Key Subroutine • • • START Getkey Loop here until key is pressed; Delay 40 ms to wait for switch bouncing to die out; Get a 4 -bit row position code; Get a 4 -bit column position code; Catenate the two 4 -bit codes into a “keycode”. Find offset of key in “Keycode” lookup table; Index using the offset found above into ASCII table Return with ASCII code of key in Acc B; Loop here until key is released; Delay 40 ms to wait for switch bouncing to die out; Return from subroutine 10/3/2020 Intro to Lab 3 37

Waiting for Keypad Input Lines to Settle • Due to the high speed at which the 9 S 12 C 128 executes instructions, it is necessary to insert a short delay (perhaps a JSR wait_y_4 us with Y = 20) between when the zeros are driven out on either the high or the low half of Port T and when the other half of Port T is read. • This delay is necessary because it takes time for the voltage on the input pins that are being read to stabilize after a change occurs on the output pins of Port T. • This is because there is a significant rise time (perhaps a microsecond) that must be waited out on an input pin due to the RC time constant formed between the internal 10 kΩ pull-up resistance and the parasitic capacitance (perhaps 50 picofarads) exhibited by the keypad. Note that tau = RC = (50 p. F)(10 kilohm) = 0. 5 u. S • If you forget to put this short “settling delay” into your getkey subroutine, you may find that your getkey subroutine works fine when you are singlestepping through the routine, but that getkey works unreliably when the program is run at full speed! 10/3/2020 Intro to Lab 3 38

Asynchronous Serial Communications Interface (SCI) • Consists of only 2 pins on the 9 S 12 C 128 microcontroller: – PS 1/TXD (serial transmit data) – PS 0/RXD (serial receive data) – Make sure the two “COM Enable” jumpers on the CSMB 9 S 12 C 128 board have been connected, so these two pins are routed through the RS 232 level translator chip and connected to the on-board CSMB 9 S 12 C 128 DB 9 serial port connector. • Transmit and Receive sides of the SCI interface operate independently and simultaneously, this is called “Full-Duplex” operation) • Uses standard “mark/space” non-return to zero asynchronous serial data transmission format that is used in “RS 232 Serial Communication”. • See the “HCS 12 Serial Communication Interface Block Guide”, S 12 SCIV 2. pdf. 10/3/2020 Intro to Lab 3 39

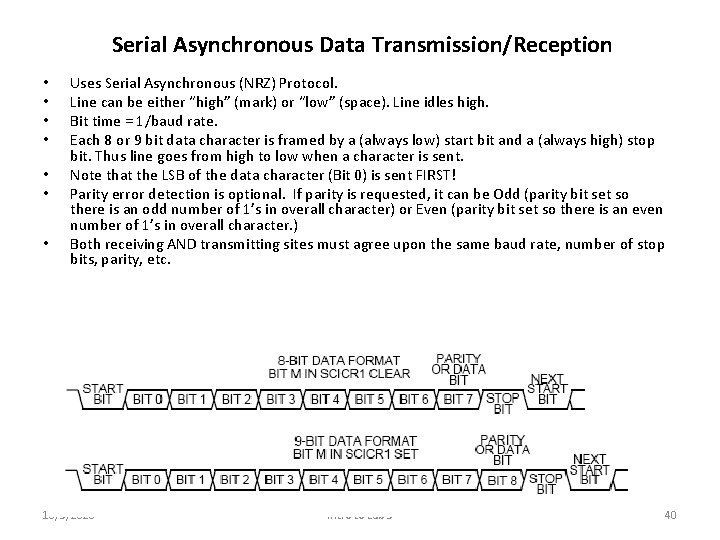

Serial Asynchronous Data Transmission/Reception • • Uses Serial Asynchronous (NRZ) Protocol. Line can be either “high” (mark) or “low” (space). Line idles high. Bit time = 1/baud rate. Each 8 or 9 bit data character is framed by a (always low) start bit and a (always high) stop bit. Thus line goes from high to low when a character is sent. Note that the LSB of the data character (Bit 0) is sent FIRST! Parity error detection is optional. If parity is requested, it can be Odd (parity bit set so there is an odd number of 1’s in overall character) or Even (parity bit set so there is an even number of 1’s in overall character. ) Both receiving AND transmitting sites must agree upon the same baud rate, number of stop bits, parity, etc. 10/3/2020 Intro to Lab 3 40

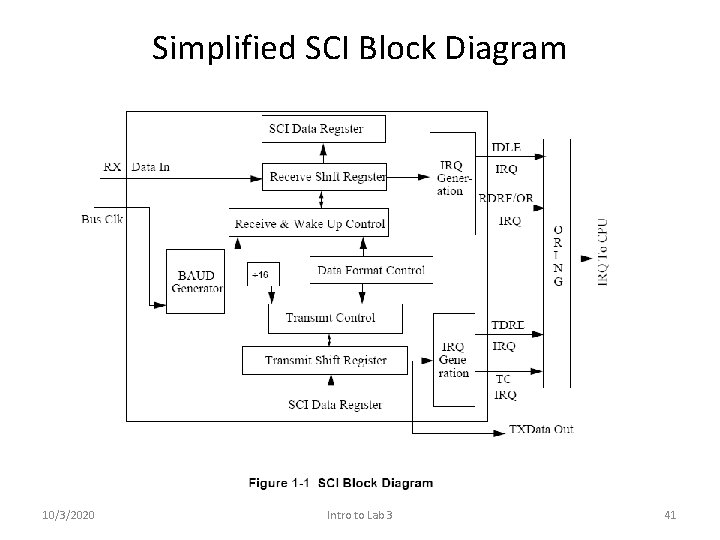

Simplified SCI Block Diagram 10/3/2020 Intro to Lab 3 41

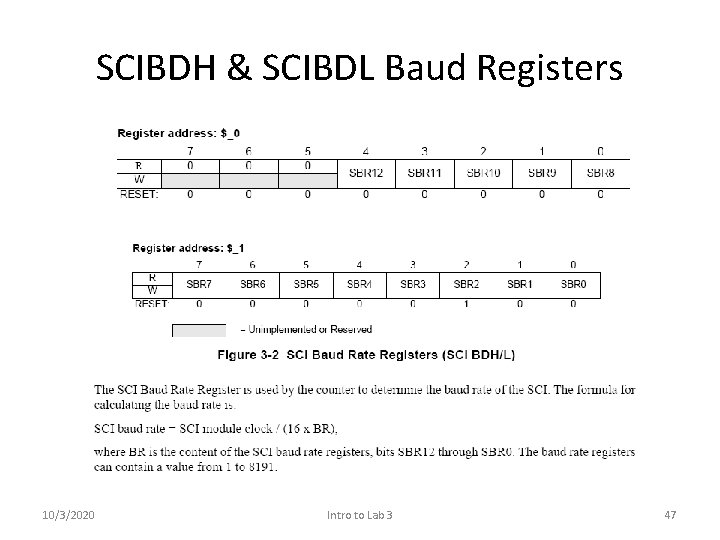

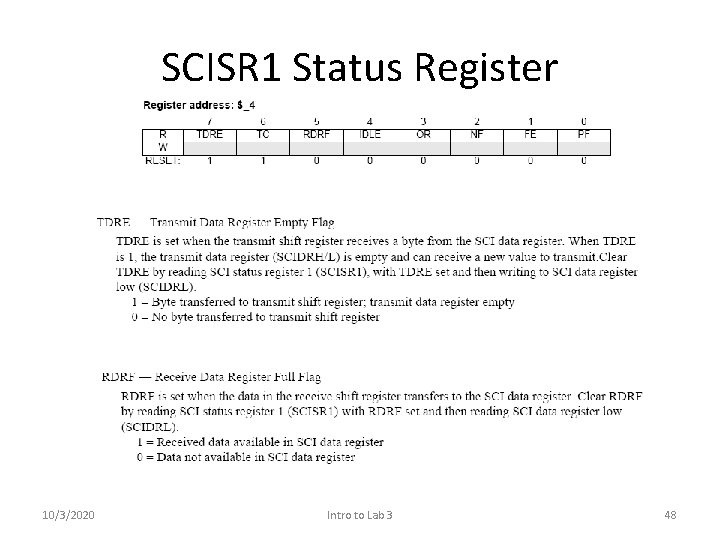

Transmit Side Operation • The transmit side is merely a shift register that is loaded from the SCI transmit holding register after the shift register is done sending current character. • This permits the software to queue up the next character to be sent even while the previous character is being sent, thus there is no software “latency” time in starting the sending of the next character! • This shift register is clocked at the baud rate selected by the baud rate generator. • The baud rate is selected by the programmer by initializing the SCIBDL and SCIBDH baud control registers. • The transmit holding register is loaded by the programmer by WRITING to the SCIDRL register address. This may only be done when the “Transmit Data Register Empty” (TDRE) bit is set in the SCISR 1 status register. • READING from the same SCIDRL address reads the received character from the SCI receive data holding register --- a DIFFERENT register entirely! 10/3/2020 Intro to Lab 3 42

Receive Side Operation • Data received by receiving shift register that dumps its data into a holding register AND sets the RDRF flag (Bit #5 of SCISR 1 status register) once serial shifting is complete. • Received data can be read from SCIDRL register once serial shifting is complete as indicated by RDRF=1. 10/3/2020 Intro to Lab 3 43

Job performed by “Receive Control Logic” • Receive controller is a state machine that is usually clocked at 16*(baud rate) • Thus RXD line is sampled by the Receive Control Unit every 16 th of a bit time. • Initially, as the line idles, the receive control unit samples repeated “ 1 s”, as it searches for the beginning of a start bit wth a time resolution of 1/16 bit time. • The first time it samples a “ 0”, it takes 7 more samples (counting out half of a bit time). If the majority of these samples are “ 0” it assumes a valid start bit was found (otherwise it sets the “Noise Flag” in the SCISR 1 register and resumes searching for a start bit). • Assuming that a valid start bit WAS found, it then takes 16 more samples (counting to the middle of the least significant data bit, D 0). It then enables the first clock pulse to the receive shift register, permitting the first data bit to be clocked into this register precisely in the middle of data bit D 0. This process repeats 7 more times, until all 8 data bits are clocked into the register 10/3/2020 Intro to Lab 3 44

Job Performed by Receive Controller (Cont’d) • If parity was enabled, a 9 th bit is clocked into the receiver shift register, and the contents of all the received bits are examined by parity detection (exclusive OR gate) logic to see if the total number of ones is odd or even, as desired. If not, the “Parity Error” flag bit is set in the SCISR 1 register. • The final bit that is clocked in is the STOP bit. It better be HIGH. If not, the “Framing Error” flag bit is set in SCISR 1. 10/3/2020 Intro to Lab 3 45

Jobs Performed by Receive Controller Cont’d • The framing error will be set if the clocks at the receive and transmit site differ by more than RX-TX Clock Frequency Tolerance = + or – 1/(2 N)*100% (where N = the total number of bits = start + data + Parity (if present) + stop bit. ) If the clocks at the transmit and receive site disagree, a total of + or - ½ bit time of N accumulated sampling time errors is available before a framing error (and associated data bit reception error) will occur. Now resume looking for a start bit during the second half of the STOP bit (go back to first step). Note that this procedure effectively “resynchronizes” the receive clock to the beginning of each new serial character’s start bit. This is why the sampling time errors do not accumulate beyond the number of bits in a single character (N). 10/3/2020 Intro to Lab 3 46

SCIBDH & SCIBDL Baud Registers 10/3/2020 Intro to Lab 3 47

SCISR 1 Status Register 10/3/2020 Intro to Lab 3 48

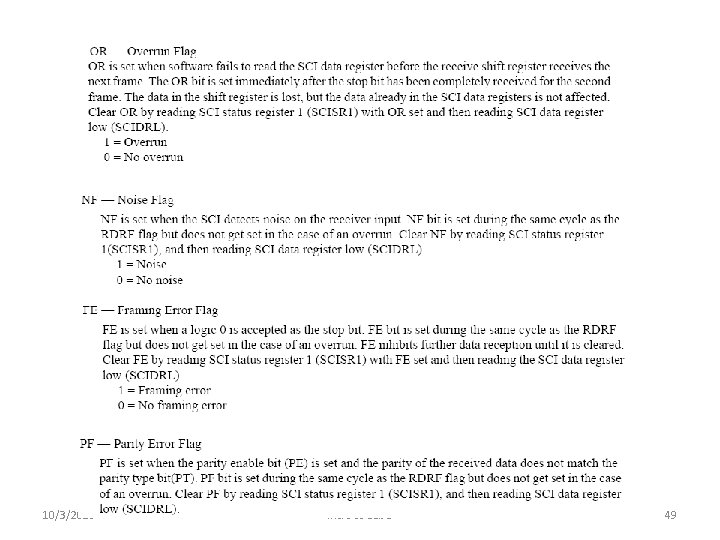

10/3/2020 Intro to Lab 3 49

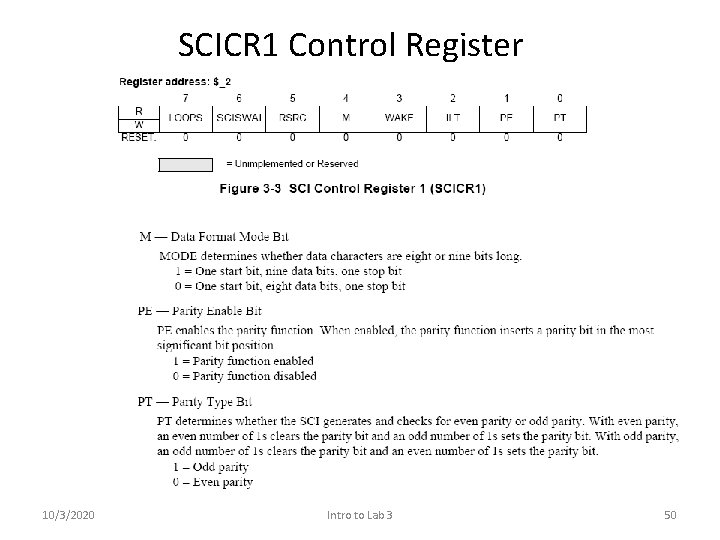

SCICR 1 Control Register 10/3/2020 Intro to Lab 3 50

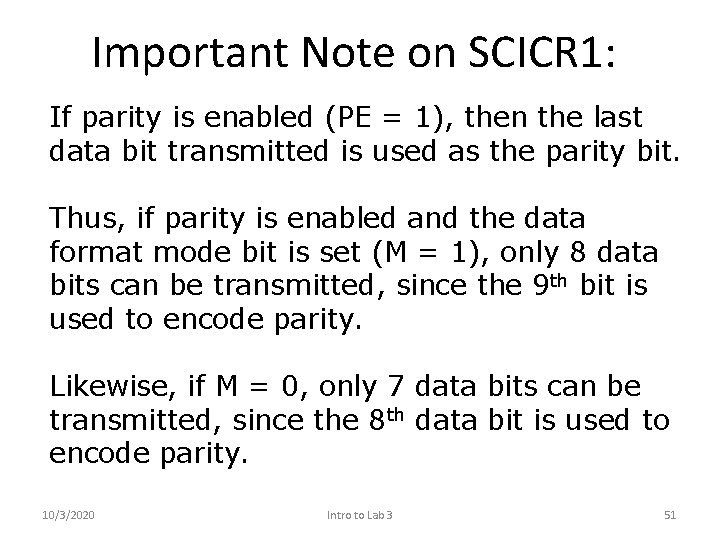

Important Note on SCICR 1: If parity is enabled (PE = 1), then the last data bit transmitted is used as the parity bit. Thus, if parity is enabled and the data format mode bit is set (M = 1), only 8 data bits can be transmitted, since the 9 th bit is used to encode parity. Likewise, if M = 0, only 7 data bits can be transmitted, since the 8 th data bit is used to encode parity. 10/3/2020 Intro to Lab 3 51

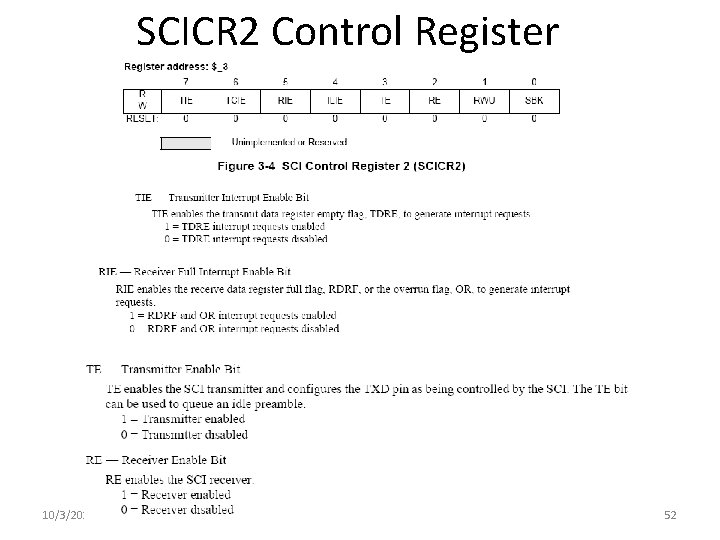

SCICR 2 Control Register 10/3/2020 Intro to Lab 3 52

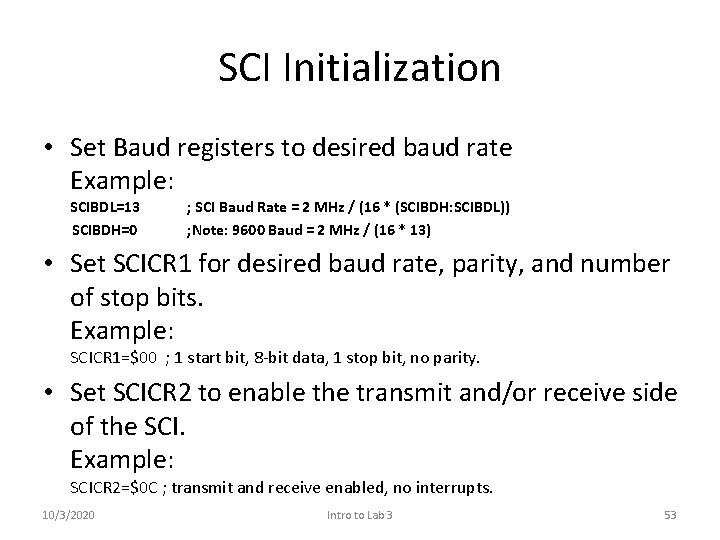

SCI Initialization • Set Baud registers to desired baud rate Example: SCIBDL=13 SCIBDH=0 ; SCI Baud Rate = 2 MHz / (16 * (SCIBDH: SCIBDL)) ; Note: 9600 Baud = 2 MHz / (16 * 13) • Set SCICR 1 for desired baud rate, parity, and number of stop bits. Example: SCICR 1=$00 ; 1 start bit, 8 -bit data, 1 stop bit, no parity. • Set SCICR 2 to enable the transmit and/or receive side of the SCI. Example: SCICR 2=$0 C ; transmit and receive enabled, no interrupts. 10/3/2020 Intro to Lab 3 53

Simple SCI “Inchar” routine • Wait for RDRF flag to be set in SCISR 1 • Read data from SCIDRL • Return from Subroutine Inchar 10/3/2020 Intro to Lab 3 54

Subroutine Outchar • Wait for TDRE bit to be set in SCISR 1 • Write data to SCIDRL • Return from Subroutine Outchar 10/3/2020 Intro to Lab 3 55

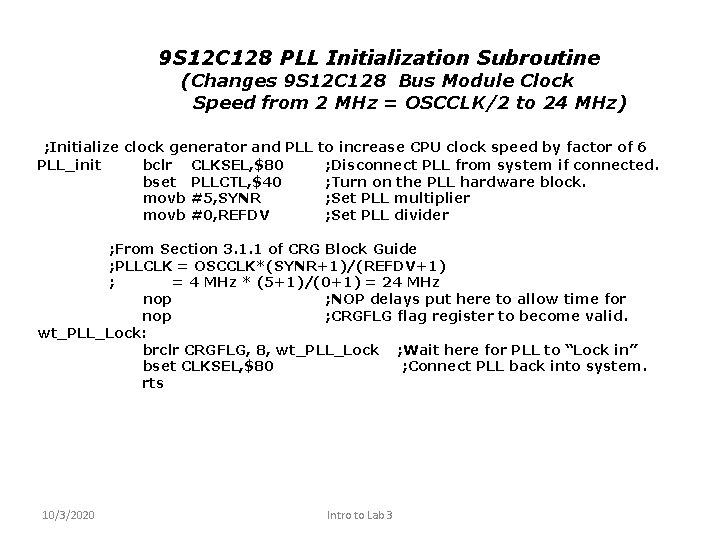

On-Chip Phase-Locked Loop (PLL) Initialization • Not needed when running under the serial monitor, since the serial monitor firmware initializes the PLL on its own. • Allows our microcontroller clock to run at 24 MHz even when in “standalone” RUN mode. • See the Clock Reset Generator CRG Block User Guide, S 12 CRGV 4. pdf 10/3/2020 Intro to Lab 3 56

9 S 12 C 128 PLL Initialization Subroutine (Changes 9 S 12 C 128 Bus Module Clock Speed from 2 MHz = OSCCLK/2 to 24 MHz) ; Initialize clock generator and PLL_init bclr CLKSEL, $80 bset PLLCTL, $40 movb #5, SYNR movb #0, REFDV to increase CPU clock speed by factor of 6 ; Disconnect PLL from system if connected. ; Turn on the PLL hardware block. ; Set PLL multiplier ; Set PLL divider ; From Section 3. 1. 1 of CRG Block Guide ; PLLCLK = OSCCLK*(SYNR+1)/(REFDV+1) ; = 4 MHz * (5+1)/(0+1) = 24 MHz nop ; NOP delays put here to allow time for nop ; CRGFLG flag register to become valid. wt_PLL_Lock: brclr CRGFLG, 8, wt_PLL_Lock ; Wait here for PLL to “Lock in” bset CLKSEL, $80 ; Connect PLL back into system. rts 10/3/2020 Intro to Lab 3

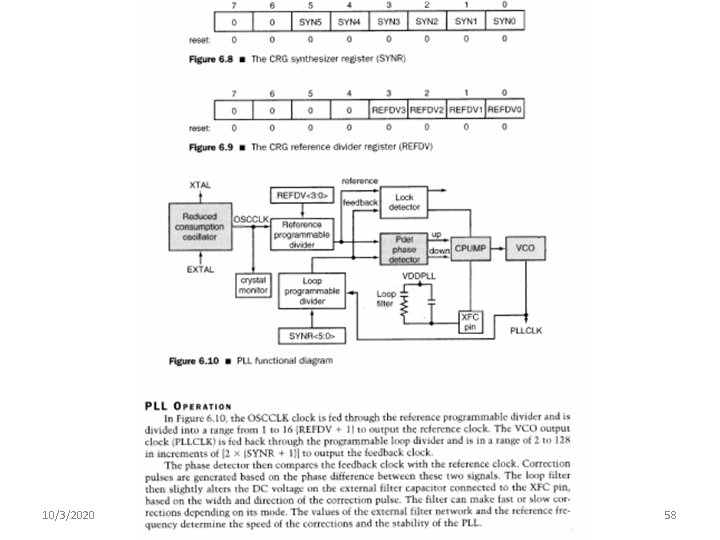

10/3/2020 Intro to Lab 3 58

- Slides: 58